# FPGA implementation of a network coding capable switch

by

Daniel Bernard Beaumont de Villiers

Thesis presented in partial fulfilment of the requirements for the degree of Master of Engineering (Electronic) in the Faculty of Engineering at Stellenbosch University

> Supervisors: Prof. H.A. Engelbrecht Mr. A. Barnard

> > March 2020

# UNIVERSITEIT.STELLENBOSCH.UNIVERSITY jou kennisvennoot.your knowledge partner

#### Plagiaatverklaring / Plagiarism Declaration

- Plagiaat is die oorneem en gebruik van die idees, materiaal en ander intellektuele eiendom van ander persone asof dit jou eie werk is.

Plagiarism is the use of ideas, material and other intellectual property of another's work and to present is as my own.

- 2 Ek erken dat die pleeg van plagiaat 'n strafbare oortreding is aangesien dit 'n vorm van diefstal is.

- I agree that plagiarism is a punishable offence because it constitutes theft.

- 3 Ek verstaan ook dat direkte vertalings plagiaat is.

I also understand that direct translations are plagiarism.

- Dienooreenkomstig is alle aanhalings en bydraes vanuit enige bron (ingesluit die internet) volledig verwys (erken). Ek erken dat die woordelikse aanhaal van teks sonder aanhalingstekens (selfs al word die bron volledig erken) plagiaat is.

Accordingly all quotations and contributions from any source whatsoever (including the internet) have been cited fully. I understand that the reproduction of text without quotation marks (even when the source is cited) is plagiarism.

- Ek verklaar dat die werk in hierdie skryfstuk vervat, behalwe waar anders aangedui, my eie oorspronklike werk is en dat ek dit nie vantevore in die geheel of gedeeltelik ingehandig het vir bepunting in hierdie module/werkstuk of 'n ander module/werkstuk nie.

- I declare that the work contained in this assignment, except where otherwise stated, is my original work and that I have not previously (in its entirety or in part) submitted it for grading in this module/assignment or another module/assignment.

Copyright © 2020 Stellenbosch University All rights reserved

## Abstract

# FPGA implementation of a network coding capable switch

D.B.B. de Villiers

Department of Electrical and Electronic Engineering, University of Stellenbosch, Private Bag X1, Matieland 7602, South Africa.

> Thesis: MEng (E&E) March 2020

The amount of internet connected devices is expected to increase dramatically in the near future. This is especially due to the widespread use of Internet of Things (IoT) devices. The Fifth-Generation (5G) of cellular network technologies aims to facilitate in the rapid expansion of IoT devices by providing an increased data rate, higher throughput, device capacity and connection reliability. In order for 5G to be fully integrated into existing telecommunication system, many new technologies are being developed.

Two technologies to help make 5G a reality are network coding and Software Defined Networking (SDN). Network coding is an alternative approach to traditional packet forwarding. Traditional packet-based networks use a "store-and-forward" approach, where intermediate nodes relay or replicate incoming information. Network coding provides an additional step and performs coding on the incoming data, known as "compute-and-forward".

SDN is another widely adopted network technology required for 5G. SDN segregates the traditional decentralized networking approach, into control and data processes. A software component is installed on each data forwarding device as the *dataplane*. The dataplane is the fast component of the network and is where all packet processing is conducted. The dataplane devices are controlled by centralised controller devices. The controllers have a "birds-eyeview" of the entire network and can therefore make more informed network processing decisions, compared to traditional networking.

Multiple software implementations of network coding have been developed and implemented. Network coding has been integrated into SDN in emulated and software environments. There exist many hardware devices that support SDN protocols such as OpenFlow. ABSTRACT iii

However, there are no commercially available network hardware devices that support network coding. Researchers in the field of computer networking have to modify existing devices to include network coding functions. Network hardware devices are often proprietary and therefore it is difficult to modify existing devices to add custom features and functions, such as network coding.

This thesis solves these problems by implementing a network coding capable switch in both a software and hardware based environment. The software based network coding functions are created as Virtual Network Functions (VNFs) that are deployed in an SDN environment as required. The hardware based network coding functionality is implemented using a Field Programmable Gate Array (FPGA) device. Both software and hardware implementations are integrated together using the OpenFlow based SDN bridge, Open vSwitch (OvS). The overall platform is designed to run on a general purpose PC and allows network coding to be evaluated in both physical and virtual network environments, with physical and Virtual Machine (VM) hosts.

The network coding implementations are evaluated using a real packet based network. The VNF based network encoder and decoder achieve a coding throughput of 164.67 and 87.99 Mbps respectively. The FPGA based network encoder and decoder are able to achieve a coding throughput of 223.16 and 496.40 Mbps respectively, providing a speedup of 1.36 and 5.71 over the VNF based implementations. The FPGA logic is run using a single PCIe lane and 50Mhz clock frequency. Taking full advantage of the FPGA device resource utilization, all four possible PCIe lanes and the maximum clock frequencies, the encoder and decoder functions could be implemented to achieve a coding throughput of 1.5 and 2.96 Gbps respectively.

The thesis demonstrates that FPGA based network coding is feasible and provides a significant performance increase over software based implementations. The performance however is reduced dramatically when integrated with a real packet based network. Future work should focus on optimising the integration between OvS and the network coding functions. This would hopefully alleviate any potential integration bottlenecks.

## Uittreksel

# FPGA implementering van 'n netwerk kodering bekwame skakelaar

("FPGA implementation of a network coding capable switch")

D.B.B. de Villiers

Departement Elektriese en Elektroniese Ingenieurswese, Universiteit van Stellenbosch, Privaatsak X1, Matieland 7602, Suid Afrika.

> Tesis: MIng (E&E) Maart 2020

Die hoeveelheid internetverbindende toestelle sal na verwagting in die nabye toekoms dramaties toeneem. Dit is veral te wyte aan die wydverspreide gebruik van Internet van Items (IvI) toestelle. Die vyfde generasie (5G) van sellulêre netwerktegnologieë is daarop gemik om die vinnige uitbreiding van IvI toestelle te vergemaklik deur 'n verhoogde datatempo, hoër deurvoer, toestelkapasiteit en verbindingsbetroubaarheid te bied. Ten einde 5G volledig in die bestaande telekommunikasiestelsel te laat integreer, word baie nuwe tegnologieë ontwikkel.

Twee tegnologieë om 5G 'n werklikheid te maak, is netwerkkodering en Sagteware Gedefinieerde netwerk (SGN). Netwerkkodering is 'n alternatiewe benadering tot tradisionele pakketversending. Tradisionele pakketgebaseerde netwerke gebruik 'n "winkel-en-vorentoe" benadering, waar tussenknope die inkomende inligting weergee of herhaal. Netwerkkodering bied 'n ekstra stap en voer kodering uit op die inkomende data, bekend as "bereken-en-vorentoe".

SGN is nog 'n algemene gebruikte netwerktegnologie wat benodig word vir 5G. SGN skei die tradisionele gedesentraliseerde netwerkbenadering in beheer en dataprosesse. 'n Sagteware komponent word op die data deurstuurtoestel geïnstalleer as die "dataplane". Die dataplane is die vinnige komponent van die netwerk en dit is waar al die pakkieverwerkings gedoen word. Die dataplane toestelle word beheer deur gesentraliseerde beheertoestelle. Die beheerders het 'n "voël-oog" van die hele netwerk en kan gevolglik meer ingeligte verwerkingsbesluite neem in vergelyking met tradisionele netwerking.

UITTREKSEL v

Verskeie sagtewareimplementering van netwerkkodering is ontwikkel en geimplementeer. Netwerkkodering is in die geëmuleerde en sagtewareomgewings in SGN geïntegreer. Daar bestaan baie hardeware toestelle wat SGN protokolle ondersteun, soos OpenFlow.

Daar is egter geen kommersiële beskikbare hardeware toestelle wat netwerkkodering ondersteun nie. Navorsers op die gebied van rekenaarnetwerke moet bestaande toestelle verander om netwerkkoderingsfunksies in te sluit. Netwerkhardeware toestelle is dikwels ontoegangklik en daarom is dit moeilik om bestaande toestelle te verander om gespesialiseerde funksies, soos netwerkkodering, by te voeg.

Hierdie tesis los hierdie probleme op deur 'n skakelaar met 'n netwerkkodering in 'n sagteware en hardeware omgewing te implementeer. Die sagteware gebaseerde netwerkkoderingsfunksies word geskep as Virtuele Netwerk Funksies (VNF's) wat na behoefte in 'n SGN omgewing ontplooi word. Die hardeware gebaseerde netwerk kodering funksionaliteit word geïmplementeer met behulp van 'n FPGA toestel. Beide sagteware en hardeware implementasies word saam geïntegreer met behulp van die OpenFlow gebaseerde SGN brug, Open vSwitch (OvS). Die algehele platform is ontwerp om op 'n algemene rekenaar te funksioneer en kan die netwerkkodering in beide fisiese en virtuele netwerkomgewings evalueer, met fisiese en Virtuele Masjiene (VM).

Die implementering van die netwerkkodering word geëvalueer met behulp van 'n ware pakket gebaseerde netwerk. Die VNF gebaseerde netwerkkodeerder en dekodeerder het 'n kodering van onderskeidelik 164.67 en 87.99 Mbps. Die FPGA gebaseerde netwerkkodeerder en dekodeerder kan 'n kodering van 223.16 en 496.40 Mbps onderskeidelik behaal, met 'n versnelling van 1.36 en 5.71 oor die VNF gebaseerde implementasies. Die FPGA logika word uitgevoer met behulp van 'n enkele PCIe baan en 50 MHz klokfrekwensie. Met die volle benutting van die FPGA hulpbronbenutting, al vier moontlike PCIe bane en die maksimum klokfrekwensies, kan die kodeerder en dekodeerfunksies geïmplementeer word om 'n kodering van onderskeidelik 1.5 en 2.96 Gbps te verkry.

Die tesis demonstreer dat FPGA gebaseerde netwerkkodering uitvoerbaar is en dat dit 'n beduidende toename in prestasie lewer ten opsigte van sagteware gebaseerde implementerings. Die werkverrigting word egter dramaties verminder as dit geïntegreer is in 'n werklike pakketgebaseerde netwerk. Toekomstige werk moet fokus op die optimalisering van die integrasie tussen OvS en die netwerkkoderingsfunksies. Dit sal hopelik die moontlike knelpunte vir integrasie verlig.

# Acknowledgements

I would like to express my sincere gratitude to the following people and organisations:

My supervisors, Prof. H.A Engelbrecht and Mr. A. Barnard, for their continuous support, encouragement, optimism and education throughout this thesis, as well as providing me with the necessary advice and feedback to complete successfully. I am privileged to have had the opportunity to work with and be mentored by both of you.

To my mother, Yolanda de Villiers for her continuous encouragement, and allowing me the opportunities to achieve my passions and goals. Without your support none of this would have been possible.

To my girlfriend, Christina Louw for her divine sense of humour and love. Thank you for standing by me though all the late nights and for always supporting me.

To my flatmates and friends in the MIH Media Lab, for all the good memories and encouragement throughout the last two years.

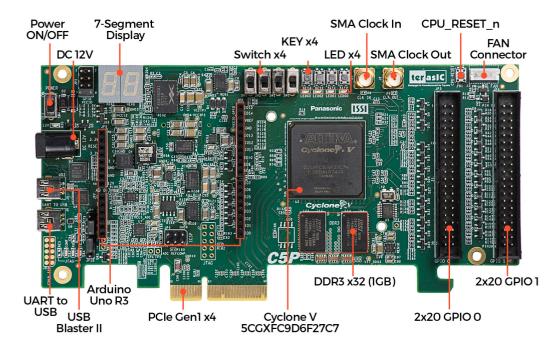

To the Department of Electrical and Electronic Engineering for providing me with a bursary for the past two years, as well as for funding the FPGA Open-VINO starter kits.

# Dedications

This thesis is dedicated to Christina.

# Contents

| $\mathbf{A}$ | bstra  | ct                                                             |

|--------------|--------|----------------------------------------------------------------|

| U            | ittrel | ksel                                                           |

| $\mathbf{A}$ | ckno   | wledgements                                                    |

| D            | edica  | tions                                                          |

| $\mathbf{C}$ | onter  | nts viii                                                       |

| Li           | st of  | Figures                                                        |

| Li           | st of  | Tables xiv                                                     |

| N            | omer   | nclature xvi                                                   |

| 1            | Intr   | roduction 1                                                    |

|              | 1.1    | Overview                                                       |

|              | 1.2    | Background                                                     |

|              | 1.3    | Problem statement                                              |

|              | 1.4    | Objectives                                                     |

|              | 1.5    | Research methodology                                           |

|              | 1.6    | Related work                                                   |

|              | 1.7    | Contributions                                                  |

|              | 1.8    | Thesis outline                                                 |

| <b>2</b>     | Lite   | erature Review 9                                               |

|              | 2.1    | Introduction                                                   |

|              | 2.2    | Sub-problems to address                                        |

|              | 2.3    | Traditional network switching                                  |

|              | 2.4    | Network coding                                                 |

|              | 2.5    | Software-based network coding                                  |

|              | 2.6    | Software-based network coding with SDN                         |

|              | 2.7    | Software-based network coding within a virtualization environ- |

|              |        | ment                                                           |

| CC | ONTE                                                     | NTS                                                     | ix        |  |  |  |

|----|----------------------------------------------------------|---------------------------------------------------------|-----------|--|--|--|

|    | 2.8                                                      | Hardware accelerated network coding                     |           |  |  |  |

|    | 2.9                                                      | Network coding switch functionality                     | 32        |  |  |  |

|    | 2.10                                                     | Summary                                                 | 35        |  |  |  |

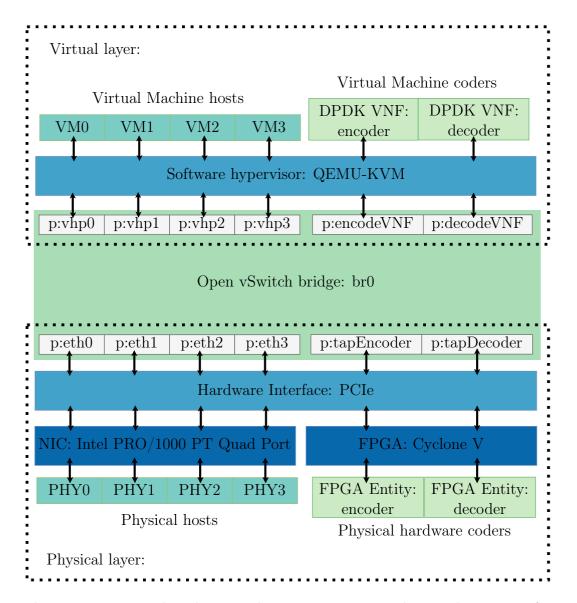

| 3  | Syst                                                     | tem architecture overview                               | 36        |  |  |  |

|    | 3.1                                                      | Introduction                                            | 36        |  |  |  |

|    | 3.2                                                      | System architecture                                     | 36        |  |  |  |

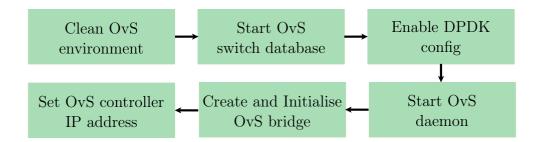

|    | 3.3                                                      | Bridge component: Open vSwitch                          | 38        |  |  |  |

|    | 3.4                                                      | Physical layer                                          | 41        |  |  |  |

|    | 3.5                                                      | Virtual layer                                           | 42        |  |  |  |

|    | 3.6                                                      | Summary                                                 | 42        |  |  |  |

| 4  | Net                                                      | work coding in the virtual layer: Virtual Network Func- |           |  |  |  |

|    | tion                                                     | $\mathbf{s}$                                            | <b>43</b> |  |  |  |

|    | 4.1                                                      | Introduction                                            | 43        |  |  |  |

|    | 4.2                                                      | Methodology                                             | 43        |  |  |  |

|    | 4.3                                                      | Component overview                                      | 44        |  |  |  |

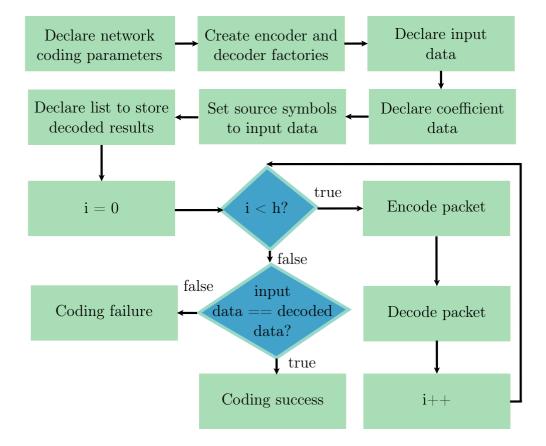

|    | 4.4                                                      | Kodo Python baseline                                    | 44        |  |  |  |

|    | 4.5                                                      | DPDK networking layer                                   | 47        |  |  |  |

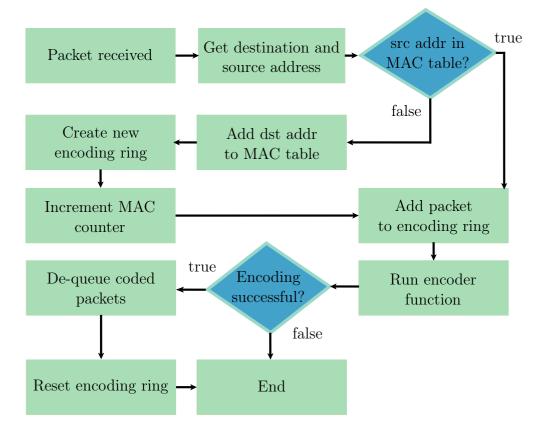

|    | 4.6                                                      | DPDK encoding pipeline                                  | 52        |  |  |  |

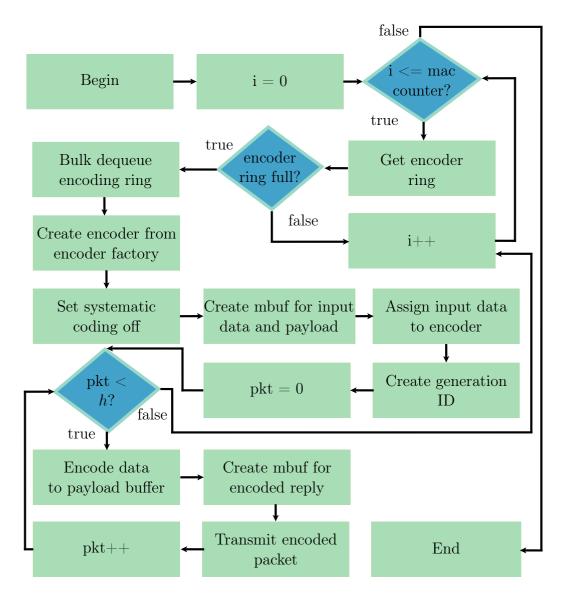

|    | 4.7                                                      | DPDK encoding function                                  | 56        |  |  |  |

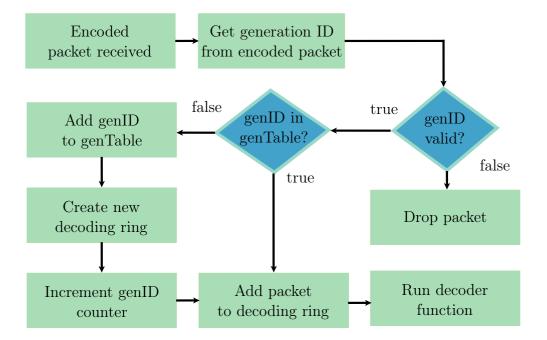

|    | 4.8                                                      | DPDK decoding pipeline                                  | 58        |  |  |  |

|    | 4.9                                                      | DPDK decoding function                                  | 60        |  |  |  |

|    | 4.10                                                     |                                                         | 61        |  |  |  |

| 5  | Network coding in the hardware layer: Field Programmable |                                                         |           |  |  |  |

|    |                                                          | e Array                                                 | 63        |  |  |  |

|    | 5.1                                                      | Introduction                                            | 63        |  |  |  |

|    | 5.2                                                      | Methodology                                             | 63        |  |  |  |

|    | 5.3                                                      | Implementation: network encoder                         | 64        |  |  |  |

|    | 5.4                                                      | Implementation: network decoder                         | 72        |  |  |  |

|    | 5.5                                                      | Module verification                                     | 80        |  |  |  |

|    | 5.6                                                      | Summary                                                 | 81        |  |  |  |

| 6  | One                                                      | en vSwitch and network coding function integration      | 82        |  |  |  |

| Ů  | 6.1                                                      | Introduction                                            | 82        |  |  |  |

|    | 6.2                                                      | Software layer integration: OvS and VNF                 |           |  |  |  |

|    | 6.3                                                      | Control plane: Ryu SDN controller                       | 84        |  |  |  |

|    | 6.4                                                      | Hardware layer integration: OvS and FPGA                |           |  |  |  |

|    | 6.5                                                      | Summary                                                 |           |  |  |  |

| 7  | Port                                                     | formance evaluation                                     | 102       |  |  |  |

| 1  | 7.1                                                      | Introduction                                            |           |  |  |  |

|    | 7.1 $7.2$                                                | Runtime analysis: network coding only                   |           |  |  |  |

|    | 1.4                                                      | rumme analysis, network coding only                     | 104       |  |  |  |

$\mathbf{x}$

|                        | 7.3                  | Network throughput, latency and packet delay variation 10 | 9  |

|------------------------|----------------------|-----------------------------------------------------------|----|

|                        | 7.4                  | FPGA resource utilization                                 |    |

|                        | 7.5                  | Maximum operating frequency                               | 0  |

|                        | 7.6                  | Summary                                                   |    |

| 8                      | Cor                  | nclusion 12                                               | 2  |

|                        | 8.1                  | Overview                                                  | 2  |

|                        | 8.2                  | Future work                                               |    |

| Bi                     | ibliog               | graphy 12                                                 | 6  |

| $\mathbf{A}$           | ppen                 | dices 13                                                  | 2  |

| $\mathbf{S}\mathbf{y}$ | sten                 | n setup 13                                                | 3  |

|                        | Netv                 | work configuration scripts outputs                        | 3  |

|                        | Phy                  | sical network setup                                       | 8  |

| K                      |                      | Python baseline 13                                        |    |

|                        | Kod                  | o Python code                                             | 9  |

| $\mathbf{R}$           | aw R                 | LNC data values                                           | .3 |

|                        | Sour                 | rce, un-coded data                                        | 4  |

|                        | $\operatorname{Cod}$ | ing coefficient data                                      | 5  |

|                        | Ence                 | oded data                                                 | 6  |

|                        | Dece                 | oded data                                                 | 6  |

| $\mathbf{R}$           | LNC                  | VNF GitHub project 14                                     | 7  |

|                        | VNI                  | F DPDK networking setup script                            | 8  |

| $\mathbf{R}$           | esult                | s 15                                                      | 0  |

| Sc                     |                      | test scripts 15                                           | _  |

|                        | Scap                 | by packet generator                                       | 3  |

|                        | Scap                 | by pcap analyzer                                          | 7  |

# List of Figures

| 1.1  | Butterfly network                                              | 2 |

|------|----------------------------------------------------------------|---|

| 2.1  | OSI networking layer model                                     | 1 |

| 2.2  | Ethernet packet format                                         | 2 |

| 2.3  | Unicast vs Multicast                                           | 3 |

| 2.4  | IGMPv2 packet format                                           | 4 |

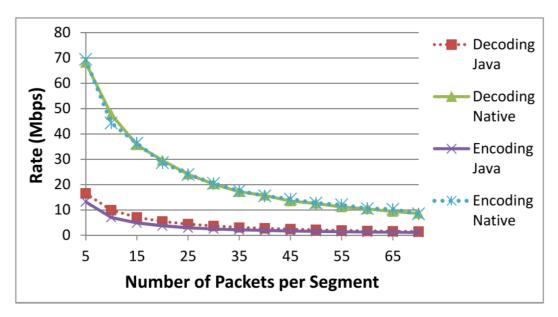

| 2.5  | MicroCast network coding throughput rates                      | 1 |

| 2.6  | Linux networking layer model                                   | 5 |

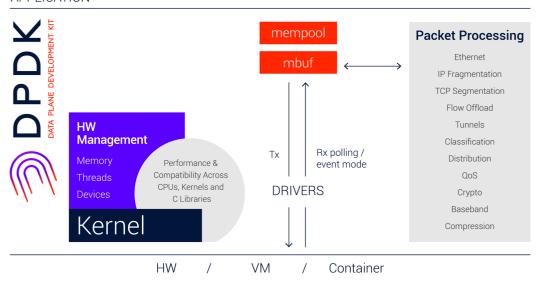

| 2.7  | DPDK overview diagram                                          | 7 |

| 2.8  | OpenVINO Starter Kit                                           | 1 |

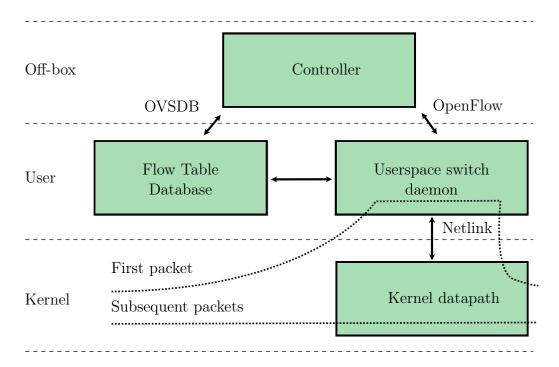

| 2.9  | Open vSwitch component diagram                                 | 3 |

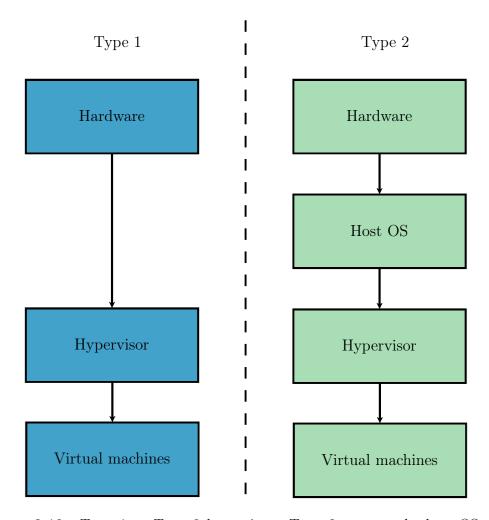

| 2.10 | Type 1 vs Type 2 hypervisor                                    | 4 |

| 3.1  | Network coding switch system overview                          | 7 |

| 3.2  | Open vSwitch and DPDK setup script flow diagram                | ) |

| 4.1  | Python RLNC implementation flow diagram                        |   |

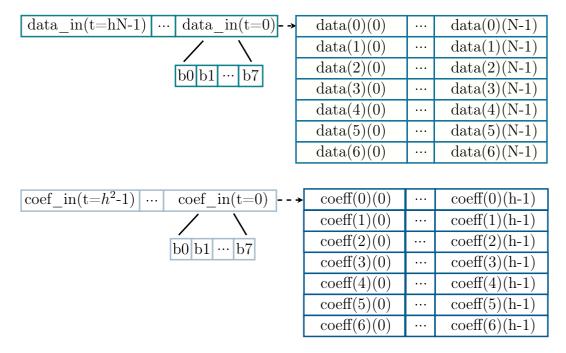

| 4.2  | Kodo input data format                                         |   |

| 4.3  | Kodo coding coefficient data format                            |   |

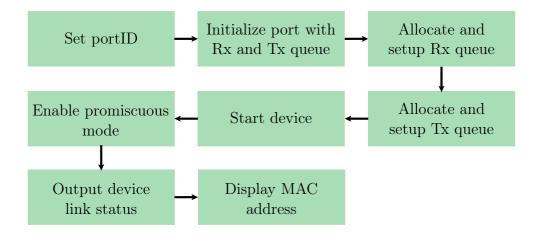

| 4.4  | DPDK Ethernet interface configuration procedure 48             |   |

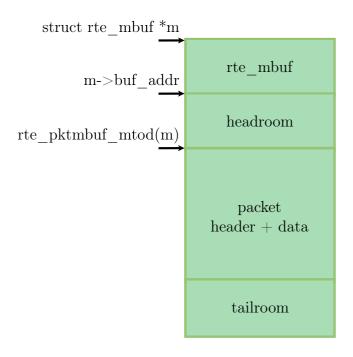

| 4.5  | DPDK memory buffer layout                                      | 9 |

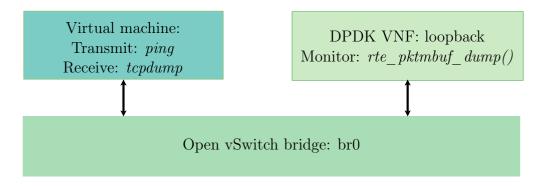

| 4.6  | Setup used to verify DPDK networking loopback function 50      | ) |

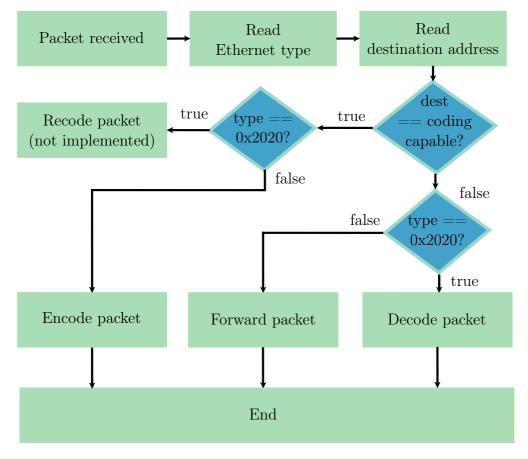

| 4.7  | Selection process used by DPDK application to determine coding |   |

|      | operations                                                     |   |

| 4.8  | DPDK encoding pipeline flow diagram                            | 4 |

| 4.9  | DPDK encoder function flow diagram 5                           |   |

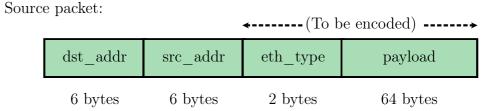

| 4.10 | Source and encoded packet formats                              | 3 |

| 4.11 | DPDK decoding pipeline flow diagram                            | 9 |

| 4.12 | DPDK decoder function flow diagram 6                           | 1 |

| 5.1  | Hardware encoder flow diagram                                  |   |

| 5.2  | Hardware encoder entity: input FIFO buffer 6                   |   |

| 5.3  | Hardware encoder input FIFO read and write FSMs 68             | 3 |

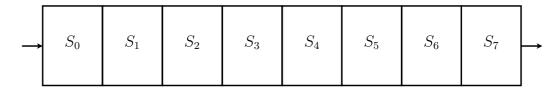

| 5.4  | 8-bit shift register                                           | 9 |

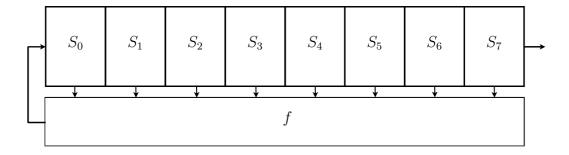

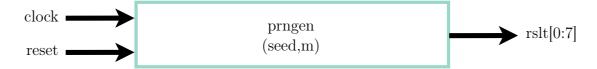

| 5.5  | 8-bit linear-feedback shift register                           | 9 |

| LIST                                 | OF FIGURES xii                                                              |

|--------------------------------------|-----------------------------------------------------------------------------|

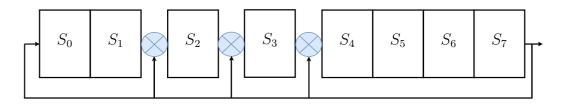

| 5.11<br>5.12<br>5.13<br>5.14<br>5.15 | 8-bit Galois linear-feedback shift register                                 |

| 6.12                                 | IGMP snooping functionality flow diagram from OvS bridge                    |

| 7.1<br>7.2<br>7.3                    | Coding runtime timing values                                                |

| 1<br>2<br>3<br>4<br>5                | Screenshot of output from OvS-DPDK networking setup script setup_ovsdpdk.sh |

| 6<br>7                               | File structure of the <i>RLNC_VNF</i> GitHub project                        |

| 8                                    | FPGA encoder signal tap result                                              |

### Stellenbosch University https://scholar.sun.ac.za

| LIST | OF FIGURES                     | xiii |

|------|--------------------------------|------|

| 9    | FPGA decoder signal tap result | 152  |

# List of Tables

| 3.1<br>3.2        | OvS Bridge port configuration: br0                                                                                                                                                     |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1<br>4.2<br>4.3 | Kodo-C network coding functions: general55Kodo-C network coding functions: encoder55Kodo-C network coding functions: decoder60                                                         |

| 6.1<br>6.2<br>6.3 | Avalon Memory-Mapped Master read template signals 93<br>Avalon Memory-Mapped Master write template signals 94<br>Summary of Terasic PCIe library functions used to interface userspace |

|                   | software application with OpenVino starter kit                                                                                                                                         |

| 7.1<br>7.2        | Timing values for the encoder and decoder VNF coding functions $105$ Runtime, throughput and loading overhead for the encoder and                                                      |

| 7.3               | decoder VNF coding functions                                                                                                                                                           |

| 7.4               | Runtime, throughput and loading overhead for the encoder and decoder FPGA coding functions                                                                                             |

| 7.5               | Throughput, latency and jitter results for VNF-based coding function in PHY to PHY test                                                                                                |

| 7.6               | Throughput, latency and jitter results for VNF-based coding function in VM to VM test                                                                                                  |

| 7.7               | Throughput, latency and jitter results for FPGA-based coding function in PHY to PHY test                                                                                               |

| 7.8               | Throughput, latency and jitter results for FPGA-based coding function in VM to VM test                                                                                                 |

| 7.9               | Overall network, input, output and in-between throughputs for VNF coders end-to-end tests                                                                                              |

| 7.10              | Overall network, input, output and in-between throughputs for                                                                                                                          |

| 7.11              | FPGA coders end-to-end tests                                                                                                                                                           |

|                   | Throughput performance reduction for FPGA coders                                                                                                                                       |

|                   | Encoder resource utilization cumulative summary                                                                                                                                        |

|                   | Decoder resource utilization cumulative summary                                                                                                                                        |

|                   |                                                                                                                                                                                        |

| LIST | T OF TABLES                                                   | xv  |

|------|---------------------------------------------------------------|-----|

| 7.15 | Maximum operating frequencies of FPGA encoder and decoder im- |     |

|      | plementations                                                 | 120 |

# Nomenclature

#### Acronyms

Fourth Generation Cellular Network Technology

Fifth Generation Cellular Network Technology

ACK Acknowledgement

ALM Adaptive Logic Module ALU Arithmetic Logic Units

API Application Programming Interface

ARP Address Resolution Protocol

BAR Base Address Register

CPU Central Processing Unit

CRC Cyclic Redundancy Checksum

CUDA Computer Unified Device Architecture

DLR Dedicated Logic Registers

DMA Direct Memory Access

DPDK Data Plane Development Kit FEC Forward-Error Correction

FIFO First-in, first-out

FOSS Free and Open Source Software FPGA Field Programmable Gate Array

FSM Finite State Machine

GPU Graphics Processing Unit

HDL Hardware Descriptive Language

IGMP Internet Group Management Protocol

IP Core Intellectual Property Core

IP Internet Protocol

IaaS Infrastructure as a Service

IoT Internet of Things

KVM Kernal-based Virtual Machine

LAN Local Area Network

*NOMENCLATURE* xvii

LCM Linear Code Multicast

LFSR Linear-Feedback Shift Register

MAC Media Address Control

**MPLS** Multiprotocol Label Switching MTU Maximum Transmission Unit NFV Network Function Virtualization

Network Interface Card NIC

OSI Open Systems Interconnection

OS Operating System OvS Open Virtual Switch

P<sub>2</sub>P Peer-to-Peer

**PCIe** Peripheral Component Interconnect Express

PCPersonal Computer PDM Poll Mode Driver

PHY Physical host

PIO Parallel Input/Output

**QEMU** Quick Emulator

RAM Random Access Memory

RLNC Random Linear Network Coding

RTT Round Time Trip

SDKSoftware Development Kit SDN Software Defined Networking

SR-IOV Single-Root Input/Output Virtualization

TCP Transmission Control Protocol TLB Translation Lookaside Buffer UDP User Datagram Protocol

VHDL Very-High-Speed Integrated Circuit Hardware Description

Language

VMVirtual Machine

Virtual Network Function VNF Wireless Mesh Networks WMN

XOR Exclusive-or

#### Variables

Galois field size mGeneration size hGAcyclic graph

NOMENCLATURE xviii

| V | Graph vertices |

|---|----------------|

| E | Graph edges    |

| S | Senders        |

| R | Receivers      |

|   |                |

N Data packet length

$egin{array}{lll} oldsymbol{x_i} & & ext{Source vector} \\ x_i & & ext{Source symbol} \\ oldsymbol{X} & & ext{Source matrix} \\ e & & ext{Single graph edge} \\ \end{array}$

$g_i(e)$  Coding coefficient symbol

$egin{array}{ll} egin{array}{ll} egin{array}{ll} g(e) & & ext{Global coding vector} \ G_t & & ext{Coefficient matrix} \end{array}$

y(e) Encoded output symbol  $y(e_i)$  Encoded output vector y(e) Encoded output matrix  $h \times h$  Identity matrix

l Number of 32-bit data segments

k Coefficient data length for each packet

$t_{coding}$  Overall coding runtime  $T_{coding}$  Overall coding throughput

$T_{network}$  Network throughput  $t_{latency}$  Network latency

PDV Network packet delay variation

#### Units

Mbps Megabits per second

$\begin{array}{ccc} \text{KB} & \text{Kilobytes} \\ \text{MB} & \text{Megabytes} \\ \text{GB} & \text{Gigabytes} \\ \text{Mhz} & \text{Megahertz} \\ \text{Ghz} & \text{Gigahertz} \\ \mu \text{s} & \text{Microseconds} \\ \end{array}$

# Chapter 1

# Introduction

#### 1.1 Overview

The objective of this thesis is to design and implement a network switch with the capability of performing network coding, in a real packet-based network. The switch requires the ability to offload packet data to both software and hardware-based packet processors. We begin the discussion by outlining the various technologies explored before moving onto addressing the problems and need for the network switch. Once the problems are understood, we derive objectives to address the problems. We look at past work that is related to the thesis and list the contributions made by our work, in comparison.

### 1.2 Background

The amount of internet connected devices is expected to increase dramatically in the near future. This is especially due to the widespread use of Internet of Things (IoT) devices. The Fifth-Generation (5G) of cellular network technology aims to provide an increased data rate, higher throughput, device capacity and connection reliability. Specifically, 5G will enable the rapid expansion of IoT technologies. Unlike previous cellular network technology generations, 5G is consider to be a "revolution" rather than a generational upgrade as with Fourth-Generation (4G). There are a number of technological challenges that exist in order for 5G to be fully integrated into existing telecommunication systems. In response, many technologies are being engineered [1]. One of these technologies is network coding.

Network coding is an alternative approach to traditional packet forwarding. Traditional packet-based networks work on a "store-and-forward" basis, where intermediate nodes relay or replicate incoming information. Network coding provides an additional step and performs coding on the incoming data, as a "compute-and-forward" paradigm. The idea that information should not only be stored at intermediate nodes, but coding could also be performed originates

from Ashlswede et al. in [2]. Network coding has shown to improve throughput and redundancy in various applications, such as multicast streaming [3].

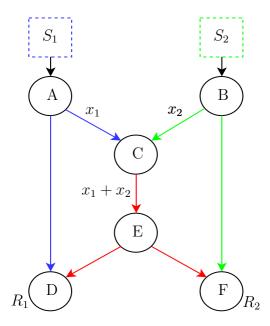

The principle example of network coding is explained using the *butterfly* network, taken from Fragouli and Soljanin in [4]. The butterfly network, in Fig. 1.1 consists of two sources  $S_1$  and  $S_2$ , and two receivers  $R_1$  and  $R_2$ . If  $R_1$  requests data from both  $S_1$  and  $S_2$ , then it will be able to receive from both. This is also the case when  $R_2$  is receiving data from both sources. When both sources send data to both receivers simultaneously, then there is congestion at the edge CE. More specifically, consider if  $S_1$  wants to send bit  $x_1$  to  $R_2$  simultaneously, while  $S_2$  sends bit  $x_2$  to  $R_1$ . In traditional information flow only one bit can be sent at a time. The other bit waits to be transmitted. In network coding however, the intermediate node C is able to combine both bits into a third packet  $x_1 + x_2$ . At the receiving end, each receiver can solve a simple system of linear equations and obtain  $x_1$  and  $x_2$ .

**Figure 1.1:** Butterfly network topology of two sources  $S_1$  and  $S_2$ , and two receivers  $R_1$  and  $R_2$ . Network coding advantage is obtained by combining bits  $x_1$  and  $x_2$  at the intermediate node C.

The first practical implementation of network coding is shown by Chou et al. [5]. A packet format is presented that enables network coding to be used in practical packet-based networks. Chou et al. also introduces the idea of grouping packets into a *generation*. The coding operations are then performed on the generation itself.

The most adopted form of network coding used in practical implementations is Random Linear Network Coding (RLNC). In RLNC, intermediate

nodes select random coding coefficients independently. This allows the receiver to decode after obtaining sufficient independent linear combinations.

Examples of RLNC software libraries that can be used in practise are: NCUtils [6],  $Random\ Linear\ Network\ Coding\ Library$  [7] and Kodo [8]. The Kodo project by Steinwurf is the most mature and widely adopted in literature. Kodo provides a large variety of network coding algorithms and functions. Kodo's functions are written in C++ and provide wrappers for other programming languages such as C and Python. While network coding libraries such as Kodo exist, there is currently no commercial network switch that implements network coding.

According to [1], another widely adopted technology required for 5G is Software Defined Networking (SDN). Traditional networking is not flexible at a large scale. Network devices are difficult to configure and manage on an individual basis. This becomes problematic when network topologies need to be upgraded or modified. It is complicated to service these networks and as a result downtime can occur.

SDN aims to solve the difficulties of traditional networking by segregating networks into control and data processes [9]. A software component is installed on each data forwarding device as the *dataplane*. The dataplane is the fast component of the network and is where all the packet processing is conducted. Control of the network is centralised using one or more controller devices. The controllers have a "birds-eye-view" of the entire network. Network control applications are run on the controllers to characterise how the data is processed in the dataplane. The controller has direct control over the dataplane through an Application Programming Interface (API). OpenFlow is currently the most widely adopted API for SDN.

An OpenFlow device uses flow tables that dictate the actions to perform on each incoming packet [10]. Unknown packets received by a dataplane device are sent to the controller. The controller determines the appropriate actions and updates the flow table on the dataplane device. This creates a rule and future packets do not need to be sent to the controller. This provides a more dynamic approach to network management. Projects such as OpenFlow enable SDN to provide easier deployment and integration of networking technologies. SDN can be used to integrate network coding operations within a network by adding the appropriate OpenFlow flows to an SDN compatible network switch.

SDN integrates well with Network Function Virtualization (NFV). Following along the direction of computer servers, computer network functionality is also being virtualized. NFV or Virtual Network Functions (VNFs) are a recently introduced trend in computer network communication systems [1]. NFV tries to move away from using dedicated networking hardware. VNFs are usually created within Virtual Machines (VMs) that run in a hypervisor environment. Therefore a server with Network Interface Cards (NICs) can be used to deploy multiple network functions. Examples of such network functions are switches, routers, gateways, firewalls and forward-error-correction coders.

A SDN-based network can assign these network functions as required. Network coding can be implemented within a VNF to be deployed in a SDN-based network.

A fast packet processing library that can be used to create VNFs is Intel's Data Plane Development Kit (DPDK) [11]. The Linux operating system provides a great amount of flexibility for packet processing. The problem however, is that there is much overhead built into the default network stack. DPDK aims to solve this by making use of Poll Mode Drivers (PMDs) to allow for network function development in the userspace. PMDs are a type of "kernel bypass" that allow for packet processing without using the default Linux networking stack. DPDK has shown a large amount of performance increases in practical network use. An example of this is the widely adopted integration with Open vSwitch (OvS) [12].

OvS is a open source virtual switch that uses OpenFlow to provide SDN capability [13]. OvS can be installed on many different Operation Systems (OS), including Linux. Therefore, OvS can be run on a general purpose desktop or server computer. Both virtual and physical network space can be utilised by adding networking or processing hardware to the computer. Examples of such hardware are NICs and accelerators. The Peripheral Component Interconnect Express (PCIe) interface is one way of connecting additional hardware to the computer.

PCIe can be used to connect hardware such as an Field Programmable Gate Array (FPGA). FPGAs are Integrated Circuit (IC) devices that can be configured to implement digital logic-based circuits. Therefore, many different packet processing circuits can be developed to run on FPGAs. FPGAs provide the ability to run multiple parallel circuits at once and can provide increased performance over software-based algorithms. Therefore FPGA's can be interfaced through PCIe, with a computer running OvS in order to accelerate the RLNC algorithm.

#### 1.3 Problem statement

Multiple software implementations of network coding have been developed and implemented. Network coding has been integrated into SDN in emulated and software environments. There exist many hardware devices that support SDN protocols such as OpenFlow.

However, there are no commercially available network hardware devices that support network coding. Researchers in the field of computer networking cannot go and buy an "off-the-shelf" network switch in order to evaluate network coding in a practical network. This leads researchers to have to modify existing devices to include network coding functions.

Hardware devices are often proprietary. While this is well justified in the commercial industry, it becomes problematic in research. It is difficult to

modify existing network devices to add custom features and functions, such as network coding.

This thesis solves these two problems by providing an easily modifiable hardware-accelerated network coding switch platform. The switch can be used to evaluate network coding in a real, packet-based network. This allows for further research to be conducted regarding network coding itself. Researchers do not have to focus on the implementation of network coding, but rather the use cases.

### 1.4 Objectives

The aim of this project is to create a flexible network switch platform, in order to evaluate network coding in a real packet-based network. Network coding functions are implemented in a hardware and software environment. This is achieved through the following objectives:

- 1. Design and implement a network coding capable switch in a software-based environment. The software implementation serves as a baseline for comparison with the hardware coders. The software implementation also allows for network coding to be used in a virtualization environment. Network coding can be deployed as a VNF and in an Infrastructure as a Service (IaaS) environment.

- 2. Design and implement a network coding capable switch with the capability of offloading network traffic to an FPGA to assist in packet processing acceleration.

- 3. Evaluate the runtime, throughput, latency and jitter performance of both the software and hardware network coding switch implementations, in a real packet-based network.

- 4. Maintain the philosophy of open networking by using techniques of SDN and NFV where possible, to provide a flexible and expandable solution. Following the current trend of modern networking enables this thesis to remain relevant for any future work.

### 1.5 Research methodology

The design and implementation of a network coding capable switch, should allow for easier configuration and study of network coding algorithms. In addition, the use of hardware-based acceleration should also increase the performance of network coding implementations in practical packet-based networks. These assumptions are validated through the following research methodology:

- 1. Designing and implementing virtual, software-based network coding functions to establish a baseline set of performance metrics (runtime, throughput, latency and jitter).

- 2. Designing and implementing FPGA-based, hardware network coding functions to evaluate the feasibility and performance of hardware-based network coding.

- 3. Designing and implementing suitable methods to interface both software and hardware coding functions together within a real packet-based network.

- 4. Creating a suitable set of testing procedures to accurately compare both software and hardware-based network coding implementations.

- 5. Performing the set of testing procedures using both software and hardware-based implementations and evaluating the results in comparison.

- 6. Outlining the benefits and weaknesses of both software and hardware-based implementations, and deriving suitable conclusions regarding both approaches.

#### 1.6 Related work

Previous work to implement network coding in practical network systems using either SDN or FPGAs are done by [14], [1] and [15]. These works of literature are referenced and expanded upon throughout this thesis.

# 1.6.1 Kim, et al. Design and evaluation of random linear network coding accelerators on FPGAs

Kim, et al. implements FPGA-based RLNC decoder logic in [14]. Two different decoder designs are presented that take advantage of the parallel computation ability of FPGAs. The designs are synthesized using a Xilinx Virtex 5 FPGA. A maximum throughput of 64.98 Mbps is obtained by the decoder implementation, providing speedup of 13.84 compared to software implementations.

The designs make use of ModelSim to simulate the hardware implementation, and do not implement the decoders in a real packet-based network. The work also only implements a RLNC decoder and not an encoder. This thesis expands on the work by Kim, et al. by providing the design for both an FPGA-based RLNC encoder and decoder as well as integration into a real packet-based network. The decoder implementation is this thesis achieves a coding throughput of 378.86 Mbps, a speedup of 5.83 over the implementation in [14].

# 1.6.2 Hansen, et al. Network coded software defined networking: Enabling 5G transmission and storage networks

Hansen, et al. [1] emphasizes the importance of network coding with SDN for 5G technologies, by implementing an integration between OpenFlow and Kodo. The article discusses the problem of adding network coding capability to existing routers and switches. A solution is provided by implementing the coding functions on a VM as a VNF. The OvS bridge is used to direct traffic flow to the coder VM as required.

This thesis expands on the work of [1] by integrating hardware-based (FPGA) network coding functions into an SDN and OvS environment, along-side VNF-based network coding functions. The VNFs are implemented using the DPDK packet processing library.

# 1.6.3 Gabriel, et al. Practical deployment of network coding for real-time applications in 5G networks

The conference paper by the Gabriel, et al. [15] demonstrates a practical deployment of RLNC VNFs within an SDN environment to improve video streaming quality due to congestion based packet loss. The demonstrator presented makes use of off-the-shelf hardware and the OpenStack SDN environment. The RLNC functions are implemented using the Kodo library.

The work focuses on the setup and implementation of the integrated system, and does not provide network performance results. This thesis expands on the work of [15] by implementing the VNFs using the DPDK library and adding FPGA-based network coding functions to the SDN environment. Practical results are given based on the implementation, to provide indication of the strengths and limitations of implementing network coding in a SDN environment.

#### 1.7 Contributions

The following contributions are made through this thesis:

- An FPGA network coding encoder and decoder is developed that can be used within a practical SDN network. This thesis presents FPGA logic for a RLNC encoder which has not yet been shown in literature. The thesis also showcases the design and implementation of integrating FPGA network coding encoder and decoder functions with the OvS OpenFlow SDN switch, and therefore a real packet-based network.

- A VNF-based network encoder and decoder that are implemented using the DPDK software library.

- A holistic research platform to evaluate network coding in a real packetbased network, using both physical and virtual networking spaces. The networking functions are integrated with OvS within an SDN environment.

- A network coding selection scheme to determine when to perform network coding in a real packet-based network.

- An SDN controller program design to implement multicast snooping within an SDN environment.

#### 1.8 Thesis outline

- Chapter 2 provides a literature review to further expand on the concepts covered in this introduction. Previous related work is discussed. The chapter intends to inform the reader of current trends in computer networking, and provide the knowledge required for understanding the rest of the thesis.

- Chapter 3 provides a system overview of the network switch. Due to the various components and interfaces of the system, a system diagram is created. This provides a visual aid in understanding the overall system architecture. Each component is introduced and discussed.

- Chapter 4 discusses the software implementation of network coding functions. The specifics of how DPDK is used to create an encoder and decoder VM-based VNFs are described.

- Chapter 5 discusses the hardware implementation of network coding functions. The details of how the RLNC algorithm is implemented in FPGA hardware are given. The chapter provides information on the methodology, architecture, implementation and evaluation of the coders.

- Chapter 6 describes how the software and hardware implementations are interfaced with the OvS bridge. Details regarding the control plane operations are provided.

- Chapter 7 describes the experimental evaluation of the various components. The software and hardware implementations are tested and compared. The results are discussed and the overall system is evaluated.

- Chapter 8 provide conclusions and recommendations regarding the thesis.

# Chapter 2

# Literature Review

#### 2.1 Introduction

The previous chapter introduces the concepts of network coding, SDN, NFV and FPGAs. In this chapter, we continue the discussion further by outlining the various sub-problems to address. Specifically, the requirements for a software and hardware platform, and network coding switch functionality are scoped. After outlining the sub-problems, we proceed into the various networking technologies to address the specified sub-problems. The literature review is used to study past work relevant to the design and development of a network coding capable switch.

### 2.2 Sub-problems to address

To design and develop a network coding switch to meet the thesis objectives from section 1.4, we begin the discussion with the various sub-problems that need to be addressed. This chapter reviews past literature to find a solution to the following:

### 2.2.1 Software platform for a network coding switch

A software-based network coding implementation is required to serve as a baseline for comparing and implementing hardware-based network coding. The software-based network coding implementation has the following requirements:

- 1. The software-based implementation must be able to use the RLNC algorithm.

- 2. The software-based network coding implementation must be SDN compatible and be used in a real packet based network.

3. The software-based network coding implementation must be deployable in a virtualization environment.

#### 2.2.2 Hardware platform for a network coding switch

A suitable hardware platform is required to perform network coding. The hardware-based implementation has the following requirements:

- 1. The hardware implementation must be able to use the RLNC algorithm.

- 2. The hardware implementation must be able to integrate with an SDN environment to be used in a real packet-based network. Specifically, the switch must be able to run an SDN dataplane protocol (such as Open-Flow) and be able to communicate and interface with an SDN controller in the controlplane.

#### 2.2.3 Network coding switch functionality

In addition to the software and hardware-based network coding implementations, the network switch also requires the following functionality:

- 1. The network switch must perform the basic switching function of forwarding networking packets.

- 2. The network switch must be SDN compatible.

- 3. The network switch must have the ability to offload network traffic to both the software and hardware-based network coding implementations.

- 4. The network switch must be able to function in both a physical and virtual network environment.

- 5. The network switch must be able to perform multicast snooping to be used in multicast streaming applications.

We begin the literature discussion with the traditional approach to network switching within a packet-based network. We then provide more details on network coding before moving onto discussing suitable platforms for the software and hardware-based network coding implementations. We conclude the literature review by evaluating the network coding switch functionality requirements.

### 2.3 Traditional network switching

The definition of traditional networking is not necessarily clear. In fact, neither is the definition of the adjective itself. In the context of this thesis however, traditional networking refers to computer networking concepts that are not part of an SDN ecosystem. More specifically, traditional networking refers to computer network systems where the data and control plane do not have a clear structural boundary. These networks are often, but not necessarily, decentralised.

The concepts of traditional networking form the basis of SDN techniques. Therefore this section is necessary to understand implementations regarding SDN and VNF. The explanations derive from [16], unless cited otherwise. The first concept is to understand how computer networks are structured.

Computer networks are divided into different layers. These layers resemble programming interfaces or libraries. There are many different models describing networking layers. The most popular is provided by the Open Systems Interconnection (OSI) project. The OSI attempts to establish networking standards by providing a seven layer model. A diagram depicting the various OSI layers is shown in Fig. 2.1. The layers of OSI are: physical, data link, network, transport, session, presentation and application.

| Layers           | Protocols                     |

|------------------|-------------------------------|

| L7: Application  | HTTP, FTP, SSH and DNS        |

| L6: Presentation | ASCII, JPEG and GIF           |

| L5: Session      | API's and Sockets             |

| L 4: Transport   | TCP and UDP                   |

| L3: Network      | IPv4, IPv6, ICMP and IGMP     |

| L2: Data link    | MAC, LLC and PPP              |

| L1: Physical     | WiFi, RJ45, USB and Bluetooth |

**Figure 2.1:** OSI networking layer model with examples of protocols that belong to each layer.

The OSI layer of most importance within this thesis is the data link layer, or the L2 layer. The data link layer is responsible for node-to-node transfer and includes Local Area Network (LAN) communication. LANs are essentially

serial lines used to interface between network hardware. The most common LAN protocol: Ethernet, was originally developed in 1976 and became popular due to its low cost and ease of use.

#### 2.3.1 Ethernet LAN protocol

An Ethernet network groups information bits into buffers of data called packets. Packets allow devices within a network to communicate. Packets often have a preceding sequence of bits called a header. The header provides the necessary information to transfer a packet through a network. The packet data that is required by the application layers is the payload.

In a computer, the Ethernet LAN protocol assigns each network interface a unique six byte hardware address. This address is known as the Media Access Control (MAC) address. Each network interface monitors for arriving packets containing a destination address equal to the device MAC address. If the packet matches, the interface forwards the packet to the CPU to be processed.

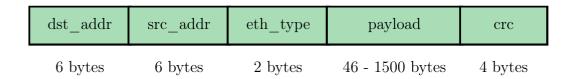

The Ethernet packet frame format is shown in Fig. 2.2. The packet traverses through the network from the source address  $src\_addr$  to the destination address  $dst\_addr$ . The Ethernet type  $eth\_type$  field provides information regarding the protocol that is used by the payload. The payload is the actual data that needs to be transmitted by the packet. The payload is not part of the Ethernet header. The Cyclic Redundancy Checksum (CRC) crc field is an error-correcting code used to detect any data changes that occurred during transmission.

**Figure 2.2:** Ethernet packet format containing: destination address  $dst\_addr$ , source address  $src\_addr$ , Ethernet type  $eth\_type$ , data payload and cyclic redundancy checksum crc.

#### 2.3.2 Ethernet switch

Ethernet networks are connected together using switches. An Ethernet switch is a L2 networking device that functions on the MAC layer. These devices forward packets between multiple Ethernet interfaces within a network.

Ethernet switches forward packets using forwarding or MAC tables. A forwarding table is a lookup table with two primary fields: destination address and next hop output port. When an Ethernet packet is received by the

switch, a lookup is performed based on the destination address. The packet is forwarded to the correct device connected to the next hop port.

To begin forwarding packets, switches first need to establish the correct forwarding table. A learning process is used to populate the forwarding table from empty. The switch learns where each destination is through the use of fallback-to-flooding. If a packet is received and the destination is unknown, the packet is forwarded through each output port. The switch floods the packet to each port. At the same time, the switch stores the source address of the received packet in the forwarding table. The source address is stored along with the port where the packet arrived, therefore creating an entry in the forwarding table. Future incoming packet destination addresses are compared to the forwarding table. If the address matches, then the switch does not flood the network, but rather forwards it to the correct interface.

#### 2.3.3 Multicast

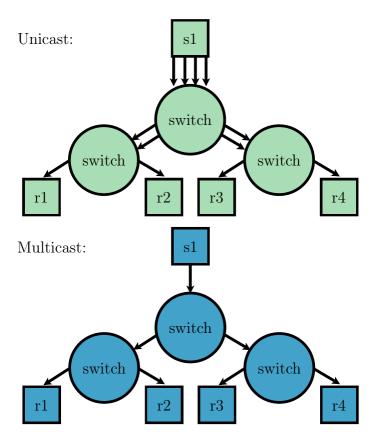

Figure 2.3: Unicast vs multicast streaming packet flows. The advantage of multicast is illustrated showing a reduced number of packet streams.

In an Ethernet network, packets are either transmitted via unicast, broadcast, or multicast. Unicast is traffic sent to a specific host, while broadcast and multicast send traffic to the whole network or a set of hosts respectively. Multicast is of particular interest in video streaming applications, where multiple users request the same data from the server simultaneously.

The advantage of multicast is demonstrated in Fig. 2.3. The example illustrates a source s1 sending data to four separate receivers r1, r2, r3 and r4. In a unicast network a separate packet is created with the destination address set to each receiver. Four packets with exactly the same payload, but different headers are transmitted. These packets are then forwarded through the network until they reach the receivers. In the multicast network however, the sender only creates one packet and therefore reduces the overall network traffic.

Multicast reduces network traffic by using group addresses. Multiple users or *subscribers* are able to receive data packets from a single source address within the multicast group. Multicast uses a unique MAC address format to distinguish from unicast Ethernet frames. A value of 1 for the least-significant bit in the first byte of the Ethernet MAC address indicates if the address is multicast.

While multicast can be done on a L2 layer, L3 or IP-based multicast is often preferred. By default, L2 switches cannot determine the location of multicast group members. As a result, switches will broadcast multicast packets instead. To avoid broadcast, switches can use what is known as *snooping*.

A popular protocol for IP-based multicast that enables L2 switch snooping is the Internet Group Management Protocol (IGMP). There are three versions of IGMP, namely IGMPv1, IGMPv2 and IGMPv3. The most widely used is IGMPv2, which is documented in the RFC-2236 standard [17]. The IGMPv2 protocol is used in this thesis and hereby referred to as IGMP.

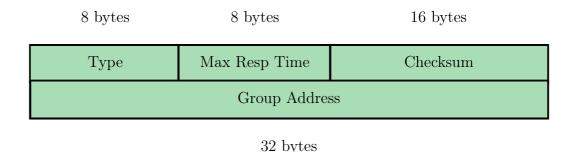

**Figure 2.4:** IGMPv2 packet format containing: message type, maximum allowed response time to respond to membership query, checksum and multicast group address.

Hosts in a network use IGMP messages to report their membership status to

neighbouring multicast routers. An IGMP packet has the format given in Fig. 2.4. The types of IGMP messages are membership query (0x11), membership report (0x16) and group leave (0x17). The maximum response time max resp time field is only used by the membership query and is the maximum allowed time to respond to a query. The multicast group being reported or left is held in the group address field.

An Ethernet switch with IGMP snooping monitors network traffic and inspects each IGMP packet. The switch creates a lookup table and stores a list of respective multicast group members. When a packet arrives, if the multicast group is known to the switch, then the switch forwards the packet to the correct members. The switch therefore, does not need to default to broadcasting and reduces the amount of network traffic.

While the multicast example in Fig. 2.3 only has a single transmitter, throughput is difficult to maintain when multiple multicast streams exist simultaneously. This is where network coding comes in. As introduced by the butterfly network in Fig. 1.1, network coding aims to improve throughput in multicast streaming applications.

### 2.4 Network coding

Network coding needs to be integrated into an intermediate device or network switch to benefit multicast traffic. To incorporate network coding into an Ethernet switch, an algorithm is required that can work in a real packet-based network.

This section aims to create a set of links from the original idea of network coding to practical coding implementations. A bias is taken towards finding practical parameters to utilise network coding for robust, continuous packet processing. Factors of packet construction, link stability, network topology and codecs are all investigated. The focus is on the practical and application side of network coding, and how it is derived from theory.

#### 2.4.1 Codes to Kodo

The theoretical discussion begins with the *max-flow min-cut* theorem. The theorem states that the maximum information flow rate of a network is limited by the minimum cut. Taken from graph theory, the minimum cut is the sum of the removed edge capacities between the source and sink nodes, to stop flow.

Ahlswede's states a conjecture similar to max-flow min-cut where the source information rate must be less or equal to the max-flow of the sender to receiver [2]. Network configurations consisting of sources sending to multiple sink nodes (i.e. multicast) would require network coding in order to achieve maximum flow capacity. Ahlswede shows that even simple codes are able to achieve max-flow. Alpha codes, which are a type of block code, are used as the original bases

for network coding. Convolutional codes are also shown to be good alternatives to block codes for practical scenarios. While the idea was introduced here, Ahlswede left lots of room for improvement.

One of the first expansions to [2] was conducted by Li, et al. using linear codes for network coding [18]. In Li's approach data is represented as a row vector, and linear transformations are applied at coding nodes. The information leaving the coding nodes is a linear combination of the incoming data. This idea is presented as a linear code multicast or LCM. A physical realization of LCM in a acyclic network is provided. Each individual, intermediate node waits until data has been received on each incoming channel. The node performs network coding and sends the encoded data out on each outgoing channel. Each intermediate node performs coding based on a sequential order.

Use of an LCM is shown to achieve the same individual max-flow capacity presented by Ahlswede. This is an advancement because linear codes are easier to implement in practise. However, due to the approach being based upon synchronisation, it is not suitable for real-time applications. Li leaves room for improvement, and opens the field to many mathematical disciplines.

Koetter and Médard took advantage of [18]'s work in [19]. They provide an algebraic framework to solve network coding scenarios. The main contribution is suitable algebraic conditions to determine network feasibility, and study network capacity when using linear codes. The results of [2] are achieved using only scalar linear algebra over a finite field. This is significant in that it allows the use of powerful algebraic mathematics to solve network coding problems. A technique for finding linear coding coefficients is also provided. Another result presented by [19] is that network coding provides robustness in the context of link failure.

Previous work and that done by [19], uses an overview of the complete network for network coding. On the other hand, Ho, et al. shows that distributed randomised coding is beneficial over routing [20]. The idea is that each intermediate node selects coding coefficients from the finite field given by [19]. The receiving nodes only require the overall linear combination to decode the original information. Random coding maintains the network capacity of [2], while providing robustness. This robustness is achieved by distributing information over the network, allowing for any topology changes or link failures. The probability of successful information flow is shown to be proportional to the finite field size.

Two additional approaches to the work of [19] for determining network feasibility, and if a linear code is valid are given in [21]. This work is done in companion, to help formulate the results of [21]. A tighter bound on required coding field size over [19] is given.

All previous discussion up to this point has been focused on the feasibility of network coding from a mathematical side. The results presented by Chou, et al. provide a practical distributed network coding scheme in [5]. The theoretical work looks at synchronous network flow, where as practical systems

are subject to packet loss, delays and jitter which cause asynchronous flow. The capacities between nodes are not known, along with a less complete network overview. Chou addresses various additional practical problems such as cycle networks, link loss, topology changes and congestion. A packet format is proposed that allows for decentralised network coding operations. The results show that a field size of  $2^8$  is sufficient in practise, while  $2^{16}$  is more than enough.

The scheme in [5] works as follows. Incoming symbols are packeted into vectors of specific length related to the field size, e.g. 1400 symbols for 2<sup>8</sup>. On the outgoing side, each vector is expressed as a linear combination of the incoming vectors. Each packet includes the global coding vector as a header, allowing a receiver to decode the original information via Gaussian elimination. The cost of this approach is in transporting the coding coefficients. The overhead however, is relatively small compared to the overall packet size, especially considering the benefit of decentralisation. This approach allows receivers to decode the original information in a practical system, as well as when randomly chosen coefficients such as those in [20] are used.

In practical systems where packets transverse asynchronously through a network, the packet format by itself becomes problematic. This is because packets from the same source vectors can be received out of order. The decoder does not know which packets should be decoded together. To solve this, [5] introduces the concept of *generations*, in which packets from the same source are grouped by generation with a specific generation size.

Each generation has a specific number which is included in the packet header. Packets received at a node are buffered by generation number. When an outgoing transmission opportunity arises, a random linear combination of all packets in that generation are sent out as a packet. Older generations are removed based on a flushing policy, where packets that arrive belonging to older generations are discarded. A loss of throughput can be experienced from this and is proportional to the delay between the time it takes for the first packet to reach a node over the slowest and fastest paths. This delay is known as delay spread. Increasing the generation size is shown to decrease throughput loss, but increases net throughput due to increased packet header size. Another condition known as interweaving length is shown to have a large effect on decreasing throughput loss.

Interweaving length is the amount of buffers which the original multicast session is distributed. It is suggested that different flushing policies can be used to reduce throughput further. Packets that do not provide new information for generating random packets to be sent out are useless and therefore disregarded. Keeping track of non-innovative packets can also help to reducing bandwidth.

The simulation results performed by Chou show performance gained in terms of received rank, throughput and decoding delay as a function of sending rate, latency, field size, generation size, and interweaving length. The average receiver rank is shown to gain very minimal increase over field sizes of  $2^8$ .

Throughput is described as the product of sending rate and average received rank divided by the generation size. The results show that throughput loss is inversely proportional to generation size and interweaving length. This shows that a larger generation size and longer interweaving length will reduce throughput losses.

After the significant practical contribution of [5], more theoretical study is conducted by some of the same authors from [19], [20] and [21]. This work presented by Ho, et al. in [3] presents a RLNC approach that achieves multicast capacity with almost certainty as the code length increases. The results contribute by expanding those of [20] and show how random codes can be created, as well as transmitted from source to receivers in a distributed network. The approach is able to maintain capacity as well as improve robustness. It is mentioned that network coding is not useful for all network configurations. As a result, simulations are conducted with two scenarios that benefit from network coding.

The scenarios that benefit from network coding are distributed networks, and networks with dynamic connections. Simulation results show that RLNC is able to outperform traditional routing approaches [20]. Overheads are observed while performing coding operations at the encoder and decoder, and with coefficients in the packet headers.

#### 2.4.2 RLNC theory

In order to implement RLNC in a software and hardware-based platform, the RLNC theory needs to be well understood to determine the types of processing operations required. We therefore continue the discussion onto the details of the RLNC algorithm.

The encoder needs to encode the incoming packet data. Incoming, uncoded packets are grouped in *generations* of a *generation size*, h. All of the packets in a generation are from the same source. These incoming packets are multiplied by a set of randomly generated coding coefficients, as RLNC. The work previously done by Chou, et al. provides a foundation for the encoding process [5]. A packet format is proposed that does not require any consideration of graph topology or coding functions. The same notation is used to provide a comparative discussion.

The standard framework for network coding is taken from Ahlswede, et al. and describes a network as an acyclic graph [2],

$$G = (V, E)$$

The set of edges E carry information between the vertices V, from the source senders  $S \subseteq V$  to the receivers  $R \subseteq V$ . The source vector for a single packet, of N symbols, is written as,

$$\mathbf{x_i} = [x_{i.1}, x_{i.2}, ..., x_{i.N}]$$

where each source symbol  $x_i$  represents one byte of data. Grouping the source packets along h incoming edges, as a generation, gives the source vectors,

$$x_1, ..., x_h$$

which is written in matrix form as,

$$\boldsymbol{X} = \begin{vmatrix} \boldsymbol{x_1} \\ \vdots \\ \boldsymbol{x_h} \end{vmatrix} = \begin{vmatrix} x_{1,1} & x_{1,2} & \dots & x_{1,N} \\ \vdots & \vdots & \ddots & \vdots \\ x_{h,1} & x_{h,2} & \dots & x_{h,N} \end{vmatrix}$$

(2.1)

Following the same formation, the coding coefficient symbols  $g_i(e)$ , along edge e are written in vector form as,

$$g(e) = [g_1(e), g_2(e), ..., g_h(e)]$$

where g(e) corresponds to the global coding vector for the edge e. Combining the global coding vectors for h incoming edges,

$$e_1, e_2, ..., e_h$$

is represented in matrix form, with rank h as,

$$G_t = \begin{vmatrix} \boldsymbol{g}(\boldsymbol{e_1}) \\ \vdots \\ \boldsymbol{g}(\boldsymbol{e_h}) \end{vmatrix} = \begin{vmatrix} g_1(e_1) & g_2(e_1) & \dots & g_h(e_1) \\ \vdots & \vdots & \ddots & \vdots \\ g_1(e_h) & g_2(e_h) & \dots & g_h(e_h) \end{vmatrix}$$

(2.2)

The output symbol for a given edge e is calculated as the linear combination of the source packets and the coding coefficients,

$$y(e) = \sum_{i=1}^{h} g_i(e)x_i = g_1(e)x_1 + g_2(e)x_2 + \dots + g_h(e)x_h$$

(2.3)

Combining all the output symbols along e into a single output packet  $y(e_i)$  provides the output vector,

$$\mathbf{y}(\mathbf{e}_{i}) = \begin{vmatrix} y_{1}(e_{i}) \\ \vdots \\ y_{N}(e_{i}) \end{vmatrix}^{T}$$

$$= \begin{vmatrix} g_{1}(e_{i})x_{1,1} + g_{2}(e_{i})x_{2,1} + \dots + g_{h}(e_{i})x_{h,1} \\ g_{1}(e_{i})x_{1,2} + g_{2}(e_{i})x_{2,2} + \dots + g_{h}(e_{i})x_{h,2} \\ \vdots \\ g_{1}(e_{i})x_{1,N} + g_{2}(e_{i})x_{2,N} + \dots + g_{h}(e_{i})x_{h,N} \end{vmatrix}^{T}$$

$$= \mathbf{g}(\mathbf{e}_{i})\mathbf{X}$$

(2.4)

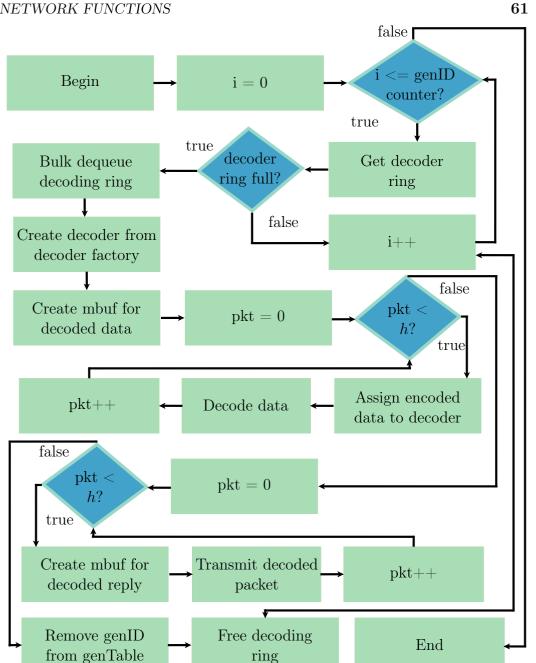

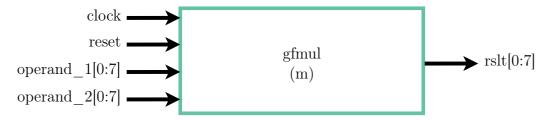

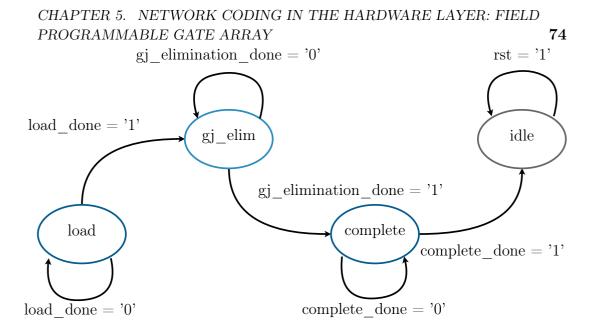

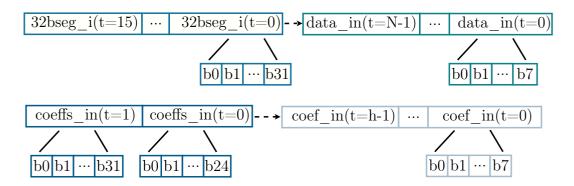

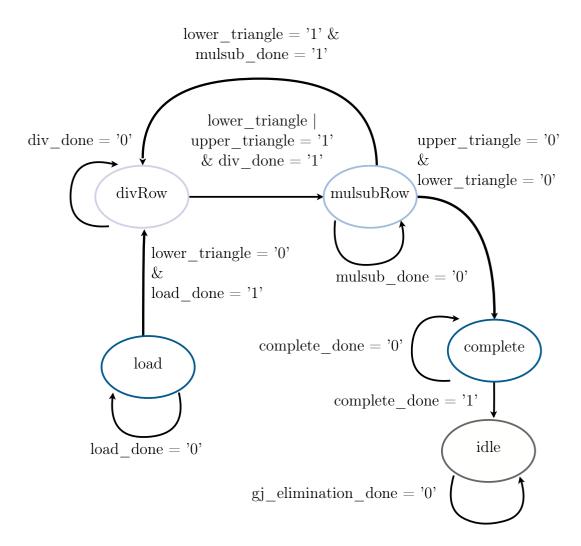

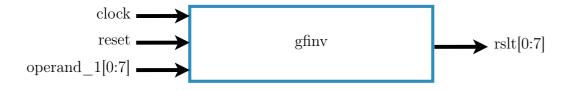

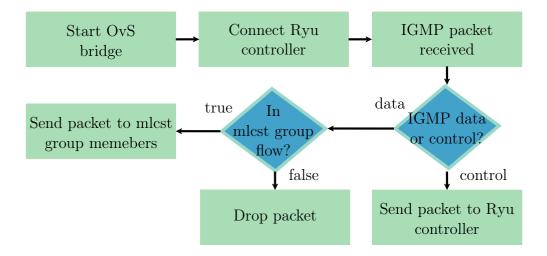

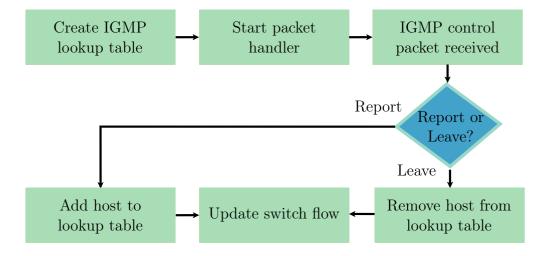

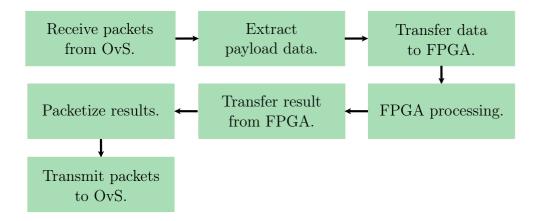

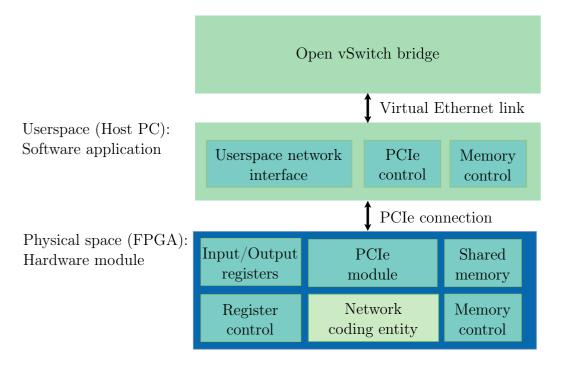

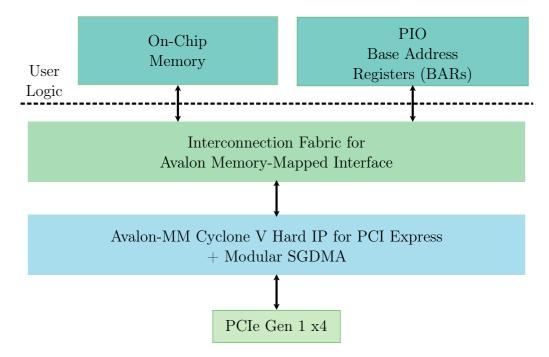

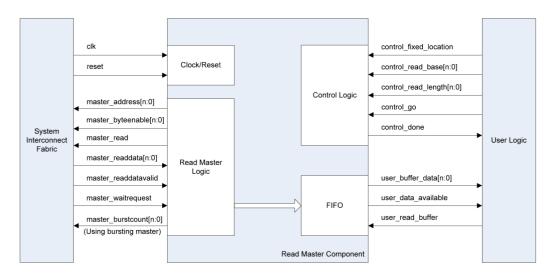

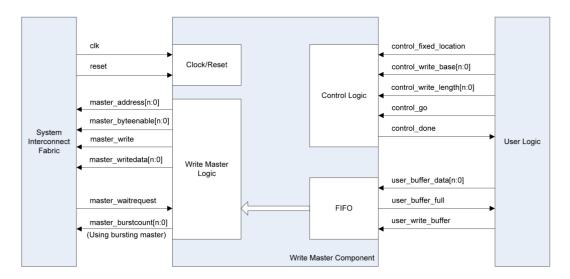

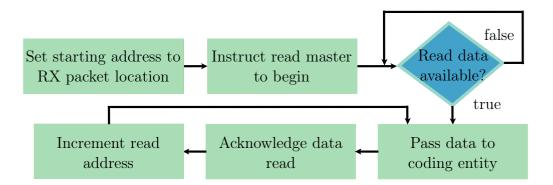

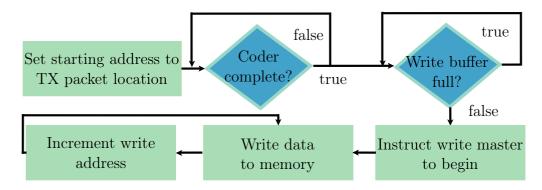

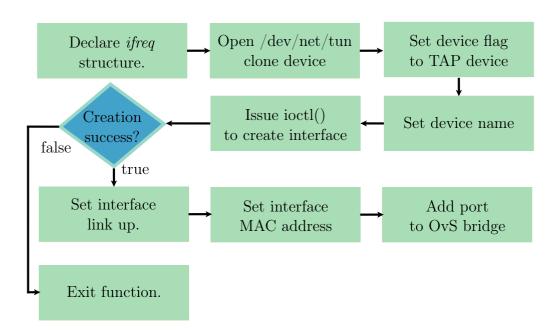

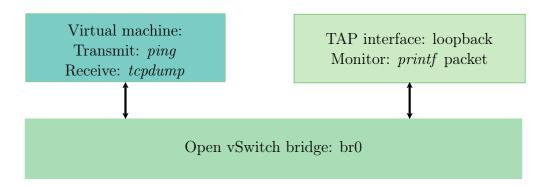

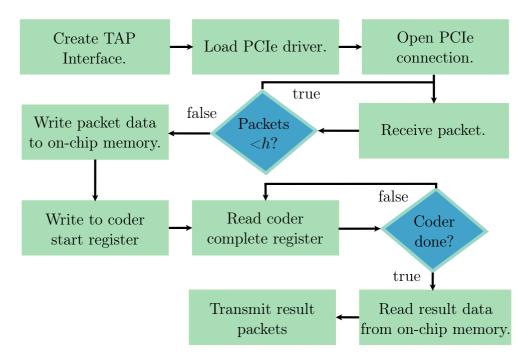

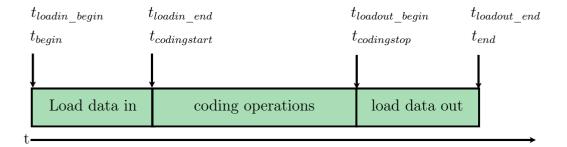

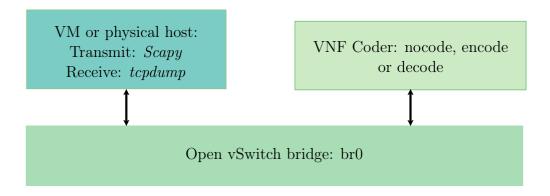

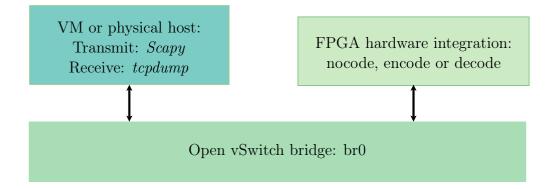

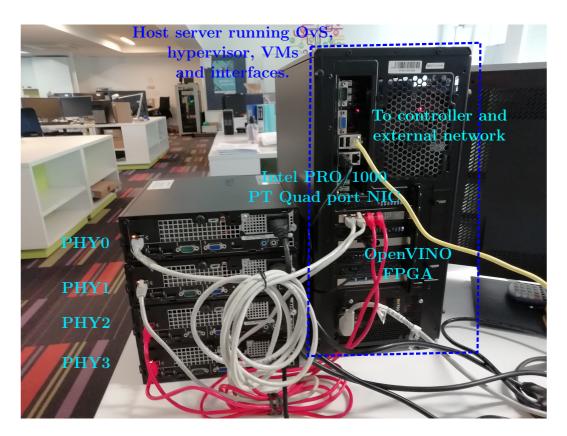

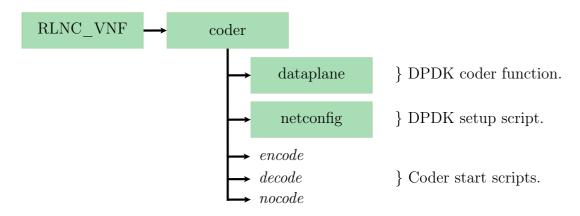

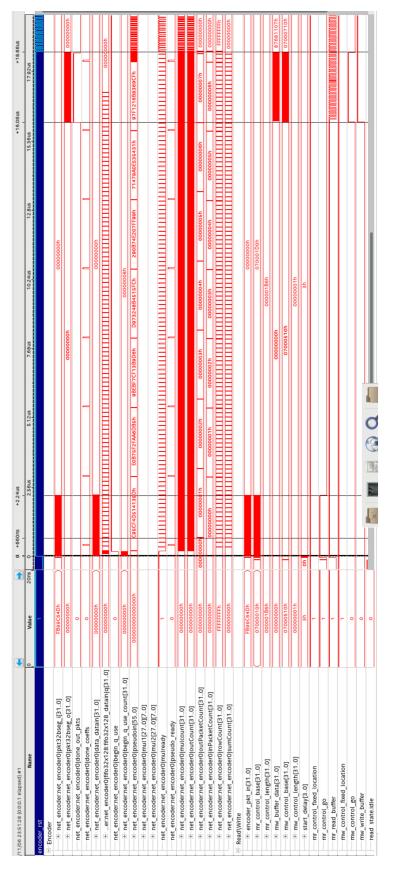

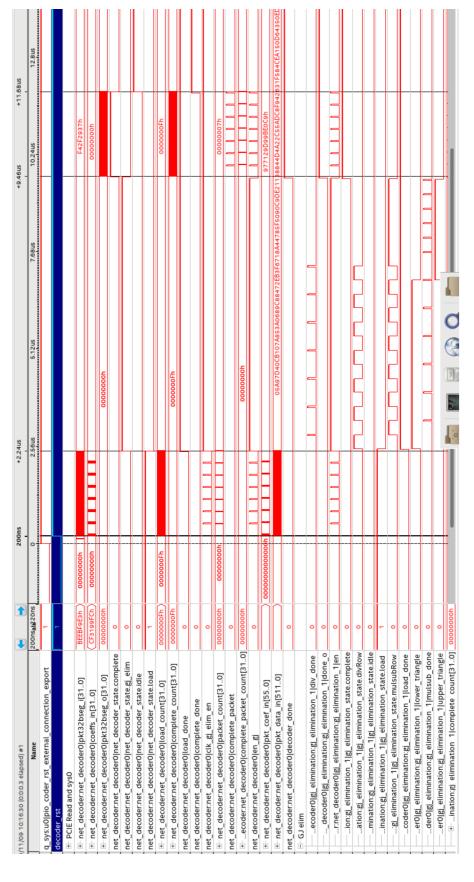

Further, combining all the output packets for a generation size h, provides the encoded output matrix,