# **Digital Control of Line-Interactive UPS**

by

JF van Papendorp

Thesis presented in partial fulfilment of the requirements for the degree Master of Science in Engineering at Stellenbosch University

Supervisor: Dr HJ Beukes Department of Electrical and Electronic Engineering

March 2011

# Declaration

By submitting this thesis electronically, I declare that the entirety of the work contained therein is my own, original work, that I am the sole author thereof (save to the extent explicitly otherwise stated), that reproduction and publication thereof by Stellenbosch University will not infringe any third party rights and that I have not previously in its entirety or in part submitted it for obtaining any qualification.

Date: ......08/02/2011.....

Copyright © 2011 Stellenbosch University All rights reserved

## Abstract

The digital control of UPS systems has been difficult in the past due to a lack of DSP technology. It was for this reason not possible to establishing the necessary control to regulate the voltages and currents of the UPS systems. Recent advances in DSP technology have however provided the means of establishing central control of the UPS system as well as incorporating more complex closed-loop control algorithms by utilising a single floating-point DSP.

Closed-loop control strategies are investigated and the central control of a line-interactive UPS is established in this study. Both the status of the physical system as well as various system parameters are controlled. The system both regulates and charges the storage batteries when the main utility supply is maintained. In the event that the utility fails, the converter instantaneously changes power flow towards the load with the aim of maintaining an uninterrupted voltage supply.

Several closed-loop deadbeat based control strategies are investigated for the regulation of the inductor current. A solution for the regulation of the DC-link is also developed and implemented. Furthermore, an intensive study is done on the regulation of the voltage supplied to the load in the event that the utility supply fails. The investigation is initially approached by considering classical control theory. Although these control strategies provided sufficient results, a predictive strategy that is based on the physical conditions of the switching converter is finally investigated to establish closed loop control of the output voltage. This resulted in a high-bandwidth voltage controller capable of maintaining control under a wide-array of load conditions.

## Opsomming

Die digitale beheer van UPS stelsels was moeilik in the verlede as gevolg van 'n gebrek aan DSP tegnologie. Dit was vir hierdie rede nie moontlik om beheer te kon bewerkstelling ten einde die spannings and strome in the UPS stelsels te kon reguleer nie. Onlangse vordering in DSP tegnologie het egter dit moontlik gemaak om sentrale beheer van die UPS stelsel te bewerkstellig sowel as om meer komplekse geslote lus beheer algoritmes te inkorporeer met behulp van 'n enkele DSP.

Geslote lus beheer strategiëe word ondersoek en die sentrale beheer van die line-interaktiewe UPS word bewerkstellig in hierdie studie. Beide die huidige toestand van die fisiese stelsel sowel as die verskeie parameters word beheer. Die stelsel beide laai en reguleer die batterye terwyl die hooftoevoer onderhou word. In die geval dat die hooftoevoer faal, word die omsetter se rigting van drywingsvloei verander om die las te voorsien van 'n ononderbroke spannings toevoer.

Verskeie geslote-lus "deadbeat" beheer strategiëe word ondersoek vir die regulasie van die induktor stroom. 'n Oplossing vir die regulasie van die GS-koppervlak word ook ontwikkel en geïmplementeer. Verder word 'n intensiewe studie gedoen op regulasie van die spanning wat aan die las gevoer word in die geval dat die hooftoevoer faal. Hierdie ondersoek word aanvanklik benader deur klassieke beheer teorie te bestudeer. Alhoewel hierdie beheer strategiëe voldoene resultate gebied het, was 'n voorspel beheerstrategie gebaseer op die fisiese toestand van die omsetter finaal ondersoek. Die resultaat is 'n hoë-bandwydte spannings beheerder wat daartoe instaat is om beheer te handhaaf onder 'n verskeidenheid van lastoestande.

## Acknowledgements

Among all other, I must firstly thank my God Almighty, His Son Jesus Christ and the ubiquitous Holy Spirit for the blessing He has bestowed upon me. Thank you for providing the capacity and capability to practice this wonderful field of engineering. To You belongs all the honour.

My colleagues, Francois Breet, Ivan Hobbs, Louis Schietekat and Frans Welgemoed, for your never-ending assistance and creating a wonderful atmosphere to work in.

Neil Serdyn, for your willingness to always help and assist me with anything in the laboratory.

Jaco Serdyn, for your assistance and guidance with many of the engineering aspects in my time in the laboratory.

My study leader, Dr HJ Beukes, for the guidance and advice you provided throughout the course of this study and for providing the financial means to conduct the study project.

And lastly, I thank my father, mother and sister for your support and patience throughout my engineering studies. Without you I could not have succeeded

# **Table of Contents**

| 1 Introduction                                              | 1  |

|-------------------------------------------------------------|----|

| 1.1 Improving the Quality of the Electricity Supply         | 1  |

| 1.2 The Uninterruptible Power System (UPS)                  | 2  |

| 1.3 UPS Topologies                                          | 3  |

| 1.3.1 Passive-Standby Offline UPS                           | 3  |

| 1.3.2 Double-Conversion On-line UPS                         | 4  |

| 1.3.3 Line-Interactive UPS                                  | 6  |

| 1.4 Problem Statement                                       | 7  |

| 1.5 Thesis Objective                                        | 8  |

| 1.6 Structure of this Thesis                                | 8  |

| 2 Development of the Control Hardware                       | 11 |

| 2.1 Introduction                                            | 11 |

| 2.2 Analogue-to-Digital Converter                           | 12 |

| 2.2.1 Basic Operation                                       | 12 |

| 2.2.2 ADC Architectures                                     | 15 |

| 2.3 Data Acquisition Solutions                              | 22 |

| 2.3.1 Single-Ended                                          | 23 |

| 2.3.2 Fully-Differential                                    | 23 |

| 2.3.3 Pseudo-Differential                                   | 23 |

| 2.4 Pulsewidth Modulation Schemes                           | 24 |

| 2.5 Overview of the Line-Interactive UPS                    | 27 |

| 2.6 Power Supply Consideration                              | 29 |

| 2.6.1 Ground Loops                                          | 29 |

| 2.6.2 Common-Mode Noise                                     | 30 |

| 2.6.3 Differential-Mode Noise                               | 31 |

| 2.6.4 Choosing a Power Supply Solution                      | 31 |

| 2.7 Online Monitoring of Small-Signal Power Supply Voltages | 33 |

| 2.7.1 Measurement of Power Supply Voltages                  | 33 |

| 2.7.2 Embedded Acquisition of Measured Voltages             | 34 |

| 2.8 System Status Sensing and Control                |  |

|------------------------------------------------------|--|

| 2.8.1 Real-Time Sensing                              |  |

| 2.8.2 Switch Control                                 |  |

| 2.9 Digital Signal Controller                        |  |

| 2.9.1 The Delfino 32-bit Floating-Point Processor    |  |

| 2.9.2 Measurement Conversion                         |  |

| 2.10 Parameter Measurement and Signal Conditioning   |  |

| 2.10.1 Voltage Measurement                           |  |

| 2.10.2 Current Measurement                           |  |

| 2.11 Optical Communication Interface                 |  |

| 2.11.1 Optical Transmission                          |  |

| 2.11.2 Optical Receiving                             |  |

| 2.12 Conclusion                                      |  |

| 3 The Switching Three-Phase Converter                |  |

| 3.1 Introduction                                     |  |

| 3.2 The Clarke Transformation                        |  |

| 3.3 Park's Transformation                            |  |

| 3.4 Dead Time Compensation                           |  |

| 3.4.1 Principle of Operation                         |  |

| 3.4.2 Simulated Performance                          |  |

| 3.5 Conclusion                                       |  |

| 4 Control of the Active Rectifier                    |  |

| 4.1 Introduction                                     |  |

| 4.2 Proposed Control Strategy                        |  |

| 4.3 Predictive Current Controller: A Direct Approach |  |

| 4.3.1 Principle of Operation                         |  |

| 4.3.2 Simulated Performance                          |  |

| 4.4 DC-Link Voltage Regulation Strategy              |  |

| 4.4.1 Principle of Operation                         |  |

| 4.4.2 Integrator Windup                              |  |

| 4.4.3 Simulated Performance                                           |  |

|-----------------------------------------------------------------------|--|

| 4.5 Conclusion                                                        |  |

| 5 Control of the Voltage-Source Inverter                              |  |

| 5.1 Introduction                                                      |  |

| 5.2 Modelling the System                                              |  |

| 5.3 Current Control Strategies                                        |  |

| 5.3.1 Introduction                                                    |  |

| 5.3.2 Predictive Current Controller: A Mathematical Approach          |  |

| 5.3.3 Predictive Current Controller: A Physical Approach              |  |

| 5.3.4 Conclusion                                                      |  |

| 5.4 Voltage Control Strategies                                        |  |

| 5.4.1 Open-Loop Voltage Controlled                                    |  |

| 5.4.2 Alpha-Beta Control: A Classical Control Approach                |  |

| 5.4.3 Alpha-Beta Control: An Alternative Approach                     |  |

| 5.4.4 Direct-Quadrature (DQ) Controller                               |  |

| 5.4.5 P+Resonant Controller                                           |  |

| 5.4.6 Predictive Voltage Controller                                   |  |

| 5.5 Conclusion                                                        |  |

| 6 Experimental Investigation                                          |  |

| 6.1 Introduction                                                      |  |

| 6.2 Open-Loop Controlled Experimental Investigation                   |  |

| 6.3 Evaluation of Classically Approached Alpha-Beta Voltage Control   |  |

| 6.4 Evaluating an Alternative Approach of Alpha-Beta Voltage Control  |  |

| 6.5 Evaluating the Voltage Controller Based in the DQ Reference Frame |  |

| 6.6 Evaluation of P+Resonant Voltage Control                          |  |

| 6.7 Evaluating a Predictive Voltage Controller                        |  |

| 6.8 Conclusion                                                        |  |

| 7 Conclusions and Recommendations                                     |  |

| 7.1 General Investigation                                             |  |

| 7.2 Dead-Time Compensation                                            |  |

| 7.3 DC    | C-Link Regulation            | 143 |

|-----------|------------------------------|-----|

| 7.4 Co    | ntrol of VSI Output Voltage  |     |

| 7.5 Rec   | commendations                |     |

| 8 Bibliog | grapy                        | 145 |

| Appendix  | x A Mathematical Derivations | I   |

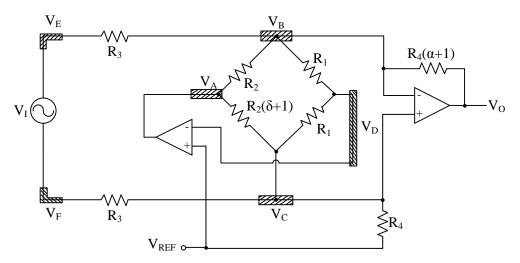

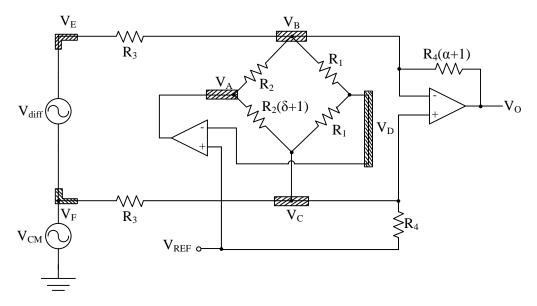

| A.1 V     | oltage Measurements          | I   |

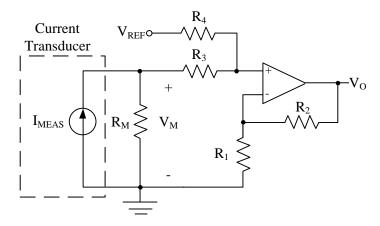

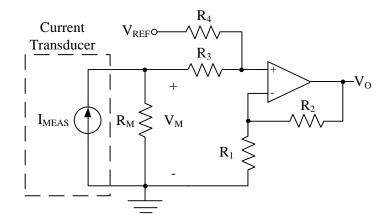

| A.2 C     | Current Measurements         | X   |

| Appendi   | x B Circuit Derivations      | XII |

| B.1 So    | chmitt Trigger               | XII |

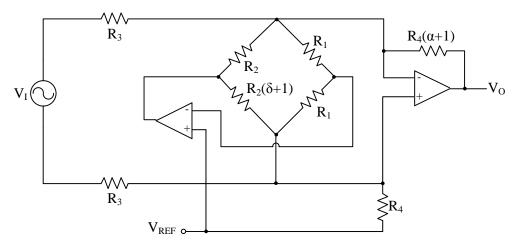

| B.2 V     | Voltage Measurement Circuit  | XII |

# Nomenclatures

| AC     | Alternating Current                               |

|--------|---------------------------------------------------|

| ADC    | Analog to Digital Converter                       |

| ALU    | Arithmetic Logic Unit                             |

| APF    | Active Power Filter                               |

| CMRR   | Common-Mode Rejection Ratio                       |

| CPLD   | Complex Programmable Logic Device                 |

| DC     | Direct Current                                    |

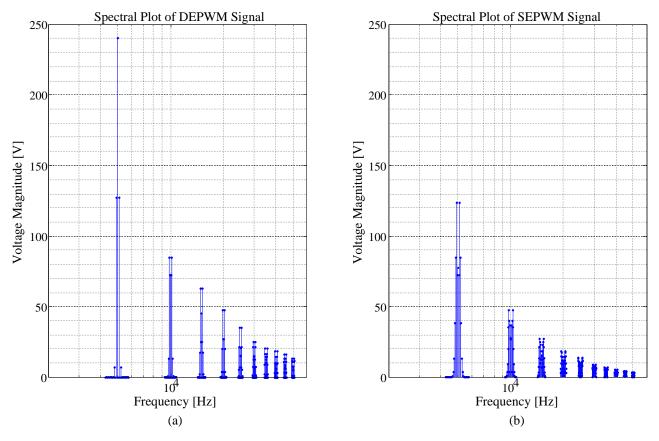

| DEPWM  | Double-Edge PWM                                   |

| DQ     | Direct-Quadrature                                 |

| DSC    | Digital Signal Controller                         |

| DSP    | Digital Signal Processor                          |

| EMI    | Electromagnetic Interference                      |

| ENOB   | Effective Number of Bits                          |

| FSR    | Full-Scale Range                                  |

| GBP    | Gain-Bandwidth Product                            |

| HMI    | Human Machine Interface                           |

| IGBT   | Isolated Gate Bipolar Transistor                  |

| LEPWM  | Leading-Edge PWM                                  |

| LSB    | Least Significant Bit                             |

| MOSFET | Metal-Oxide Semiconductor Field-Effect Transistor |

| MSB    | Most Significant Bit                              |

| РСВ    | Printed Circuit Board                             |

| PCC    | Point of Common Coupling                          |

| PI     | Proportional Integral                             |

| PM     | Phase Margin                                      |

| PWM    | Pulsewidth Modulation                             |

| RMS    | Root Mean Squared                                 |

| RTC    | Real-Time Clock                                   |

| SAR    | Successive Approximation Register                 |

| SD     | Secure-Digital                                    |

| SEPWM  | Single-Edge PWM                                   |

| SHA    | Sample-and-Hold Amplifier                         |

| SINAD  | Signal-to-Noise Ratio + Distortion                |

| SMPS   | Switch-Mode Power Supply                          |

| SNR    | Signal-to-Noise Ratio                             |

| SNR    | Signal to Noise Ratio                             |

| SVM    | Space Vector Modulation                           |

| SVPWM  | Space Vector Pulsewidth Modulation                |

|        |                                                   |

| TEPWM | Trailing-Edge PWM                   |

|-------|-------------------------------------|

| THD   | Total Harmonic Distortion           |

| THD+N | Total Harmonic Distortion and Noise |

| UPS   | Uninterruptible Power Supply        |

| VSI   | Voltage-Source Inverter             |

# **List of Figures**

| Figure 1-1: Passive-Standby Topology                           |  |

|----------------------------------------------------------------|--|

| Figure 1-2: Double-Conversion On-Line UPS Topology             |  |

| Figure 1-3: Line-Interactive Topology                          |  |

| Figure 2-1: Focus on Discretisation of Analogue Signals        |  |

| Figure 2-2: Generic ADC Structure                              |  |

| Figure 2-3: Flash Architecture Structure                       |  |

| Figure 2-4: Pipeline Architecture Overview                     |  |

| Figure 2-5: Single-Stage Pipeline Diagram                      |  |

| Figure 2-6: Illustrating Inter-Stage Misalignment              |  |

| Figure 2-7: Illustrating Pipelined Latency                     |  |

| Figure 2-8: Basic SAR Structure                                |  |

| Figure 2-9: Capacitive DAC based on Charge Redistribution      |  |

| Figure 2-10: SAR Operation                                     |  |

| Figure 2-11: Focus on Signal Measurement and Conditioning      |  |

| Figure 2-12: Focus on PWM Scheme                               |  |

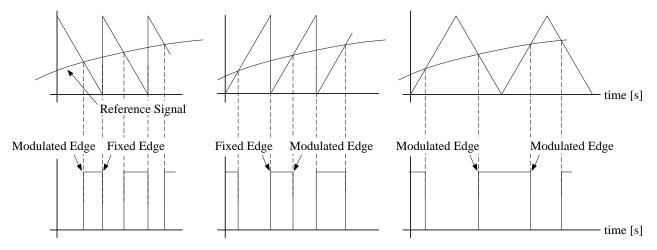

| Figure 2-13: Generation of (a) LEPWM (b) TEPWM (c) DEPWM       |  |

| Figure 2-14: Magnitude Spectrum of Pulsewidth Modulated Signal |  |

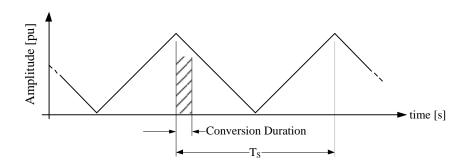

| Figure 2-15: Synchronised Sampling of Switched Signal          |  |

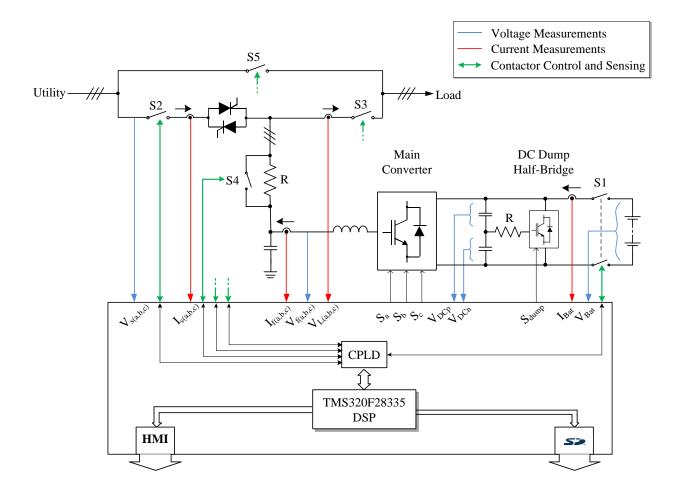

| Figure 2-16: Line-Interactive UPS System Overview              |  |

| Figure 2-17: A Common Ground Loop                              |  |

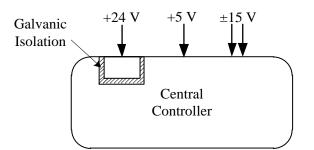

| Figure 2-18: CM-Filter Equivalent Circuit                      |  |

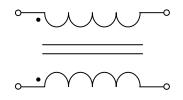

| Figure 2-19: Suppressing Differential-Mode Noise               |  |

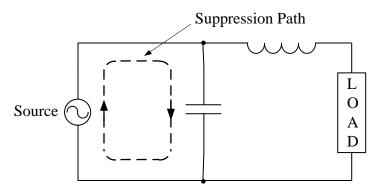

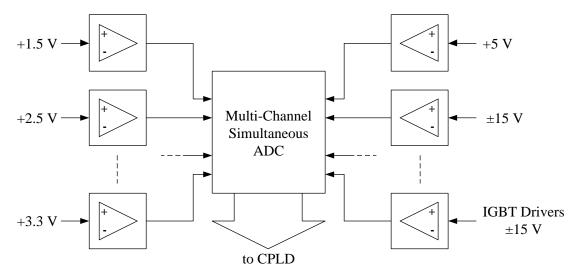

| Figure 2-20: Power Supply Overview                             |  |

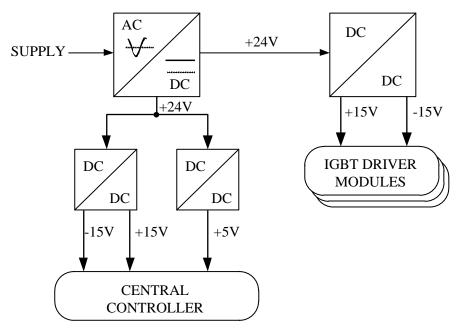

| Figure 2-21: Central Controller Power Supply Overview          |  |

| Figure 2-22: Voltage Measurement                               |  |

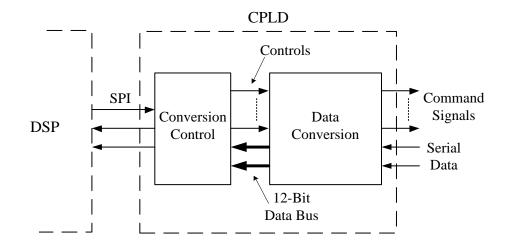

| Figure 2-23: Embedded Design of Voltage Acquisition            |  |

| Figure 2-24: Sensing Circuit with Incorporated Schmitt Trigger |  |

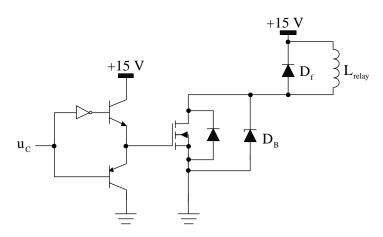

| Figure 2-25: Switch Control Circuit                            |  |

| Figure 2-26: Controller Block Diagram                          |  |

| Figure 2-27: Conversion Duration Timing Diagram                |  |

| Figure 2-28: Voltage Measurement                               |  |

| Figure 2-29: Current Measurement                               |  |

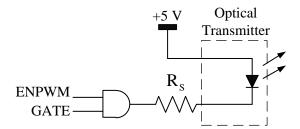

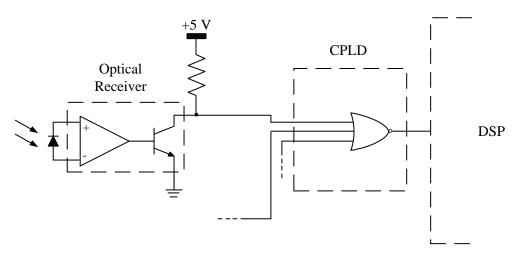

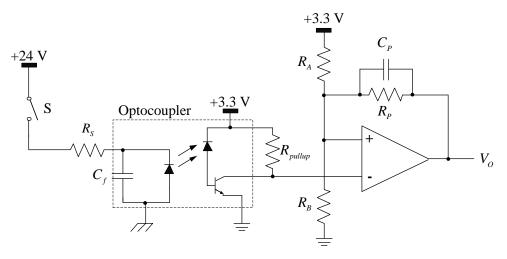

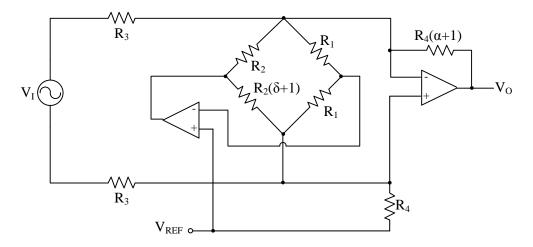

| Figure 2-30: Optical Transmitter Circuit                       |  |

| Figure 2-31: Optical Receiver Circuit                          |  |

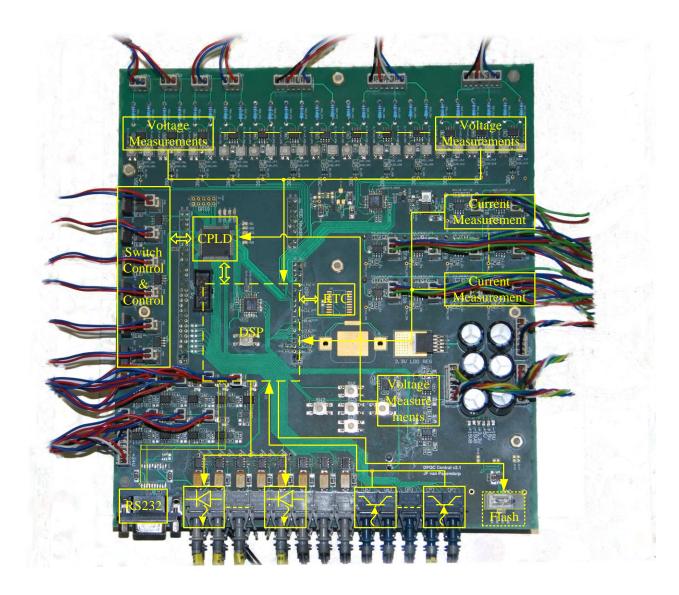

| Figure 2-32: Photograph of Digital Central Controller          |  |

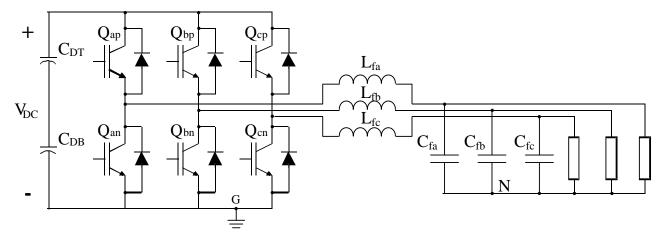

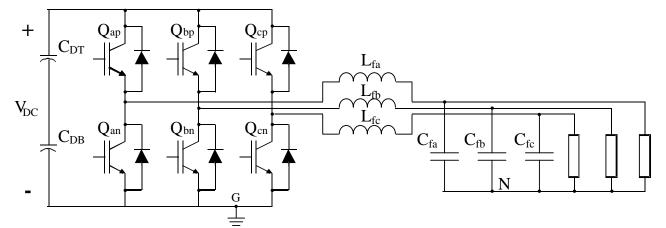

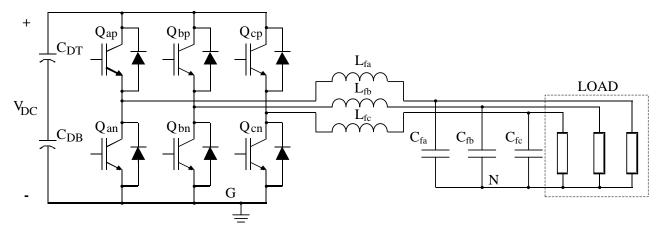

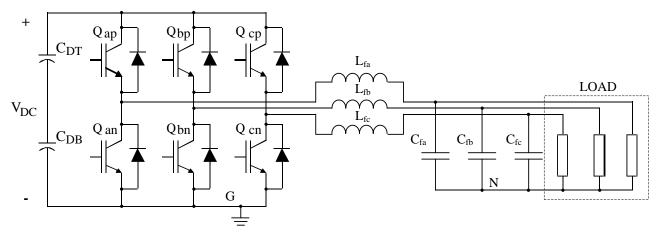

| Figure 3-1: Three-Phase Inverter Topology                                                              | . 49 |

|--------------------------------------------------------------------------------------------------------|------|

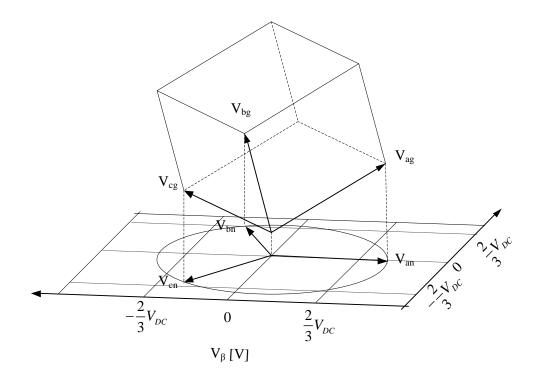

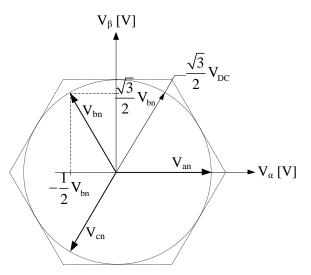

| Figure 3-2: Three-Phase System Projection onto αβ-Plane                                                | . 50 |

| Figure 3-3: Projecting ABC-Vectors onto αβ-Plane                                                       | . 50 |

| Figure 3-4: Construction of the Rotational αβ-Reference Vector                                         | . 51 |

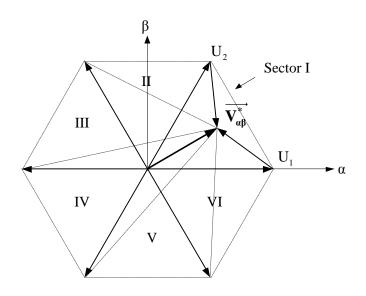

| Figure 3-5: Constructing the αβ-Reference                                                              | . 53 |

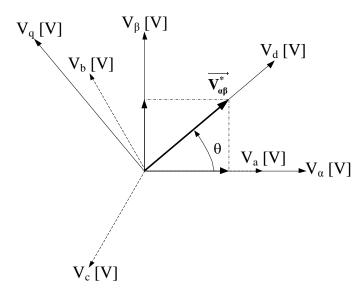

| Figure 3-6: Rotational Reference Frame                                                                 | . 55 |

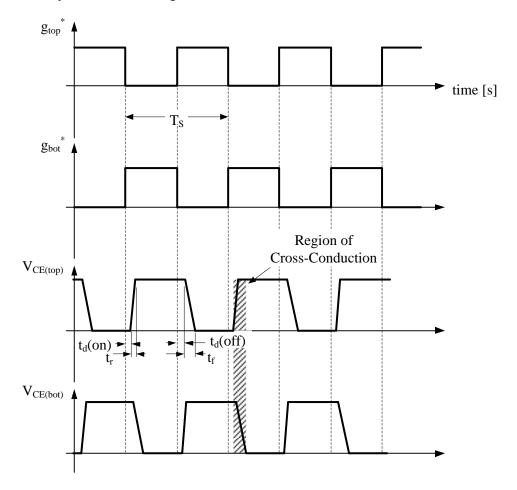

| Figure 3-7: Ideal Switching versus Actual Transition of Power Switch                                   | . 56 |

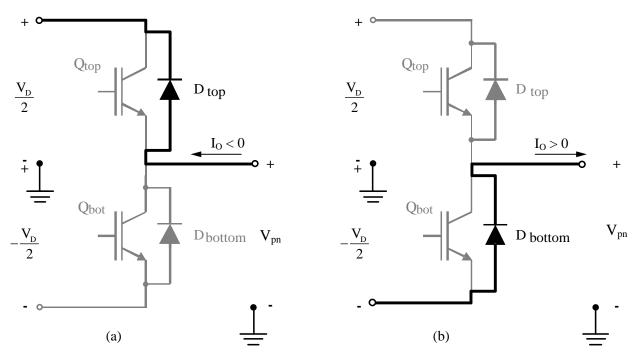

| Figure 3-8: Current Flow during Dead Time when Output Current is (a) Negative and (b) Positive         | . 57 |

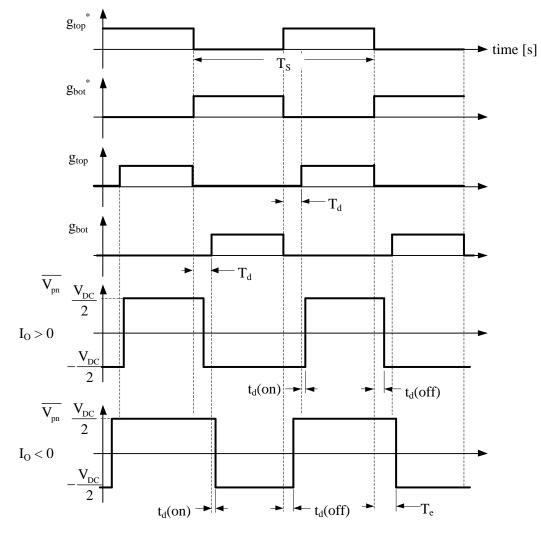

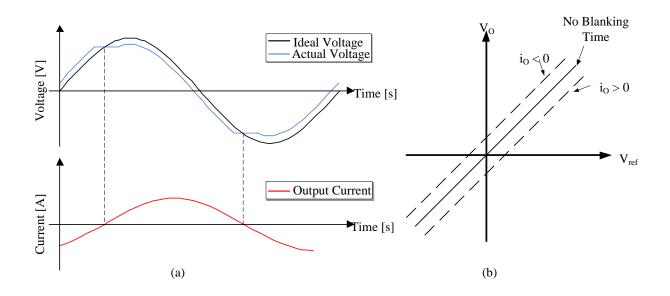

| Figure 3-9: Illustrating Output Voltage Corruption due to Blanking Time                                | . 58 |

| Figure 3-10: Corruption of Output Voltage due to Dead Time (a) in Time Domain and (b) versus the In    | nput |

| Reference Voltage                                                                                      | . 59 |

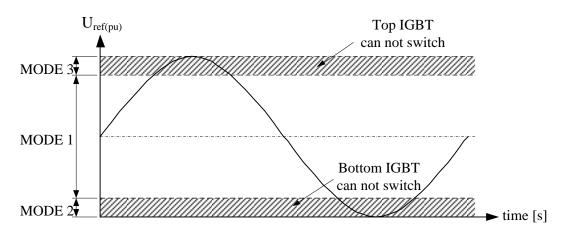

| Figure 3-11: Mode Definitions used in Dead Time Compensation                                           | . 60 |

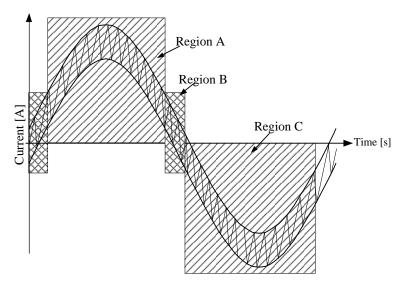

| Figure 3-12: Defining Inductor Current Regions                                                         | . 65 |

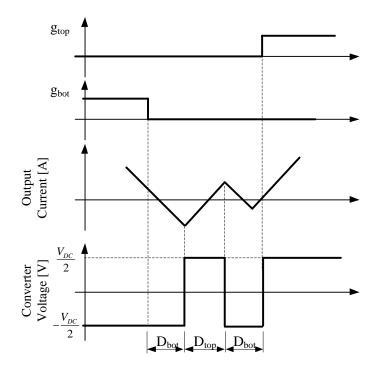

| Figure 3-13: Waveform Distortion during Region B                                                       | . 65 |

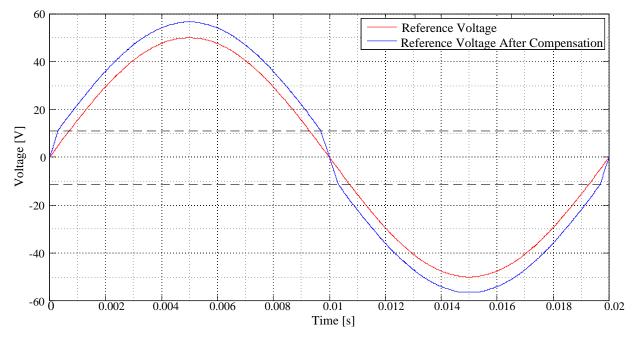

| Figure 3-14: Resulting Modified Output Voltage due to Dead Time Compensation                           | . 66 |

| Figure 3-15: Three-Phase VSI Simulation Model                                                          | . 67 |

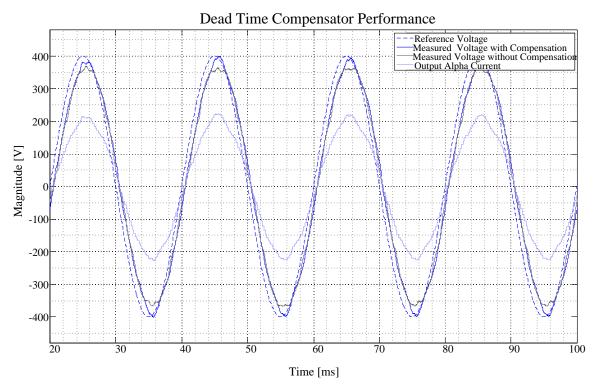

| Figure 3-16: Simulation of Dead Time Compensator Performance                                           | . 67 |

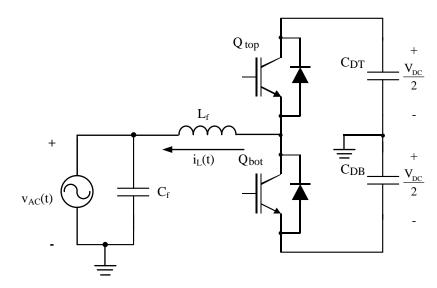

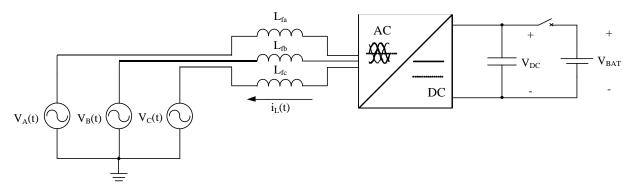

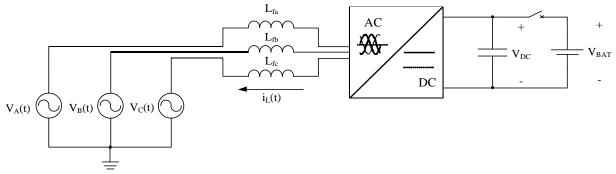

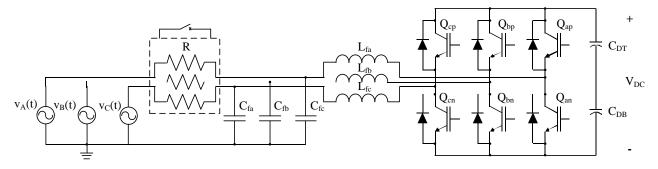

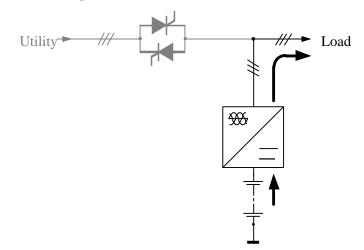

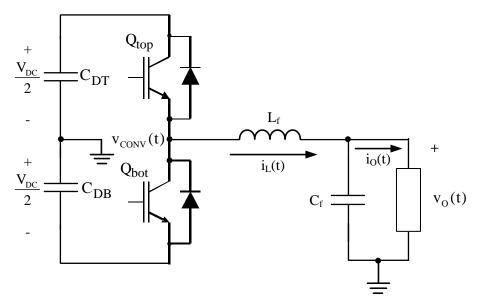

| Figure 4-1: Active Rectifier of the Line-Interactive UPS                                               | . 70 |

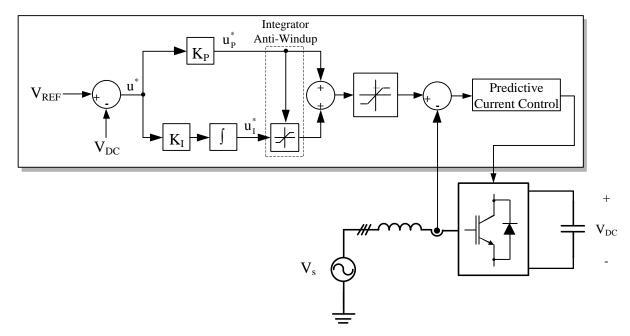

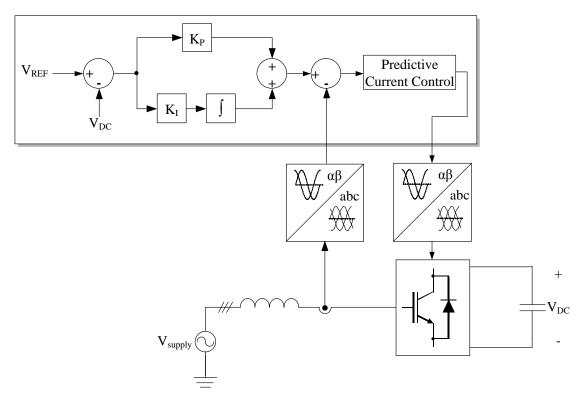

| Figure 4-2: Proposed Control of the Active Rectifier                                                   | . 71 |

| Figure 4-3: Typical Single-Phase Active Rectifier                                                      | . 72 |

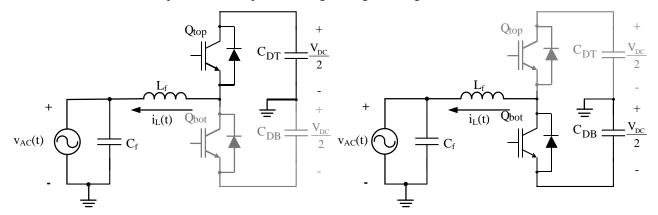

| Figure 4-4: Switching States of the Active Rectifier with (a) High-Side Active and (b) Low-Side Active | 72   |

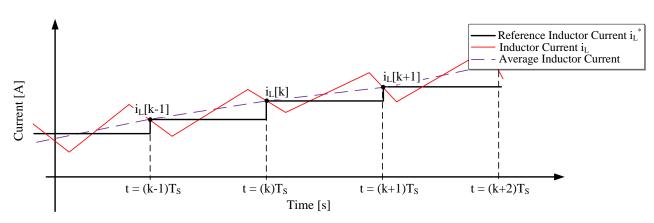

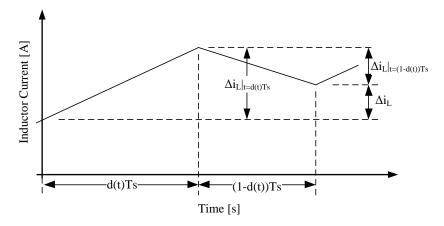

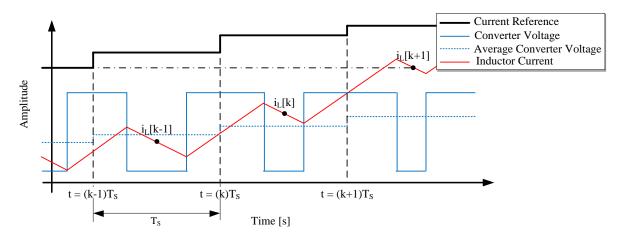

| Figure 4-5: Inductor Current for One Switching Period                                                  | . 73 |

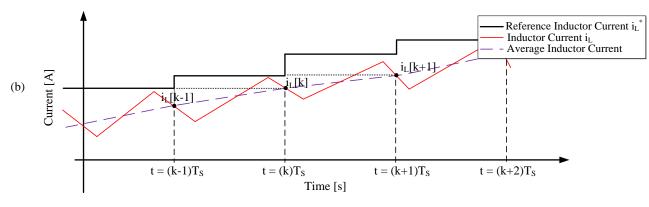

| Figure 4-6: Inductor Current Signals                                                                   | . 74 |

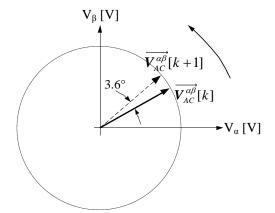

| Figure 4-7: Advancing the Space Vector                                                                 | . 75 |

| Figure 4-8: Active Rectifier Simulation Model                                                          | . 75 |

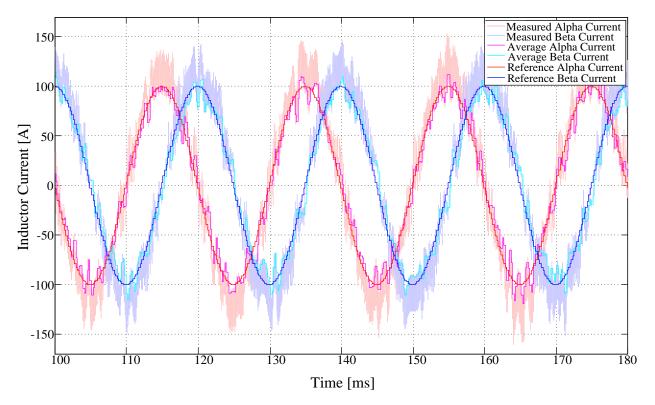

| Figure 4-9: Predictive Current Controller #1 Simulation Results                                        | . 76 |

| Figure 4-10: Overview of Active Rectifier                                                              | . 77 |

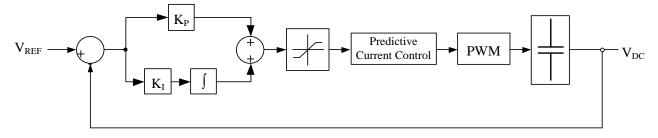

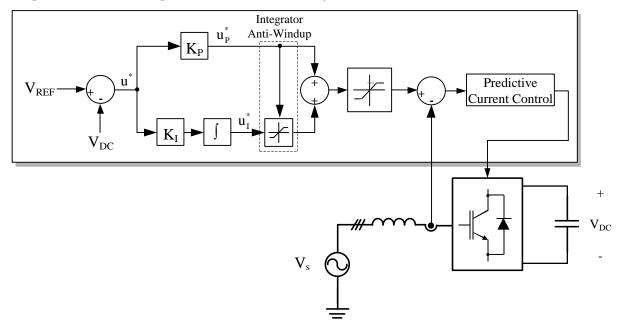

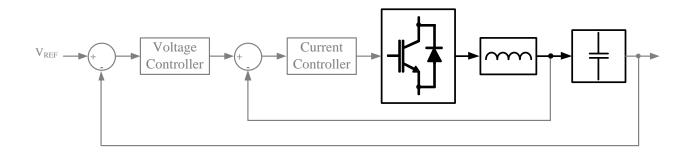

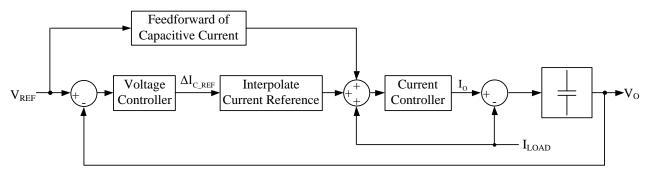

| Figure 4-11: Proposed Multi-loop Control Strategy                                                      | . 78 |

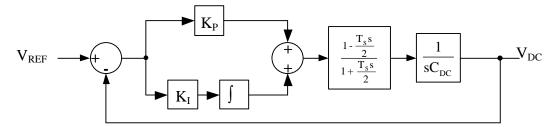

| Figure 4-12: Proposed DC-Link Voltage Controller and System Model Representation                       | . 78 |

| Figure 4-13: Simplified Control Scheme utilised in DC-link Voltage Regulator                           | . 79 |

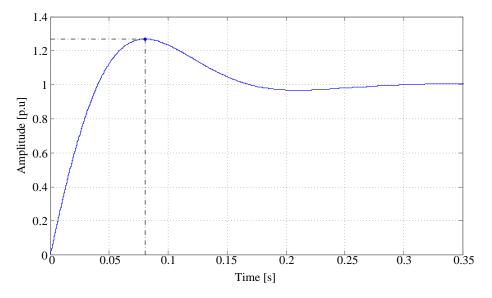

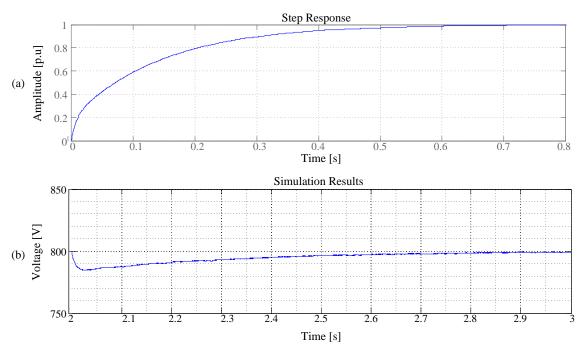

| Figure 4-14: Matlab Step Response of Voltage Control System                                            | . 80 |

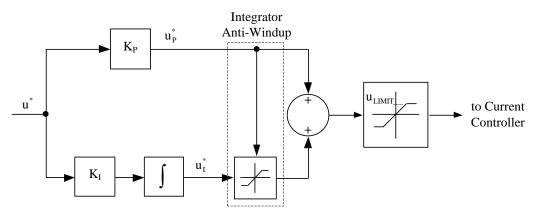

| Figure 4-15: Proposed Integrator Anti-Windup Scheme                                                    | . 82 |

| Figure 4-16: Complete Double-Loop Controller                                                           | . 82 |

| Figure 4-17: Complete Active Rectifier Simulation                                                      | . 83 |

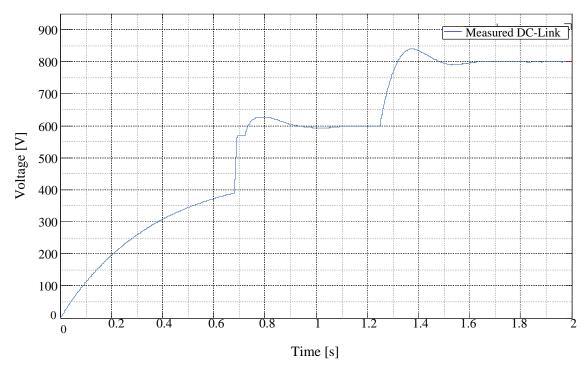

| Figure 4-18: DC-Link Voltage during Active Rectifier Initialisation                                    | . 83 |

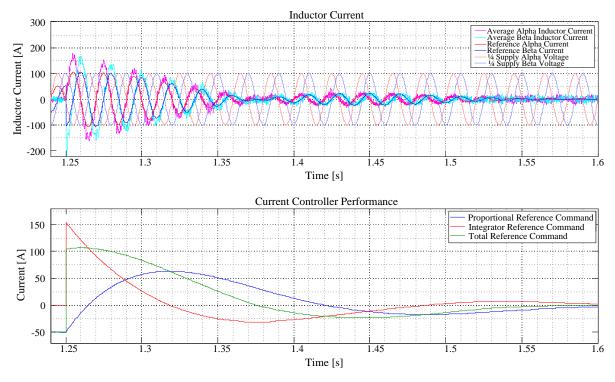

| Figure 4-19: (a) Matlab Step Response with Battery included (b) Simulation Results when connecting     | the  |

| Battery                                                                                                | . 85 |

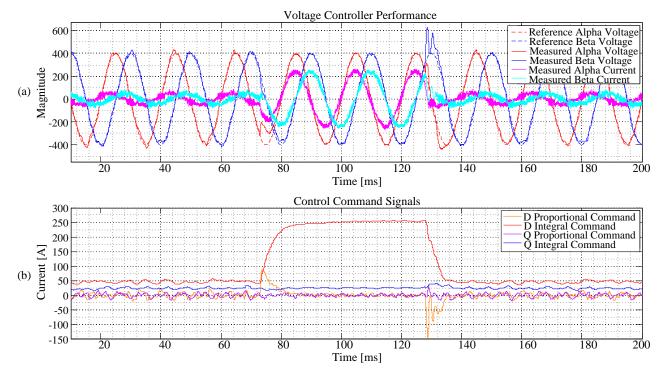

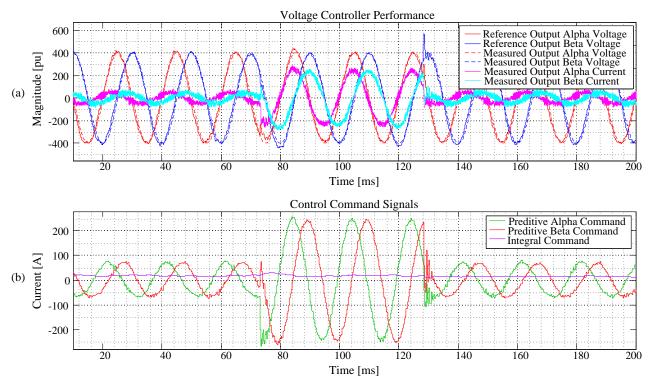

| Figure 4-20: (a) System Signals (b) Voltage Controller Command Signals                                 | . 85 |

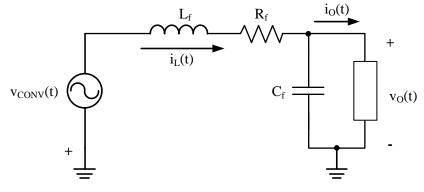

| Figure 5-1: DC-AC Converter of the Line-Interactive UPS                                                                         | 88    |

|---------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 5-2: Focus on Modelling of the VSI Converter                                                                             | 89    |

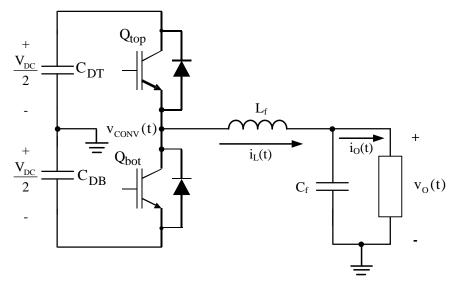

| Figure 5-3: Single-Phase Half-Bridge VSI                                                                                        | 89    |

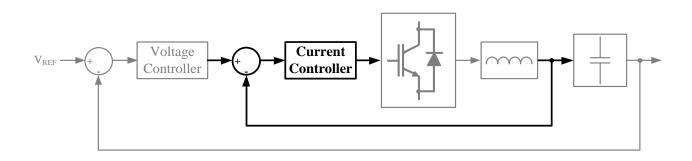

| Figure 5-4: Focus on Current Control of UPS Output Current                                                                      | 92    |

| Figure 5-5: Half-Bridge VSI                                                                                                     | 92    |

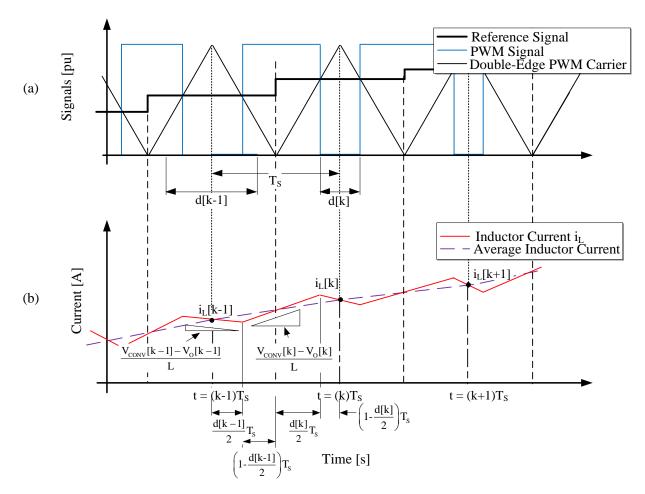

| Figure 5-6: (a) Reference and PWM Signals and (b) Inductor Currents                                                             | 93    |

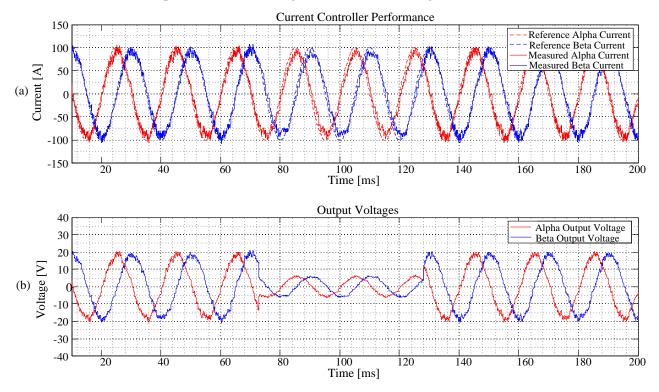

| Figure 5-7: Performance of Current Controller                                                                                   | 95    |

| Figure 5-8: Averaged Single-Phase VSI                                                                                           | 96    |

| Figure 5-9: Average and Instantaneous Signals                                                                                   | 97    |

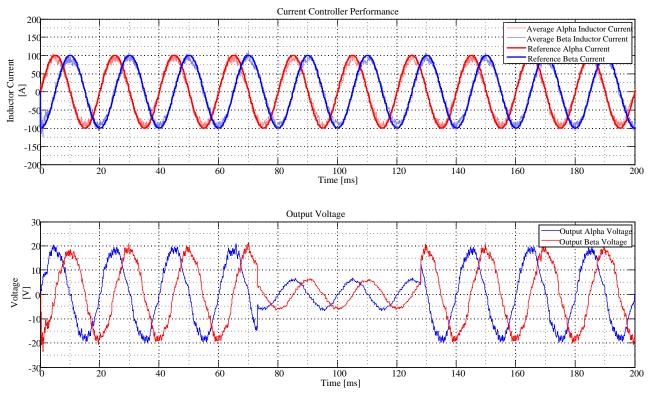

| Figure 5-10: Two-Cycle Predicted Current Controller Performance                                                                 | 98    |

| Figure 5-11: Focus on UPS Output Voltage Controller                                                                             | 99    |

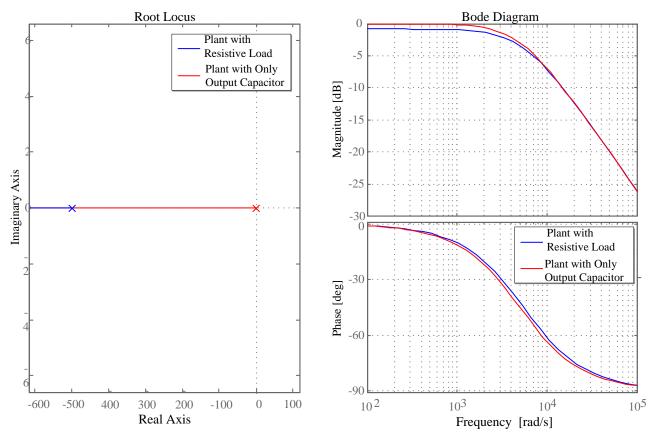

| Figure 5-12: System Root Loci and Bode Plots                                                                                    | . 100 |

| Figure 5-13: Simplorer Simulation Three-Phase Open-Loop VSI Model                                                               | . 102 |

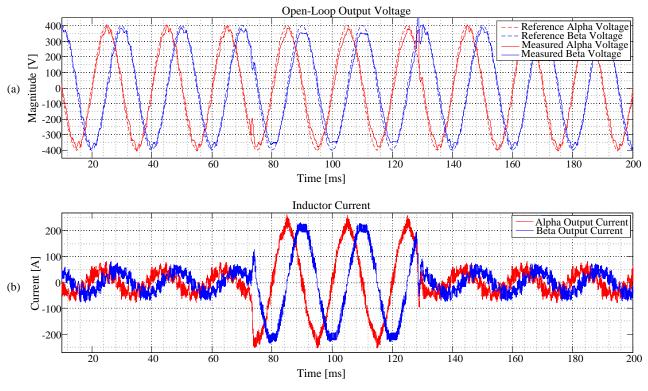

| Figure 5-14: Simplorer Results of Open-Loop Controlled VSI                                                                      | . 103 |

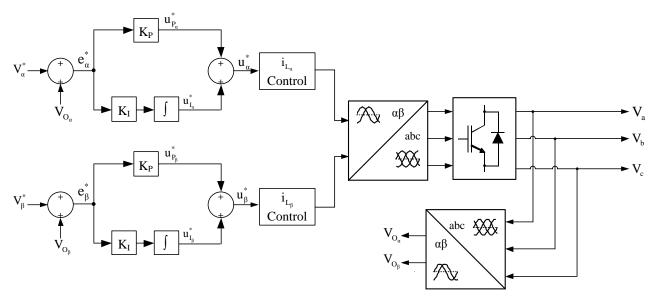

| Figure 5-15: A Simple PI Control Proposal                                                                                       | . 104 |

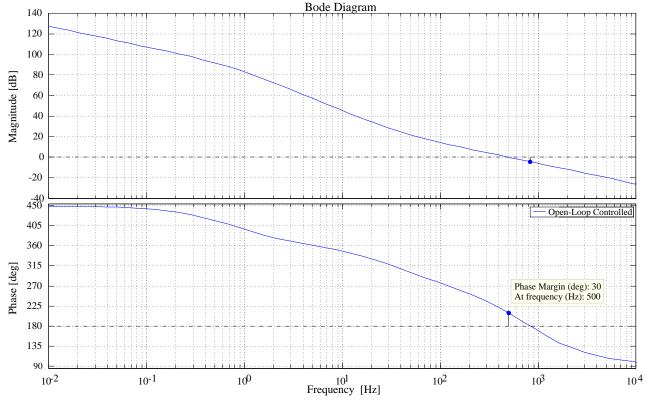

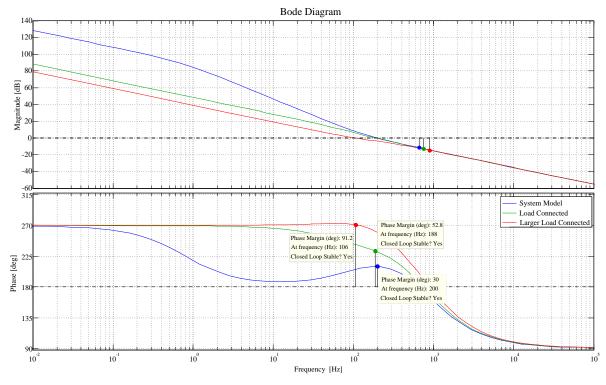

| Figure 5-16: Bode Diagram of Initially Proposed PI Controller                                                                   | . 106 |

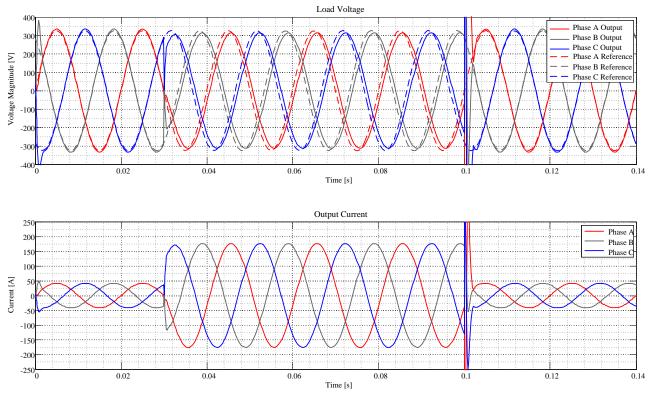

| Figure 5-17: Matlab Simulated Performance Results of Proposed PI Control of $\alpha\beta$ -Voltages                             | . 107 |

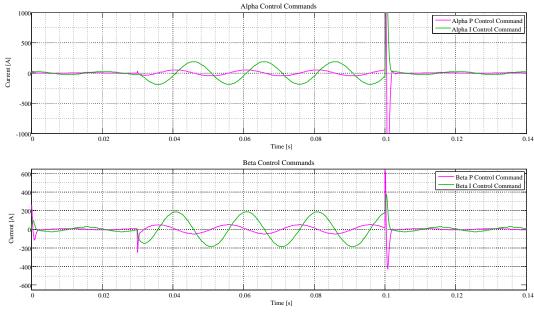

| Figure 5-18: PI Control Commands                                                                                                | . 108 |

| Figure 5-19: Model for Simulation of PI Control of the $\alpha\beta$ Voltages Vectors                                           | . 108 |

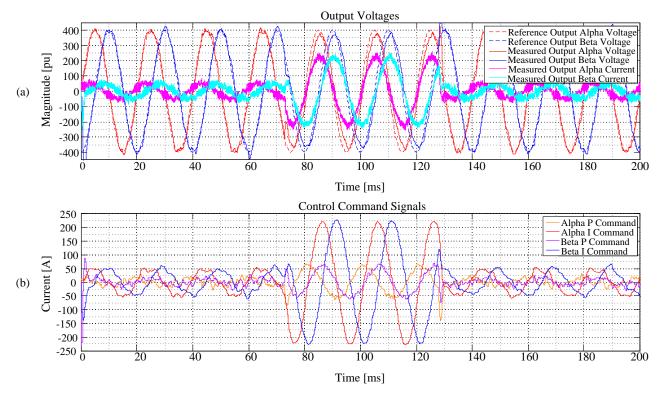

| Figure 5-20: Simplorer Results of PI Control of $\alpha\beta$ Voltages                                                          | . 109 |

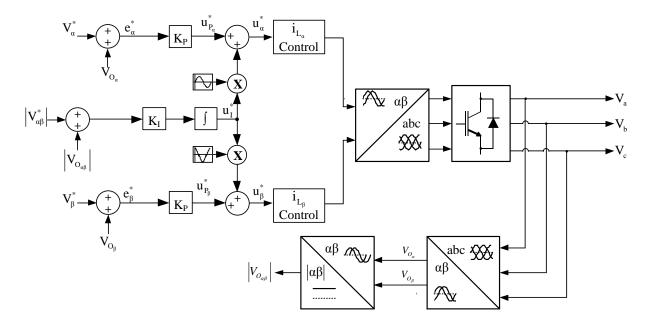

| Figure 5-21: Proportional Control of $\alpha\beta$ Voltage Vectors and Integral Control of $V_{\alpha\beta}^*$ Vector Magnitude | : 111 |

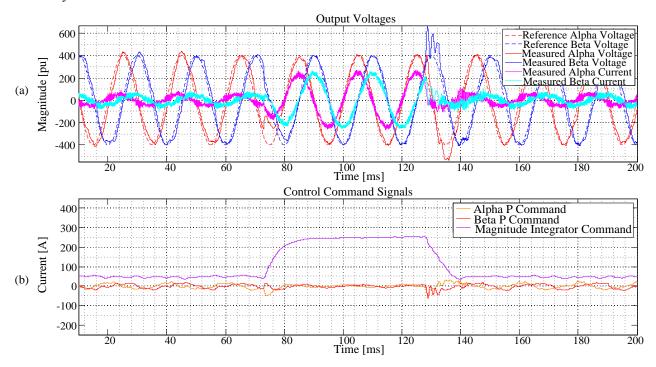

| Figure 5-22: Control Performance of $\alpha\beta$ -Voltage Controller with additional Integral Magnitude Control.               | . 112 |

| Figure 5-23: Bode-Plots of System with Different Load Impedances                                                                | . 113 |

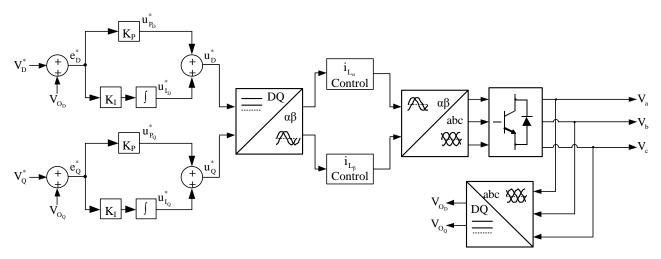

| Figure 5-24: PI Controller based on the DQ Reference Frame                                                                      | . 114 |

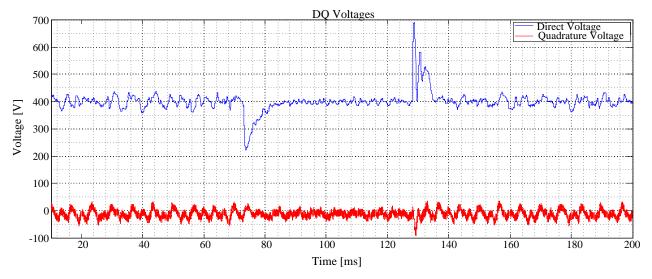

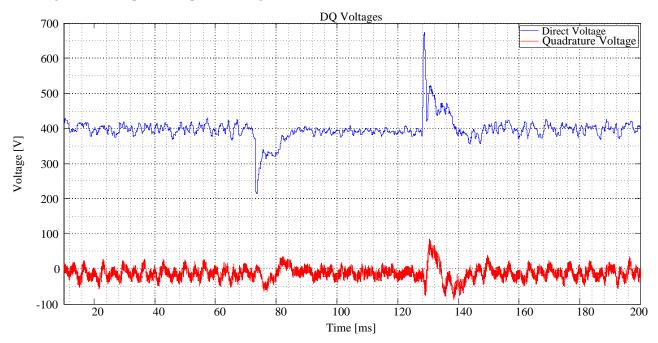

| Figure 5-25: Simulated Direct- and Quadrature Voltages of DQ Controller                                                         | . 115 |

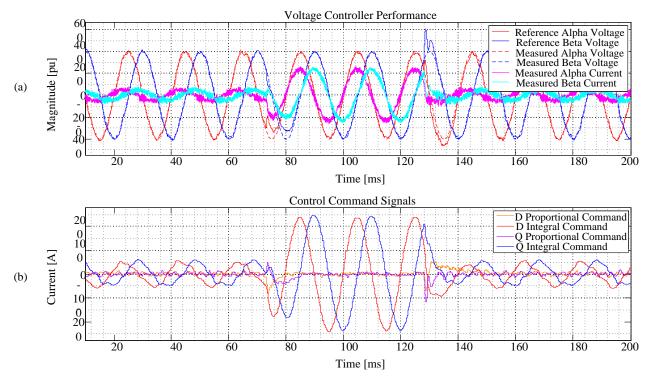

| Figure 5-26: Simulated Performance of PI Control of the D- and Q Voltages                                                       | . 116 |

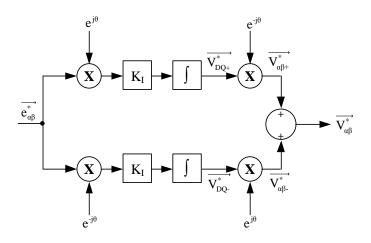

| Figure 5-27: Rotational Reference Frame Equivalent Integrator                                                                   | . 118 |

| Figure 5-28: Simulated D- and Q Voltage of P+Resonant Controller                                                                | . 119 |

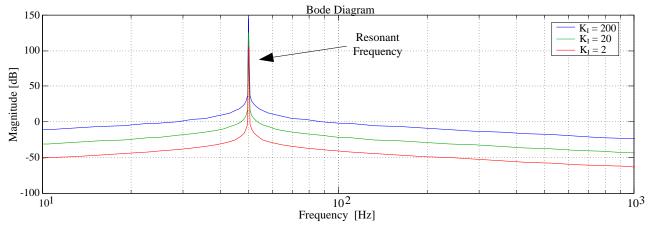

| Figure 5-29: Bode Diagram of Resonant Controller                                                                                | . 120 |

| Figure 5-30: Simulated Performance of P+Resonant Controller                                                                     | . 120 |

| Figure 5-31: Predictive Voltage Controller                                                                                      | . 121 |

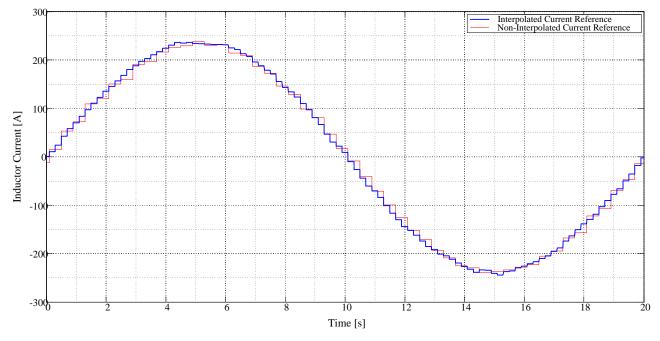

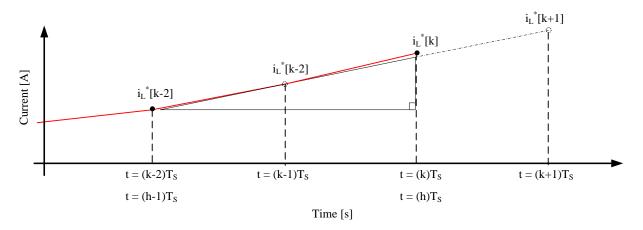

| Figure 5-32: Current Reference Improvement by Interpolation                                                                     | . 123 |

| Figure 5-33: Simple Linear Interpolation Method                                                                                 | . 124 |

| Figure 5-34: Simulated Performance of Predictive Voltage Controller                                                             | . 126 |

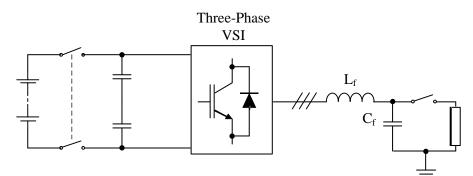

| Figure 6-1: Practical Three-Phase VSI                                                                                           | . 129 |

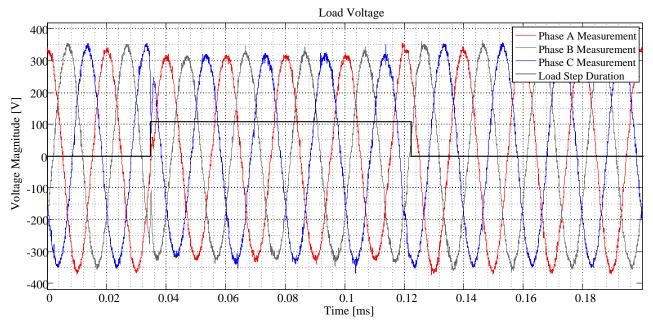

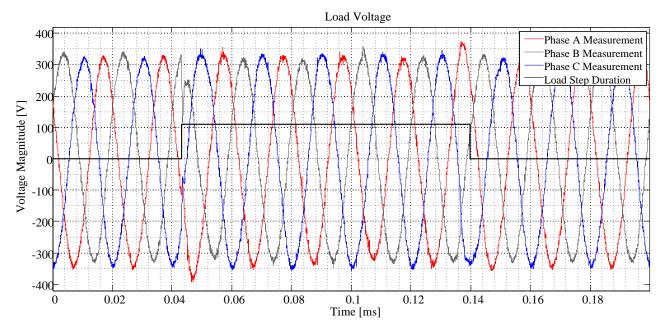

| Figure 6-2: Open-Loop Output Voltage Measurement                                                                                | . 130 |

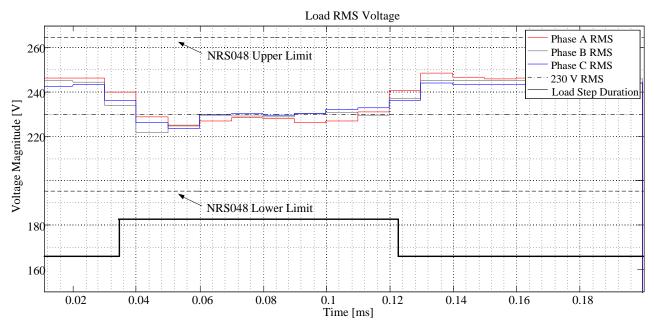

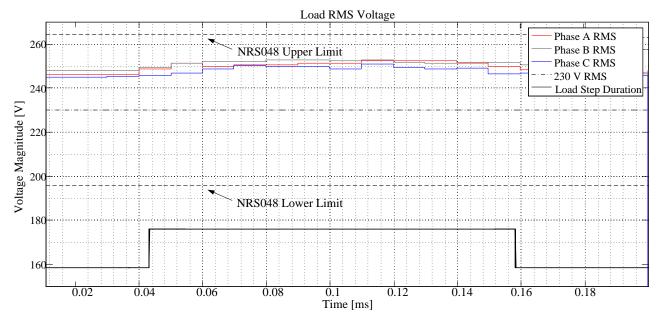

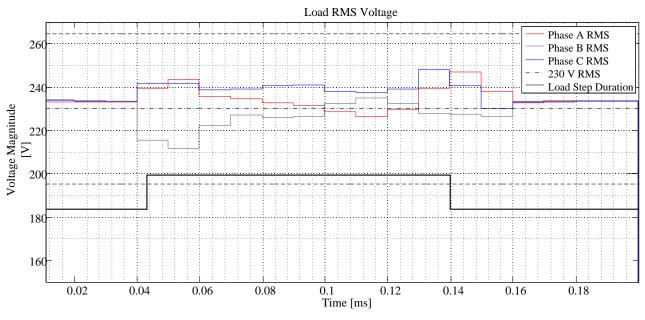

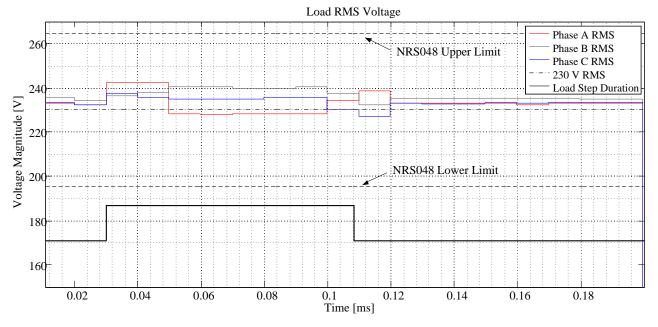

| Figure 6-3: Open-Loop RMS Analysis                                                                                              | . 131 |

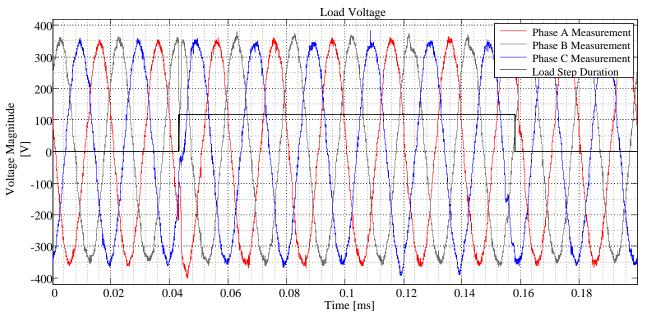

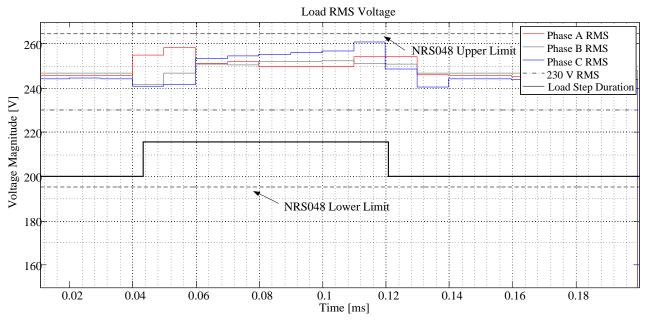

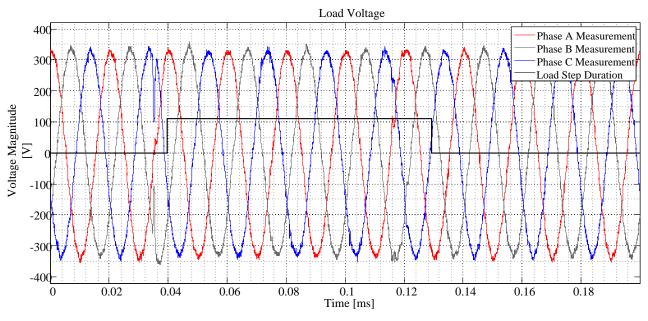

| Figure 6-4: Classical PI Controlled Output Voltage Measurement                                                                  | . 132 |

| Figure 6-5: Classical PI Control RMS Analysis                           | 132 |

|-------------------------------------------------------------------------|-----|

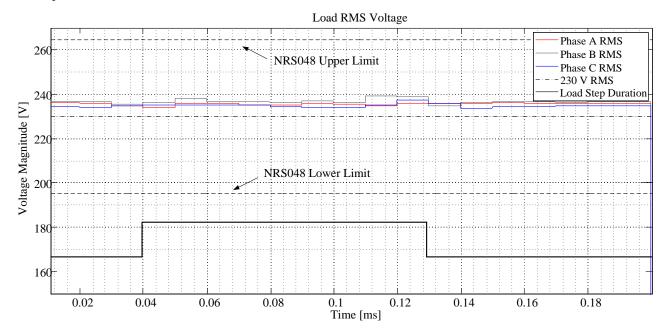

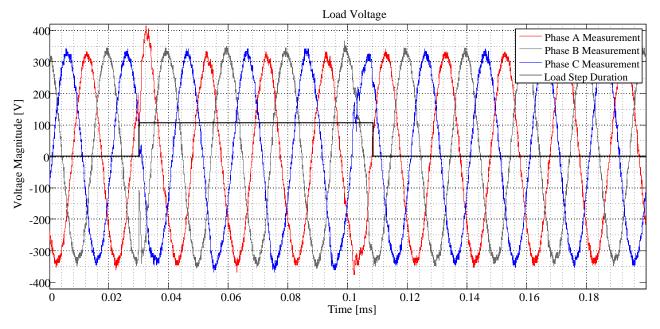

| Figure 6-6: Classical PI Control Alternative Output Voltage Measurement | 133 |

| Figure 6-7: Classical PI Control Alternative RMS Analysis               | 134 |

| Figure 6-8: DQ Controlled Output Voltage Measurement                    | 134 |

| Figure 6-9: DQ Controlled RMS Analysis                                  | 135 |

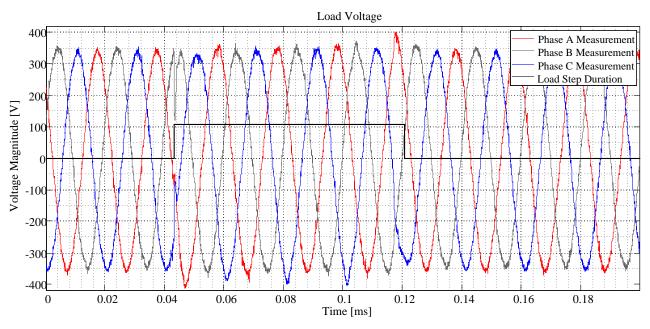

| Figure 6-10: P+Resonant Controlled Output Voltage Measurement           | 136 |

| Figure 6-11: P+ Resonant Controlled RMS Analysis                        | 136 |

| Figure 6-12: Predictive Controlled Output Voltage Measurement           | 137 |

| Figure 6-13: Predictive Controlled RMS Analysis                         | 138 |

| Figure A-8-1: Voltage Measurement Circuit                               | I   |

| Fig A-8-2: Voltage Measurement Circuit                                  | X   |

| Figure A-8-3: Current Measurement Circuit                               | X   |

# **List of Tables**

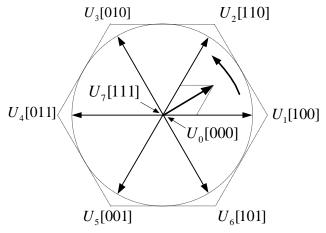

| Table 3-1: Three-Phase Inverter Switching States                                                | 49  |

|-------------------------------------------------------------------------------------------------|-----|

| Table 4-1: AC-DC Simulation Parameters                                                          | 76  |

| Table 5-1: Open-Loop Simulation Parameters                                                      | 102 |

| Table 5-2: Simulation Parameters of PI Controller                                               | 109 |

| Table 6-1: Practical System Parameters                                                          | 129 |

| Table 6-2: RMS Voltage and Tracking Error of Controllers under No-Load and High-Load Conditions | 140 |

# **1 INTRODUCTION**

#### 1.1 Improving the Quality of the Electricity Supply

An inherent part of any country's infrastructure is its electricity supply network. The electricity supplied by the national power utility must comply with numerous requirements. These requirements have been developed over the years and been set out in regulations that specify with which degree of quality the electricity supplied by the utility must comply. Some of these deviations, as discussed by [1] and [2], include over- and under-voltages for a few or more supply cycles, voltage spikes, harmonic distortions, frequency fluctuations and electromagnetic interferences (EMI).

There exist several solutions of mitigating the abovementioned voltage deviation with each having its respective advantages. A tap changer proposed by [3] and an electronic voltage regulator proposed by [4] can be used to compensate for over-and under-voltages. Furthermore, a multilevel converter such as the solid-state transformer as proposed by [5] and [6] assists in the mitigation of transient pollutants like harmonic distortions, voltage spikes, etc. None of these proposals, however, are able to ensure a continued supply of power to the end-user upon the occurrence of a power outage. The uninterruptible power system (UPS) is used to address this shortcoming.

With electrical loads becoming increasingly more technologically sophisticated, there is a growing need for a high quality supply of power from the supply grid. With an ever expanding grid, the risk on components such as transmission equipment is also increasing resulting in the further deterioration of the supply power quality. Traditional power quality mitigation devices like the simple UPS and the active power filter have been used to address power outages, supply harmonics and power factor problems, to name a few. In the following section the low conversion efficiency and unacceptable harmonics [7] generated by certain UPS topologies will pointed out.

It will be shown that the line-interactive UPS does not have these disadvantages if it is appropriately controlled by a good control scheme. The line-interactive UPS is a multi-functional, high-efficiency bidirectional; shunt connected, power quality compensator with a static switching converter [7]. Depending on the digital control scheme, the line-interactive UPS is capable of both active filtering, voltage regulation and dip compensation. Additionally, it is capable of supplying uninterrupted power to the load when the supply voltage deviates outside an allowable limit.

#### **1.2 The Uninterruptible Power System (UPS)**

One of the most important qualities that an electrical utility must have is that it has to be able to supply electrical power that will satisfy the demands of all the end-users of the national grid. It is, however, not always possible to guarantee a constant supply of power to all end-devices.

Numerous solutions have been proposed and developed to ensure constant power supply to an end-user. Some of these include the integration of renewable energy sources like solar photovoltaic power systems or small-scale wind generators in the electrical infrastructure of the end-user. Another popular solution is the installation of a backup generator at the end-user that utilises fossil fuels like gas or diesel. The generator will supply the required power upon the occurrence of a power outage. The problem with this setup is that the generator requires a finite amount of time to initialise before being capable of supplying the power demanded by the end-user. It is during this start up time that the end-devices will be without electrical power. The inclusion of an uninterruptible power system (UPS) at the point of common coupling (PCC)<sup>1</sup> will increase the guarantee that the end-user is provided with a constant supply of power.

In addition to acting as precaution against power outages, a UPS is also capable of mitigating various types of faults and voltage deviations. Depending on the topology of the UPS, as discussed in section 1.3, the UPS is capable of mitigating some or all of the deviations mentioned in section 1.1. Notwithstanding common misconceptions, it is not always required that the UPS instantly provide electrical power once an outage occurs, since the IEC 61000-4 standard [8] specifies a "ride-through" duration that certain types of end-devices have to adhere to.

The manner in which the system controlling the UPS operates, greatly affects the degree to which the UPS is capable of diminishing voltage deviations. The control of the output is generally based on three types of control systems, one being, the closed-loop or feedback controller where the signal supplied by the system is measured and fed back to the controller to diminish any errors made in the waveform. Conversely, the second control system is open-loop control where the controller is unaware of the condition of the signal it outputs. Additionally, the open-loop control system can be augmented by including a path to respond to a disturbance in the system. Such a system is called a feed-forward system. The voltage output quality is generally superior if closed-loop control strategies are employed rather than simply operating the UPS in an open-loop manner. Sudden changes in load conditions can more successfully be dealt with if closed-loop control topologies are used, where the use of open-loop controllers does not necessarily ensure voltage stability under changing load conditions. Nevertheless, high power UPS systems are capable of supplying stable and relatively high quality electrical power to the end-user. It is nonetheless undeniable that the

<sup>&</sup>lt;sup>1</sup> The PCC is defined by [54] as the interface between a source and load in an electrical system.

voltage quality will be affected by the load conditions, since the UPS is incapable of correcting errors in the voltage waveform supplied to the user. On the other hand, closed-loop controllers are capable of removing these voltage errors.

It has been established that the utilisation of a closed-loop control topology will ensure diminished deviations in the voltage supplied by a UPS. It is, on the other hand, extremely difficult for the controller to eliminate these voltage deviations totally. This incapability consequently affects the voltage quality provided by the UPS. Poor quality in the power supplied by the UPS to any end-device can greatly reduce the lifetime of sensitive devices and even cause permanent damage or failure. It is therefore of the utmost importance that the UPS be able to provide power of sufficient high quality to the end-devices under any conditions. It is thus important to investigate the performance of closed-loop strategies in UPS applications.

#### **1.3 UPS Topologies**

According to Sölter [2] and the IEC 62040-3 regulation [9] there are generally three categories of UPS systems:

- Passive-Standby Off-line UPS

- Double-Conversion On-line UPS

- Line-Interactive UPS

The IEC 62040-3 standard [9] has specified that a UPS must provide the load with isolation from as many of the disturbances and faults discussed in section 1.1 as possible. The extent to which the UPS is able to mitigate these disturbances partly depends upon its topology. The different topological classifications will be discussed in the following sections.

When the primary utility is maintained, the UPS system operates in Normal-Mode, whereby it will charge its storage medium. If the primary utility however fails, the system will go into UPS-Mode. During this mode the energy from the storage medium will be converted to provide the load with an uninterrupted supply of power.

#### 1.3.1 Passive-Standby Offline UPS

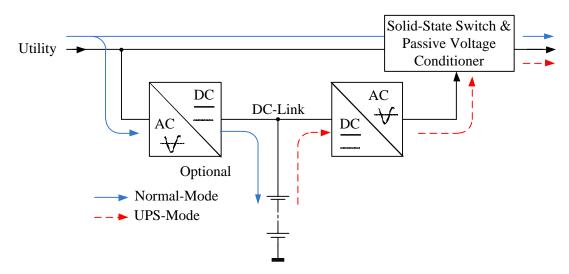

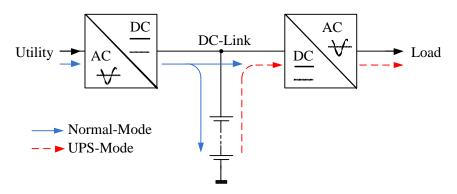

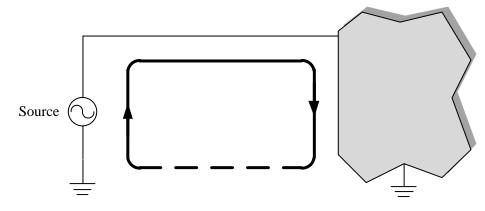

According to Karve [10] the accepted passive-standby offline topology as defined by the IEC 62040-3 standard is illustrated in Figure 1-1.

Figure 1-1: Passive-Standby Topology

This topology has the clear advantage of being a relatively simple design. It utilises either an electronic or electromechanical switch to transfer the supply of power to the load from either the UPS or the utility supply. It is however common that these switches are solid-state switches to ensure quick transition between supply sources. In the event that the utility supply goes outside the specified tolerance range or fails outright, the UPS switch will transfer the supply of power to the inverter. This transition from utility supply to inverter supply has a relatively long duration (usually 10 ms or longer). This might result in the load experiencing a brief loss of power. The long transition is acceptable with certain end-devices that must comply with the IEC 61000 standard that specifies a "ride-through" duration upon the occurrence of brief power failures, but this situation is in general unacceptable for most end-devices. The simplicity of the design is also the great disadvantage of the topology, since it is incapable of effectively mitigating voltage deviations. It is unable to provide isolation for voltage fluctuations that occur on the utility supply.

This topology is a result of a compromise between isolation from voltage disturbances and cost, and is the worst topology to be used for protection from voltage disturbance and faults.

#### **1.3.2 Double-Conversion On-line UPS**

The double-conversion on-line UPS topology employs, as its name implies, two converters. If the graphical representation of this topology in Figure 1-2 is considered, it is clear that a cascaded combination of the two converters is used. This combination provides a highly advantageous condition for the load, where the voltage supplied to the load is decoupled from the voltage supplied by the utility. In other words, any voltage disturbances and/or fault that occur on the utility will not affect the voltage supplied to the load.

Figure 1-2: Double-Conversion On-Line UPS Topology

The advantage of having a decoupled load supply is due to the organisation of the two converters. The AC-DC converter provides a controlled DC-link to be used by the load-side DC-AC inverter. This converter also ensures that the current drawn from the utility is similarly decoupled from the current drawn by the load [11]. In other words, if a pulsating current is drawn from the UPS, the utility-side AC-DC converter ensures that a smooth sinusoidal current waveform is drawn from the utility. Furthermore, the controlled DC-link combined with the stabilising characteristics of the bus capacitors, ensures the effective elimination of any irregularities that occur on the utility voltage.

Unlike the line-interactive UPS (discussed in the following section), the double-conversion on-line UPS is able to operate under conditions with lower-than-nominal utility supply voltage. This means that if a long duration under-voltage situation occurs on the utility supply, the load voltage will be unaffected since power will be drawn from the storage batteries. Another great advantage that this topology provides above a line-interactive UPS topology, is that the load-side converter can be configured to comply with customisable UPS specifications and can even supply voltage at a different frequency than the utility supply. This is definitely not possible with a line-interactive UPS topology. The double-conversion on-line UPS topology however has a few disadvantages.

One of the main disadvantages associated with this converter is that the two converters will operate continuously over the full power rating spread of the UPS. This corresponds with an increase in the converters' temperatures and subsequently a reduced efficiency and expected operating lifetime. The utilisation of two converters in series also increases the complexity of the UPS and moreover implies reduced overall reliability. This increased complexity in the power path increases the probability of failure and a subsequent power loss experienced by the load.

A UPS utilising this topology commonly contains a solid-state bypass switch that is used in the case of extended overload conditions, as pointed out by [11]. It is during the transition to the bypass mode that the power supply to the load will be lost for a few milliseconds. It is important to point out that this is not the case with a line-interactive UPS. Transfer from normal-mode to UPS-mode in a line-interactive UPS does

not correspond with a short duration loss of power to the load. Constant power supply is ensured as long as the UPS load conditions comply with the specifications set out by the IEC 62040-3 regulation [9], [11].

This topology is still commonly used in applications with larger than 10 kVA power ratings [12], notwithstanding the disadvantages associated with this topology. All things considered, this topology provides a means of effectively mitigating most or even all of the voltage disturbances and faults identified in section 1.1.

#### **1.3.3 Line-Interactive UPS**

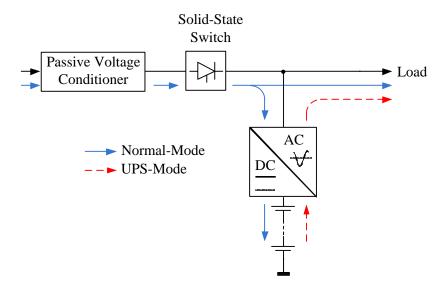

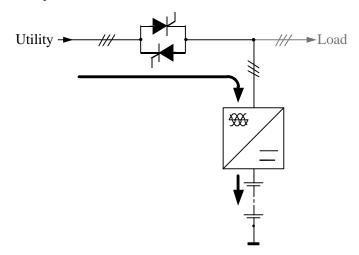

A line-interactive UPS regulates the AC power delivered by the electrical utility to a load and generally consists of one converter. Figure 1-3 depicts the general topology of the line-interactive UPS.

Figure 1-3: Line-Interactive Topology

The line-interactive UPS is incapable of actively suppressing voltage fluctuations and disturbances as successfully as the double-conversion on-line UPS. The voltage conditioner module usually consists of passive components such as surge arrestors or voltage suppressors to mitigate any sporadic voltage disturbances. It is evident that the inverter is permanently connected to the load. This ensures quick to nearly instantaneous restoration of power to the load upon the occurrence of a power outage by the utility. When the power supply is sustained by the utility, the inverter operates as an AC-DC converter, actively rectifying the AC power to charge the storage batteries. Operating the converter in this manner ensures that smooth sinusoidal current is drawn from the utility. The power flow during this mode of operation is usually 10% of the maximum capability of the converter [11]. This ensures the converter temperature is kept low enough for long duration operation. According to [11] a subtle but important aspect of a line-interactive UPS is that while it conditions the voltage supplied to the load, it does not alter the wave shape of the current drawn by the load. This topology also ensures the continuous regulation of the voltage supplied to the load. When an over- or under-voltage condition is experienced by the load, the UPS is able to change the flow of power to

the load from the batteries via the inverter. In conjunction with the power supplied by the utility, this eliminates single-point failure and thus guarantees two independent power paths [12].

In conclusion, the line-interactive UPS topology provides sustained power to load upon the event that the utility supply fails. The sustained power is ensured by utilising only one converter which implies a reduced cost and complexity when compared with the double-conversion UPS topology.

#### **1.4 Problem Statement**

The ultimate goal of the closed-loop controller in UPS applications is to control the transient behaviour of the output signal effectively. The aim is to achieve sinusoidal output transient behaviour. The controller might be unable to achieve this sinusoidal waveform effectively, due to discrepancy between the actual condition of the system and how the controller perceives the system to be.

One, among many, of these discrepancies may be the incorrect or inaccurate modelling of the system. Inaccurate modelling can make the difference between the control of a single three-phase system and the control of three independent single-phase systems. These systems have their similarities, but there are definitive behavioural differences. For example, the model for a single three-phase system will be different than three single-phase systems, because the three phases are dependent on each other in a single three-phase system. This is however not always the case with three single-phase system. It is possible to independently operated the three phases. There are cases in the single three-phase system when the three phases can be operated independently from each other and will be further discussed in section 3.2 where the Park transform can provide a means on independent operation for balanced systems.

Inaccurate circuitry used for the measurement of the voltages and currents can also degrade the controller's performance. Additionally, the performance of the analogue-to-digital (ADC) can also greatly affect the controller performance, since this produces the digital representation of the analogue signal used by the controller. An error made in either of these systems will result in incorrect signals being fed back to the controller and consequently resulting in an inaccurately controlled system. This is the case for all digitally implemented closed-loop control systems.

The above-mentioned discrepancies have to be kept in mind when a digital closed-loop control system is designed. To achieve the best possible controller performance, these systems have to be analysed in an attempt to reduce the negative effect they have on the system as a whole. Additionally, the design and implementation of a closed-loop control strategy that will be capable of providing sufficient performance under all load conditions, needs to be investigated.

Introduction

#### **1.5 Thesis Objective**

The objective of this thesis is to investigate the digital control of a line-interactive UPS. Firstly, the sources that cause degradation of the controller performance are identified. Due to the quantifiable effect that the data acquisition system has on the controller and its performance, it is deemed necessary to make an in-depth analysis of each respective degrading component. The manners in which voltages and currents can be acquired are examined and the best options for line-interactive UPS applications being identified. Additionally, the candidates for the electronic measurement of the voltages and currents are identified. Their advantages and disadvantages will be discussed resulting in the optimal choice of measurement circuit for the applicable UPS topology. The influences of environmental conditions like EMI, ground loops and other sources of noise are identified, discussed and recommendations are made on how to minimise the susceptibility to these noise sources. Furthermore, numerous analogue-to-digital methods are considered with the aim of concluding which method will result in the best performance of the controller. Likewise, the various switching schemes are examined and an optimal combination of ADC and switching scheme is chosen.

Secondly, an investigation is done on digital control strategies. The emphasis of this thesis is on the regulation of the voltage produced by the line-interactive UPS. Ohmic law states that the current through a load is directly proportional to the potential difference across the terminals of that load. Consequently, current control strategies are also further examined to achieve higher voltage regulation performance.

#### **1.6 Structure of this Thesis**

In this chapter the main contributors that corrupt the quality of the voltage supplied by a national utility, was mentioned. A few methods were mentioned that are used to mitigate some of these voltage pollutants. The UPS was introduced as a means of providing uninterrupted voltage supply to a load in the case of the utility supply failing. In this chapter the predominant topologies used in UPS systems, were listed and their classification according to the international IEC 62040-3 regulation [9] was discussed. The problem statement was given and it was identified that the focus of this thesis is on the control of the voltage supplied by the UPS. It was also mentioned that a digital controller is required to achieve sufficient control of voltage.

In chapter 2 the development and design of the analogue circuits and electronics that are used to enable the implementation of the control strategies incorporated into the digital controller, is discussed. The control hardware requires numerous voltages. Common sources of noise and the compromises the system's noise immunity are identified. A power supply structure is subsequently developed that is the least susceptible to environmental noise and electromagnetically induced disturbances. A study is made of different measurement topologies where each topology's advantages and disadvantages are discussed. The most

popular ADC architectures are furthermore also discussed in chapter 2, since the ADC can greatly influence the accuracy of the digital controller.

The switching converter in the line-interactive UPS functions both as an AC-DC converter and a DC-AC converter. In chapter 3 a dead-time compensation scheme that are common to both the AC-DC and DC-AC converters are discussed. The discussed theory includes the discussion and derivation of the Park and Clarke transformations. In the subsequent chapters 4 and 5 uses all the material discussed in chapter 3 and the dead-time compensation scheme are employed along with all the control schemes derived in these chapters. A literature study on the different control topologies and types is also supplied.

In chapter 4 a closed-loop control scheme to control the inductor current when the line-interactive UPS operates in standby mode is provided. It is during this mode that the utility supplies power to the load and the UPS charges its storage batteries. A regulation algorithm is also derived to regulate the DC-link during this mode of operation.

When the utility supply fails the UPS system supplies power to the load from the storage batteries. In chapter 5 a model of the UPS system that is used in the subsequent design of the current- and voltage controllers, is derived. Two closed-loop current controllers for regulating the inductor current during this mode of operation are discussed and several voltage control algorithms are also developed and further discussed. The necessary literature study required for the derivation of the controllers is incorporated in this chapter. Simulations are done and the results are analysed to gauge the controllers' capability.

In chapter 6 an experimental investigation into the performance of the voltage controllers developed in chapter 5, is provided. Each voltage controller's performance is evaluated and compared with the requirements set out by the national NRS 048 regulation [13].

# **CHAPTER 2**

## DEVELOPMENT OF THE CONTROL HARDWARE

### **2 DEVELOPMENT OF THE CONTROL HARDWARE**

#### **2.1 Introduction**

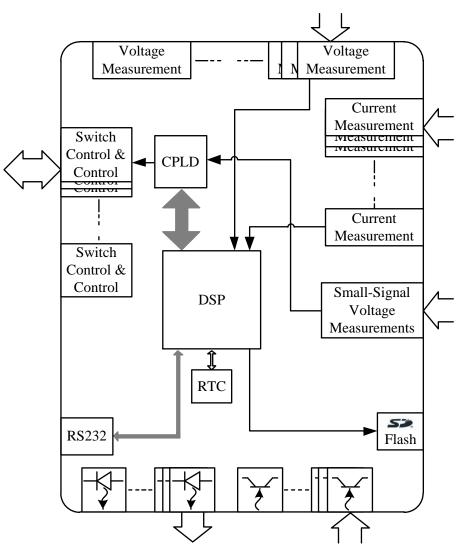

To be capable of digitally controlling a line-interactive UPS, a central controller is required. The controller must be able to sense the current operating status of the UPS system and also provide closed-loop control of both the currents and voltages in the unit. The control schemes described in the subsequent chapters can then be implemented in the digital system.

In this chapter the development of the digital central controller of the UPS system is discussed. At the core of the controller is a digital signal processor (DSP). A very important attribute of the DSP is its floating-point arithmetic-logic-unit (ALU). The floating-point ALU opens the door to the implementation of several control schemes that were not possible with fixed-point ALUs. A floating-point ALU is capable of computing several complex calculations at a much faster rate than a fixed-point ALU. Calculations are done synchronously on the DSP. It is therefore important that all calculations need to be executed before the next calculation cycle commences. The advantage gained from having a floating-point ALU at your disposal is that more complex calculation can now be implemented without the concern that their execution will overrun to the next calculation cycle.

A study is also done on the several means of improving the digital control capability of the system. It was found that the means by which the digital system acquires the analogue signals of a UPS system can be a source of numerous anomalies and disturbances.

These sources of disturbances range from the circuitry used for the measurement and conditioning of analogue signals to the digitisation of these signals. A study on most of the methods whereby the quality and performance of the digital controller can be improved is also provided.

The DSP will not only be used for the closed-loop control of the system's voltages and currents but will also be capable of controlling the system as a whole. The various components that make up the controller will be discussed and it will be explained how each contributes to achieving control of the system. Additionally, the DSP provides a means of communicating with a human-machine-interface (HMI) through a simple RS232 protocol and is even be able to log all relevant data on a non-volatile memory unit such as a Secure-Digital (SD)-card.

#### 2.2 Analogue-to-Digital Converter

It is evident that to achieve effective and accurate control of the UPS voltages and currents, it is imperative to have a very accurate measurement of a signal at the exact time instant that the controller requires that signal. In the case where a controller is digitally-based the analogue-to-digital converter (ADC) is required to reproduce a digital representation of the analogue measurement. However, due to real-world irregularities and the fact that every operation has a finite duration, it is not possible to acquire this digital representation instantaneously.

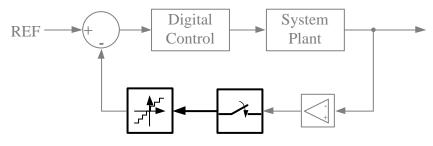

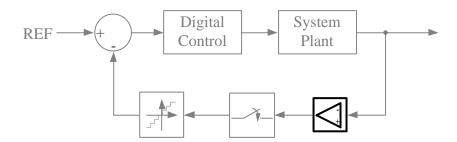

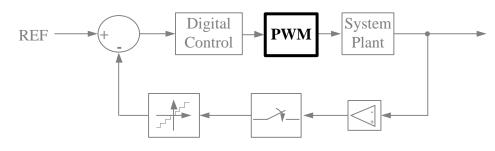

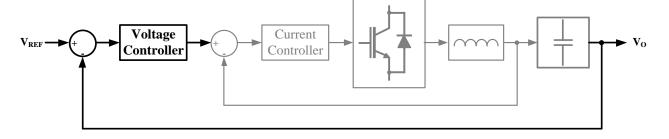

The functionality and operation of the ADC process therefore needs to be investigated to determine the best ADC solution that will ensure optimal performance of the digital central controller. Figure 2-1 depicts typical closed-loop control topology and shows that the emphasis of this section is on the discretisation of the analogue signals of a system.

Figure 2-1: Focus on Discretisation of Analogue Signals

As the name implies, an ADC is a component which serves the function of converting an analogue signal to a numerically equivalent digital value. There are different techniques according to which this conversion is done, each having its respective advantages and drawbacks. For example, a certain technique will provide a high sampling rate but at the expense of accuracy. It is therefore important at least to possess a basic understanding of the ADC and the operation of the different conversion techniques to determine how to obtain a digital representation of the analogue signals in the UPS system.

#### 2.2.1 Basic Operation

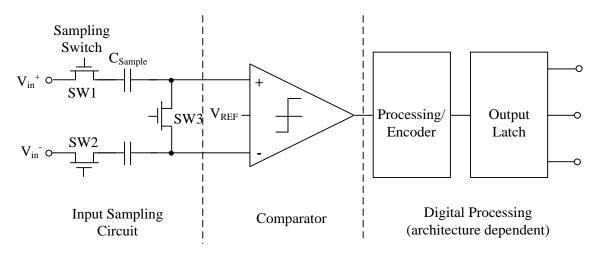

The greater majority of ADCs are based on the same generic structure. This structure can be considered in Figure 2-2, where the analogue signal is acquired by means of a sampling circuit, which is subsequently used by a comparator optimised for ADC purposes to obtain a digital equivalent of the sampled analogue signal. Thereafter, the data is processed depending upon the type of architecture on which the ADC is based. As can be seen, there is a logical flow between these processes. These processes will forthwith discussed briefly.

Figure 2-2: Generic ADC Structure

#### **Input Sampling Circuit**

This portion of the ADC, in conjunction with the accompanying comparator, in essence serves as the sampleand-hold amplifier (SHA) of the ADC. The structure of the input sampling circuit varies in complexity depending on the architecture in which it is utilised. For example, an additional resistor may be included in series with the sampling capacitor  $C_{sample}$  to control the rate at which this capacitor is charged. It is important to note that the source of the analogue signal must be able to charge this capacitor to a settling level accurate to the bit-resolution of the ADC, e.g. for an ADC with a 12-bit resolution and an analogue input range of 5 V, this capacitor must be charged to an accuracy settling level of 1.22 mV. This level is obtained by using equation (2.1):

$$V_{LSB} = \frac{V_{FSB}}{s^{N}}$$

(2.1)

with  $V_{LSB}$  being the equivalent voltage of the Least-Significant-Bit,  $V_{FSB}$  being the analogue full-scale voltage range of the ADC and N indicating the bit-resolution of the ADC. It is also common in the design of modern ADCs to include additional functionality to the ADC. For instance, it is highly desirable to reduce the effects of noise in the resulting digital value produced by the ADC. Noise will have a tremendously adverse effect on the input sampling circuit and it is desirable to include additional noise filters in the circuit.

The input sampling circuit has two functional modes: sample-mode and hold-mode. The sample-mode is the acquisition phase where the analogue signal is obtained. During this mode, the solid-state based switches SW1, SW2 and SW3 are closed, resulting in the series connecting and consequent charging of the sampling capacitors. During the hold-mode, the conversion phase is initiated where all the switches are open and the comparator measures the differential voltage at its input. This differential voltage is held stable by the sampling capacitors for the duration of the conversion phase. A general design habit is to place an additional capacitor on the input of the ADC to facilitate the sampling of the analogue signals and improve the dynamic performance of the ADC.

As distinguished by [14], the structure of the input sampling circuit is categorised as having either a singleended, pseudo-differential or fully-differential structure. Sections 2.3.1 to 2.3.3 provide a brief discussion of these different structures.

#### Comparator

The analogue-to-digital conversion process is not possible without the aid of a comparator. It is here that the analogue signal is converted to a digital format. This makes the comparator an integral part of the ADC and closer attention to its operation in the analogue-to-digital conversion process is therefore merited.

The basic function of a comparator is to produce a logic output signal based on its differential input. In ADC applications, the comparator compares this differential input with a reference voltage, which can be generated internally or provided by an external reference circuit. A common problem experienced with the comparator is that the output tends to oscillate when the differential input magnitude is very close to the reference voltage. The comparator is subsequently unable to produce a definitive logic output state. According to Kester in [15] the comparator is then in a so-called "metastable" state. This oscillation will eventually settle, but will result in the corruption of the converted value for that instant in time.

These oscillations cause errors that are known as "sparkle codes" and account - to a small extent - for the quantisation errors experienced with ADCs in general. The comparator is designed with a small hysteresis band at the threshold between logic states to prevent instability in the transition region and to counteract this oscillatory operation. Comparators used in ADC applications additionally utilise a built-in latch at the input of the comparator which improves their performance as sampling devices.

The latch at the input of the comparator locks the output in the logic state it was in at the instant it was enabled, allowing the sampling of very short duration analogue signals, and holds the signals for further processing. Due to the fact that the latching occurs on the input signal of the comparator, this ensures miniscule sampling delay. Since the output of the comparator is determined by not only the differential signal provided by the input sampling circuit but also on the reference voltage, it is evident that this reference voltage must be as accurate and devoid of noise as much as possible. Any disturbances on either the differential input or the reference voltage will result in the irrecoverable corruption of the signal used in the digital processing portion of the ADC.

#### **Digital Processing**

The analogue signal that was sampled by the input sampling circuit and thereafter discretised by the comparator needs to be interpreted and processed into a usable digital format such as a binary code or twos complement code. This is done in the digital processing portion of the ADC and directly determines the major characteristics of the ADC. Characteristics such as the sampling rate, throughput rate, accuracy,

latency and even power consumption. Due to the vast different techniques of digital processing, the ADC family has been divided into different architectures. In other words, the architecture of an ADC determines the manner in which the data is processed. The architecture of an ADC not only determines the digital processing technique, but also branches out to the other portions of the ADC structure. The structure of the input sampling circuit can differ from one architecture to another. Furthermore, the architecture even determines whether only one comparator is used in an ADC or numerous comparators are utilised to facilitate parallel processing.

There are numerous ADC architectures. The following architectures will be considered in this study:

- Direct Conversion or Flash

- Pipelined Sub-Ranging

- SAR

The motivation for only considering these architectures is the fact that these are the most commonly used in power electronic applications. Most other architectures are either based on one of the above-mentioned or are hybrids between the above architectures.

#### 2.2.2 ADC Architectures

To change the technique an analogue signal is converted, the manner in which the different sub-components are arranged and how they interact with each other need to be changed physically. These differently organised layouts are called ADC architectures. These architectures are further investigated in the subsequent sub-sections.

#### 2.2.2.1 Direct Conversion/ Flash

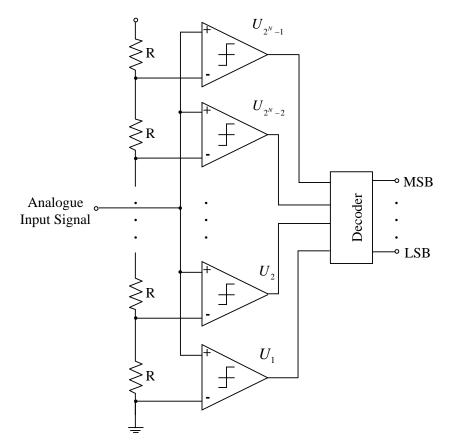

This architecture is commonly known as the flash architecture but is also called the parallel [16] or the direct conversion architecture [17], because this architecture directly converts the analogue signal to a digital value. It does not utilise complex manipulations and techniques to convert the analogue signal. This architecture is based on the cascaded arrangement of a vast number of comparators that are optimised for ADC applications as discussed in section 2.2.1.

As seen in Figure 2-3, these comparators are used for the analysis of a certain portion of the analogue signal. For an N-bit converter there are  $(2^N - 1)$  comparators and a resistive-divider string consisting of  $2^N$  resistors provides the reference voltage for each comparators.

Figure 2-3: Flash Architecture Structure

The reference voltage for each comparator is 1 LSB (determine with equation (2.1)) greater than the reference voltage of the comparator immediately below it. The comparators, subsequently produce output codes which are processed and latched out as a binary numeral. Due to the high parallelism provided by the flash architecture, it is capable of extremely high sampling rates. With an increase in sampling rate, the power dissipation likewise increases. It is discernable that with an increase in bit resolution the number of comparators and resistors greatly increase. This results in an increase of die real-estate and also much higher power usage. It is due to these rapid increases that flash architectures based ADC are constrained to applications requiring relatively low bit resolution but that still necessitate high sampling rates.

However, the flash architecture is still the fastest ADC architecture on the market, capable of achieving sampling rates in the Giga-samples per second range [15]. It is thanks to this great speed that the flash-architecture serves as the stepping-stone for the development of the modern pipelined sub-ranging architecture.

#### 2.2.2.2 Pipelined Sub-Ranging

Also known as sub-ranging quantisers [17], the pipelined architecture takes over where the flash architecture is unable to deliver. This architecture has the same advantage as the flash architecture in that it is capable of very high sampling rates, but does not have the drawbacks associated with the flash architecture. Admittedly,

the flash architecture provides extremely high sampling rates but it comes at the price of low resolution and high power consumption. The pipelined architecture does not have these drawbacks. On the contrary, ADCs based on the pipelined architecture are capable of high bit resolutions (12-bit to even 24-bit) along with similarly flash-equivalently high sampling rates (100 MSPS and more) at relatively low to moderate power dissipation ( $\approx$ 400 mW). Note that there is an inversely proportional relationship, albeit a weak relationship, between the resolution and the sampling rate of a pipeline-based ADC. In other words, with a drastic increase in resolution accuracy, the sampling rate capability of the ADC will slightly decrease. Still, how this architecture achieves all of these phenomenal advantages is based on its unique approach to parallel processing of the analogue signal.

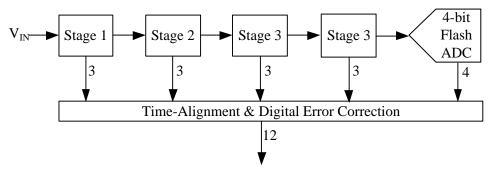

The term pipeline is coined by [18] as the ability of one stage to process data from the previous stage during any given phase of the sampling clock cycle. The alias of this architecture, sub-ranging, more clearly defines this architecture as dividing the input signal into a number of smaller ranges (sub-ranges) which are, in turn, further subdivided [18]. In other words, the design is based on dividing the sampling of the analogue signal across multiple stages with each stage employing a flash ADC to convert a certain bit-range part of the input signal. This is shown in Figure 2-4, where, for illustrative purposes, a pipelined structure for a 12-bit ADC is employed. As seen in this figure, the conversion process starts with the input signal being converted in Stage 1.

Figure 2-4: Pipeline Architecture Overview

A single stage is depicted in Figure 2-5 and shows how a pipelined architecture utilises the flash ADCs consequently ensuring high sample- and throughput-rates in a 12-bit ADC. Every stage samples the analogue signal accurate to, say, 3-bit accuracy which is converted with a digital-to-analogue converter (DAC) back to an analogue signal which is accurate to 12-bit resolution. This is subtracted for the original sample with the purpose of determining the error made during the conversion process. This error is subsequently gained by a factor of, in this case, 4 and sent to the following stage where the same process will be executed. It is important to note that the different stage can be different bit-resolution ADC. This process is repeated depending on the design choices of the manufacturer, until finally at the last stage the residue from the preceding stages are converted by an ADC with a slightly higher resolution accuracy.

Figure 2-5: Single-Stage Pipeline Diagram

The capability of the pipelined architecture to achieve parallel conversion of numerous samples is thanks to the property of each stage to commence with the next available sample immediately once it has completed quantisation of the sample it has currently been busy with. This parallelism yields high sampling rates and great throughput rates in the pipelined architecture [19].

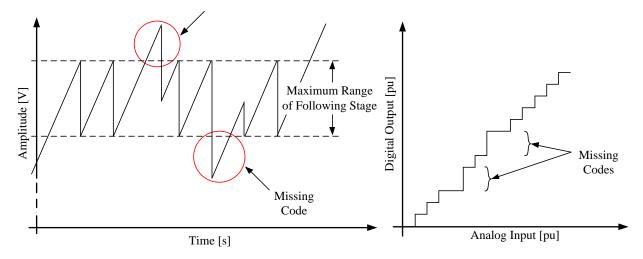

To produce a digital output which is accurate to the bit-resolution of the specific ADC it is necessary to timealign the converted results from each respective stage. This is achieved by using a sample-and-hold to store the data from each stage in shift registers. In conjunction to the time-alignment between the different stages, the output from a preceding stage is also adjusted to ensure optimal alignment for utilisation of the succeeding stage. This is achieved by amplifying the residue signal (see Figure 2-5) produced by the DAC from the preceding stage occupies the full-scale of the analogue input range for the following stage. Finally, a digital error correction algorithm is employed to correct for errors due to misalignment between the stages [19]. Such a misalignment is depicted in Figure 2-6 in the case when a ramp analogue signal is input to the ADC. This misalignment occasionally occurs when the residue signal is larger than expected, resulting in the analogue signal input to the following stage being larger than the maximum analogue range of that stage. The ADC is subsequently unable to produce a digitally equivalent value, which gives rise to the missing codes shown in Figure 2-6.

Figure 2-6: Illustrating Inter-Stage Misalignment

Any errors made due to the abovementioned misalignment are however corrected with a digital error correction algorithm by adding extra quantisation levels in the region where the residue signal has exceeded the maximum analogue range.

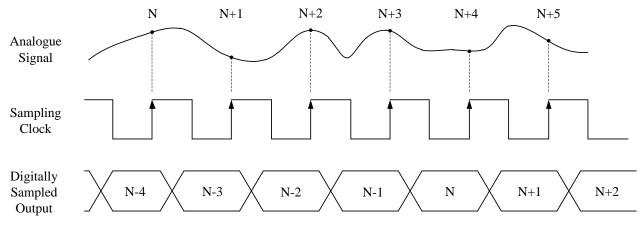

This necessity to ensure optimal alignment in time and alignment of the signal amplitudes gives rise to the delay in the production of the final digital output. This delay is known as latency (or pipeline delay) and is one of the main characteristics for which this architecture is notorious. Figure 2-7 illustrates this latency making it clear that the digital output of the ADC is time delayed with respect to the analogue signal it is sampling. The sample-and-hold used between stages to achieve time-alignment of the respective digital results operates on the sampling clock of the ADC. The latency thus is a function of the number of stages employed in the ADC and the cycle duration of the sampling clock. Consequently, the latency is always defined as an integer multiple (which is determined by the number of stages) of the sample clock duration. It is therefore clear to see that the latency can be reduced by either reducing the number of stages employed in the ADC or by greatly increasing the sampling clock rate.

Figure 2-7: Illustrating Pipelined Latency

As discussed at the beginning of this section, the goal is to reduce the conversion duration of the ADC and conclusively it is clear that the pipelined architecture is able to produce the required high sampling rate. This architecture is nonetheless too fast for the current DSP currently being used. There is also not a way of effectively synchronising the measured values with the rest of the system. If the DSP is used to drive the ADC, the current DSP technology limits the capability of the DSP to produce a sampling clock that operates at such high frequencies.

Synchronisation between the DSP and the ADC is therefore very difficult and even impossible. DSP technology only recently progressed to the point where synchronisation at moderately high frequencies can become possible, but the DSP used in this project does not have that capability.

The utilisation of an ADC with such high sampling rates is generally unnecessary in typical power electronic applications. The switching frequency of the converter is usually at a low frequency (in the range of a few kilohertz) relative to the sampling frequency of pipelined ADCs. Sampling at such high frequencies would only seem viable if oversampling of the signals need to be employed.

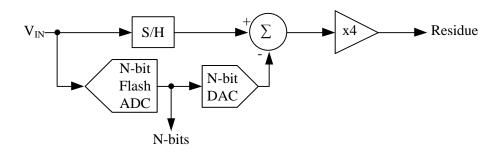

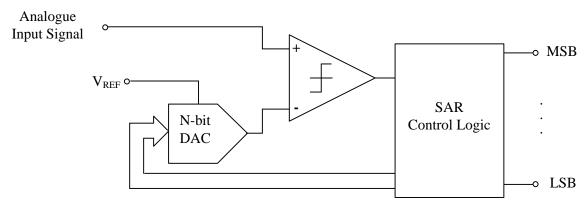

#### 2.2.2.3 Successive Approximation Register (SAR)

This architecture employs a conversion technique which is also known as the bit-weighing conversion technique. The general structure of the SAR architecture can be seen in Figure 2-8 and it can be seen that it employs only a single comparator.

Figure 2-8: Basic SAR Structure

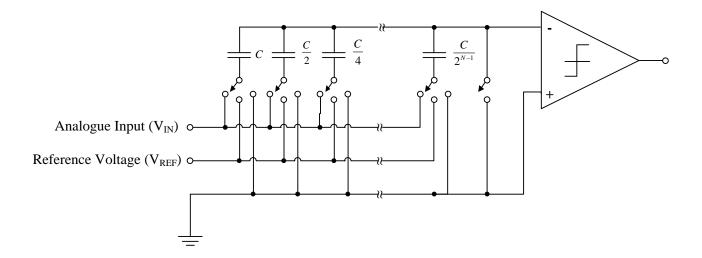

Employing only a single comparator greatly reduces the overall complexity and component count of ADCs based on this architecture. Another advantage is that there is very low power dissipation and that only a small amount of real-estate is used on the die. The method of conversion employs a binary search algorithm by comparing the analogue signal with a signal produced by an N-bit DAC [17]. The signal produced by the DAC is determined by the reference voltage,  $V_{REF}$ , and the commands received from the SAR control logic. It is common practice to use a capacitive-DAC [20] because it has an inherent track-and-hold functionality. As explained by [20], [21] and [22], the capacitive DAC employs an array of N capacitors, with each capacitor having a binary weighted, ie C,  $\frac{C}{2}$ , ...,  $\frac{C}{2^N-1}$  capacitance values with N being the bit resolution of the ADC. The use of capacitors enables the utilisation of charge redistribution in the conversion process and has the added advantage of providing more precise matching of the component values.

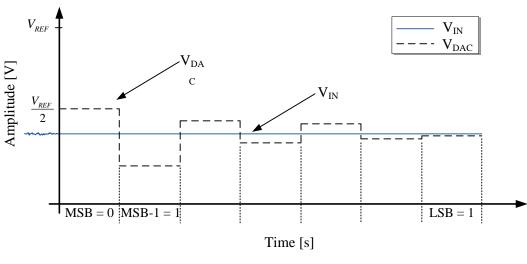

The conversion process is illustrated in Figure 2-10, which shows a typical capacitive DAC utilising a capacitor array to apply the principle of charge redistribution. When the analogue signal is acquired, the inverting input terminal of the comparator is connected to ground and all N capacitors are connected to the analogue input signal. After this acquisition phase, the inverting input is disconnected from ground and all the capacitors are disconnected from the analogue input. This effectively captures a charge in the capacitor

array which is proportional to the analogue input,  $V_{IN}$ . Thereafter, the capacitor array is connected to ground, resulting in the non-inverting input of the comparator being biased at  $-V_{IN}$ . The binary search algorithm commences by disconnecting the capacitor that represents the MSB, from ground and connecting it to  $V_{REF}$ , leading to the non-inverting input being driven positive by a voltage of  $\frac{V_{REF}}{2}$ . In other words, if  $V_{IN} = -0.6V_{REF}$ , then the connection of the MSB capacitor will drive the non-inverting input of the comparator to ( $-0.6V_{REF} + 0.5V_{REF}$ ) =  $-0.1V_{REF}$ . This voltage is subsequently compared with the inverting input of the comparator (which is connected to ground) and produces a logic high, thus implying that the MSB represents a value that is larger than  $\frac{V_{REF}}{2}$ . This process is repeated, this time disconnecting the second largest capacitor in the array, which has a binary weight as previously mentioned, i.e half the capacitance of the largest capacitor. A similar comparison is done which determines the logic value of the second-most-significant-bit (MSB – 1). This continues until logic values for all the bits have been determined, after which the ADC is ready to compensate with the conversion of another analogue signal.

Figure 2-9: Capacitive DAC based on Charge Redistribution

An example of a conversion process can be seen in Figure 2-10 which shows how the DAC output voltage approximates the sampled analogue input signal by successively comparing the weight of each bit with the reference voltage.

Figure 2-10: SAR Operation

Each comparison operation has a duration of one sample clock cycle. Therefore, the conversion time is directly proportional to the bit-resolution of the ADC and the sampling clock cycle duration, i.e at least 12 clock cycles are required to convert an analogue signal to a digital equivalent, accurate to 12-bits.

Establishing closed-loop control requires that the output telemetry be fed back to the central controller. This implies that the measurements fed back to the controller need to be synchronised with the reference signal. It is therefore required to control the instant when an analogue signal is converted to its equivalent digital code. This instant can be controlled in the SAR-based ADC, meaning that the data produced by the ADC can be synchronised with the central controller, whereas the pipeline-based ADC continuously converts the analogue signal and additional means are required to synchronise the controller with the data. ADCs based on the SAR architecture are the most popular general-purpose ADCs for data acquisition in low-to-medium frequency time domain applications.

# 2.3 Data Acquisition Solutions