# A Bi-Directional, Direct Conversion Converter for use in Household Renewable Energy Systems

By Adriaan Nicholaas Schutte

Thesis presented in partial fulfilment of the requirements for the degree of Master of Science (Engineering) at the University of Stellenbosch

Supervisor: Mr. P-J Randewijk

27 February 2009

# DECLARATION

By submitting this thesis electronically, I declare that the entirety of the work contained therein is my own, original work, that I am the owner of the copyright thereof (unless to the extent explicitly otherwise stated) and that I have not previously in its entirety or in part submitted it for obtaining any qualification.

Copyright © 2008 Stellenbosch University All rights reserved

# **Summary**

A bi-directional, direct conversion switch-mode converter is proposed for use in distributed household renewable energy systems. The converter is intended as the central interface between the household energy system's low voltage Direct Current bus and the high voltage Alternating Current bus. The low voltage DC bus is connected to renewable generation and storage devices, while the high voltage AC bus is connected to the user's equipment and the mains grid.

The converter overcomes the inherent reverse-duty cycle problem associated with bidirectional converters by using a combination step-up / step-down half-bridge converter on the high voltage side of a high frequency transformer. The low voltage side of the transformer is driven by a full bridge inverter that acts as a rectifier during reverse mode.

In order to control the flow of power in both directions the converter implements Average Current Mode Control. A method is developed to determine the transfer functions of common switch-mode converters by inspection alone. This method is applied to the proposed converter, and both current and voltage mode control loops are designed with the frequency response method. The control system is implemented using a Digital Signal Processor.

A method of simultaneously simulating both the converter hardware and software is developed using VHDL. This method greatly reduced the development effort of the converter. The operation of the proposed converter is verified through this method of simulation.

A prototype converter is constructed and successfully tested, thereby proving the viability of the proposed converter topology and control methodology.

# **Opsomming**

A bi-direksionele, direkte-omskakelking skakelmodus omsetter word voorgestel vir gebruik in huishoudelike hernubare energie stelsels. Daar word beoog dat die omsetter die sentrale koppelvlak sal vorm tussen die laagspanning gelykstroom bus en die hoogspanning wisselstroom bus van 'n huishoudelike energie stelsel. Die laagspanning bus is verbind aan die hernubare energie opwekking en stoor toestelle, terwyl die hoogspanning wisselstroom bus aan die gebruiker se toestelle en die net kragtoevoer verbind is.

Die omsetter bevat 'n gekombineerde opkapper / afkapper halfbrug omsetter aan die hoogspanning kant van 'n hoe-frekwensie transformator. Hierdie halfbrug omsetter oorkom die omgekeerde-dienssiklus probleem wat ondervind word in bi-direksionele omsetters. Die lagspanning kant van die transformator word gedryf deur 'n volbrug omsetter, wat ook as gelykrigter dien tydens die omgekeerde drywingsvloei modus.

Die beheer van drywingsvloei in beide rigtings noodsaak die gebruik van stroomwyse beheer. Die omsetter gebruik die Gemiddelde Stroomwyse Beheer metode. 'n Metode is ontwikkel om die oordragsfunksies van algemene omsetters deur inspeksie te verkry. Hierdie metode is toegepas op die voorgestelde omsetter, en beide stroom en spannings beheerlusse is ontwerp deur middel van die frekwensie respons metode. Die beheerstelsel van die omsetter is met behulp van 'n Digitale Seinverwerker geimplementeer.

'n Metode is ontwikkel waarmee die omsetter se hardeware en sagteware gelyktydig gesimuleer kan word. Hierdie metode het die werkslas tydens die ontwikkeling van die omsetter aansienlik verlaag. Die simulasie metode is verder gebruik om die korrekte werking van die omsetter te toon.

'n Prototipe omsetter is gebou en suksesvol getoets. Daardeur is die lewensvatbaarheid van die omsetter en die beheer metodologie bewys.

# **Acknowledgements**

I extend my deepest gratitude towards:

My wife, for her unwavering encouragement and support, specifically for her help with the mechanical construction of the converter prototype and support during the revision process.

My parents for everything they have given and continue to give me, and specifically their significant financial support for this project.

My study leader, Mr. Randewijk, for his patience and understanding.

Above all, the Lord Almighty, who is in control of everything.

# **Contents**

| 1 | Introduc  | tion                                                    | 15 |

|---|-----------|---------------------------------------------------------|----|

|   | 1.1 Bac   | kground                                                 | 15 |

|   | 1.2 Pro   | ject Objectives                                         | 16 |

|   | 1.2.1     | Main Objective                                          | 16 |

|   | 1.2.2     | Project Deliverables                                    |    |

|   | 1.3 Cor   | verter Function and Requirements                        | 17 |

|   | 1.3.1     | Typical Household Renewable Energy Components           |    |

|   | 1.3.2     | Typical Household Energy Installation                   | 19 |

|   | 1.3.3     | Proposed Converter                                      | 21 |

|   | 1.4 Cor   | verter Requirements                                     | 21 |

|   | 1.5 Doc   | cument Structure and Chapter Summary                    | 23 |

|   | 1.5.1     | Topology Development Section                            | 23 |

|   | 1.5.2     | Hardware Design Section                                 | 23 |

|   | 1.5.3     | Software Design Section                                 | 24 |

|   | 1.5.4     | Results Section                                         | 24 |

|   | 1.5.5     | Appendices                                              | 25 |

| 2 | Literatur | e Study                                                 | 26 |

|   |           | pter Introduction                                       |    |

|   | 2.2 Ove   | erview of Bi-Directional DC-DC Converter Topologies     |    |

|   | 2.2.1     | Usage of Bo-Directional DC-DC Converters                |    |

|   | 2.2.2     | Current Source DC-DC Converter                          |    |

|   | 2.2.3     | Dual Inductor Current Source DC-DC Converter            |    |

|   | 2.2.4     | Bi-Directional DC-DC Converter Conclusion               |    |

|   |           | erview of Current Mode Control Methods                  |    |

|   | 2.3.1     | Current Mode Control Methods                            |    |

|   | 2.3.2     | Average Current Mode Control                            |    |

|   | 2.3.3     | Current Mode Control Conclusion                         |    |

|   |           | pter Conclusion                                         |    |

| 3 |           | l Converter Topology                                    |    |

|   |           | pter Introduction                                       |    |

|   |           | -directional Converters                                 |    |

|   |           | verse Power Flow: The Non-Unity Duty Cycle Problem      |    |

|   |           | -polar Bi-Directional Topology                          |    |

|   | -         | polar Bi-directional Topology                           |    |

|   | 3.5.1     | Mode 1: Positive Voltage, Forward Current               |    |

|   | 3.5.2     | Mode 2: Positive Voltage, Reverse Current               |    |

|   | 3.5.3     | Mode 3: Negative Voltage, Reverse Current               |    |

|   | 3.5.4     | Mode 4: Negative Voltage, Forward Current               |    |

|   | 3.5.5     | General Operation of Bi-polar, Bi-directional Converter |    |

|   | 3.5.6     | Alternative Methods of Operation                        |    |

|   |           | ended Range Bi-polar Bi-Directional Converter           |    |

|   | 3.6.1     | Forward Mode                                            |    |

|   | 3.6.2     | Reverse Mode                                            |    |

|   | 3.6.3     | Alternative Topologies                                  |    |

|   |           | Converter Operation                                     |    |

|   |           | ctical Considerations                                   |    |

|   | 3.8.1     | Topology Refinements                                    |    |

|   | 3.8.2    | Safety Isolation                                  | 53 |

|---|----------|---------------------------------------------------|----|

|   | 3.9 Cha  | pter Conclusion                                   | 54 |

| 4 | Hardwar  | e Design: Power Section                           | 55 |

|   |          | pter Introduction                                 |    |

|   | 4.2 Tra  | nsformer Design and Switching Frequency           | 56 |

|   | 4.2.1    | Turns Ratio Determination                         |    |

|   | 4.2.2    | Core Selection Considerations                     | 57 |

|   | 4.3 Swi  | tch Design                                        | 61 |

|   | 4.3.1    | Switch Type Selection                             | 61 |

|   | 4.3.2    | Low Voltage Transistors                           | 62 |

|   | 4.3.3    | High Voltage Transistors                          | 64 |

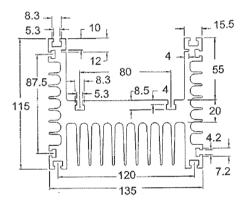

|   | 4.3.4    | Heat Sink                                         | 65 |

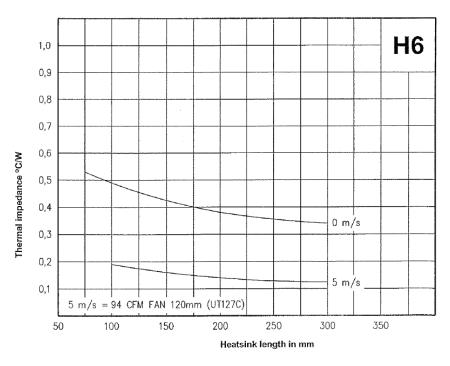

|   | 4.4 Indu | uctor and Capacitor Design                        | 68 |

|   | 4.4.1    | Output Capacitor                                  | 68 |

|   | 4.4.2    | Inductor                                          | 74 |

|   | 4.4.3    | Low Voltage Capacitor                             | 78 |

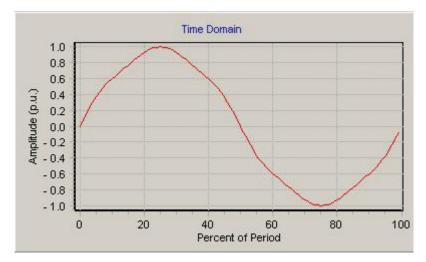

|   | 4.5 Pow  | ver PCB Design                                    | 78 |

|   | 4.5.1    | Low Voltage (MOSFET) PCB                          | 79 |

|   | 4.5.2    | Mid Section (IGBT) PCB                            | 79 |

|   | 4.5.3    | High Voltage (Output) PCB                         | 80 |

|   | 4.6 Cha  | pter Conclusion                                   |    |

| 5 | Hardwar  | e Design: Drivers and Sensors                     |    |

|   | 5.1 Cha  | pter Introduction                                 | 81 |

|   | 5.2 IGE  | T Drivers                                         | 81 |

|   | 5.2.1    | IGBT Connection                                   | 81 |

|   | 5.2.2    | Driver Isolation                                  |    |

|   | 5.2.3    | Circuit Design                                    |    |

|   | 5.3 MO   | SFET Drivers                                      | 85 |

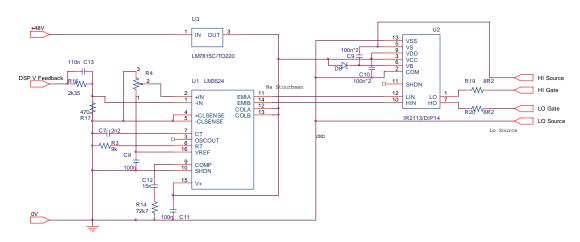

|   | 5.3.1    | Circuit Design                                    | 85 |

|   | 5.4 Sen  | sor Design                                        |    |

|   | 5.4.1    | Current Transducer Selection                      |    |

|   | 5.4.2    | Voltage Transducer Selection                      |    |

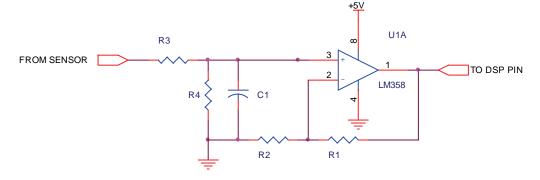

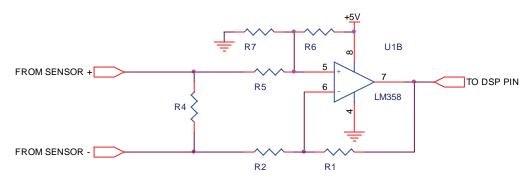

|   | 5.4.3    | Sensor Interfacing                                | 89 |

|   | 5.5 Cha  | pter Conclusion                                   |    |

| 6 | Hardwar  | e Design: Digital Controller and Power Supply     | 90 |

|   | 6.1 Cha  | pter Introduction                                 | 90 |

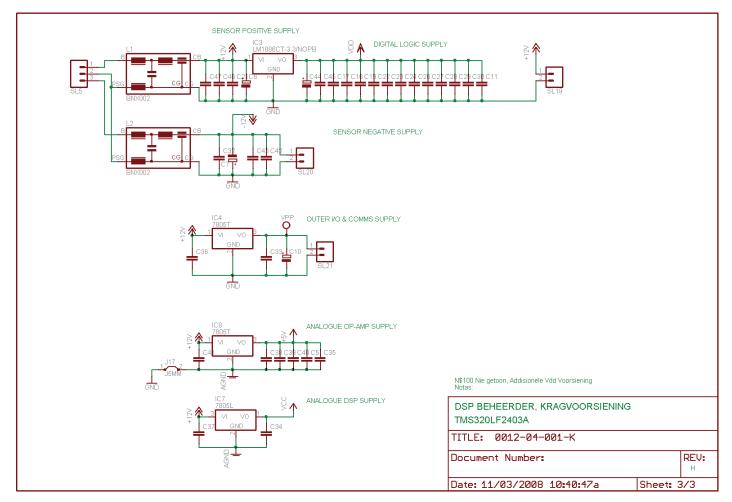

|   | 6.2 Con  | trol Power Supply Design                          | 91 |

|   | 6.2.1    | Sourcing of Control Power                         | 91 |

|   | 6.2.2    | Control Power Voltage Regulation and Distribution | 92 |

|   | 6.2.3    | Control Power Consumption                         | 93 |

|   | 6.2.4    | Control Power Supply Control                      | 94 |

|   | 6.3 DSI  | P Board Design                                    | 94 |

|   | 6.3.1    | Microprocessor Selection                          | 95 |

|   | 6.3.2    | Voltage Regulators                                | 96 |

|   | 6.3.3    | Digital I/O Design                                | 96 |

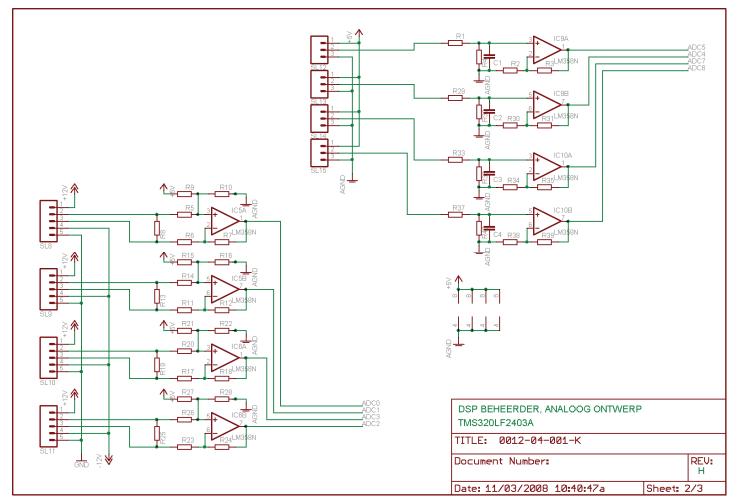

|   | 6.3.4    | Analogue I/O Design                               | 98 |

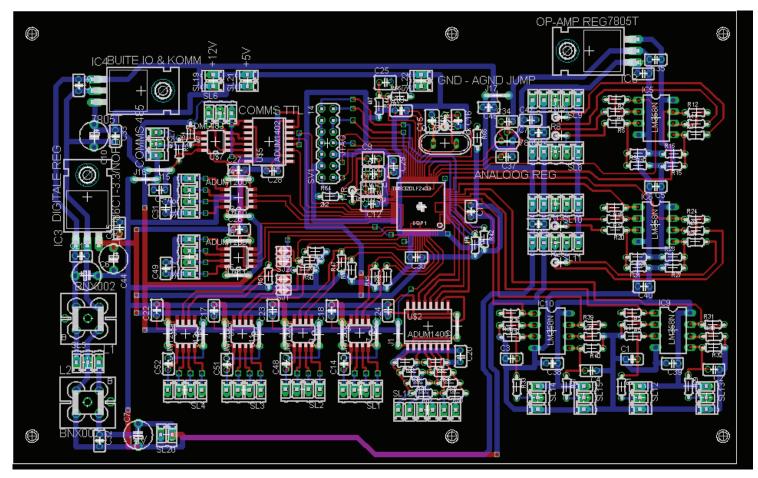

|   | 6.3.5    | DSP Board Layout                                  |    |

|   | 6.4 Cha  | pter Conclusion                                   |    |

| 7 | Converte | er Control Methodology and Compensation Equations |    |

|   | 7.1 Cha  | pter Introduction                                 |    |

|   | 7.2 Con          | trol Loop Design Methodology                                | 105 |

|---|------------------|-------------------------------------------------------------|-----|

|   | 7.2.1            | Voltage and Current Control Loops                           |     |

|   | 7.2.2            | Control Loop Design Procedure                               |     |

|   | 7.2.2            | Circuit Simplifications for Transfer Function Determination |     |

|   |                  | rent Control Loop                                           |     |

|   | 7.3.1            | Additional Gains                                            |     |

|   | 7.3.2            | Current Loop Response                                       |     |

|   | 7.3.2            | Compensator Design                                          |     |

|   | 7.3.3            | Compensator Design                                          |     |

|   |                  |                                                             |     |

|   | 7.4 von<br>7.4.1 | tage Mode Control                                           |     |

|   |                  | Additional Gain                                             |     |

|   | 7.4.2            | Frequency Response                                          |     |

|   | 7.4.3            | Compensator Design                                          |     |

|   | 7.4.4            | Compensator Digitization                                    |     |

|   |                  | ermining Transfer Functions Through Inspection              |     |

|   | 7.5.1            | Introduction                                                |     |

|   | 7.5.2            | Time Varying Components                                     |     |

|   | 7.5.3            | Impedance of Components                                     |     |

|   | 7.5.4            | Effect of Changes in Duty Cycle                             |     |

|   | 7.5.5            | Output Current Not Inductor Current                         |     |

|   | 7.5.6            | Voltage Transfer Function                                   |     |

|   | 7.5.7            | General Method                                              |     |

|   |                  | pter Conclusion                                             |     |

| 8 | DSP Con          | figuration and Software                                     | 124 |

|   | 8.1 Cha          | pter Introduction                                           | 124 |

|   | 8.2 DSF          | P Control Implementation                                    | 124 |

|   | 8.2.1            | DSP Peripherals                                             | 124 |

|   | 8.2.2            | DSP Sampling and Switching Schemes                          | 125 |

|   | 8.2.3            | DSP PWM Configuration                                       | 128 |

|   | 8.3 AC           | Output Control                                              | 131 |

|   | 8.3.1            | Voltage Reference                                           | 131 |

|   | 8.3.2            | Compensating Equations                                      | 132 |

|   | 8.3.3            | Mode and Direction                                          |     |

|   | 8.4 DSF          | Software                                                    |     |

|   | 8.4.1            | Control Code Algorithm                                      |     |

|   | 8.4.2            | Code Execution Period                                       |     |

|   | 8.5 Cha          | pter Conclusion                                             |     |

| 9 |                  | r Simulation                                                |     |

| - |                  | oduction                                                    |     |

|   |                  | ulation Models                                              |     |

|   | 9.2.1            | Power Component Models                                      |     |

|   | 9.2.2            | Control Model                                               |     |

|   | 9.2.3            | VHDL Code                                                   |     |

|   |                  | ware Problems Identified Through Simulation                 |     |

|   | 9.3.1            | Sampling Period.                                            |     |

|   | 9.3.1<br>9.3.2   | Inductor Size                                               |     |

|   | 9.3.2<br>9.3.3   |                                                             |     |

|   |                  | Output Capacitors                                           |     |

|   | 9.3.4            | Mode Control                                                |     |

|   | 9.3.5            | Duty Cycle Continuity                                       |     |

|   | 9.3.6            | Current Error Calculation                                   | 141 |

| 9.4  | Simulation Load Cases                                                     | 141    |

|------|---------------------------------------------------------------------------|--------|

| 9.5  | Simulation Results                                                        | 141    |

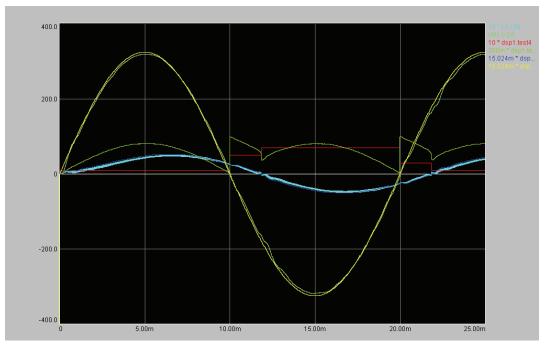

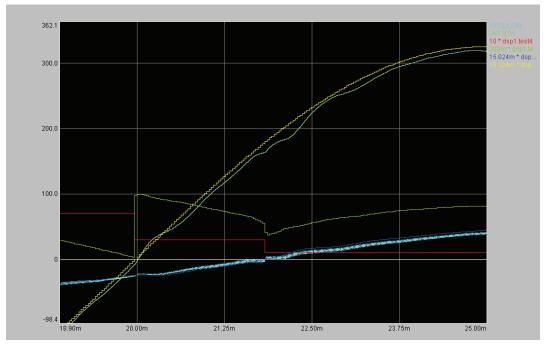

| 9.5  | 5.1 Resistive Load                                                        | 142    |

| 9.5  | 5.2 Inductive Load                                                        | 143    |

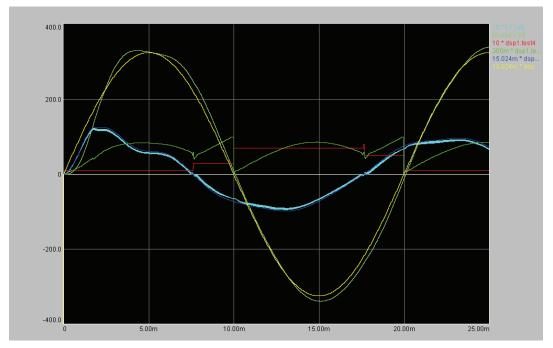

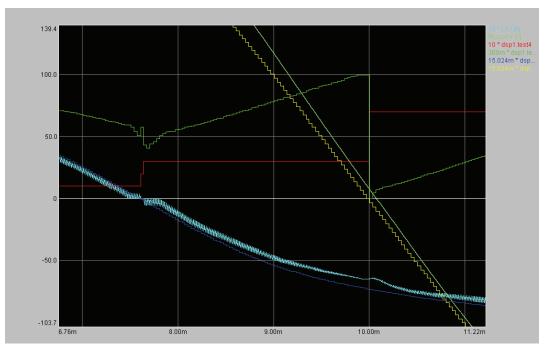

| 9.5  | 5.3 Capacitive Load                                                       | 145    |

| 9.6  | Simulation Conclusion                                                     | 146    |

| 10   | Physical Implementation and Commissioning                                 | 148    |

| 10.1 | Chapter Introduction                                                      | 148    |

| 10.2 | Enclosure, Mounting and Cabling                                           | 148    |

| 10   | .2.1 External Connectors and Circuit Breakers                             | 148    |

| 10   | .2.2 Power PCB's                                                          | 148    |

| 10   | .2.3 Driver PCB's                                                         | 148    |

| 10   | .2.4 DSP and Control Power PCB's, Cabling                                 | 149    |

| 10.3 | Converter Prototype Photographs                                           | 149    |

| 11   | Measurements and Results                                                  | 151    |

| 11.1 | Chapter Introduction                                                      | 151    |

| 11.2 | Experimental and Measurement Setup                                        | 151    |

| 11.  | .2.1 Equipment Used                                                       | 151    |

| 11.  | .2.2 Forward Mode DC Test Setup                                           | 151    |

| 11.  | .2.3 Reverse Mode DC Test Setup                                           | 152    |

| 11.  | .2.4 AC Test Setup                                                        | 152    |

| 11.3 | Measurements: Sub-System Tests                                            | 152    |

| 11.  | .3.1 Control Power Supply                                                 | 152    |

| 11.  | .3.2 DSP and Drivers                                                      | 154    |

|      | .3.3 Transducers and Analogue Circuits                                    |        |

| 11.4 | Results: DC Tests                                                         | 159    |

| 11.  | .4.1 Forward Mode                                                         | 159    |

|      | .4.2 Reverse Mode                                                         |        |

| 11.5 | Results: DC Converter Efficiency                                          |        |

| 11.6 | Results: AC Tests                                                         | 168    |

| 11.  | .6.1 Resistive Load                                                       |        |

|      | .6.2 Resistors and Capacitors in Series                                   |        |

| 11.  | .6.3 Resistors and Capacitors in Parallel                                 | 170    |

| 11.7 | Results Conclusion                                                        |        |

|      | Conclusions and Recommendations                                           |        |

| 12.1 | Chapter Introduction                                                      |        |

| 12.2 | Deliverable 1: Development of a Suitable Converter Topology               |        |

| 12.3 | Deliverable 2: Development of Suitable Control Methodologies              |        |

| 12.4 | Deliverable 3: Combined Hardware and Software Simulation                  |        |

| 12.5 | Deliverable 4: Design and Construct Prototype Converter Power Section     |        |

| 12.6 | Deliverable 5: Design and Construct Prototype Converter Control So<br>176 | ection |

| 12.7 | Deliverable 6: Demonstrate 4 –Quadrant DC Operation of Converter          | 177    |

| 12.8 | Deliverable 7: Demonstrate AC Operation of Converter                      |        |

| 12.9 | Concluding Remarks                                                        | 178    |

| 13   | References                                                                | 179    |

|      | Appendix A                                                                |        |

| 14.1 | Appendix A.1: Transformer Core Selection Table                            |        |

| 14.2 | Appendix A.2: Inductor Core Selection Table                               |        |

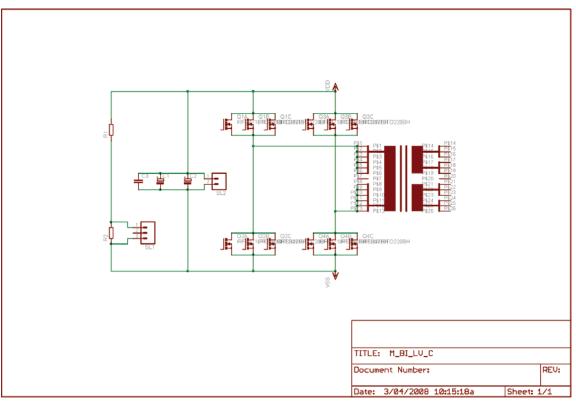

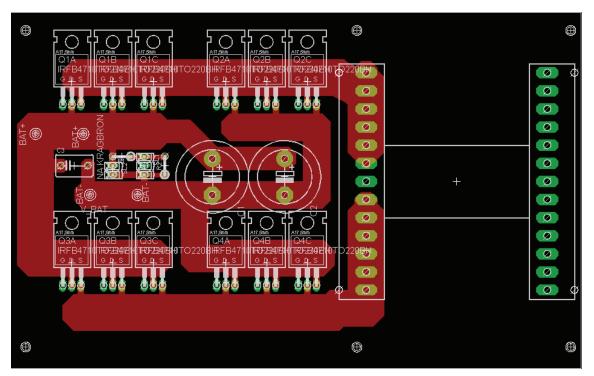

| 14.3 | Appendix A.3: Schematic and Layout: Low Voltage Board                     | 184    |

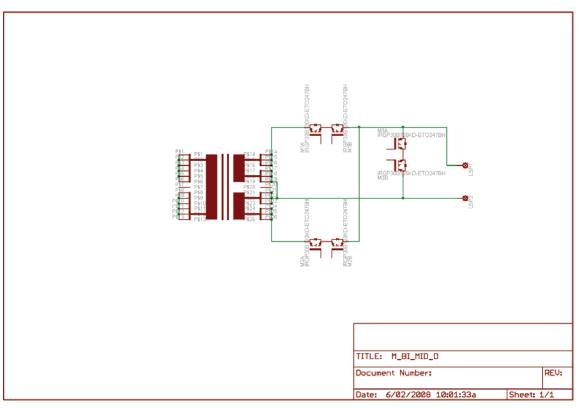

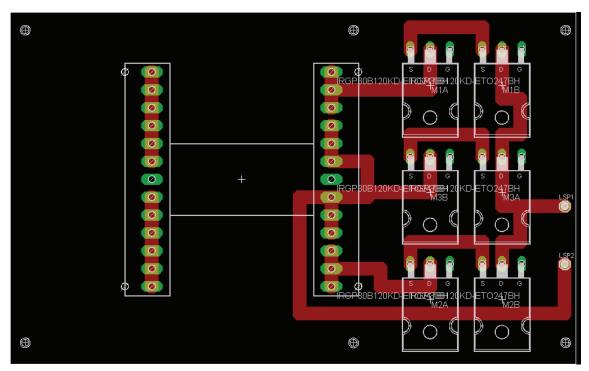

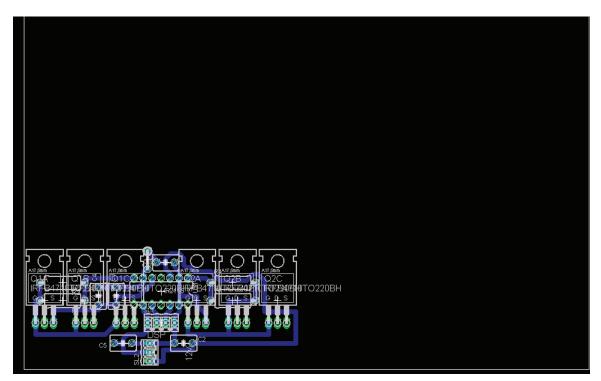

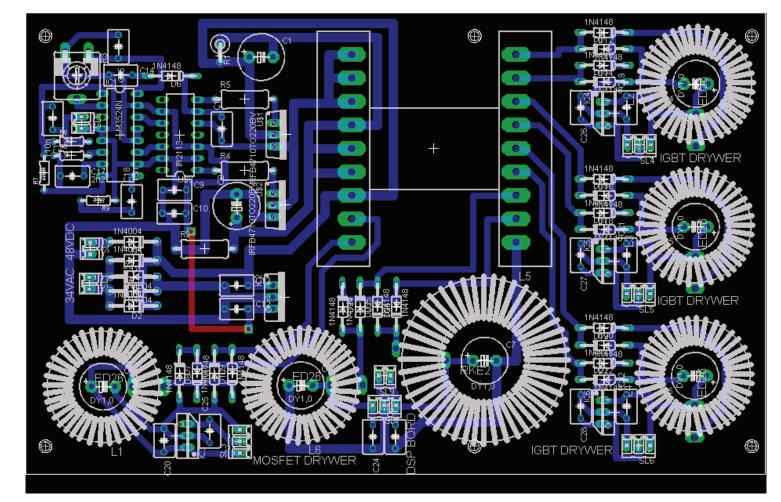

| 14.4  | Appendix A.4: Schematic and Layout: Mid Section Board          | 185      |

|-------|----------------------------------------------------------------|----------|

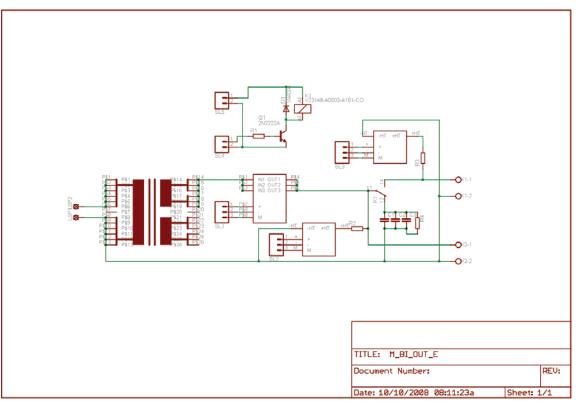

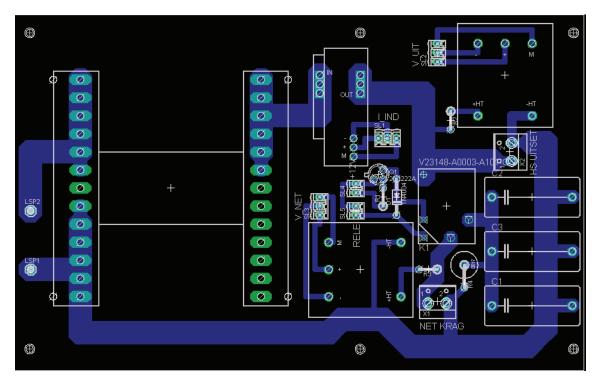

| 14.5  | Appendix A.5: Schematic and Layout: High Voltage Board         | 186      |

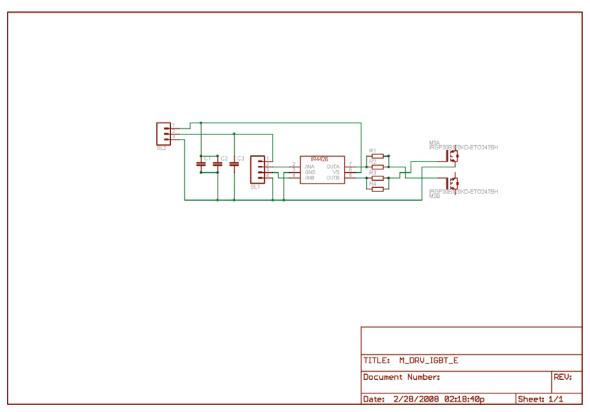

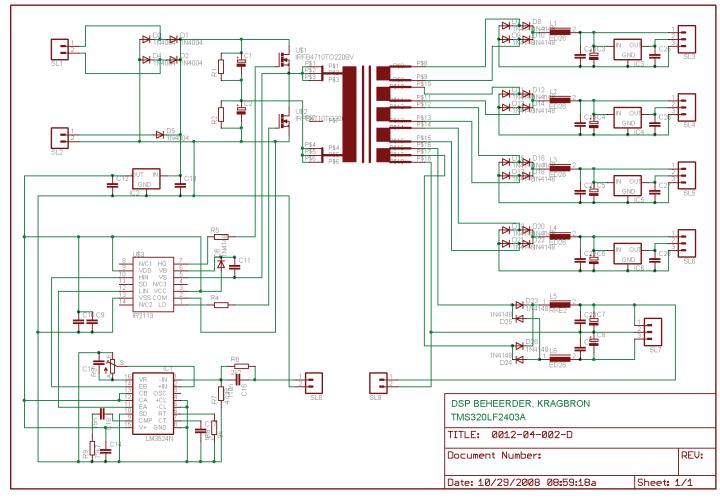

| 14.6  | Appendix A.6: Schematic and Layout: IGBT Drivers               | 187      |

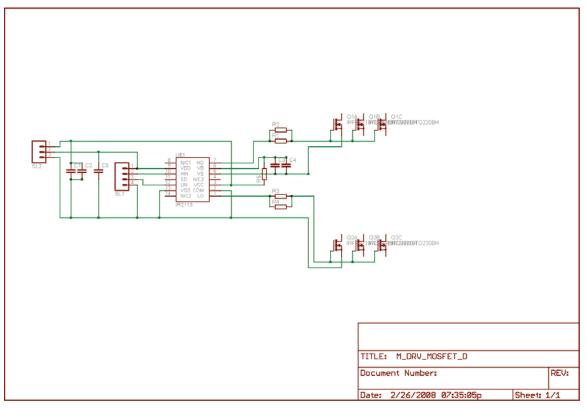

| 14.7  | Appendix A.7: Schematic and Layout: MOSFET Drivers             | 188      |

| 14.8  | Appendix A.8: Schematic: Control Power Supply Board            | 189      |

| 14.9  | Appendix A.9: Layout: Control Power Supply Board               | 190      |

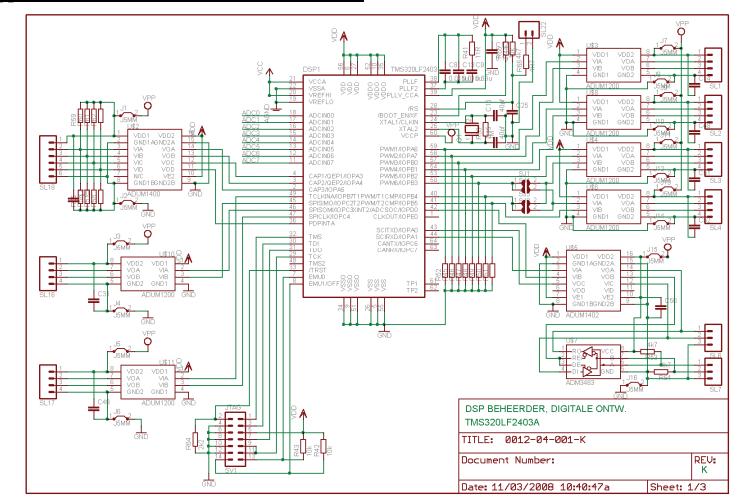

| 14.10 | Appendix A.10: Schematic: DSP Control Board                    | 191      |

| 14.11 | Appendix A.11: Layout: DSP Control Board                       | 194      |

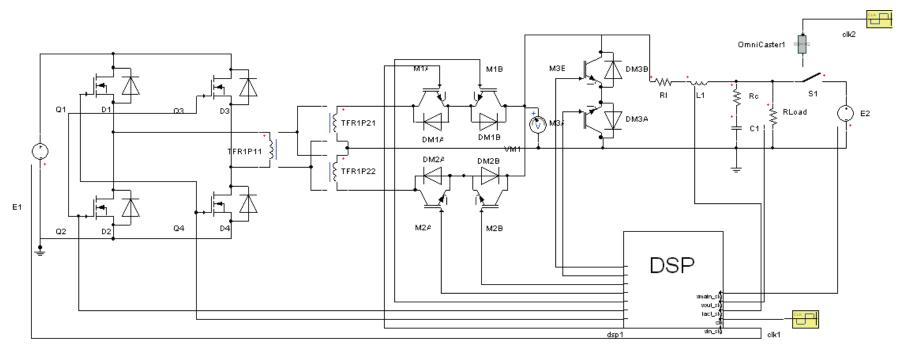

| 14.12 | Appendix A.12: Simplorer Schematic                             | 195      |

| 14.13 | Appendix A.13: Derivation of Forward Mode Transfer Function    | 196      |

| 14.1  | 3.1 Introduction                                               | 196      |

| 14.1  | 3.2 A.13.1 Forward Mode: State Space Representation            | 196      |

| 14.1  | 3.3 A.13.2 Forward Mode: Averaging the State-Space Represe     | entation |

|       | 200                                                            |          |

| 14.1  | 3.4 A.13.3 Forward Voltage Mode Compensation                   | 202      |

| 15 A  | ppendix B: Software Code                                       | 208      |

| 15.1  | Appendix B.1: Matlab Code: Forward Mode Response and Compe     | nsation  |

|       | 209                                                            |          |

| 15.2  | Appendix B.2: Matlab Code: Reverse Mode Response and Compe     | nsation  |

|       | 210                                                            |          |

| 15.3  | Appendix B.3: Matlab Code: AC Output Response and Compensation | n211     |

| 15.4  | Appendix B.4: DSP Code Listing                                 | 213      |

| 15.4  | .1 Main Program                                                | 213      |

| 15.4  | .2 Interrupt Vector Table                                      | 218      |

| 15.4  |                                                                |          |

| 15.4  | .4 Event Manager A Intitialization                             | 222      |

| 15.4  | •                                                              |          |

| 15.4  | .6 Analogue to Digital Converter Initialization                | 227      |

|       |                                                                |          |

| 15.5  |                                                                |          |

# List of Figures

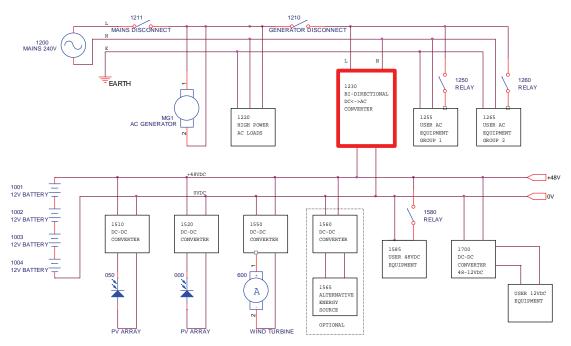

| Figure 1: Typical Household Renewable Energy System               | 19  |

|-------------------------------------------------------------------|-----|

| Figure 2: Prototype Bidirectional Bipolar Converter               | 25  |

| Figure 3: Typical On-Line UPS Layout                              | 27  |

| Figure 4: Current Source DC-DC Bi-Directional Converter           |     |

| Figure 5: Current Source Converter: Forward Operation             |     |

| Figure 6: Current Source Converter: Reverse Operation             | 29  |

| Figure 7: Combined Generator / UPS System                         |     |

| Figure 8: Dual Inductor DC-DC Converter                           | 32  |

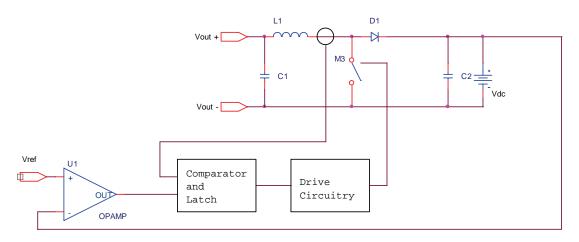

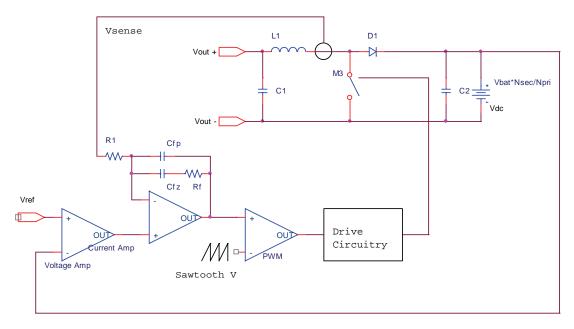

| Figure 9: Basic Current Mode Control                              | 35  |

| Figure 10: Slope Compensation                                     |     |

| Figure 11: Average Current Mode Control                           |     |

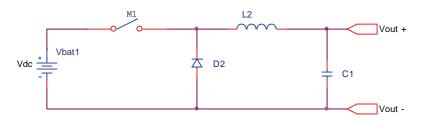

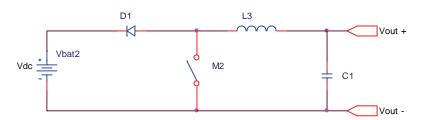

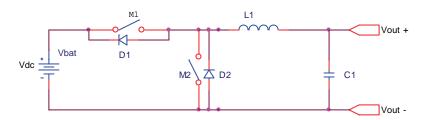

| Figure 12: Step Down Uni-directional Converter                    | 40  |

| Figure 13: Boost Uni-directional Converter                        |     |

| Figure 14: Proposed Uni-polar Bi-directional Topology             | 42  |

| Figure 15: Redrawn Uni-polar Bi-Directional Converter             | 43  |

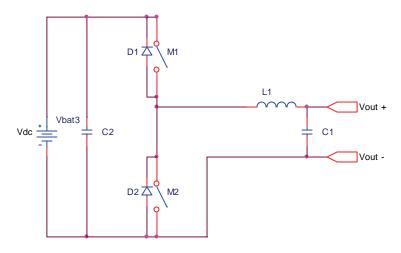

| Figure 16: Proposed Bi-polar Bi-Directional Converter             | 44  |

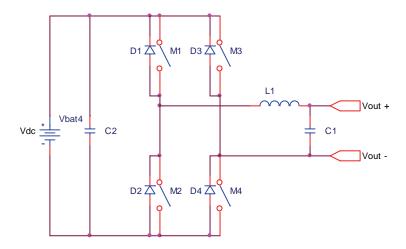

| Figure 17: Extended Range Bi-polar Bi-directional Converter       |     |

| Figure 18: Alternative Topology 1                                 | 49  |

| Figure 19: Alternative Topology 2                                 | 49  |

| Figure 20: Alternative Topology 3                                 | 50  |

| Figure 21: Bi-Directional AC Topology                             |     |

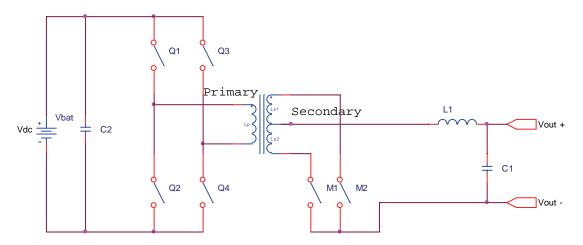

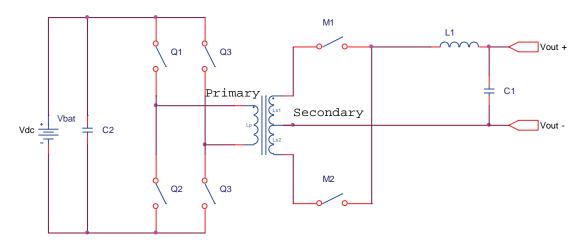

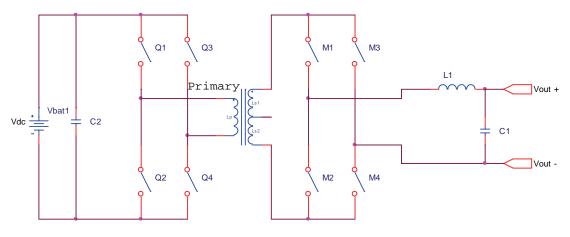

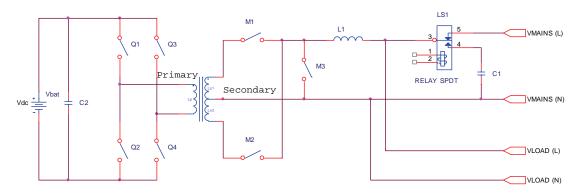

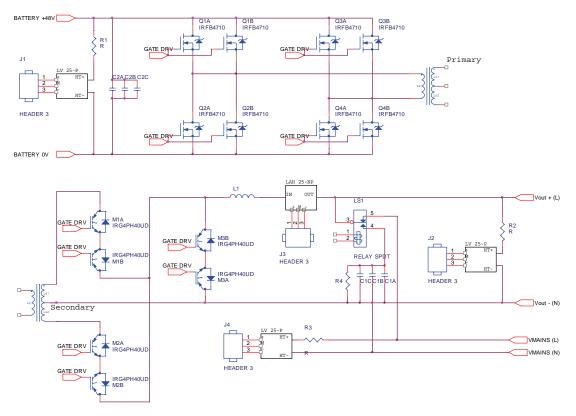

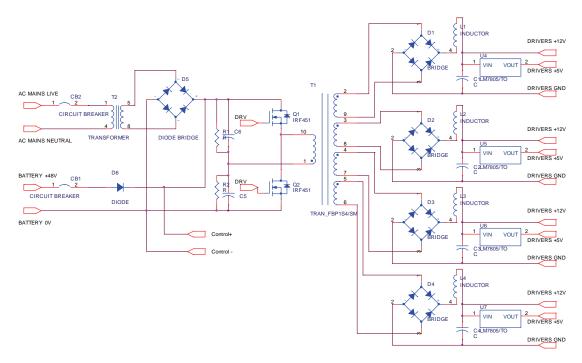

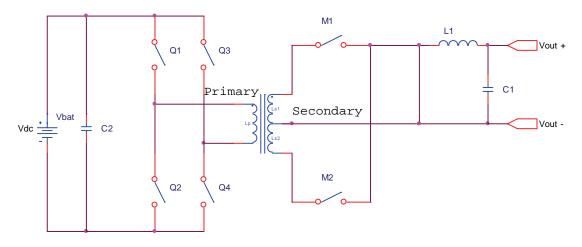

| Figure 22: Converter Power Section Schematic                      | 55  |

| Figure 23: Fastron H6 Heat Sink Profile                           | 66  |

| Figure 24: Fastron H6 Heat Sink Performance                       |     |

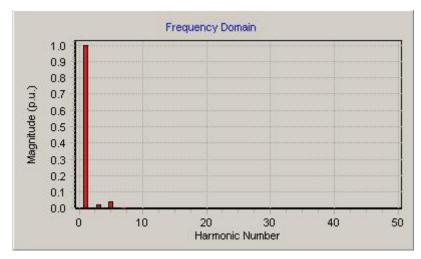

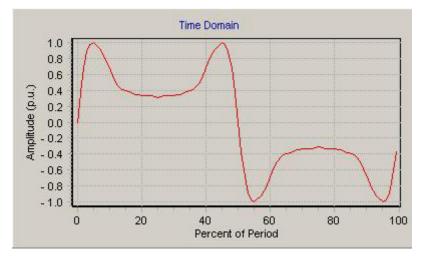

| Figure 25: Typical Residential Current Waveform, Time Domain      | 69  |

| Figure 26: Typical Residential Current Waveform, Frequency Domain | 70  |

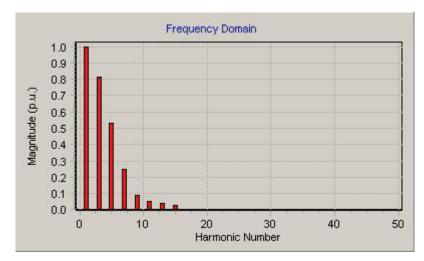

| Figure 27: Typical Computer Current Waveform, Time Domain         |     |

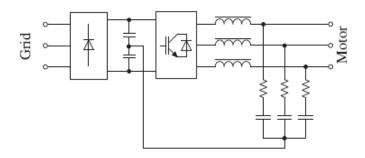

| Figure 28: Typical Computer Current Waveform, Frequency Domain    |     |

| Figure 29: VSD with LC Output Filter                              | 72  |

| Figure 30: LC Filter Frequency Response                           | 73  |

| Figure 31: IGBT Driver Circuit                                    | 83  |

| Figure 32: MOSFET Driver Circuit                                  | 86  |

| Figure 33: Control System Layout                                  | 90  |

| Figure 34: Control Power Supply Schematic                         | 91  |

| Figure 35: Control Power Supply Control                           | 94  |

| Figure 36: Absolute Amplifier                                     | 99  |

| Figure 37: Differential Amplifier                                 | 100 |

| Figure 38: Voltage and Current Control Loops                      |     |

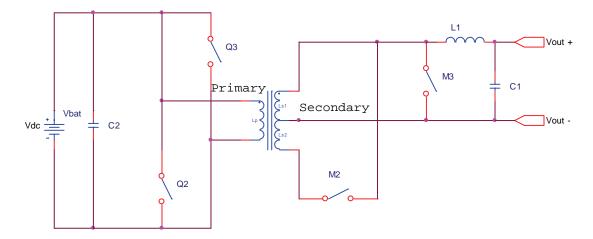

| Figure 39: Converter in Reverse Mode                              | 108 |

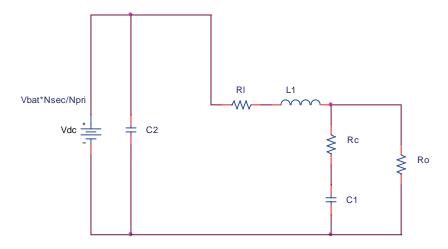

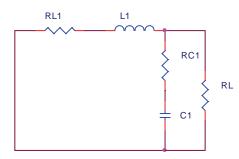

| Figure 40: Equivalent Circuit, Reverse Mode                       |     |

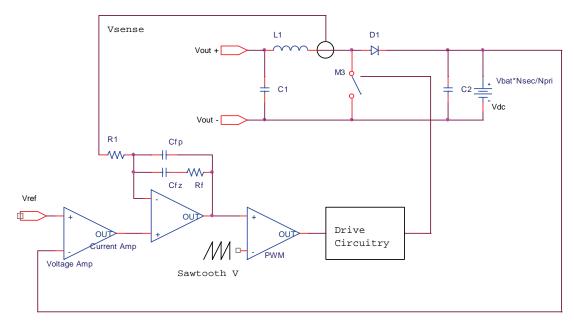

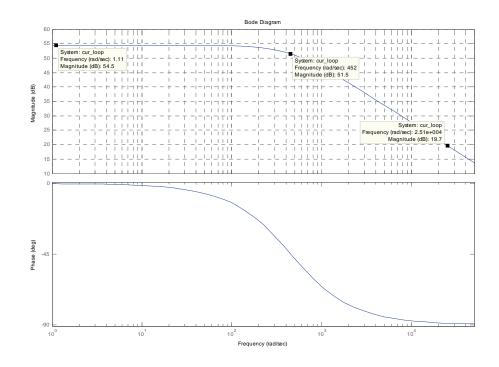

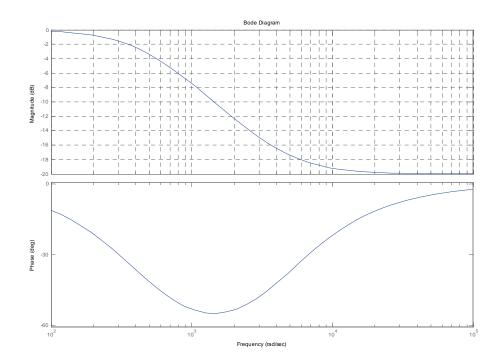

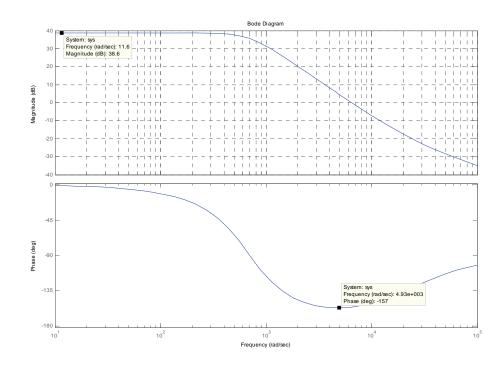

| Figure 41: AC Output Converter, Open Loop Current Response        | 111 |

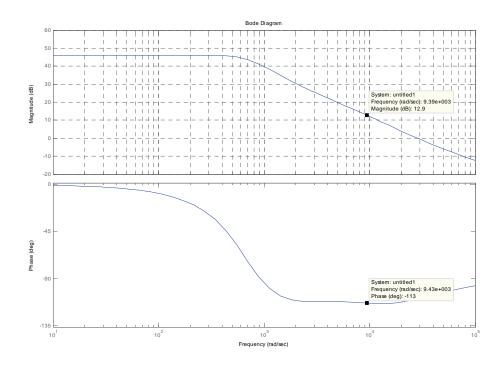

| Figure 42: AC Output Converter, Current Loop Compensator          | 112 |

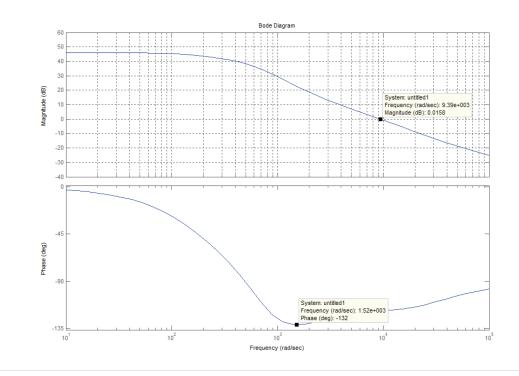

| Figure 43: AC Output Converter, Compensated Current Loop          |     |

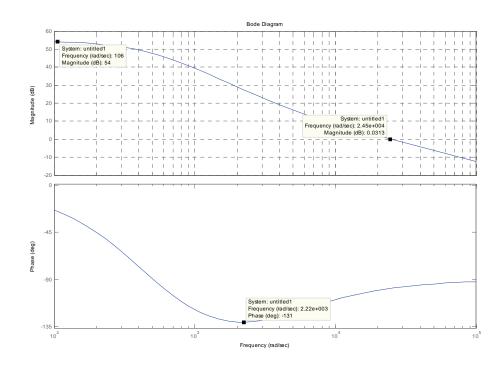

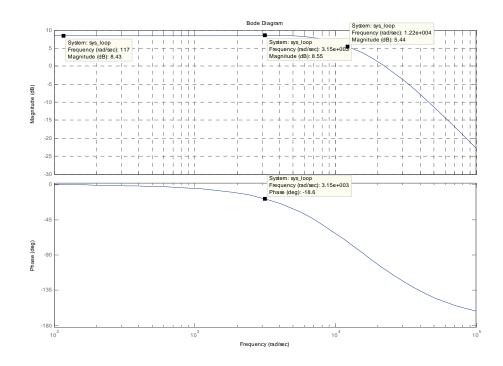

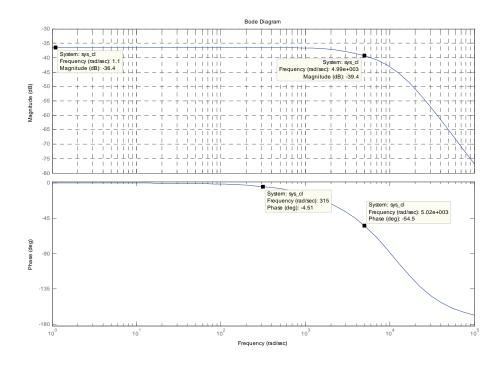

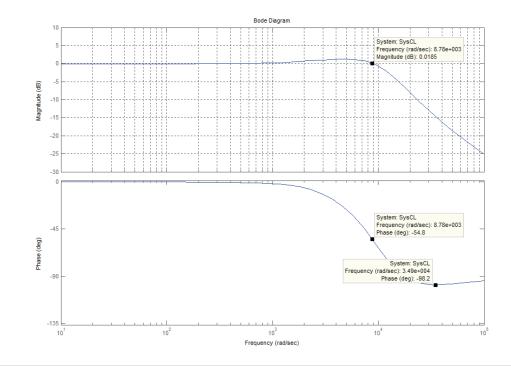

| Figure 44: AC Output Converter, Open Loop Voltage Response        | 115 |

| Figure 45: AC Output Converter, Closed Loop Voltage Response      | 116 |

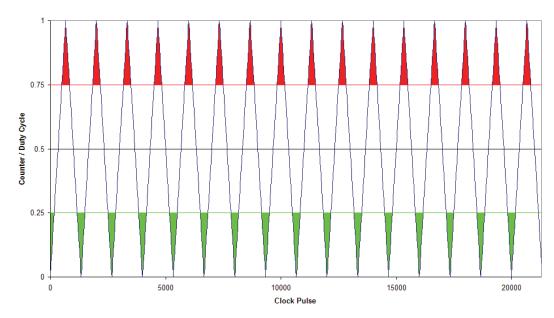

| Figure 46: Forward Switching Scheme                               | 127 |

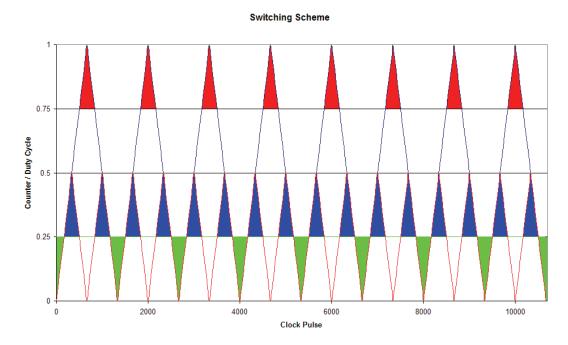

| Figure 47: Reverse Switching Scheme                                                                        | 128   |

|------------------------------------------------------------------------------------------------------------|-------|

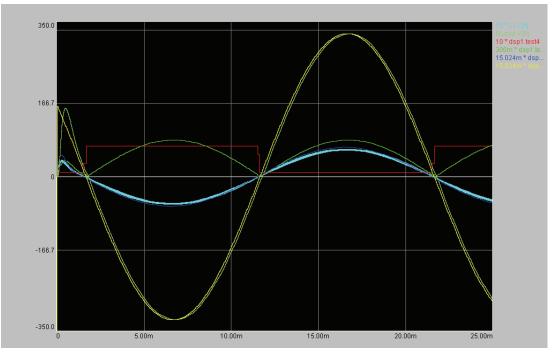

| Figure 48: Resistive Load Simulation, Output                                                               |       |

| Figure 49: Resistive Load Simulation, Output                                                               |       |

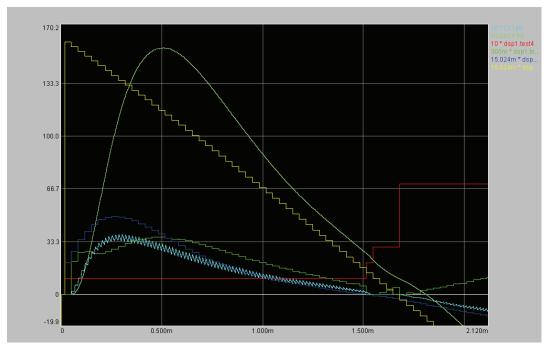

| Figure 50: Inductive Load Simulation, Output                                                               |       |

| Figure 51: Inductive Load Simulation, Crossover Transients                                                 |       |

| Figure 52: Capacitive Load Simulation, Output                                                              |       |

| Figure 53: Capacitive Load Simulation, Crossover Transients                                                |       |

| Figure 54: Converter External Connections                                                                  |       |

| Figure 54: Converter Internal Layout                                                                       |       |

| •                                                                                                          |       |

| Figure 56: Power Supply, Transformer Tap (Ch.1) and Gate Drive (Ch.2)                                      |       |

| Figure 57: Power Supply, Secondary Winding (Ch.1) and Gate Drive (Ch.2)                                    |       |

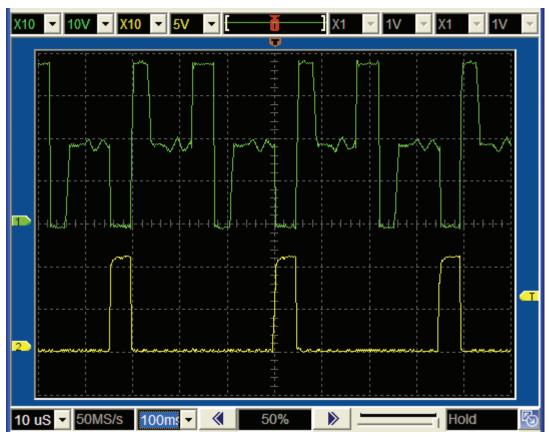

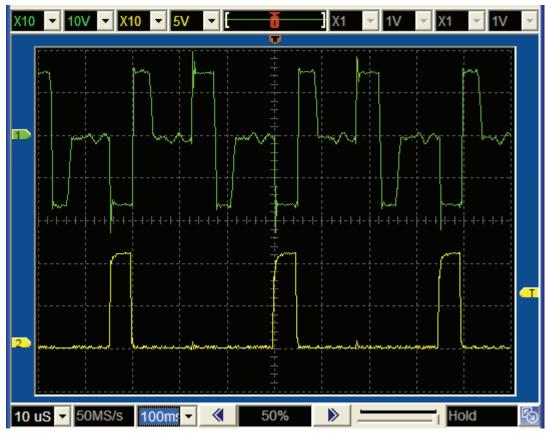

| Figure 58: DSP, Gate Drive, Q1 (Ch.1) and Q2 (Ch.2)                                                        |       |

| Figure 59: DSP, Gate Drive, M1 (Ch.1) and M2 (Ch.2)                                                        |       |

| Figure 60: DSP, Gate Drive, M1 (Ch.1) and M3 (Ch.2)                                                        |       |

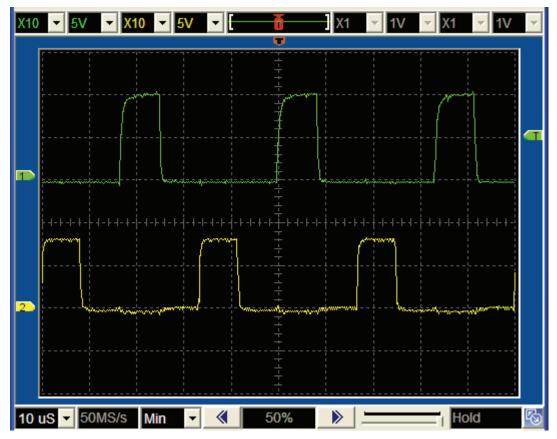

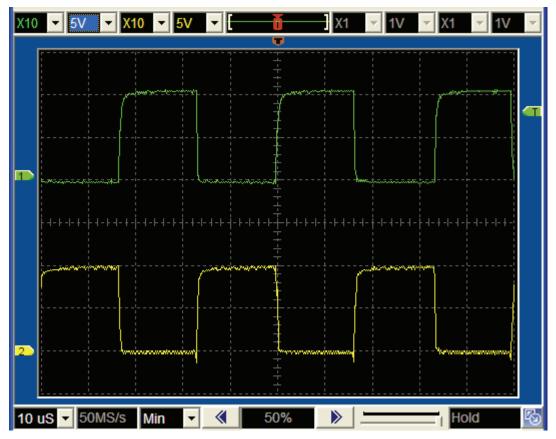

| Figure 61: DSP, Execution Time (Ch.1) and PWM Output (Ch.2)                                                |       |

| Figure 62: Fwd. Mode, Pos. Output, Inductor Voltage (Ch.1) and Current (Ch.2).                             |       |

| Figure 63: Fwd. Mode, Pos. Output, Maximum Power. Inductor Voltage (Ch.1)                                  |       |

| Current (Ch.2)                                                                                             |       |

| Figure 64: Fwd Mode, Inductor Voltage (Ch.1) and Current (Ch.2)                                            |       |

| Figure 65: Fwd Mode, Neg. Output, Inductor Voltage (Ch.1) and Current (Ch.2).                              |       |

| Figure 66: Fwd Mode, Neg. Output, Inductor (Ch.1) and Output (Ch.2) Volt                                   | •     |

| Ringing Effect                                                                                             |       |

| Figure 67: Fwd. Mode, Input Voltage (Ch.1)                                                                 |       |

| Figure 68: Rev. Mode, Pos. Input, Inductor Voltage (Ch.1) and Current (Ch.2)                               |       |

| Figure 69: Rev. Mode, Neg. Input, Inductor Voltage (Ch.1) and Current (Ch.2)                               |       |

| Figure 70: Reverse Mode, Rectifier Input Voltage (Ch.1)                                                    |       |

| Figure 71: AC Output, Resistive Load, Output Voltage (Ch.1) and Current (Ch.2)                             |       |

| Figure 72: AC Output, Resistors and Capacitors in Series, Output Voltage (Ch.1                             | ) and |

| Current (Ch.2)                                                                                             |       |

| Figure 73: AC Output, Resistors and Capacitor in Parallel, Output Voltage (Ch.1                            | ) and |

| Current (Ch.2)                                                                                             | 171   |

| Figure 74: Low Voltage Board Schematic                                                                     | 184   |

| Figure 75: Low Voltage Board Layout                                                                        | 184   |

| Figure 76: Mid Section Board Schematic                                                                     | 185   |

| Figure 77: Mid Section Board Layout                                                                        | 185   |

| Figure 78: High Voltage Board Schematic                                                                    | 186   |

| Figure 79: High Voltage Board Layout                                                                       |       |

| Figure 80: IGBT Driver Board Schematic                                                                     |       |

| Figure 81: IGBT Driver Board Layout                                                                        |       |

| Figure 82: MOSFET Driver Board Schematic                                                                   |       |

| Figure 83: MOSFET Driver Board Layout                                                                      |       |

| Figure 84: Control Power Supply Schematic                                                                  |       |

| Figure 85: Control Power Supply Layout                                                                     |       |

| Figure 86: DSP Controller Schematic Sheet 1                                                                |       |

| Figure 87: DSP Controller Schematic Sheet 2                                                                |       |

| Figure 88: DSP Controller Schematic Sheet 3                                                                |       |

| Figure 89: DSP Controller Layout                                                                           |       |

| Figure 90: Simplorer Simulation Schematic                                                                  |       |

| Figure 91: Forward Mode, $M_1$ or $M_2$ On ( $M_1$ on shown)                                               |       |

| Figure 92: Forward Mode, $M_1 \& M_2$ Off ( $M_1$ of $M_2$ off ( $M_1$ of $M_2$ off ( $M_1$ of $M_2$ off). |       |

| $15010 > 21 1 01 mild 11000, 111 0 112 011 \dots 011 0 000 0000000000000$                                  |       |

| Figure 93: Forward Mode, M <sub>1</sub> or M <sub>2</sub> On | 198 |

|--------------------------------------------------------------|-----|

| Figure 94: Forward Mode, M <sub>1</sub> & M <sub>2</sub> Off |     |

| Figure 95: Converter Forward Response, Uncompensated         |     |

| Figure 96: Forward Converter Response, Lead Comp.            |     |

| Figure 97: Forward Converter Response, Lead & Lag Comp.      |     |

| Figure 98: Forward Converter Response: Closed Loop           |     |

# **Glossary of Acronyms and Abbreviations**

|          | A                                                 |

|----------|---------------------------------------------------|

| A        | Ampere                                            |

| AC       | Alternating Current                               |

| ADC      | Analogue to Digital Converter                     |

| ACMC     | Average Current Mode Control                      |

| BJT      | Bipolar Junction Transistor                       |

| C        | Capacitance, Coulomb                              |

| CAD      | Computer Aided Design                             |

| CPU      | Central Processing Unit                           |

| D        | Duty Cycle                                        |

| dB       | Decibel                                           |

| DC       | Direct Current                                    |

| DSP      | Digital Signal Processor                          |

| ELV      | Extra Low Voltage                                 |

| F        | Farad                                             |

| Н        | Henry                                             |

| HV       | High Voltage (>100V in this report)               |

| Hz       | Hertz                                             |

| I/O      | Input / Output                                    |

| IC       | Integrated Circuit                                |

| IGBT     | Insulated Gate Bipolar Transistor                 |

| ISR      | Interrupt Service Routine                         |

| JTAG     | Joint Test Action Group                           |

| K        | Kelvin                                            |

| L        | Inductance                                        |

| LSB      | Least Significant Bit                             |

| LTI      | Linear Time-Invariant                             |

| LV       | Low Voltage (<50V in this report)                 |

| MOSFET   | Metal-Oxide Semiconductor Field-Effect Transistor |

| MSB      |                                                   |

| P        | Most Significant Bit<br>Power                     |

| P<br>PCB |                                                   |

| -        | Printed Circuit Board                             |

| PCC      | Point of Common Coupling                          |

| PV       | Photo Voltaic                                     |

| PWM      | Pulse-Width Modulation                            |

| R        | Resistance                                        |

| RAM      | Random Access Memory                              |

| RMS      | Root Mean Square                                  |

| S        | Second(s)                                         |

| SELV     | Safety Extra Low Voltage                          |

| SMT      | Surface Mount Technology                          |

| THD      | Total Harmonic Distortion                         |

| UPS      | Uninterruptable Power Supply                      |

| V        | Volt                                              |

| VHDL     | VHSIC Hardware Description Language               |

| VHSIC    | Very High Speed Integrated Circuit                |

| VSD      | Variable Speed Drive                              |

| W        | Watt                                              |

| Z        | Complex Impedance                                 |

|          | L L ···                                           |

# 1 Introduction

# 1.1<u>Background</u>

Due to the increasing demand for electric power generation by means of clean renewable energy resources, several large-scale generation schemes utilising natural energy resources have been proposed and implemented. To date these schemes have mostly followed the traditional (fossil and nuclear fuelled) model consisting of large centralised generation facilities with widespread distribution networks.

It is opinion of the author that this centralized-generation, distributed consumption model is fundamentally flawed when applied to renewable energy resources. Globally, research and growing knowledge of renewable energy have shown that more efficient usage of renewable energy sources is possible with a distributed generation model. Currently usable forms of renewable energy are mostly distributed in nature, which suits a distributed generation and utilization model. Distributed generation is considered an important part of most countries' renewable energy development and implementation strategy.

The above statements are substantiated by the following media release by the European Commission. It quoted from a European Distributed Resources Project synopsis report (European Commission, 2004: 5):

"The greatest potential market for DG (distributed generation) is displacing power supplied through the grid. On-site production minimises the transmission and distribution losses as well as the transmission and distribution costs, a significant part (above 30%) of the total electricity cost. As the demand for more and better quality electric power increases, DG can provide alternatives for reliable, costeffective, premium power for homes and business. It can also offer customers continuity and reliability of supply, when a power outage occurs at home or in the neighbourhood, by restoring power in a short time."

Distributed generation does not only refer to household size generation but includes larger generation facilities situated close to communities or industries. This project will however focus on a power electronic converter for a household renewable energy system, since this application holds the greatest potential gain from renewable energy usage. It is generally accepted within renewable energy circles that households in future will be expected to generate a significant portion of their own energy requirements as the efforts to stem global warming increase and fossil fuel resources becomes more expensive.

This chapter will show that a central component of a typical distributed household renewable energy system is a power electronic converter that accepts low voltage DC input (from batteries, photovoltaic panels and wind generators) and converts this to a high voltage AC output, for interface to user equipment and the mains grid.

The development of this DC-AC converter is the topic of this thesis.

# 1.2 Project Objectives

# 1.2.1 Main Objective

The objective of this project is to develop a direct conversion, bi-directional, low voltage DC to high voltage AC converter, which will enable the implementation of household distributed renewable energy systems using currently available power generation devices. Direct conversion here means that an intermediate DC bus is not used. Most converters currently available use intermediate DC busses, as discussed in section 2.2. A converter without an intermediate DC bus may be more cost effective and potentially improve the efficiency of conversion.

## 1.2.2 Project Deliverables

Achieving the main project objective will consist of achieving several subobjectives or deliverables. These deliverables can be used as measures of the progress and overall success of the project.

The following deliverables have been defined for this project:

## 1.2.2.1 Deliverable 1: Development of a Suitable Converter Topology

Develop a converter topology that accepts a low voltage DC input and produces high voltage output that can be both positive and negative with respect to the input. In addition, the output current of the converter may be positive and negative for both positive and negative voltage outputs (that is, it must support four-quadrant operation).

#### 1.2.2.2 Deliverable 2: Development of Suitable Control Methodologies

Develop control methodologies and compensation means in order to perform both current and voltage mode control of the converter. Special emphasis is placed on the development of current mode control methodologies.

## **1.2.2.3** Deliverable 3: Combined Hardware and Software Simulation

Simultaneously simulate the power electronic, control components and software in a single simulation in order to verify the operation of the converter, as well as minimise faultfinding and debugging on the prototype system.

#### **1.2.2.4** Deliverable 4: Design and Construct Prototype Converter Power Section

Design and prototype the power electronics sections of the converter using commercially available components.

#### **1.2.2.5** Deliverable 5: Design and Construct Prototype Converter Control Section

Design and prototype a Digital Signal Processor (DSP) based controller including necessary drivers, sensors and power supplies.

# **1.2.2.6** Deliverable 6: Demonstrate 4 –Quadrant DC Operation of Converter

Demonstrate that the converter is capable of positive and negative DC power flows, with both positive and negative DC voltage outputs (that is, operate in all four quadrants).

#### 1.2.2.7 Deliverable 7: Demonstrate AC Operation of Converter

Demonstrate that the converter is capable of producing an AC output at mains frequency with resistive and reactive loads.

## **1.3**Converter Function and Requirements

In order to establish the need for the proposed converter, as well as to extract requirements for the design of the converter, it is necessary to analyze the household renewable energy system of which the converter is the central component.

Section 1.3.1 discusses the individual components that typically constitute a household renewable energy system. The characteristics of each of the components discussed will both influence the design of the final system and the converter itself.

In Section 1.3.2, the individual components are synthesized into a representative household installation, where the central position of the proposed converter is clearly shown.

This section is based on the personal experience of the author who has for several years researched the design of cost competitive renewable energy systems.

#### 1.3.1 Typical Household Renewable Energy Components

#### **1.3.1.1 Energy Capture Devices**

Although a multitude of alternative methods of harnessing renewable energy for household use have been proposed, to date only Photovoltaic (PV) Panels and wind generators have become freely commercially available. Although these devices have relatively low conversion efficiencies, especially PV panels, they are widely available and are extensively used in installations that require energy independency, e.g. remote farms and villages, telecommunications installations and ocean-going yachts. Note that all PV panels, and most small wind generators, provide an unregulated Direct Current (DC) output, which is typically interfaced with a storage device via linear or switch-mode power electronic converters.

#### **1.3.1.2** Energy Storage Devices

Whenever energy is generated that cannot immediately be used, storage is required. This is particularly true in renewable energy systems, whose output is mostly dependent on fluctuating atmospheric conditions and often does not coincide with energy usage patterns. Electrical energy storage is therefore an indispensable part of almost all renewable energy systems.

Batteries have to date dominated the renewable energy storage market. Lead acid, calcium and gel batteries are all widely available, due in part to the widespread use of automotive batteries.

It should again be noted that almost all types of electrical storage devices, perhaps with the exception perhaps of flywheel and pumped storage systems, store energy directly as an accumulation of electrical charge (either on conductors, in dissolved ions, etc.). It is therefore reasonable to claim that most storage devices that are suitable for household use accept and provide electrical energy as a DC flow of electrons.

#### **1.3.1.3** User Equipment

Electrical power is almost universally distributed to households by means of Alternating Current (AC) systems with a Root Mean Square (RMS) voltage of between 110 and 250 V, and a frequency of 50-60 Hz. A multitude of reasons for this situation exist, including:

- It is relatively easy to convert between AC voltages using transformers.

- A relatively high system voltage results in low currents for a given power requirement, thereby limiting transmission losses.

The average household therefore has numerous devices that require a regulated AC supply to operate satisfactorily. The overall cost of a renewable energy system would be greatly increased if users were to replace all equipment with devices that are capable of operating from DC alone.

It should be noted that many household items can be purchased in low voltage DC versions. These include all types of chargers, computers, lights and fridges / freezers. These devices are however considered specialized and are not as readily available as AC powered versions, and are typically more expensive.

#### 1.3.1.4 Mains Grid Connection

Experience has shown that the peak household energy consumption may easily be 5 times the average weekly consumption. These peaks are due to the simultaneous use of high power devices like kettles, welders, heaters, ovens and stoves. If a renewable energy system were to be designed to supply this peak energy demand, the size of the system would be significantly increased, only to cope with a demand situation that represents perhaps 5% of the system operational time.

The effect of peak maximum demand may be averaged to some extent by interconnecting a number of household renewable energy systems. This allows each individual system to be sized slightly above the household's average consumption (including daily morning and evening peaks). The individual systems must be interconnected to both each other or to a traditional mains grid. This allows each system to buy additional electricity from the grid when required, and sell electricity back into the grid when an excess is available.

#### **1.3.1.5 Backup Energy Sources**

If the mains grid supply is not reliable, as is the present case in South Africa, a means for generating electrical power during times of peak household demand and grid unavailability is required.

The most widely used form of backup generation is a petrol or diesel generator. These generators typically generate the same voltage and frequency as the mains supply, so that they can be directly connected to user equipment. For the purpose of this converter, the generator is taken as a mains connection without the option of sinking energy into it.

#### 1.3.2 Typical Household Energy Installation

The individual components discussed in section 1.3.1 can now be synthesized into the system of Figure 1:

Figure 1: Typical Household Renewable Energy System

This is a representative system only, since each household's system has to be designed according to the local weather conditions, energy usage, grid availability and budget. It does however facilitate the discussion of the interconnection of the individual components, thereby clearly showing the functional and performance requirements of the converters.

The following paragraphs discuss the design of the system in Figure 1 and how it influences the design of the proposed converter.

#### 1.3.2.1 System DC Bus

Since the PV panels (000 and 050), wind generator (600), DC user loads (1585 and 1700) and storage batteries (1001 - 1004) all operate on DC voltages, they are connected to a common DC bus. It is desirable that the system contains as few DC buses as possible, since every DC-DC conversion increases the system cost and introduces losses.

Typical DC bus voltages may range from 12 V / 24 V for small households, motor homes and yachts, to 36 V and 48 V for larger installations. From a power transfer point of view, a high DC bus voltage is desirable, since this will result in significantly smaller DC current when the converter is supplying high-power AC loads. 48 VDC was selected for the present system since it is high enough to transfer a relatively large amount of power and it is the industry standard for telecommunications systems. Subsequently a large range of suitable semiconductors is available at relatively low prices.

The PV panels and wind generator are connected through DC-DC regulators, which will likely support maximum power point tracking. Any 48 VDC user loads are directly connected to the bus, and 12V or 24V user equipment can be connected through a DC-DC converter.

#### 1.3.2.2 System AC Bus

The system shows a single-phase AC bus. Two contactors are provided to isolate the system in case of mains failure. The Mains Disconnect contactor (1211) enables the system to continue to provide the user's equipment with power during a mains failure, without attempting to provide power back into the grid.

The Generator Disconnect (1210) contactor is used to isolate the generator, as well as any high-power loads that cannot be powered from the batteries, from the remainder of the system. If the user wishes to run these high-powered loads, the generator must be run.

The Mains Disconnect and Generator Disconnect contactors are placed in series to allow the batteries to be charged from the generator during a mains failure.

It is a statutory requirement (according to SANS 10142 in South Africa and AS/NZS 3000 in Australia) for the mains grid, generator, converter and user equipment to share common earth and neutral conductors. Any discontinuity in either the earth or neutral conductors would render earth-leakage protection devices inoperable, and would be illegal in most countries.

The user's equipment is connected in groups to allow selective operation of low and high priority equipment.

#### 1.3.3 Proposed Converter

The proposed converter, which is the topic of this thesis, is shown in heavy red lines in Figure 1. It can be seen that the proposed converter acts as a bridge between the high voltage AC and the low voltage DC buses of the system. It controls all power flow between the DC and AC busses. Since the output of the converter is an AC waveform, the converter must be able to produce both positive and negative outputs with respect to the battery polarity.

During normal system operation power typically flows from the DC bus to the AC bus so that at least some of the user's equipment energy usage is offset by the output from the PV panels and wind generators. When excess energy is available due to low user demand, the converter must be able to sink the excess energy into the mains grid. To ensure that transmission losses are kept to a minimum, the converter must be able to source and sink power from the mains grid at unity power factor.

When the mains grid or the generator is not connected, all AC bus power is supplied by the converter from the batteries and / or PV panels and wind generators. In this case, the batteries could be discharged to a deep level, so that it is desirable to recharge them when mains power is restored, or the generator is run. Although a separate charger may be used, the system may be simplified and the cost lowered by using a bi-directional converter, since the inverting and charging functions would then share at least some power and control components, as well as a housing and operator interface.

It is thus clear that the converter must be able to provide a bi-directional flow of power to and from the AC bus.

There is also a more subtle reason for requiring bi-directional power flow. Since the AC loads may be reactive, which is more often the case than not, the voltage and current supplied to the AC bus may not be in phase, and therefore could have opposite polarities. In this case, the instantaneous power transfer to the AC bus could oscillate between positive and negative at twice the mains frequency.

# 1.4 Converter Requirements

The requirements for the design of the proposed converter is taken directly from the preceding discussions of the suggested household renewable energy system (section 1.3.2), as well as the individual components of the system the converter is required to interface with (section 1.3.1). These discussions can be condensed into the following set of requirements:

• Requirement 1: The low-voltage side of the converter shall be connected to a DC bus with a nominal potential of 48VDC. The bus

voltage may vary between 36 VDC and 60VDC, depending on the charge state of the bus storage batteries.

- Requirement 2: The high-voltage side of the converter shall be connected to a single phase AC bus, and be capable of producing positive and negative voltages on the AC bus in a continuous range of 325 V to + 325 V, which corresponds to the peak values of a 230 Vrms waveform.

- Requirement 3: The converter shall be able to support both positive and negative current flow for both positive and negative output voltages.

- Requirement 4: The converter shall support both current and voltage output modes, depending on whether the mains or generator supply is available.

- Requirement 5: The converter shall contain an internal switch that will connect and disconnect the mains or generator supply and the output capacitor to the AC bus. When mains supply is available, the switch will connect the mains and disconnect the output capacitor, and the converter will function in current control mode. When the mains supply is not available, the mains will be disconnected and the capacitor connected, and the converter shall operate in voltage control mode.

- Requirement 6: In voltage control mode, the converter output voltage shall be capable of being modulated to produce a sinusoidal AC waveform of 230 VAC magnitude and a frequency of 50Hz (for use in South Africa and Australia).

- Requirement 7: During voltage control mode, user loads that can be reasonably expected at a household installation shall not distort the converter output waveform significantly.

- Requirement 8: In current control mode, the converter output current shall be capable of being modulated to produce a sinusoidal current waveform of selectable amplitude that is in-phase or 180 degrees out of phase with reference to the mains voltage.

- Requirement 9: In voltage control mode the converter shall be able to drive reactive loads without significant output waveform distortion.

- Requirement 10: The converter shall be capable of supplying or sourcing 2 kW of electrical power to / from the AC bus.

- Requirement 11: The converter shall be able to operate at full power in ambient temperatures of up to 40 degrees Celsius.

- Requirement 12: The high voltage and low voltage sides of the converter shall be galvanically isolated.

- Requirement 13: The converter, the mains grid and the user equipment shall share common neutral and earth conductors.

These requirements form the basis of the design of the proposed converter as described in the following chapters.

# 1.5 Document Structure and Chapter Summary

This document can broadly be divided into five sections, namely:

- Topology Development Section

- Hardware Design Section

- Software Design Section

- Results Section

- Appendices

## 1.5.1 <u>Topology Development Section</u>

Chapters 1 to 3 detail the intended function of the converter, what literature sources were consulted during the design of the converter, and the development of the actual topology.

Chapter 1 (Introduction) established the need for the converter and the requirements for its design. A typical household renewable energy system of which this converter will be the central component was considered. The individual components typically used in such systems was discussed. The system requirements were detailed and the project goals and deliverables were defined.

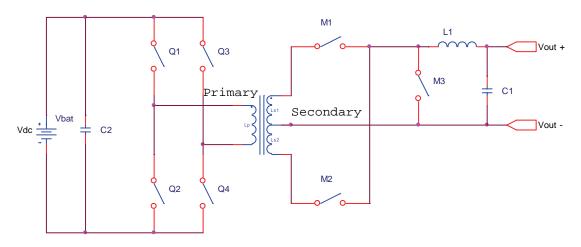

Chapter 2 (Literature Study) reviews the literature sources used during the development of the converter. These sources reviewed covers two areas within the field of power electronic, namely the design of bi-directional DC-DC converters with intermediate transformers, and current mode control in switch mode converters.

Chapter 3 (Proposed Converter Topology) develops the converter topology based on the requirements of Chapter 1 and the literature study of Chapter 2. The topology is developed by first considering simple uni-direction DC-DC converters. These will be synthesized into a bi-directional DC-DC converter. A transformer is included in the topology to enable the one side of the converter to operate at voltages typically encountered in mains grids.

## 1.5.2 Hardware Design Section

Chapters 4 to 6 detail the hardware design of the converter.

Chapter 4 (Hardware Design: Power Section) describes the design of the converter power section. It covers the selection of all components as well as the circuit and manufactured component design. The topology developed in Chapter 3, together with the practical considerations mentioned in that chapter are directly used as the basis for Chapter 4.

Chapter 5 (Hardware Design: Drivers and Sensors) describes the transistor gate drivers and the voltage and current sensors that form the interface between the power section and the control system. This chapter therefore forms the link between the power design of Chapter 4 and the digital controller design of Chapter 6.

Chapter 6 (Hardware Design: Digital Controller and Power Supply) details the design of both the control power supply and the digital controller. A switch-mode converter is used to convert input power to five isolated supplies to feed the driver boards as well as the digital controller board. The digital controller board is designed around a Digital Signal Processor (DSP) that contains all necessary functions to implement the complete converter control system.

#### 1.5.3 Software Design Section

Chapters 7 to 9 describe the design of the control methodology, compensation equations, digital controller software, as well as the converter simulation.

Chapter 7 (Converter Control Methodology and Compensation Equations) details the calculation of the compensation equations that are used by the DSP to control the current and voltage feedback loops of the converter. A method is also detailed by which the transfer functions of switch mode converters can be obtained through inspection.

Chapter 8 (DSP Configuration and Software) describes the design of the Digital Signal Processor software. The software discussion covers both the control code that implements the control methodologies developed in Chapter 7, as well as DSP hardware configuration code. The design of the software was an iterative process, since the software design both drove the simulation of Chapter 9, but was influenced by the problems identified through the simulation.

Chapter 9 (Converter Simulation) presents a method for simultaneously simulating both the converter hardware and software. Chapter 9 details this method as well as the results of the converter simulation. The simulation identified several problems with the original converter design and allowed these problems to be corrected before the prototype was constructed. The final simulation results proved the operation of the proposed converter topology.

#### 1.5.4 <u>Results Section</u>

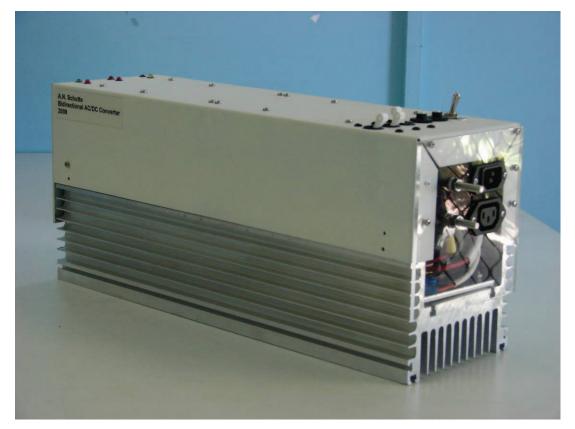

Chapter 10 (Physical Implementation) briefly describes the construction of the converter prototype and provides images of the final product.

Chapter 11 (Measurements and Results) reports the results of measurements made with the prototype converter. Measurements are shown that verify the correct operation of the various sub-systems of the converter. The converter is operated in DC output mode and the resulting measurements verified the operation of the converter in all four quadrants. A ringing effect was observed during these tests, which significantly affected on the operation of the converter. The DC efficiency of the converter in the forward mode was also determined. The results of measurements with the converter operating in closed-loop AC mode are also reported. These results confirm that the converter is capably of feeding AC loads of any power factor.

Chapter 12 (Conclusions and Recommendations) evaluates the success of the project by considering the achievement of the deliverables defined in Chapter 1. For each deliverable, the degree of success, the successful and unsuccessful design elements and the recommendations for future work is given.

#### 1.5.5 Appendices

Two appendices to this thesis are provided, namely Appendix A and Appendix B.

Appendix A contains all tables, schematics and PCB layouts referred to in the main text.

Appendix B contains all computer code that was generated for the project. Code generated includes Matlab, VHDL and C programs.

Figure 2: Prototype Bidirectional Bipolar Converter

# 2 Literature Study

# 2.1 Chapter Introduction

Within the field of Power Electronics, there are two areas that are of particular interest for the development of the proposed bi-directional, direct conversion, DC-AC converter. These two areas are namely that of bi-directional converter design, as well as that of current mode control methodologies.

Within the area of bi-directional converter design, there is a definite boundary between DC-DC and DC-AC converters. Almost all commercially available bi-directional low voltage DC to high voltage AC converters consists of a DC-DC converter with a transformer, followed by a DC-AC inverter. As such, the original literature review for this thesis found no applicable references that describe a direct conversion DC-AC converter. An overview will therefore be given of the bi-directional DC-DC converter with transformers that formed the basis of the proposed converter design.

All of the converters discussed in this section require some form of current more control. Current mode control of switch-mode converters is viewed as an advanced method for controlling converters that cannot be satisfactorily controlled by voltage mode control. Although several methods of current mode control are described in literature, Average Current Mode Control (ACMC) has recently become popular. It will be shown that ACMC is suited for use with the proposed converter topology.

Chapter 3 develops the topology of the proposed converter from basic step-up and step-down converters. The operation of the proposed converter is similar to that of the converters evaluated in this chapter. Since the operation of the proposed bi-directional converter is described in detail in Chapter 3, a detail description will not be repeated here for every converter discussed. Instead, the reader is invited to refer to Chapter 3 if the operation of the converters in this chapter is not entirely clear.

# 2.2 Overview of Bi-Directional DC-DC Converter Topologies

#### 2.2.1 Usage of Bo-Directional DC-DC Converters

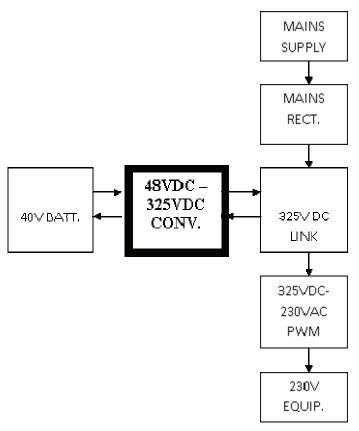

Consider again the main topic of this report, the bi-directional converter shown as part of the household renewable energy system of Figure 2. A requirement was defined in Chapter 1 that the converter shall directly convert between the low voltage DC and high voltage AC sides in a single step. This requirement attempts to reduce the converter cost and increase the efficiency by not using an intermediate high-voltage DC bus. If the requirement for direct conversion is omitted, the converter of Figure 2 is in fact a relatively common device, often referred to as an Uninterruptible Power Supply (UPS).

Figure 3 shows a typical arrangement for an on-line UPS.

Figure 3: Typical On-Line UPS Layout

In this system arrangement, a DC link capacitor is used on the high-voltage side of the DC-DC converter. It is fed from the mains supply through a bridge rectifier, and supplies user loads via a DC-AC PWM controlled bridge inverter. Note that in addition to not supporting direct conversion, this system layout requires two DC-AC inverters if energy is to be supplied back into the mains grid.

The interface between the low and high voltage buses (that is between the DC link capacitor and the batteries) in Figure 3 is now a bi-directional DC-DC converter. Although some lower cost UPS systems use separate charging and discharging circuits, many systems use a bi-directional converter similar to that of the proposed converter.

The following two converters represent typical topologies for this bidirectional DC-DC converter, and are closely related to the proposed converter of this thesis.

#### 2.2.2 <u>Current Source DC-DC Converter</u>

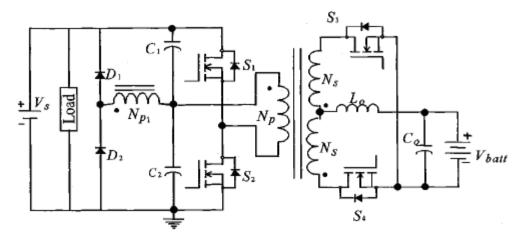

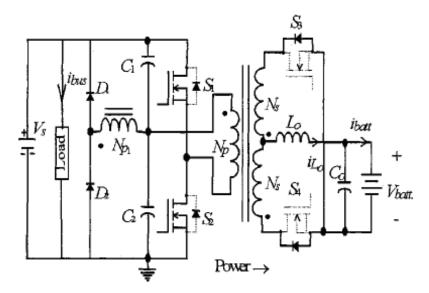

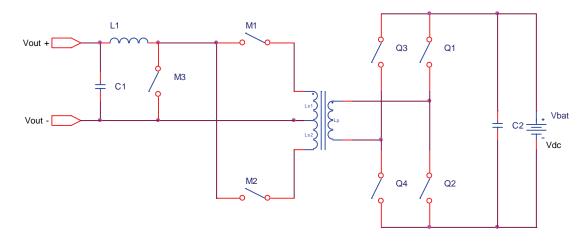

The original reference for this project is the converter of Figure 4 proposed by (Jain et al, 2000: 595). It is referred to as a current source converter due to the inductor at its battery side.

Figure 4: Current Source DC-DC Bi-Directional Converter

Capacitors C1 and C2 are used on the high voltage side of the transformer to provide a midpoint reference at  $0.5V_s$ . During the forward mode (battery charging), switches S1 and S2 operate as a half-bridge converter driving the primary winding of the transformer with a square voltage waveform. It is customary to include a resistor across each of C1 and C2, in order to ensure that the midpoint reference does not drift. These resistors typically dissipate a relatively large amount of power and reduce the converter efficiency. In the topology of Figure 4, these resistors are replaced with an auxiliary primary winding that has the same amount of turns and is in phase with the main primary winding. Together with diodes D1 and D2, this auxiliary winding maintains the midpoint reference.

#### 2.2.2.1 Forward Operation

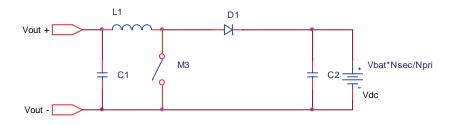

Figure 5 shows the forward operation of the current source DC-DC converter (Jain et al, 2000: 596).

**Figure 5: Current Source Converter: Forward Operation**

During the forward mode, the body diodes of S3 and S4 act as a half-bridge rectifier, and the switches S3 and S4 are not actively switched. When voltage is applied to the primary winding, one of the secondary windings will alternately induce a voltage at its switch (S3 or S4) that is negative with regards to the battery negative terminal. Since the body diode of that switch will be forward biased, it will conduct and current will build up in the inductor.

When voltage is not applied to the primary winding, the inductor current will drive the centre tap of the secondary winding negative, and both the body diodes of S3 and S4 will conduct. Since the current flow will be in opposite directions in the two windings, their magnetic fields will cancel and no power will be coupled to the high voltage side. In this case, the centre tap of the transformer, and thus the inductor, in effectively shorted to the negative battery terminal and the inductor current is sustained through both body diodes. This effect is discussed in more detail in Chapter 3.

The inductor and output capacitor act as the usual LC filter found in a basic step-down converter.

Note that the operation of the present converter is identical to that of a stepdown converter, with the exception of the inclusion of the transformer. It may also be noted that the forward mode can be easily controlled with a voltagemode controller.

#### 2.2.2.2 Current Source Converter Reverse Operation

Figure 6 shows the reverse operation of the current source DC-DC converter (Jain et al, 2000: 596).

Figure 6: Current Source Converter: Reverse Operation

For the reverse mode, the body diodes of switches S1 and S2 on the high-voltage side act as a half-bridge rectifier. The auxiliary primary winding again ensures that the midpoint reference does not drift during operation.

In order to reverse the direction of power flow, switches S3 and S4 are switched in simultaneously. As with the forward mode, the currents in the two secondary windings then flow in opposite directions, so that their magnetic fields cancel and no power is coupled to the primary side. The effect of this is that the transformer side of the inductor is effectively shorted to the battery negative terminal, so that the current inductor current increases in the reverse direction. When S3 or S4 is now alternately switched off, the inductor current is forced through one of the secondary windings, and the power is coupled to the primary winding, where it is rectified.

Note that the operation of the converter in the reverse mode is identical to that of a basic-step converter, with the addition of the transformer. The inductor is placed in series with the battery, so that a higher voltage is applied to the secondary windings than what was possible during the forward mode.

The reason for the inclusion of this step-up converter in the topology is the non-unity duty cycle problem in bi-directional converters. This problem is discussed in Chapter 3 during the development of the proposed topology.

This converter requires current mode control during the reverse mode, as discussed in the section 2.2.2.3.

#### 2.2.2.3 Evaluation of Current Source DC-DC Converter

The author designed and constructed a converter based upon this topology for his final year engineering project (Schutte, 2002). Although the topology does provide a means for bi-directional power flow between two DC levels, it does have several disadvantages.

The major disadvantage is that the inductor is on the low-voltage side, where the current is the highest. With power ratings in the order of 1-2 kW, the currents in the inductor become large, and therefore the inductor itself becomes uncomfortably large.

The large currents are also present in the secondary windings. When S3 or S4 switches off, the current through the concerned secondary winding has to be completely blocked by the switch. There is no freewheeling path for the winding current, and the switch transistor must do a hard turn-off. Since the secondary windings have inductance, the switch turn-off exhibit large voltage spikes that required the use of significant snubber circuits. It was found that the snubbers dissipate a relatively large amount of energy.

Furthermore, current mode control of the converter was required for the reverse mode. Voltage mode control cannot be used, since the output voltage does not necessarily increase with an increase in duty cycle. This can be seen by considering a 100% duty cycle, where both S3 and S4 is permanently on. The inductor current increases linearly, but the actual output voltage decreases since no power is transferred to the high voltage side. The inductor current will therefore increase unbounded until component failure occurs.

No current mode control integrated circuit is available for this topology, and the author developed a complex analogue current mode controller for this purpose. Its operation however did not prove reliable.

#### 2.2.3 Dual Inductor Current Source DC-DC Converter

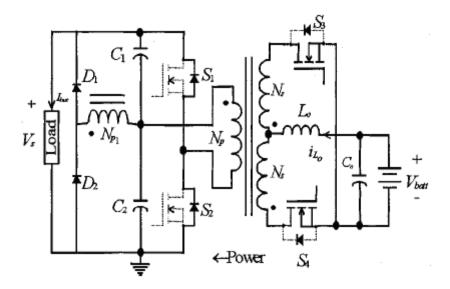

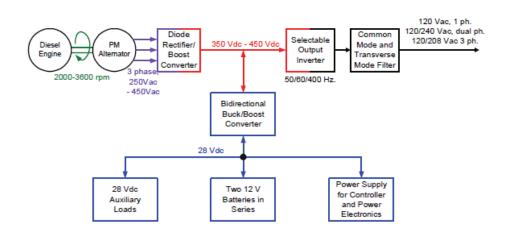

A similar but more advanced topology has been suggested by (Tolbert et al, 2002: 2). This topology was developed for use in the military generator / UPS combination of Figure 7:

Figure 7: Combined Generator / UPS System

The batteries are used as a source of power when high power loads are connected to the output. During normal operation they are charged by the permanent magnet alternator through the bi-directional DC-DC converter. During backup operation the current flow is reversed and power is supplied to the DC link. The following discussion will focus on the DC-DC converter of this system.

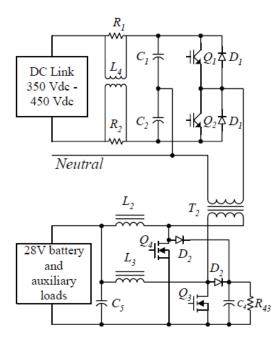

The bi-directional DC-DC converter topology developed for this system attempts to solve some of the problems of the previous topology by using two inductors, as shown in Figure 8 (Tolbert et al, 2002: 3).

Figure 8: Dual Inductor DC-DC Converter

In addition to the two-inductor layout, the topology also uses a RL link damper (R1, R2 and L4) in order to prevent oscillations between C1 and C2, and the alternator converter capacitors. R43 and C4 are used as a snubber circuit.

The operation of this converter is similar to that of the current source converter of the previous section. The discussion of section 2.2.3.1 therefore focuses on the differences between the two topologies.

#### 2.2.3.1 Operation of Dual Inductor DC-DC Converter

During the forward mode, the high-voltage side again acts as a half-bridge converter driving the transformer primary winding. The topology however uses two inductors on the low-voltage side, coupled to a single secondary winding. This arrangement acts as a current doubler rectifier, which is basically two step-down converters in parallel. When the secondary winding voltage is positive, the body diode Q3 conducts and current in L2 builds up. When the secondary winding voltage is negative, the body diode of Q4 conducts and current builds up in L3.

During the reverse mode, switches Q3 and Q4 is operated in exactly the same way as for the previous topology. Both are switched on simultaneously, and are then alternately switched off. When a switch turns off, the associated inductor current is forced through the secondary winding, and power is coupled to the primary side where it is rectified. Note that the switch that is switched on when the other is turned off has to carry the currents of both inductors.

#### 2.2.3.2 Evaluation of Dual Inductor DC-DC Converter

The dual inductors of Figure 8 have the major advantage of not requiring large snubber circuits as with the current source converter. When Q3 or Q4 turns

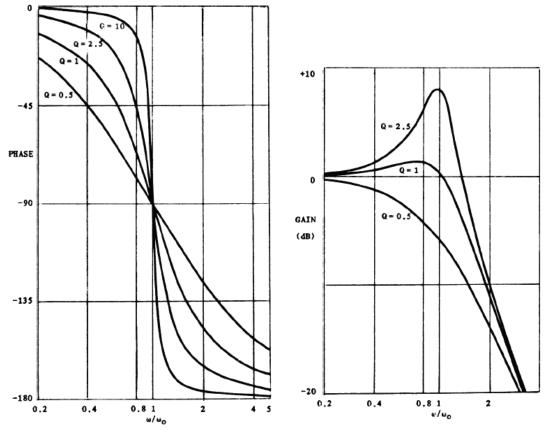

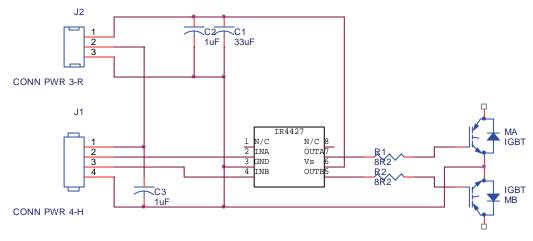

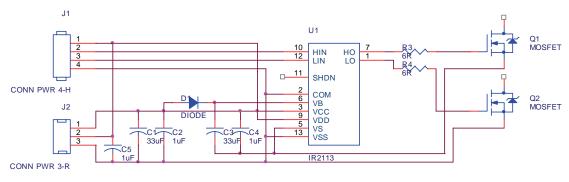

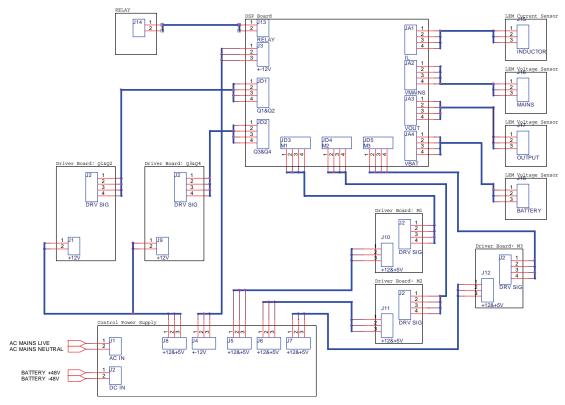

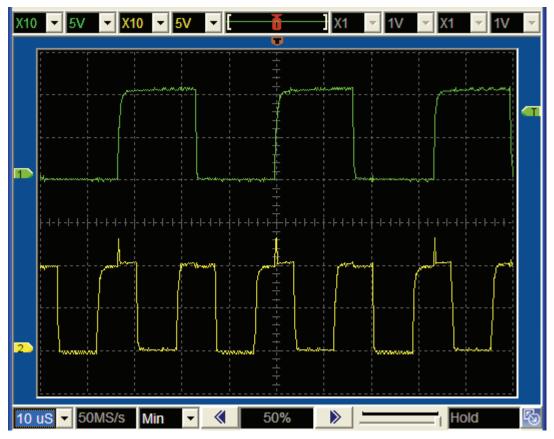

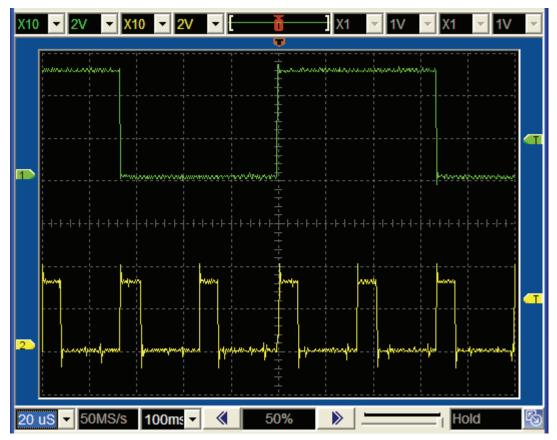

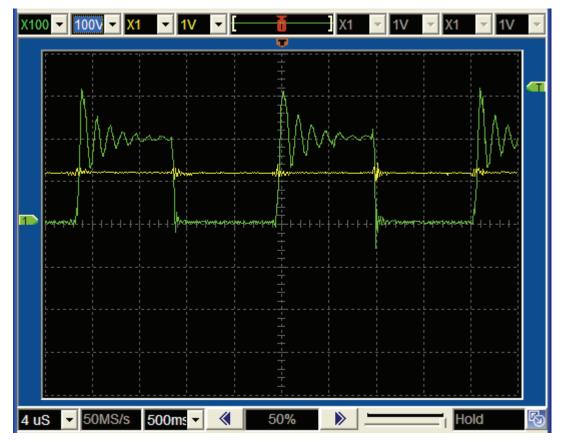

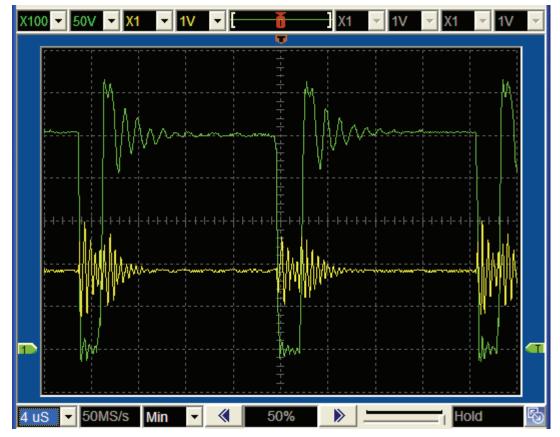

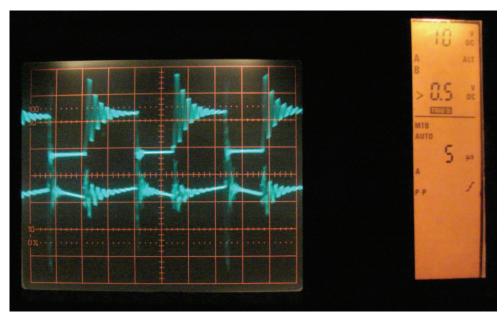

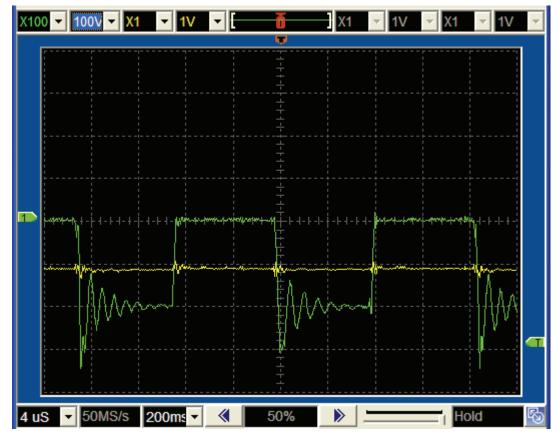

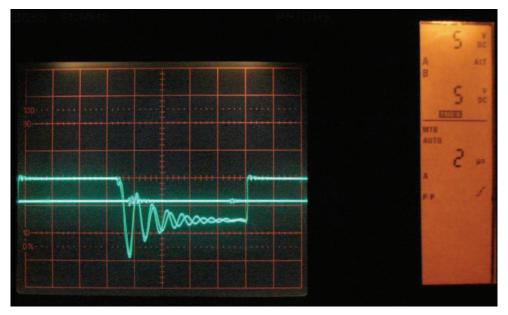

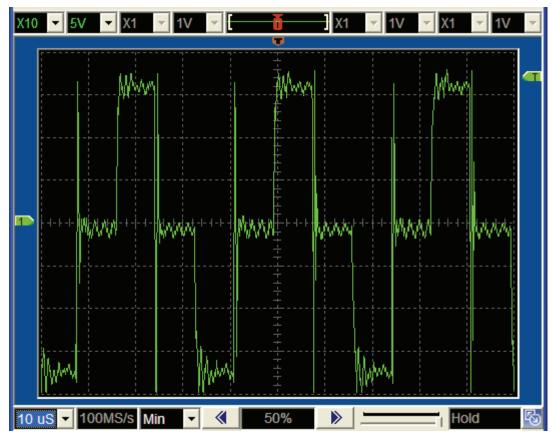

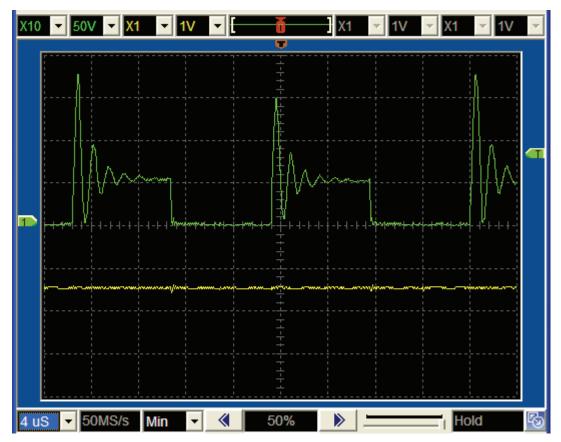

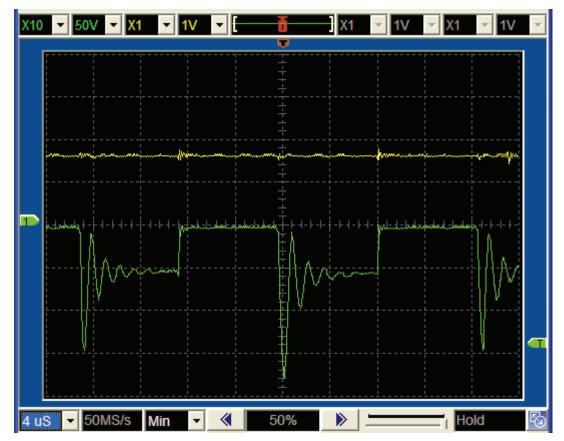

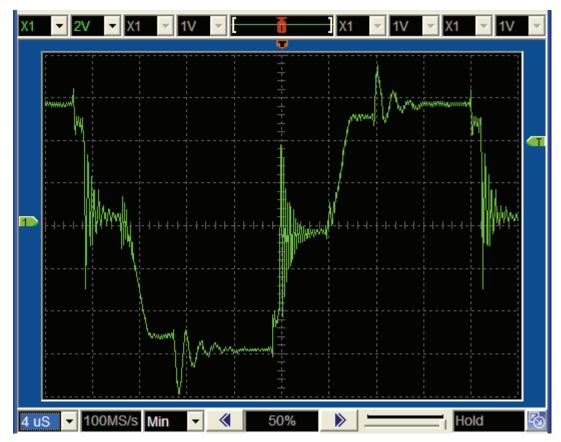

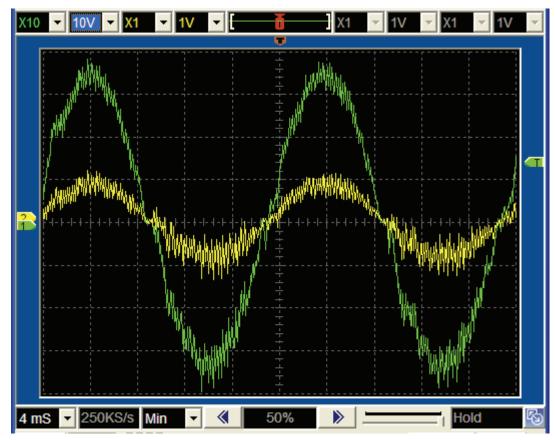

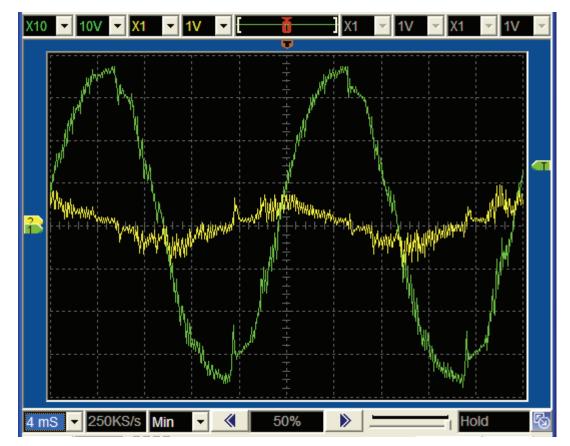

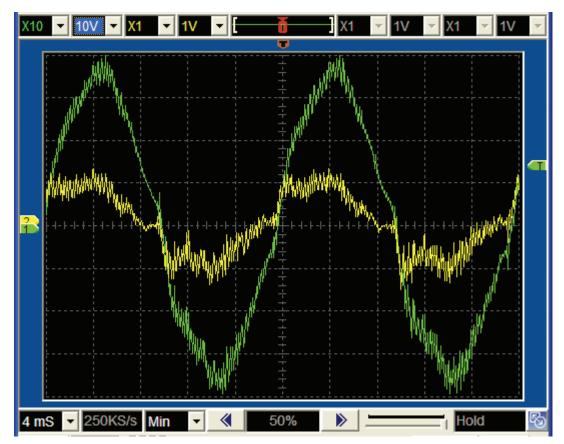

off, the inductor current is forced through the secondary winding. Thus, it is not a hard turn-off where the current through an inductive component (winding) has to be stopped, as in the previous topology. This greatly increases the efficiency and simplifies the design.