## A Reusable Signal Processing Architecture for Satellite Based Communication Systems

by

Jakobus Stephanus Botha

Thesis presented in partial fulfilment of the requirements for the degree of Master of Science in Electronical Engineering at Stellenbosch University

> Supervisor: Dr G-J van Rooyen Department of Electrical and Electronic Engineering

> > ${\rm March}~2011$

## Declaration

By submitting this thesis electronically, I declare that the entirety of the work contained therein is my own, original work, that I am the sole author thereof (save to the extent explicitly otherwise stated), that reproduction and publication thereof by Stellenbosch University will not infringe any third party rights and that I have not previously in its entirety or in part submitted it for obtaining any qualification.

Date: March 2011

Copyright © 2011 Stellenbosch University All rights reserved.

## Abstract

**Keywords:** digital signal processing, embedded systems, telecommunications, satellite technology

The rapid growth of the telecommunications industry is a worldwide phenomenon with people and computers generating and transmitting more and more information daily. Despite this growth, there are still areas in South Africa which lack terrestrial communications coverage. People inhabit these rural areas and their essential communication needs are not met. Satellite based communication coverage can provide a valuable service in these circumstances.

In this thesis, the design of a satellite-based communications payload – which makes use of software defined radio techniques – is presented in terms of the Open Systems Interconnect layer structure. A robust hardware plat-form using a space-qualified on-board computer, a Xilinx Virtex-5 Field Programmable Gate Array (FPGA) and a Freescale digital signal processor (DSP) is designed, implemented and thoroughly tested. A device driver is designed for hardware and firmware components. A prototype ground station is also designed and constructed using a low-power PC, a Xilinx Spartan-3E FPGA, a Freescale DSP and radio frequency hardware.

A wide range of testing methodologies were successfully utilised to deploy a functional system which is critically evaluated in the last chapter.

## Uittreksel

**Sleutelwoord:** syferseinverwerking, toegewyde stelsels, telekommunikasie, satelliettegnologie

Die vinnig groeiende telekommunikasieindustrie is 'n wêreldwye verskynsel waarin mense en rekenaars daagliks meer en meer data genereer. Ten spyte van die groei, is daar nog steeds gebiede in Suid-Afrika wat aan 'n gebrek van aardse kommunikasiedekking lei. Mense bewoon dié areas maar daar word nie aan hul noodsaaklike kommunikasiebehoeftes voldoen nie. Satelliet-gebaseerde kommunikasiedekking kan 'n waardevolle diens in hierdie omstandighede wees.

Hierdie tesis beskryf die ontwerp van 'n ruimtegebaseerde kommunikasieloonvrag – wat gebruik maak van sagteware-gedefinieerde radiotegnieke – aangebied in terme van die Open Systems Interconnect laagstruktuur. 'n Robuuste apparatuurplatform wat gebruik maak van 'n ruimte-gekwalifiseerde rekenaar, 'n Xilinx Virtex-5 Veldprogrameerbare Hek-Skikking (VPHS) en 'n Freescale syferseinverwerker is ontwerp, geïmplementeer en deeglik getoets. 'n Toestelbestuurder moes ontwerp word vir die apparatuur- en fermatuur-komponente. 'n Prototipe grondstasie is ook ontwerp en gebou met behulp van 'n lae-krag PC, 'n Xilinx Spartan-3E VPHS, 'n Freescale seinverwerker en radiofrekwensie apparatuur.

'n Wye verskeidenheid van toetsmetodes is suksesvol benut om 'n funksionele stelsel te ontwikkel wat krities geëvalueer word in die laaste hoofstuk.

## Acknowledgements

- Most of my thanks goes to Dr G-J van Rooyen for his inspiration and guidance as my supervisor.

- I also extend heartfelt thanks to the Department of Communications of the South African government for showing a strong interest in extrater-restrial communications systems and for initialising this project.

- I also acknowledge my friend Adrian Cooke for introducing me to Dr Riaan Wolhuter after a particularly pleasant hike in Stettynskloof.

- I would like to thank Dr Wolhuter for his support during the project. His many interesting stories and his wisdom provided me with inspiration during my studies.

- I would also like to thank the many friends I've made in the E&E faculty. Some inspiring and thought provoking lunches have helped me grow as a person. Especially those with Albert Visagie, Pieter Holtzhauzen, Charl Botha and Edward de Villiers.

- My parents deserve a lot of my thanks for their continued support during my studies.

- Lastly I would like to thank my colleague Ewald van der Westhuizen for the long hours of team work during the project's integration phase.

## Contents

| D             | eclar                                                       | ation                                                                                                                                                                                                                                                        | i                                                                                                          |

|---------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| A             | ckno                                                        | wledgements                                                                                                                                                                                                                                                  | iv                                                                                                         |

| C             | onter                                                       | its                                                                                                                                                                                                                                                          | $\mathbf{v}$                                                                                               |

| Li            | st of                                                       | Figures                                                                                                                                                                                                                                                      | vii                                                                                                        |

| $\mathbf{Li}$ | st of                                                       | Tables                                                                                                                                                                                                                                                       | ix                                                                                                         |

| N             | omer                                                        | nclature                                                                                                                                                                                                                                                     | $\mathbf{x}$                                                                                               |

| <b>1</b><br>2 | $1.1 \\ 1.2 \\ 1.3 \\ 1.4$                                  | <b>Project Background</b> Project Background         Project Evolution       Proposed Solution         Proposed Solution       Structure of This Thesis         Structure of This Thesis       Structure         thodology and Perspective       Methodology | <b>1</b><br>1<br>2<br>3<br>4<br><b>6</b><br>6                                                              |

|               | 2.1<br>2.2<br>2.3<br>2.4                                    | OSI Model                                                                                                                                                                                                                                                    | 7<br>8<br>11                                                                                               |

| 3             | Pay<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8 | Ioad DesignPayload Design OverviewThe SH4 On-Board ComputerOBC Design in Terms of the OSI ModelOBC Resource ManagerDownlink TransmitterThe Software Defined RadioThe Field Programmable Gate ArrayFPGA Design in Terms of the OSI Model                      | <ol> <li>12</li> <li>13</li> <li>14</li> <li>17</li> <li>20</li> <li>21</li> <li>25</li> <li>26</li> </ol> |

| 4             | Gro                                                         | ound Station Design                                                                                                                                                                                                                                          | <b>32</b>                                                                                                  |

|          | 4.1                  | Necessary Hardware                  | 32         |

|----------|----------------------|-------------------------------------|------------|

|          | 4.2                  | Ad Hoc Sensor Network               | 34         |

|          | 4.3                  | PC                                  |            |

|          | 4.4                  | FPGA                                |            |

|          | 4.5                  | Modem                               |            |

|          | 4.6                  | DAC                                 | 38         |

|          | 4.7                  | Quadrature Upmixer                  |            |

|          | 4.8                  | RF Hardware                         | 38         |

|          | 4.9                  | Transmitter (Uplink) Antenna        | 39         |

|          | 4.10                 | Receiver (Downlink) Antenna         |            |

|          | 4.11                 | Downlink Data Radio                 | 40         |

| <b>5</b> | Pay                  | load Implementation                 | <b>4</b> 4 |

|          | 5.1                  | Development Environment             | 44         |

|          | 5.2                  | Electrical Interface Connections    |            |

|          | 5.3                  | OBC Resource Manager Implementation |            |

|          | 5.4                  | FPGA Firmware                       | 56         |

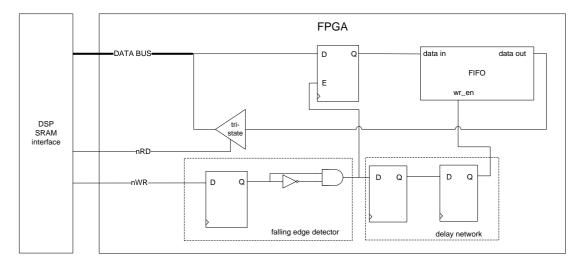

|          | 5.5                  | DSP SRAM Interface                  | 61         |

|          | 5.6                  | Downlink Data Radio Implementation  | 62         |

|          | 5.7                  | Low Level Integration Testing       | 63         |

| 6        | Gro                  | und Station Implementation          | 67         |

|          | 6.1                  | Downlink Receiver                   | 67         |

|          | 6.2                  | Uplink Transmitter                  | 68         |

| 7        | Inte                 | gration and Testing                 | 79         |

|          | 7.1                  | Payload Loopback Tests              | 79         |

|          | 7.2                  | Ground Station Integration Tests    | 81         |

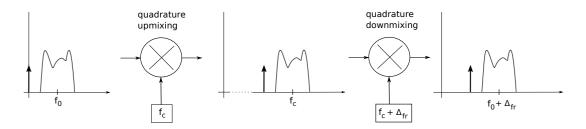

|          | 7.3                  | Quadrature Mixing Integration Test  | 83         |

|          | 7.4                  | Ground Station Loopback Test        | 84         |

| 8        | Con                  | clusion                             | 89         |

|          | 8.1                  | Summary of Completed Work           | 89         |

|          | 8.2                  | Recommendations                     | 90         |

|          | 8.3                  | Final Comments                      | 90         |

| A        | $\operatorname{Tim}$ | ing Diagrams                        | 92         |

| в        | Gro                  | und Station RF Power Measurements   | 93         |

| Bi       | bliog                | raphy                               | 95         |

|          | - C                  |                                     | -          |

# List of Figures

| 1.1          | Overview of the SAA platform                                                 |

|--------------|------------------------------------------------------------------------------|

| $2.1 \\ 2.2$ | A simplified OSI model.8The SAA subsystem.9                                  |

| 3.2          | Client software device access sequence                                       |

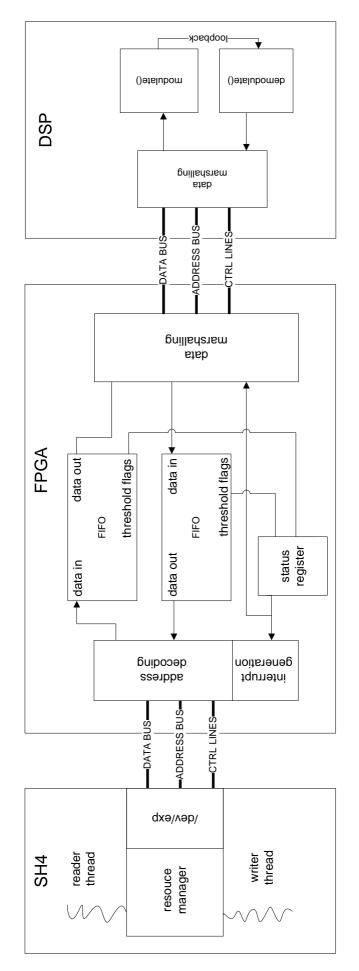

| 3.6          | DSP-FPGA dataflow diagram                                                    |

| 3.1          | The greater payload                                                          |

| 3.3          | Use case diagram for the resource manager                                    |

| 3.4          | Interrupt generation sequence                                                |

| 3.5          | ISR integration diagram                                                      |

| 3.7          | Payload FPGA firmware                                                        |

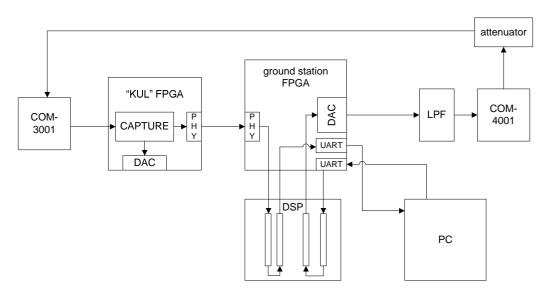

| 4.1          | Functional overview of the ground station                                    |

| 4.2          | Ground station overview                                                      |

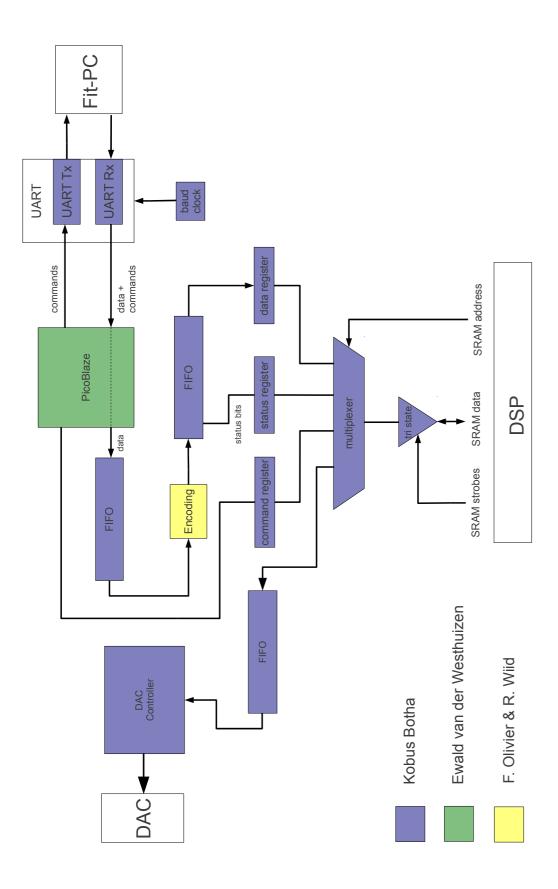

| 4.3          | Ground station FPGA firmware. $\ldots \ldots \ldots \ldots \ldots \ldots 43$ |

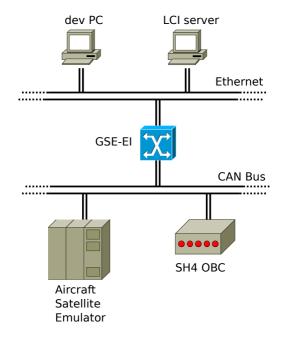

| 5.1          | CAN bus development environment                                              |

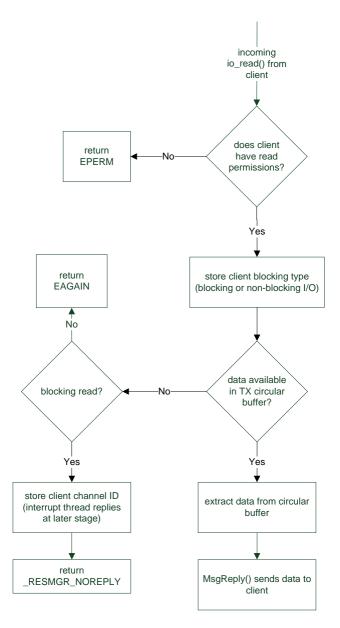

| 5.2          | io_read() operations                                                         |

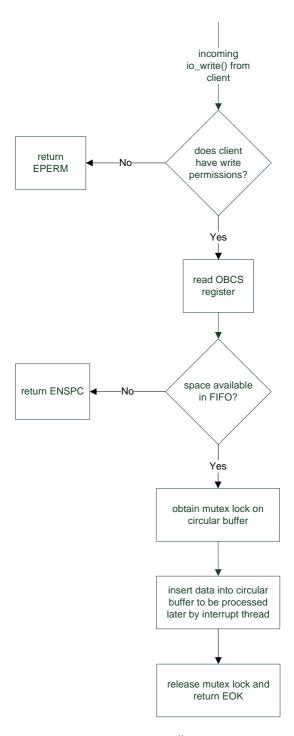

| 5.3          | io_write() operations                                                        |

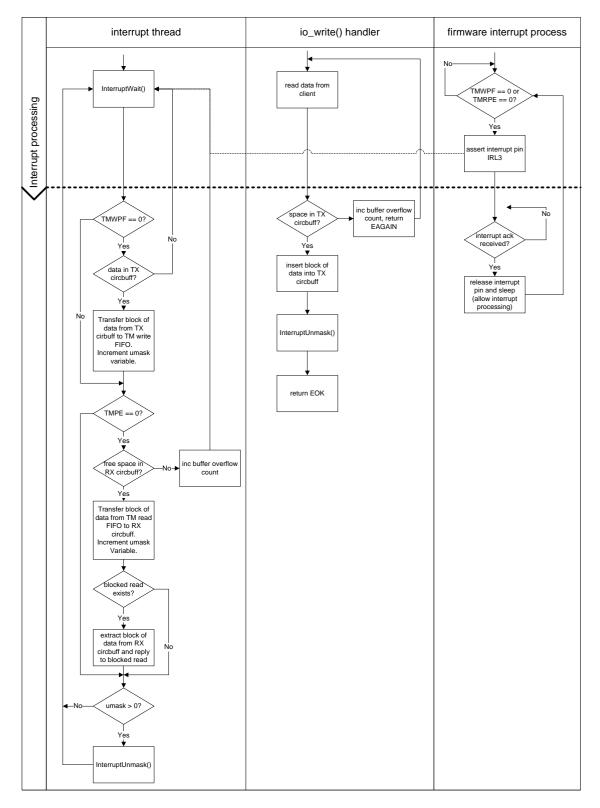

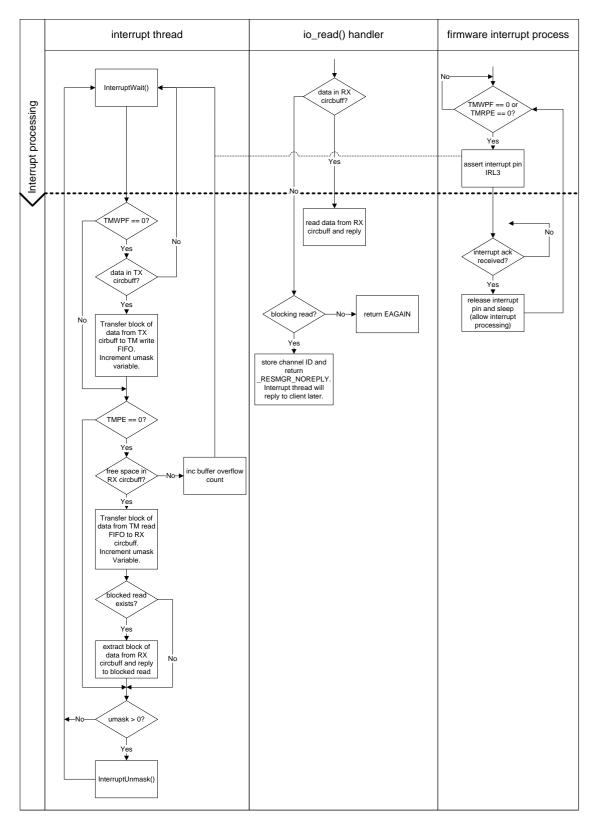

| 5.4          | Interrupt interaction detail: write()                                        |

| 5.5          | Interrupt interaction detail: read()                                         |

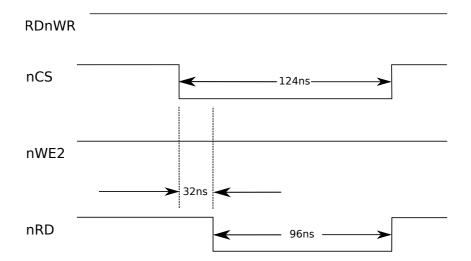

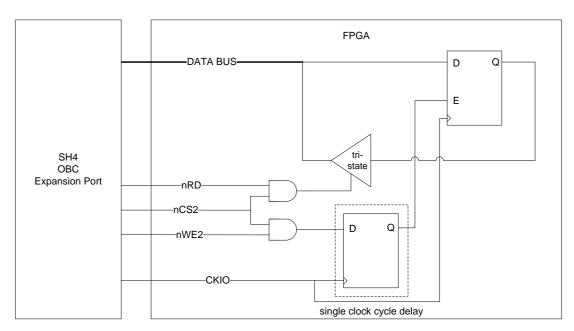

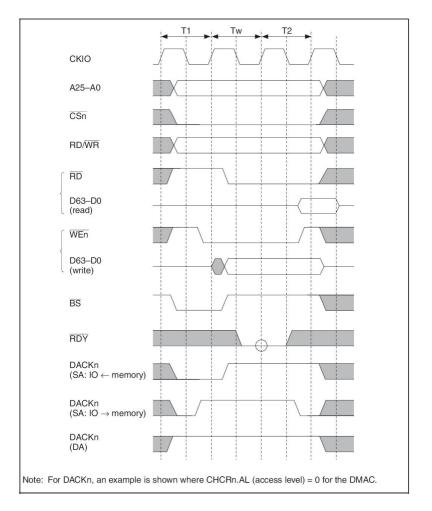

| 5.6          | Expansion port read timings                                                  |

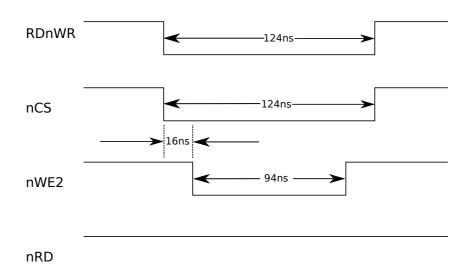

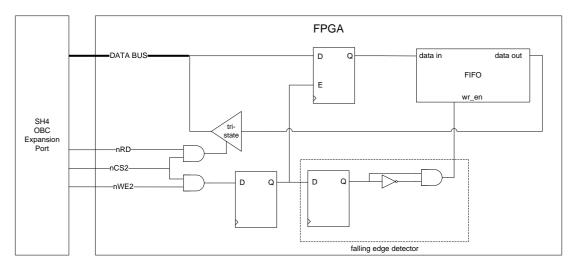

| 5.7          | Expansion port write timings                                                 |

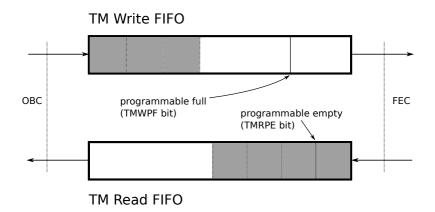

| 5.8          | FIFO thresholds                                                              |

| 5.9          | Register loopback test                                                       |

| 5.10         | OBC single FIFO loopback test                                                |

| 5.11         | DSP single FIFO loopback test                                                |

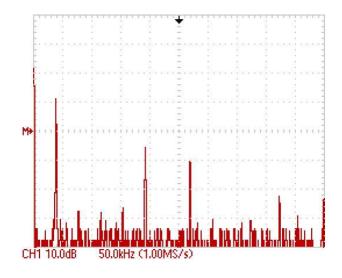

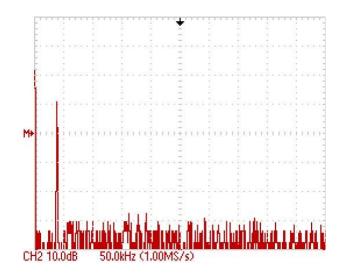

| 6.1          | FFT of a single DDS output channel                                           |

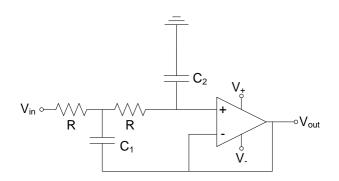

| 6.2          | Sallen-Key low pass filter                                                   |

| 6.3          | FFT of a single reconstruction filter output channel                         |

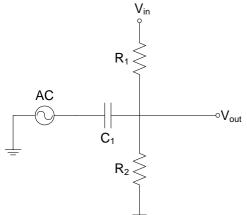

| 6.4          | DC offset adding circuit                                                     |

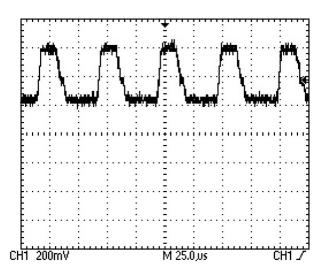

| 6.5          | Distortion noted on DAC outputs                                              |

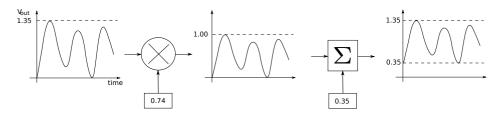

| 6.6          | Analogue representation of DAC output scaling                                |

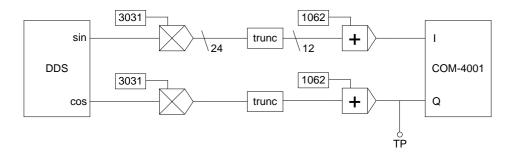

|              |                                                                              |

| 6.7                                                            | Digital DC offset.                                                     | 75 |

|----------------------------------------------------------------|------------------------------------------------------------------------|----|

| 7.1                                                            | Resource manager with dual FIFO loopback test                          | 80 |

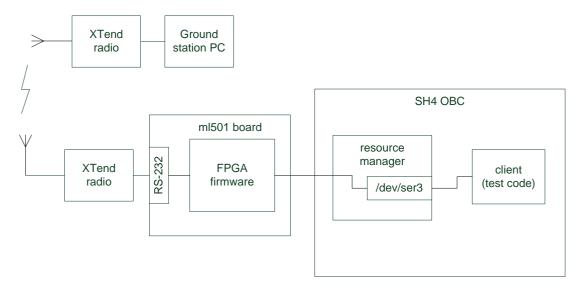

| 7.2                                                            | Data radio integration test.                                           | 82 |

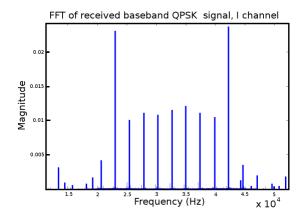

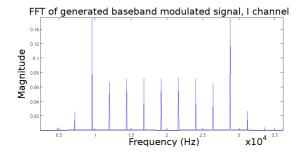

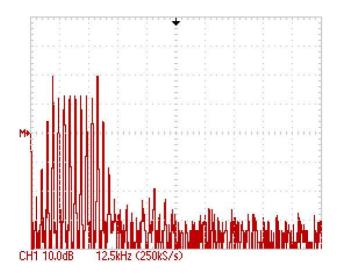

| 7.3                                                            | Fast Fourier Transform of the COM-3001 test point 1 signal             | 83 |

| 7.4 Fast Fourier Transform of a baseband modulated signal gene |                                                                        |    |

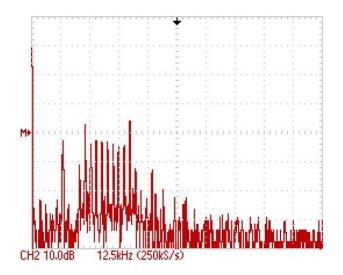

|                                                                | in Matlab                                                              | 84 |

| 7.5                                                            | Ground station RF integration.                                         | 85 |

| 7.6                                                            | FFT of a modulated uplink message signal.                              | 86 |

| 7.7                                                            | FFT of a received baseband signal.                                     | 86 |

| 7.8                                                            | Frequency domain representation of carrier leakage                     | 87 |

| 7.9                                                            | SH4 OBC, FPGA and DSP loopback test.                                   | 88 |

| A.1                                                            | SRAM interface wait timing (software wait only) $\ldots \ldots \ldots$ | 92 |

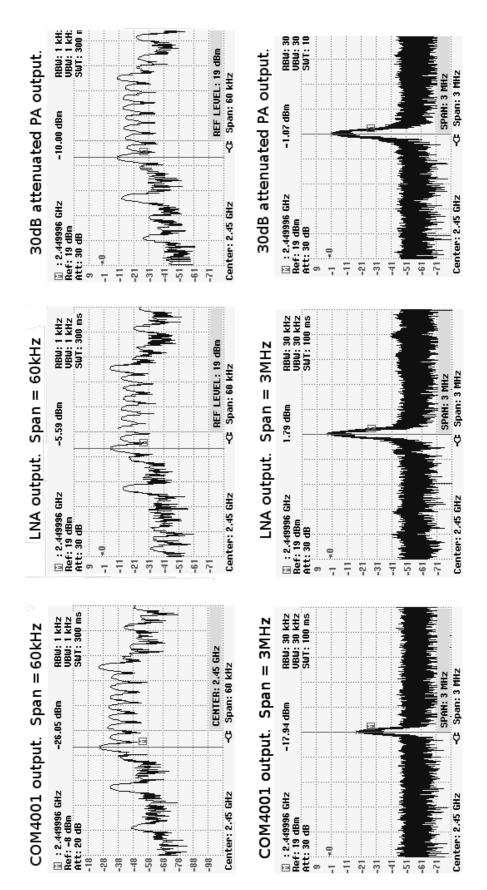

| B.1                                                            | Ground station RF measurements.                                        | 94 |

## List of Tables

| 4.1 | Quadrature mixer comparison                  | 38 |

|-----|----------------------------------------------|----|

| 5.1 | Simplified OBC expansion port firmware model | 19 |

| 5.2 | OBCS bit definitions                         | 50 |

| 5.3 | OBCC bit definitions                         | 51 |

| 6.1 | PA pin voltages.                             | 77 |

| 6.2 | RF power measurements                        | 77 |

## Nomenclature

### Acronyms

| ADC                   | Analogue-to-Digital Converter                |

|-----------------------|----------------------------------------------|

| ASE                   | Aircraft-to-Satellite Emulator               |

| CAN                   | Controller Area Network                      |

| CMOS                  | Complementary Metal-Oxide-Semiconductor      |

| CPG                   | Clock Pulse Generator                        |

| CPU                   | Central Processing Unit                      |

| DAC                   | Digital-to-Analogue Converter                |

| DRAM                  | Dynamic Random Access Memory                 |

| DSP                   | Digital Signal Processor                     |

| EDC                   | Error Detection and Correction               |

| EDC<br>EMC            |                                              |

|                       | Electromagnetic Compatibility                |

| EMI                   | Electromagnetic Interference                 |

| FFT                   | Fast Fourier Transform                       |

| FIFO                  | First In First Out                           |

| FPGA                  | Field Programmable Gate Array                |

| FSM                   | Finite State Machine                         |

| I/Q                   | In-phase/Quadrature                          |

| ISM                   | Industrial, Scientific and Medical           |

| ISR                   | Interrupt Service Routine                    |

| KUL                   | Katholieke Universiteit Leuven               |

| LEO                   | Low Earth Orbit                              |

| LNA                   | Low Noise Amplifier                          |

| LO                    | Local Oscillator                             |

| LVCMOS                | Low Voltage CMOS                             |

| LVDS                  | Low Voltage Differential Signaling           |

| MCCPL                 | Multiple Channel Communications Payload      |

| OBC                   | On Board Computer                            |

| PA                    | Power Amplifier                              |

| $\operatorname{PLL}$  | Phase Locked Loop                            |

| POSIX                 | Portable Operating System Interface for Unix |

| $\operatorname{QPSK}$ | Quadrature Phase Shift Keying                |

| $\operatorname{RF}$   | Radio Frequency                              |

|                       |                                              |

| SAA           | Steerable Antenna Array                     |

|---------------|---------------------------------------------|

| SH4           | SuperH-4                                    |

| SIC           | Signal Interface Card                       |

| SRAM          | Static Random Access Memory                 |

| SPI           | Serial Peripheral Interface                 |

| $\mathrm{TM}$ | Telemetry                                   |

| UART          | Universal Asynchronous Receiver/Transmitter |

| USB           | Universal Serial Bus                        |

| VHDL          | VHSIC Hardware Description Language         |

| VHSIC         | Very-High-Speed Integrated Circuits         |

## Terms of Reference

This project began during a commissioning by the Department of Communications of the South African government – with the University of Stellenbosch as contractors – for a multiple channel communications system that would possibly provide telecommunications coverage in remote areas of South Africa. It was to be implemented as a payload on a low earth orbit satellite.

The project funding was canceled by the Department of Communications after the first year and the project continued in academic form. The Katholieke Universiteit Leuven (KUL) subsequently expressed interest in developing a payload for a low earth orbit satellite using a Steerable Antenna Array (SAA). Much of the development done for the Department of Communications could be used as-is for the KUL project.

Specific constraints were placed on the project by KUL and the project supervisors:

- two Xilinx field programmable gate array boards, an ML501 and a Spartan-3E were to be used for the research done by Francois Olivier into low density parity check codes,

- a Freescale DSP development kit was to be used for the signal processing tasks as the hardware and design experience was available within the group,

- a Renesas SH4, from the engineering model of Sumbandila Satellite's communications payload, was to be used as on-board computer as it was immediately available and supported by Sun Space,

- the space readiness in terms of radiation tolerance and vibration resistance of the hardware was only to be investigated during a subsequent phase of the project,

- KUL would supply the steerable antenna array which was to be tested,

- a minimum data rate of 19 200 bits per second was required by KUL for the communications link and

- the error correction code rate used by Francois Olivier would double the effective data baud rate, resulting in a physical layer baud rate of 38 400 bits per second.

The specific objectives identified for the part of the project documented in this thesis, were:

- physical integration and interconnection of all hardware components,

- low level software design on the Renesas SH4 to provide software interfaces to off-board hardware resources,

- low level software design on the Freescale DSP to provide a software interface to the external hardware,

- firmware design on the Xilinx FPGAs to enable interfacing with external components,

- radio frequency component selection to enable transmission of data over the channel and

- design of a prototype ground station which would be used for testing of the SAA.

## Chapter 1

## Introduction

### 1.1 Project Background

The rapid growth of the telecommunications industry is a worldwide phenomenon with people and computers generating and transmitting more and more information each day. Despite this rapid growth, there are still areas in South Africa without communications coverage. People inhabit these rural areas, yet certain essential communication needs are often not met. For example, rural hospitals may find it very difficult to communicate with specialists or suppliers in urban areas. Low-cost, low-bandwidth satellite communications coverage can be a valuable tool in these circumstances. Such a communications system can also, for example, play a central role in the transfer of aggregated data from distributed data capturing units.

SUNSAT, the first locally built satellite, was an Orbital Satellite Carrying Amateur Radio which used frequencies in the Very High Frequency and Ultra High Frequency bands for communication with terrestrial ground stations [6]. The second locally built satellite, Sumbandila, has a low-cost, low-bandwidth communications system on board [12].

The communications payload on the Sumbandila satellite was designed and implemented by Stellenbosch University (SU) and Sun Space and Information Systems with the Department of Communications (DoC) of the South African government as client. The system consists of an On Board Computer (OBC) and a VHF-UHF Communications Unit (VUCU). The VUCU is a full duplex communications unit using separate frequency bands for the uplink and the downlink, the design of which was heavily influenced by SUNSAT. However, the frequencies allocated by the International Telecommunications Union (ITU) and the Independent Communications Authority of South Africa for the uplink and downlink are roughly 0.2 MHz apart and the unit is unable to communicate in full-duplex mode as the transmitted signal's power is much higher than the received signal's, therefore swamping the receiver. Half duplex therefore had to be implemented in software. This meant that the effective data throughput rate of the payload fell to under 4800 bps, which allows only fairly short text messages to be sent.

Also aboard Sumbandila is an experimental payload consisting of various scientific experiments [45]. Among the experiments are:

- An instrument to measure the Earth's atmospheric phenomena below 30 kHz, developed by the University of KwaZulu-Natal,

- The Southern African Amateur Radio Satellite Association has placed an amateur radio service on board which communicates in voice beacon, digipeater and parrot modes,

- The Nelson Mandela Metropolitan University has an experiment to measure the non-linear vibration effects of strings in microgravity and

- Stellenbosch University has an experiment on board which will measure the effects of radiation on electronics.

Central to these experiments was the Stellenbosch University's Software Defined Radio (SDR) group's Signal Interface Card (SIC) which controls the electronics and provides an interface between the experiments and an OBC running Linux. The results of the experiments are then transmitted to earth via a special version of the VUCU.

The DoC then commissioned SU to design a broadband communications payload for possible use on a future satellite. The requirement from the DoC was a high-speed, multi-channel communications system that could be used with low-cost ground stations that could be deployed throughout the country. Three phases spanning three years were alloted for the completion of the project.

In the first year a technological proof of concept of the payload was to be built. During the second year an engineering model would be built. The final phase would see rigorous space readiness testing being done with a flight model being built as final deliverable.

### 1.2 **Project Evolution**

Before the end of the first phase the DoC canceled the project. This happened before the research was completed and put an end to the funding which meant the project continued in an academic form from then on.

Shortly thereafter KUL approached Stellenbosch University with a proposed project to test their SAA on an LEO satellite for their In-Situ Hyper Spectral II (IS-HSII) project. KUL has a potentially novel approach to beam steering from space and they needed a platform on which they could test their antenna. An agreement was reached that Stellenbosch University would provide KUL with a hardware platform which they could used for testing their SAA.

Building space compliant hardware was not possible because there was no existing satellite specification; there were no system constraints such as weight and available space from which a design could begin.

The solution to this is to use Stellenbosch University's Jora lightweight two seat glider. A prototype payload platform would be constructed and used to the test the SAA on the Jora. The prototype would use space compliant hardware where possible but full space compliance would only be considered after the first successful aircraft flight test.

Due to the similarities between the MCCPL and the KUL SAA payload it was decided that the MCCPL architecture would, for the most part, be a good starting point for the design and was used as such. It was also decided that the payload would be a good platform on which to continue the SDR modem design.

### **1.3** Proposed Solution

Much of the hardware and expertise required to implement the KUL SAA testing platform was already available within the group. This was in part due to the MCCPL project. The MCCPL system design was therefore an ideal starting point for the design of the SAA platform. A modified version of the MCCPL architecture was presented to Katholieke Universiteit Leuven by F. Olivier, G-J van Rooyen and R. Wolhuter [47].

The proposal listed the following as key components:

- an aircraft-to-satellite emulator (ASE), which would translate Jora avionics (yaw, pitch and roll) into satellite telemetry,

- the SH4 on-board computer, a space qualified processor unit,

- a software defined radio (SDR) modem to enable data communication and

- a ground station which would communicate with the SAA platform.

The proposal was accepted by KUL. It contained specifications which provided clear objectives for the platform. Among the specifications are:

- the RF operational band used would be the S-band portion of the Industrial, Scientific and Medical (ISM) band,

- a minimum baud rate of 19 200 bps was required for the communications link,

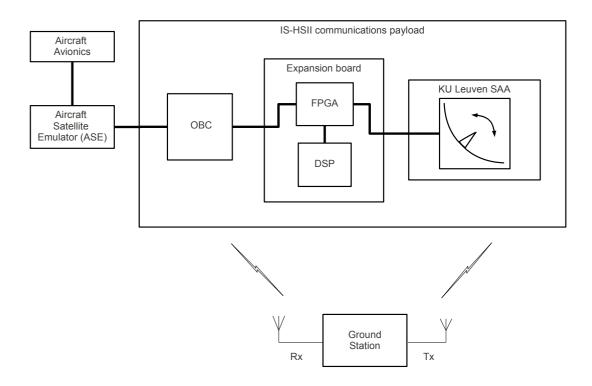

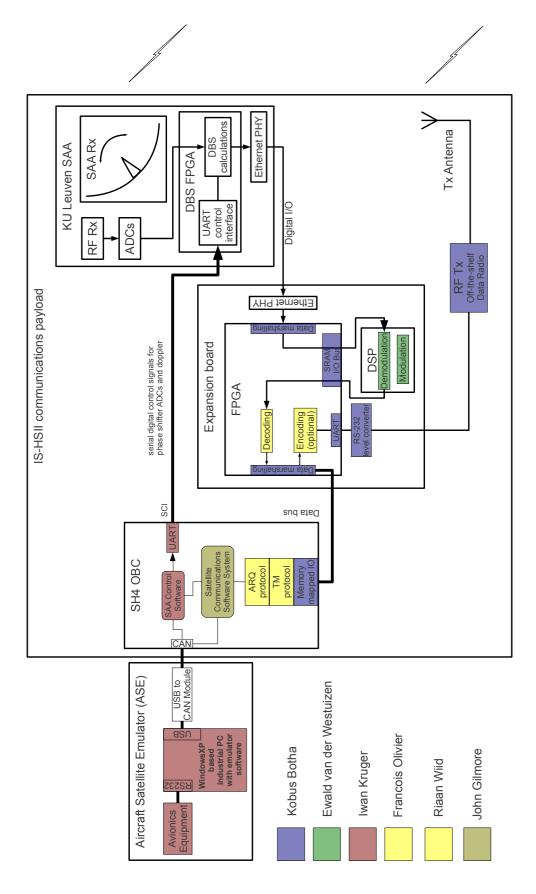

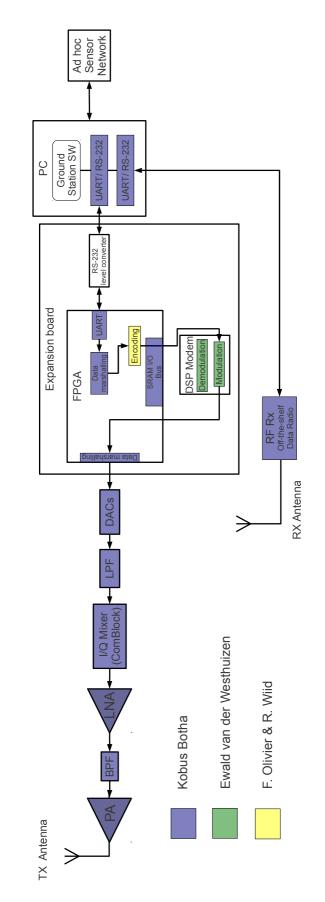

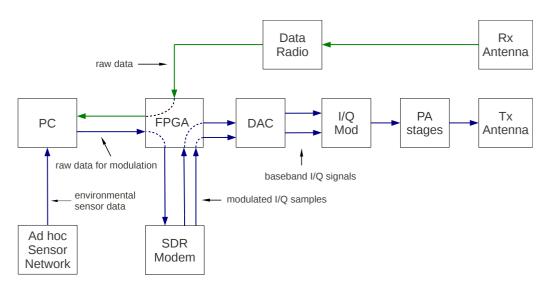

Figure 1.1: Overview of the SAA platform.

- a low-density constellation modulation method such as Quadrature Phase Shift Keying (QPSK) would be used for the SDR modem design,

- the project was to include aircraft borne flight hardware and

- Stellenbosch University would develop and supply a ground station for communicating with the payload.

Due to the size of the project, a team of engineers was required for the project. The work done which formed a part of this thesis is clearly outlined in subsequent chapters. An overview of the airborne platform together with a ground station is presented in Figure 1.1. Reconfigurability was kept in mind during the course of the thesis to allow reuse of developed components.

## 1.4 Structure of This Thesis

In Chapter 2 a methodology for complex system design and implementation is derived. A useful model for explaining concepts throughout the thesis is presented. The methodology is then used to implement a high level design of the payload and ground station systems.

Chapter 3 provides a more in-depth view of the platform overview presented in Figure 1.1. The detailed design of the payload is also presented in this chapter. Software and hardware components are designed from system constraints and low level schematics are presented. Chapter 4 follows the same procedure and provides the same level of detail for the ground station system.

In Chapters 5 and 6 the implementation of the payload and ground station systems are presented. Low level smoke tests are performed to verify simple implementations where necessary and these tests are documented here. Limited integration between components is done.

The integration of the subsystems is then discussed in Chapter 7. The final integration tests are performed and documented in this chapter. A high level ground-to-air simulation test is also described in this chapter.

In Chapter 8 the results of the system tests are summarized. The testing results are critically analyzed and recommendations to noted problems are made based on the analysis. Future work which can be done on the project is also presented.

## Chapter 2

## Methodology and Perspective

In this chapter an overview of the platform required by KUL for the testing of their antenna is presented. The platform's intended use is as a communications payload on an LEO satellite. As stated in the terms of reference, however, stringent requirements for harsh space conditions were not considered extensively. Nonetheless, the system is referred to as a payload throughout this text.

The payload is split into subsystems, where possible, to allow modular design, implementation, and testing; the subsystems are all presented in this chapter and are used to separate the work which formed part of this thesis from work which was done by others.

Firstly a useful model is presented to the reader to assist in the description of the subsystems during subsequent chapters. Thereafter an overview of the payload is presented. The satellite earth station, also referred to as the ground station, is then described.

### 2.1 Methodology

The methodology derived in this section describes the design process, the implementation process and the testing process, all of which are presented in subsequent chapters.

#### 2.1.1 Outline

The design of a new communications system is a complex process. There is usually not a predefined sequence of steps to follow which lead you to a correct or optimal solution. There are, however, certain system constraints (stated in the terms of reference) which form a base from which the design can begin. Furthermore, there exist specific outcome criteria; a set of functional requirements for the payload are known. The outcome criteria are abstract concepts – top level specifications which do not entail implementation details. Since the objective of this thesis is ultimately the construction and testing of an operational system, implementation details need to be considered extensively. Based upon these two givens (known top level specifications and required real world implementation) a work methodology for the entire thesis is formed.

#### 2.1.2 Derivation

When implementing a system, all components should be smoke tested before integration. This is to cater for components that do not perform according to specification. From this, it is evident that the most effective methodology for this thesis is top-level design followed by bottom-up implementation.

Once the lowest level subsystems have been tested successfully, integration begins. After each step of integration a new subsystem is formed. This subsystem must then be tested. This iterative process continues until the entire system has passed an end-to-end test and is performing according to specification. There is a feedback path from the implementation stage whereby the top-level design can be updated if, for example, a component does not perform as expected.

#### 2.1.3 Presentation

The derived methodology is strictly adhered to throughout the thesis. The detailed level design of the entire system down to component level was performed first and is presented in the two design chapters. Each design chapter contains a detailed figure of the design which clearly distinguishes between the parts of the system that were implemented as a part of this thesis and the parts that were implemented by others. The implementation of the bottom level components is described in the two implementation chapters. The integration and end-to-end system testing is described in the final testing chapter.

### 2.2 OSI Model

The International Standards for Organisation developed a model called the Open Systems Interconnect (OSI) model as a tool for subdividing communications systems [27]. The model consists of divisions called layers; the layers are stacked in a consecutive hierarchy. Each layer interfaces with the layers above and below it: it provides services to layers other than itself and it requests "services" from other layers. This is useful in partitioning designs, developing robust independent blocks, and implementing top-down or bottom-up design.

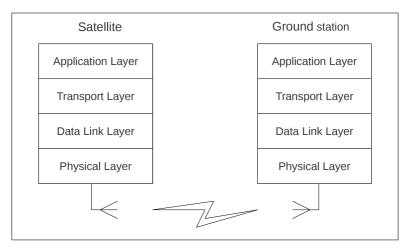

For this project a simplified version of the OSI Model that does not include the session, presentation and network layers is used. This is because full communications functionality and testing of the SAA is provided without them. The simplified model is depicted in figure 2.1. In summary, the layers are:

- **Physical Layer**: At the bottom of the OSI Layer is the physical layer. This layer is described in terms of the raw transmission of bits between nodes in the communication network. Logical concepts such as frames and packets do not exist at the physical layer. Furthermore, not all physical devices and interfaces form part of the physical layer, only those that form the lowest layer of transmission.

- Data Link Layer: The Data Link Layer is the first layer above the physical layer and is the layer which builds frames from data words. The Data Link Layer is the protocol layer which transfers data between nodes. It might provide the ability to detect and correct errors that occurred in the physical layer.

- **Transport Layer**: The Transport Layer provides end-to-end communication services for applications. It also provides services such as reliability, i.e. it ensures that data from the application layer is transmitted reliably.

- Application Layer: High level system and user applications reside in the application layer. The application layer has no concept of physical error correction, low level data words or frames. It uses logical addressing.

## 2.3 Top Level Payload Design

This section uses the two top level payload objectives (of communicating with a system in space and testing the SAA) to provide a setting for the rest of the

Figure 2.1: A simplified OSI model.

thesis. The objectives of the payload place certain constraints on the design. The purpose of the payload is twofold: firstly it must serve as a platform on which KUL's SAA can be tested. Secondly, the payload must enable the transmission of useful data between ground stations i.e. it must function as a communications payload. These two objectives are now described in detail.

#### 2.3.1 Testing of the KUL Antenna

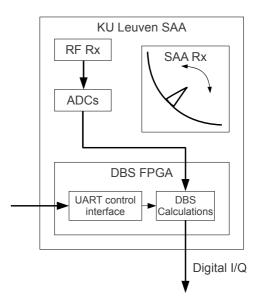

The SAA subsystem is supplied by KUL. It is depicted in Figure 2.2. The SAA itself is intended to be used as a receiver and consists of  $m \times n$  individual receiving elements. Each element is a Right-Hand Circularly Polarised (RHCP) antenna with a wavelength of  $416.\dot{6} \times 10^{-12}$  m. Digital Beam Steering (DBS) techniques are used to alter the radiation pattern of the array to improve the performance of the RF link. The DBS calculations are done on the digitised signal by an FPGA with an Ethernet interface.

The beam steering is controlled by sending x-y coordinates to the steering control logic on the FPGA which performs phase and gain calculations to create a radiation pattern with a peak at the received coordinates. A transmitter must therefore be designed to transmit an RF signal to the SAA. Testing will then involve varying the angle of incidence between this transmitter and the SAA over time and measuring the gain of the SAA while altering its radiation pattern.

Ultimately the SAA will be on board a Low Earth Orbit (LEO) satellite. The orbital path of the satellite results in a varying angle of incidence as the

Figure 2.2: The SAA subsystem.

satellite passes overhead. Whilst simple tests to vary the angle of incidence of the received RF signal can be carried out over long distances between two terrestrial points, a more realistic test would be to fly overhead with the payload mounted on an aircraft. This kind of test would reconstruct signal attenuation near the horizon.

It was recognised that to test the payload on an aircraft would require a satellite emulator to convert avionic data into orbital data. This aircraft emulator was designed and implemented by Iwan Kruger [31].

#### 2.3.2 Communications Link

The SAA implements quadrature mixing to achieve greater spectral efficiency and make the system less prone to channel noise. This means that the received RF signal is demodulated into separate In Phase (I) and Quadrature (Q) components. The I and Q signals are then digitised by a pair of Analogue to Digital Converters (ADCs) in the SAA subsystem. These digitised I and Q signal samples then require further demodulation to extract the raw data bit stream. These samples are presented to external components via an Ethernet interface.

The two interfaces to the SAA subsystem are a bidirectional control interface for sending and receiving beam steering commands and an Ethernet interface which delivers the digitised signal samples. This means a processor is required to send commands over the serial interface and some type of demodulation communications hardware is required to demodulate the signal samples. The major subsystems required to implement the payload communications system are therefore:

- a processor,

- a modulator/demodulator and

- an FPGA.

The FPGA is used for signal routing and data marshaling between components. The modem used is an extension of the modem written by Ewald van der Westhuizen from the multiple channel communications payload [7]. The processor used is the SH4 On Board Computer from the Sumbandila Communications Payload [16].

Error Detection and Correction (EDAC) is used in communications systems to improve bit error rates. A data protocol is used to ensure reliable data transfer. EDAC methods for the payload were investigated by Francois Olivier [36]. These methods are currently being implemented by Riaan Wiid [46].

It was also noted that the scheduling system on Sumbandila's communications payload, written by H. R. Gerber and A. Cooke [12], used a suboptimal scheduling mechanism. If the orbital parameters (two line elements) and the precise location of the ground station are known, it is possible to design an efficient scheduler. This was done by John Gilmore [22].

To implement a useful communications link, three more components are required:

- an uplink transmitter,

- a downlink transmitter and

- a downlink receiver

The downlink transmitter implementation had no direct effect on the testing of the SAA itself. Therefore an off-the-shelf data radio would be used to implement the downlink. The uplink transmitter and downlink receiver systems form part of the ground station, an overview of which will be presented next.

### 2.4 Ground Station Overview

The ground station's primary function is to transmit an RF signal to the payload in such a manner that the operation of the SAA can be tested accurately. A secondary function of the ground station is to transmit some kind of useful data over the communications link to another ground station. A specific list of functional system requirements will now be constructed from these broadly stated requirements.

The SAA acts as an RF receiver system centered at 2.45 GHz. It expects a waveform that is Right Hand Circularly Polarised (RHCP) – clockwise in the direction of propagation. The SAA performs quadrature down mixing and sampling to deliver baseband digital I and Q signals on its output. The functional system requirements for the ground station can now be listed. They are:

- the ground station must transmit an RF signal of the correct amplitude, frequency and polarisation,

- the RF signal must contain a complex I/Q message signal and

- the I/Q message signals must in turn contain modulated information.

These three specifications form the criteria against which all other design decisions will be made. These design decisions are further discussed in Chapter 4.

# Chapter 3 Payload Design

In this chapter the detailed design of all the components on the payload is presented. In the first section an overview of the payload provides background for the subsequent sections. Each major component is presented in its own section and is followed by a detailed design in terms of the OSI model, where deemed useful to the discussion. The SDR modem, for example, exists purely on the physical layer, so its design will not be handled in terms of the OSI layers. Figure 3.1 is a diagram of the payload.

## 3.1 Payload Design Overview

The payload consists of individual interconnected components. To provide a clear picture of the payload's operation and the interconnection of the components, all components will be described briefly. Due to the large nature of the project, the implementation of certain components fell outside the scope of this thesis. These components and subsystems were the responsibility of other team members. This section describes exactly which components formed part of this thesis and which did not.

At the core of the payload is the SAA subsystem designed by KUL which must be tested. The SAA subsystem has the following components:

- the physical antenna array,

- RF receiver hardware for down mixing and demodulation,

- ADCs for sampling the baseband signals and

- an FPGA which performs beam steering calculations and provides interfaces to the greater payload.

The SAA interface uses a Ethernet physical layer chip [34] to transmit I/Q samples to the greater payload. The components on the payload that formed a part of this thesis are:

- $\bullet$  data marshaling firmware which routes the digital I/Q samples from the SAA to the SDR modem via the FPGA,

- firmware to route the demodulated data from the SDR modem to the OBC,

- a device driver on the OBC acting as an interface to the FPGA and

- firmware to route the data from the OBC to the downlink data radio.

The remainder of the work that forms part of this thesis was done on the ground station, discussed in later sections.

### 3.2 The SH4 On-Board Computer

As stated in the terms of reference, the OBC to be used for this project was designed and built by SunSpace. It is space qualified and has withstood the harsh space environment on the Sumbandila Satellite which is in orbit at the time of writing [41]. The OBC is based on a 32-bit RISC processor, the Renesas SH7750R [39] (referred to as the SH4 in this thesis). The OBC features a dual redundant CAN interface, NAND flash non-volatile memory, a bi-directional Low Voltage Differential Signaling (LVDS) I/O port and a memory expansion port.

The actual OBC unit used for this thesis was the same OBC from the Sumbandila Communications Payload engineering model. It was loaded with the QNX operating system making it ready for use immediately. Although the Linux operating system has been ported to the SH4 OBC in [45], it was decided to use QNX for reasons explained below, despite the fact that running Linux on the OBC has certain advantages (such as code portability and development flexibility).

The decision to use QNX as operating system was based on the following two points. Firstly, QNX is a commercial operating system which means that professional support is available from QNX Software Systems. Secondly, other engineers would be involved in the development of the payload, so a reliable operating system was required. If the operating system required development it could cause delays in other research projects.

The SH4 OBC provides two serial ports which can be used. One of the serial ports, /dev/ser1, is permanently mapped to a terminal by the QNX image [17]. The second serial port is mapped to a serial device, /dev/ser2, which can be used as a general purpose Universal Asynchronous Receiver/Transmitter (UART), but which was used by Kruger's Aircraft Satellite Emulator to send beam steering commands to the SAA subsystem [31].

### 3.3 OBC Design in Terms of the OSI Model

A view of the software components and hardware interfaces required on the OBC are now presented. Most of the OBC-related work done for this thesis was on the physical layer of the OSI model, yet the application and data link layer components are briefly described to provide an understanding of the system.

### 3.3.1 Application Layer

System software running on the application layer is required to provide the communications payload with store and forward capability. Store and forward means that useful data can be transmitted between ground stations via the payload. When multiple ground stations are trying to communicate with the payload simultaneously, some type of scheduling system is required. The scheduling system implemented by H.R. Gerber and A. Cooke [12] simply chose a ground station from a master list at random until all ground stations were serviced. It was realised that, if the location of the ground stations and the orbit of the satellite is known, it is possible to design a much more efficient, potentially optimal scheduling system. This area of research did not form part of the work done in this thesis, however, and was done by J. Gilmore [22].

#### 3.3.2 Transport Layer

Data from the application software must be transmitted (and received) over the channel. This is done by using a very simple transport protocol to ensure the reliable delivery of packets at the receiver's transport layer. The protocol used to accomplish this is the Automatic Repeat Request (ARQ) protocol, implemented by J. Gilmore and R. Wiid [21].

#### 3.3.3 Data Link Layer

The ARQ packets from the transport layer must be sent to the physical layer. This is done by splitting the packets up into frames as per the Telecommand and Telemetry (TM) protocol designed by the European Cooperation for Space Standardization [18]. A single TM frame is 84 bytes in length. The TM protocol was implemented by F. Olivier, E. van der Westhuizen and R. Wiid [46].

#### 3.3.4 Physical Layer

TM frames from the data link layer on the OBC need to be physically transported to the FPGA which relays them to the modem for modulation. A suitable electrical interface must be chosen between the OBC and the FPGA. A software interface must be designed allowing other programs on the OBC to use this interface.

#### **Electrical Interface**

The SH4 OBC has the following physical interfaces:

- an LVDS I/O interface,

- two Controller Area Netwrok (CAN) bus interfaces,

- two serial ports and

- a memory expansion port.

Considerations for the design of the interfaces include: sufficient data rates, electrical compatibility between physical components and features such as addressing, interrupts and DMA.

The CAN bus interfaces are intended for connecting the "major components" of the satellite and are reserved for this purpose. Of the two serial ports, one is mapped to a Unix serial console which is useful for connecting to the SH4. The other serial port is reserved for sending control commands to the SAA. The LVDS I/O is useful for high speed point to point data transfers. While it could be used for our interface to the FPGA, it would require additional addressing wrappers because more than one address on the FPGA needs to be accessed. This leaves the expansion port, which, as is described below, meets the requirements.

The expansion port comes in the form of a PC-104+ connector into which a daughter board typically slots. This connector provides a 32-bit data bus which is memory mapped as external memory to the SH4's address space. It also provides an active low power up reset pin,  $\overline{\text{RESET}}$ , that allows the daughter board to reset to a known state at startup. There is also an interrupt pin,  $\overline{\text{IRL3}}$ , that allows the daughter board to generate hardware interrupts. Four chip select pins are also provided to allow multiple components to be connected to the expansion port on the same address and data bus.

All of the pins on the expansion port are connected to LVCMOS-3.3 buffers, the 74ALVC162245 from Fairchild Semiconductor [19]. These buffers then connect to the "outside world". This protects the SH4 from accidental damage.

The maximum data rate of the expansion port is a crucial consideration to ensure that data transfers between the OBC and the FPGA occur timeously. Calculating the theoretical maximum data rate of the expansion port is not trivial. The expansion port has its own clock which determines the speed at which data transfers occur. The maximum internal clock to bus clock ratio equals  $\frac{1}{2}$ . To determine the maximum internal clock speed, it is noted in [17] that the internal clock speed is determined by the external mode pins MD[2..0]. These pins have a fixed value of 011 and cannot be adjusted. From [39], Table 10.3(2), this means that the on-chip Phase Locked Loop (PLL) is activated with a multiplication factor of 12. The SH4 input clock pin is fed by a 16 MHz crystal. The internal clock frequency is therefore fixed at 192 MHz and the maximum bus clock speed is therefore 96 MHz.

The SH4 has a 32-bit virtual address space. The virtual address is divided into five areas according to the upper address value. External memory comprises a 29-bit address space, divided into eight areas. Various memory modules can be connected to the seven areas of external address, and chip select signals  $\overline{\text{CS}}[0-6]$  are used to multiplex all the data buses.  $\overline{\text{CS}}[2-5]$  are available on the expansion port.  $\overline{\text{CS2}}$  was chosen and its corresponding external area is Area 2. All Area 2 address (0x8000000 - 0xC000000) accesses will activate  $\overline{\text{CS2}}$ .

Given a clock frequency,  $f_c$ , the theoretical upper bound on the transfer data rate, r, is determined by  $c_m$ , the number of cycles per memory access and  $c_i$ , the number of cycles for inter-area accesses. This is given by

$$r = \frac{f_c}{c_m + c_i} \times w \,\mathrm{bps} \tag{3.3.1}$$

where w is the word size (32 bits in this case).

The required data rate across the interface is determined by the baud rate specification of 19 200 bps. The required bidirectional data rate across the expansion port is therefore 38 400 bps because the physical interface is half duplex.

Assuming external memory is accessed as synchronous SRAM, the SRAM timing diagram, provided in [39] is consulted. It is evident that a no-wait memory access lasts for two bus clock cycles. The minimum inter-area access wait period is one clock cycle. Substituting these values into equation 3.3.1 yields

$$r = \frac{96 \times 10^6}{3} \times 32 = 1024 \times 10^6 \,\mathrm{bps} \tag{3.3.2}$$

However, since the expansion port is memory mapped directly to the SH4's data and memory buses, accessing it will be much slower than this upper limit because memory accesses are shared with other processes running on the SH4. It is not possible to say exactly what the effective throughput will be – this will have to be measured.

It is, however, possible to say that the upper limit is five orders of magnitude faster than the required data rate so it seems feasible that the expansion port will not become congested.

The total required pin count for implementing an SRAM interface to the OBC on the FPGA is 40: 32 pins for data, three pins for the clock, read and write strobes respectively,  $\overline{\text{RESET}}$ ,  $\overline{\text{IRL3}}$ , a single chip select and two address pins. Whilst only one pin is required for addressing – for reading and writing

to the modem – an extra pin is included in the design to allow for address expansion.

#### **Resource Manager**

Data transfers over the expansion port must be managed by a piece of dedicated software. Software which is dedicated to managing hardware is called a Resource Manager in QNX terminology. The resource manager must provide an interface to client software enabling access to a physical resource, in this case the expansion port. A multi threaded, interrupt driven, full duplex resource manager was developed as part of this thesis and is discussed in Section 3.4.

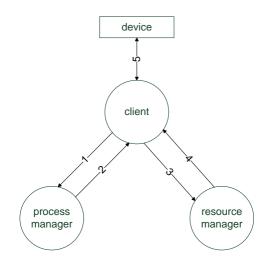

### 3.4 OBC Resource Manager

The QNX kernel is a micro-kernel which means that the resource manager is a user level program. The client connecting to the resource manager is the TM protocol written by Wiid *et al.* [46]. The sequence in which the client software interacts with the resource manager, the operating system and the physical device is designed to hide implementation details of the resource manager from the client. The sequence is presented in Figure 3.2.

Figure 3.2: Client software device access sequence.

When the resource manager is launched, it registers a device in the namespace such as /dev/exp. When a client wants to access the device, the following steps take place:

- the client initially queries the process manager (a module responsible for pathname management) using the *open()* call and asks it to look up the name /dev/exp,

- in step 2 the process manager responds with some values which uniquely identify an open communication channel to the resource manager,

- the client then connects to the resource manager on this channel,

- once the resource manager receives the connection it generally responds with a success (and *open()* returns with a file descriptor) or an error,

- the client then uses this file descriptor to communicate with the device through *read()* and *write()* calls.

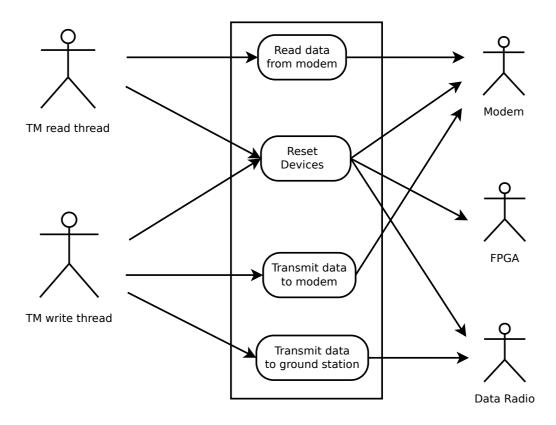

The Unix standard of exposing a device as a file is used in QNX. The standard *open()*, *read()*, *write()* and *devctl()* file operations are implemented. The TM protocol implementation consists of two threads, namely a reader thread and a writer thread, which attempt to transfer TM frames from and to the ground station respectively.

Note that the design must cater for two separate transmit paths at this stage. The first transmit path is for the downlink data radio (an off-the-shelf component used to rapidly implement a working prototype) while the second transmit path is for a dedicated DAC that will eventually form part of the downlink transmitter chain.

The resource manager therefore exposes a serial device, /dev/ser3, to allow data to be transmitted to the downlink data radio. It was decided to implement both devices, /dev/exp and /dev/ser3 with a single resource manager. This is because the data radio connects to a UART on the ML501 FPGA board and all traffic to it must also cross the expansion port. Stated differently, there is only a single physical device – the expansion port – and it is managed by a single resource manager which provides two logical devices.

The required behaviour of the resource manager is presented in Figure 3.3 as a use case diagram.

#### 3.4.1 Software Polling vs Hardware Interrupts

Because the CPU is shared with other processes, such as the ground station scheduler, CPU efficiency is an important design criterion for the resource manager. The possible responses of the resource manager, specifically to a read() system call, are analysed to determine which response method uses the least CPU cycles. The result is extrapolated to the write() system call response.

When a client makes a read call to the resource manager to read from the modem, there is either data available or not. If there is nothing available, the read() function can exit with a return value indicating that zero bytes were

read. In this case, the read thread would need to poll the resource manager until data became available – an unwanted scenario implying wasted CPU cycles. Alternatively, the resource manager blocks the reading thread, and the resource manager returns with data when it is available.

If the reading thread is blocked, the resource manager can poll the FPGA to determine whether data is available. This is another scenario where CPU cycles would be wasted. A third scenario exists wherein the resource manager is designed to be driven by hardware interrupts. When the read blocks, the resource manager can reply at a later stage after an interrupt has indicated that data is available. This interrupt driven design is clearly the most efficient choice and the design thereof is now analysed.

#### 3.4.2 Interrupt Driven Resource Manager Design

The SH4 has 4 external interrupt pins, IRL[3-0], whereby interrupts can be generated. The pins can be configured as a single interrupt source, with the levels determining the interrupt priority. A level of 0000 indicates the highest level interrupt request. Alternatively, each interrupt pin can be configured as an independent interrupt source, with the priority of each interrupt source also configurable. The expansion port, however, provides only a single interrupt pin, IRL3, so it was decided to configure it as an independent interrupt source.

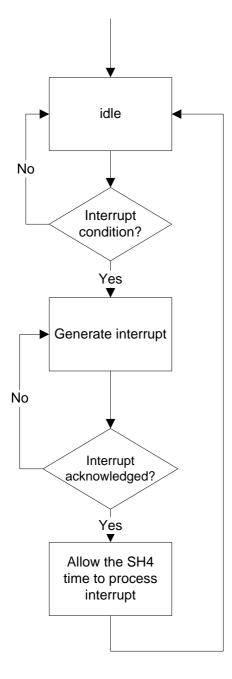

When generating an interrupt on the IRL3 pin, the FPGA must assert the interrupt until the interrupt is acknowledged. This is because the interrupts on the SH4 are level triggered. Once the interrupt has been acknowledged, the process generating the interrupt on the FPGA must allow the SH4 some time to process the interrupt before generating another one. A countdown timer is used for this. The process is depicted in Figure 3.4. A required component in an interrupt driven resource manager is an Interrupt Service Routine (ISR). The ISR runs at the highest possible scheduling priority. The ISR must therefore be lightweight and simple, performing only critical tasks, with the "real" work being scheduled to worker threads. The ISR is responsible for:

- masking (disabling) further interrupts,

- determining the source of the interrupt,

- notifying the FPGA that the interrupt was received,

- updating a data structure shared between the ISR and some of the threads in the resource manager,

- signaling the resource manager that some kind of event has occurred.

Determining the source of the interrupt must be done in software because there is only a single interrupt pin available yet there are multiple interrupt conditions. The simplest way to do this is by reading a status register on the FPGA. The process is described in detail in Section 5.3.5.

The action of reading the status register can be used as an interrupt acknowledge. If the value of the status register is read while the FPGA is generating an interrupt, that signifies that the ISR has received the interrupt. To prevent accidental acknowledgement of the interrupt, it is ensured that the ISR is the only part of the resource manager which ever accesses the status register.

Because the ISR runs with the highest priority available, it should not perform tasks such as block data transfer. A dedicated thread is therefore included in the resource manager design for this purpose. When an interrupt is generated, the ISR acknowledges the interrupt by reading the value of the status register. The value of the status register is then passed to the worker thread. The worker thread can then use this value to determine the source of the interrupt. When the worker thread reads this value, care must be taken to ensure that the value is not updated by another interrupt. The thread therefore disables interrupts when checking this value, and enables them once it is finished handling the interrupt. Data accesses to this shared value should therefore be kept to a minimum.

In the idle state, the worker thread waits for a signal from the ISR that there is "work" to be done. QNX provides two methods for doing this. In the first method the ISRs sole purpose is to signal the thread. In the second method the ISR performs some critical task and then signals the thread. The second method is used in this design.

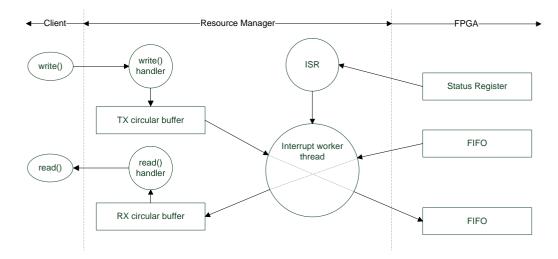

The worker thread is what reads and writes data from the FPGA buffers. It checks the value of the status register (passed to it by the ISR) and decides which buffers to service based on this value. The data it has read from the buffers must then be made available to the software client, in this case the TM protocol threads. If the worker thread tries to pass the data directly to the client, and if the client is not immediately ready to receive the data, this data will be overwritten when the worker thread reads new data. The data is therefore stored in circular buffers until the client is ready to read it. The data flow between the various buffers is depicted in Figure 3.5.

### 3.5 Downlink Transmitter

An off the shelf data radio was used as a downlink transmitter to simplify the implementation of the prototype. A data radio is a device which accepts data bits at the input and outputs a modulated RF signal which is fit for propagation over the channel. A data radio with a data rate of 19 200 bps, transmit power of 1 W, receiver sensitivity of -110 dBm operating in the 900 MHz ISM band was sought. These link budget requirements were drawn up by Iwan Kruger [30]. The ISM band was chosen because off-the-shelf components which

operate in it are readily available. The XTend OEM RF module was identified as a suitable data radio. It is a 1 W, 900 MHz RF module that accepts serial data at its input via a UART at a data rate of up to 115 200 bps. The receiving module then delivers the same data at its output, assuming the two modules are within range.

### 3.6 The Software Defined Radio

The modem deals purely with the manipulation of physical data bits. It does not have any Error Detection and Correction (EDAC) functionality, does not implement any protocols or run any application software. It is therefore situated, in its entirety, in the physical layer of the OSI model.

The function of the software modem is to act as a translator between digital information and radio frequency communication. The detailed design and implementation of the modem was done by Ewald van der Westhuizen [44]. The work done in this thesis involved integrating the modem to the rest of the payload.

A brief overview of the modulation techniques used are presented to provide an understanding of how the modem connects with the greater payload. Thereafter a detailed analysis of the physical interfaces is done.

#### 3.6.1 Modem Overview

The stream of bits at the modem's input is a digital pulse train. Any aspect of this signal can be modulated – amplitude, frequency or phase. The three basic digital modulation schemes which use these aspects are Amplitude Shift Keying (ASK), Frequency Shift Keying (FSK) and Phase Shift Keying. One of these had to be chosen as a modulation scheme. It is evident from [37] that Phase Shift Keying achieves better power efficiency and bandwidth efficiency than the ASK or FSK schemes.

A more complex form of Phase Shift Keying namely Quadrature Phase Shift Keying (QPSK) provides greater bandwidth efficiency than ordinary PSK. Only a brief description of QPSK will be given because this thesis did not entail the implementation of QPSK. In QPSK modulation, a cosine carrier's phase is varied in time. Given two carriers, typically called the I and Q signals, each carrier's phase will change once within a time slot. A change in phase represents a symbol transition. A symbol therefore consists of two bits.

Differential QPSK is a method whereby only relative symbol transitions are used to demodulate the data. This is useful when incoherent demodulation is required. D-QPSK was used as the final modulation scheme for the modem.

A sampling frequency of 230 400 Hz is required for successful demodulation of a received signal in this application [44]. Also specified in the SDR modem design is a sample size of 16 bits. To calculate the data flow rate for the modem at the given sampling frequency, the data rates of the following data paths are summed:

- unmodulated incoming data from the OBC,

- modulated data to be sent to the DACs,

- signal samples from the ADCs that need to be demodulated and

- demodulated data to the OBC.

The rate of the user data from the OBC is the effective data rate specified in the terms of reference, 19 200 bps. The data destined for the OBC flows at the same rate. The total data rate of I and Q samples being sent to the DACs can be calculated as  $230400 \times 16 \times 2 = 7372800$  bps. The data rate for incoming samples from the ADCs is the same. The effective bidirectional data rate is therefore  $38400 + 7372800 \times 2 = 14784000$  bps.

For this thesis, however, only the uplink signal was generated using the SDR modem. The downlink was implemented using an off-the-shelf radio. The effective data rate that was implemented is thus 7 392 000 bps.

#### 3.6.2 General Purpose I/O Pins

The DSP has 34 I/O pins which can be programmed to function as general purpose I/O. These pins can be programmed to behave in an arbitrary manner. For example, code could be written to implement a Universal Asynchronous Receiver/Transmitter (UART) using these pins. However, dedicated hardware usually provides faster data rates and requires less code to be written. Based upon this, it was decided by the author that one of the dedicated and more flexible hardware interfaces would be considered.

#### 3.6.3 Host Interface

The Host Interface is a byte wide interface supporting 8-, 16- or 24-bit word data transfers. It has rich features such as:

- host commands whereby the host (in this case the FPGA) can issue commands to the DSP,

- a choice of either polling, interrupt-driven or Direct Memory Access (DMA) transfer modes and

- a maximum data rate of roughly 81 MB/s.

The Host Interface lacks built-in addressing hardware, which means an addressing scheme must be implemented. A relatively simple scheme would be to add an 8 bit control byte to each 16 bit sample and use the interface in 24 bit mode. Contained in this control byte would be an address which the FPGA can use to determine whether the data is destined for the DAC, the ADC or the OBC.

The Host Interface meets all the requirements and provides useful additional functionality. It was therefore chosen above the other interfaces and the FPGA firmware was designed around the Host Interface. However, during implementation, unexpected behaviour was encountered. Specifically, a double assert of the data strobe by the DSP would occur during the middle of a three byte transfer. This caused entire words to be discarded when being transferred over the interface. The data strobe is normally asserted as an active low signal once to indicate a strobe. The double strobe phenomenon is defined as two such strobes occuring directly after one other, causing the host device to recognise it as two seperate strobes (while only a single strobe was expected).

After extensive investigation this double assertion waveform was measured with a logic analyser and a copy of the measurement was sent to Freescale to get assistance. Direct contact was made with a Freescale engineer who was unable to explain the behaviour. The double data strobe assertion phenomenon was also independently confirmed by Ewald van der Westhuizen on a separate Freescale development board. The Host Interface was thus deemed unusable.

## 3.6.4 Enhanced Synchronous Serial Interface (ESSI)

The DSP has two full-duplex ESSI ports allowing serial communication between devices at a maximum rate of 44 MB/s [20]. The ESSI does not feature any dedicated addressing hardware so, as with the Host Interface, additional complexity must be added to implement addressing. The two ESSI ports were designed for 6 channel digital surround sound applications as each ESSI can function with a single receiver and drive three separate transmitters.

#### 3.6.5 External Memory Expansion Port

The DSP expansion port can be used for either memory expansion or as memory mapped I/O. It consists of a 24-bit address bus, a 24-bit data bus, and control lines that provide features such as chip select and bus arbitration. The expansion port supports the implementation of external Static Random Access Memory (SRAM) or Dynamic Random Access Memory (DRAM). The implementation of DRAM on an FPGA is more complex than that of SRAM. Furthermore, the DRAM timing specifications were not present in the DSP's data sheet. The SRAM timing waveforms were available so it was decided to investigate the implementation of an SRAM interface over the expansion port.

Read and write operations over the SRAM interface are synchronous with the DSP's internal core clock. The DSP's internal clock runs at 275 MHz. A single SRAM access takes one clock cycle. Up to 31 wait states can be inserted by programming the Bus Control Register. An infinite number of wait states can be added by the TA control signal. The expansion port is therefore capable of providing the required data rate.

The total required pin count for implementing an SRAM interface to the DSP on the FPGA is 30: 24 pins for the data bus, a pin for the clock signal, a read strobe and a write strobe. Whilst only 2 pins are required for addressing (this is because only 3 addresses on the FPGA are used, namely DAC write, ADC read and OBC read / write) three pins are used in the design to allow for address expansion.

## 3.6.6 SRAM Code

The DSP is the bus master of the SRAM interface. The modem has two main function calls namely *modulate()* and *demodulate()*. Each of these function calls requires two data buffers. There are therefore four buffers containing data on the DSP. The simplest implementation of data transfer is round robin software polling, although this wastes clock cycles unnecessarily. Interrupt and DMA driven transfers are also possible, although it was not possible to get DMA transfers working during the implementation phase. The DMA controller was configured as per the data sheet, the source address, destination address and block size values loaded and the DMA controller was told to initiate the transfer yet the data was never transferred to the destination address. The cause of this problem remains unknown. For this reason it was decided to use interrupt driven transfers over the SRAM interface where possible.

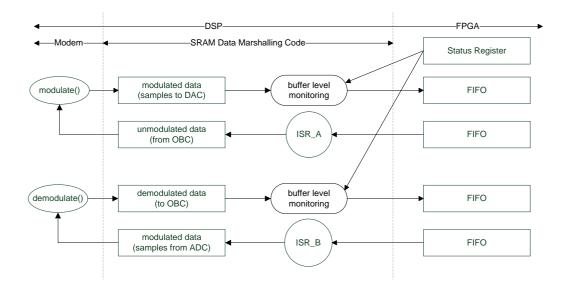

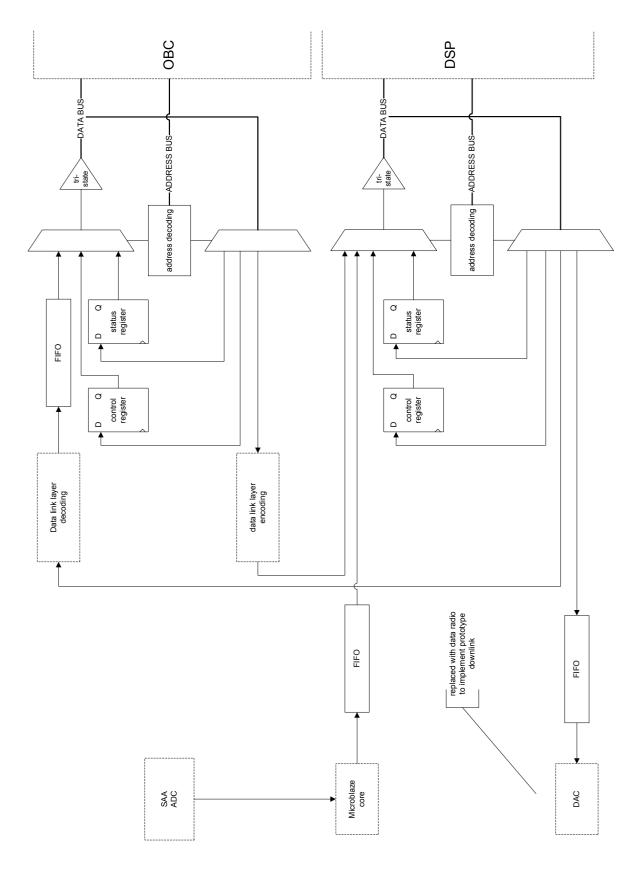

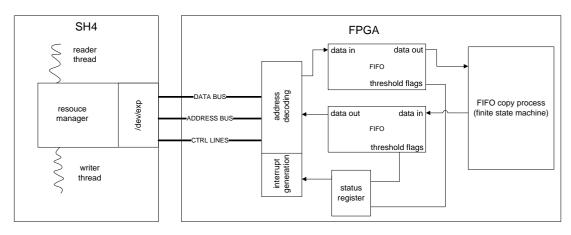

Four dedicated hardware interrupt lines are available on the DSP. The FPGA can generate an interrupt when it has data in its buffers which the DSP must read. The corresponding ISR reads a block of data from the FPGA and places it in a buffer. When the DSP has a block of data that it wants to transmit to the FPGA, however, it must poll a status register on the FPGA to determine whether there is space in its buffers to accept the data. If there is space in the buffer it performs a write, otherwise it retries at a later stage. This polling will only occur once a block of data is available in the appropriate buffers, which means not many clock cycles are wasted on polling in this direction. The data flow of this design is depicted in Figure 3.6.

Figure 3.6: DSP-FPGA dataflow diagram.

# 3.7 The Field Programmable Gate Array

The choice of an FPGA was driven by two main requirements. Because the FPGA's primary function was marshaling the flow of the various data between components, enough I/O pins were a primary requirement. Furthermore, functional blocks such as First In First Out (FIFO) buffers were required to allow reliable data transfer between clock domains. Thirdly, PCB layout was to be avoided where possible during the prototyping phase due to the complexity of the system.

Two FPGA boards were immediately identified as being available. The first was a prototype version of the Signal Interface Card (SIC) from the experimental payload research on Sumbandila Satellite. The second was a Xilinx Virtex-5 ML501 development board [49]. The SIC has a PC104+ connector which slots into the SH4 OBC making it ideal for this project and was chosen above the Xilinx board for this reason. However, during implementation, it was discovered that the FPGA on the SIC, an Actel ProAsicPlus, did not have functional FIFO blocks. This was thoroughly investigated. Actel's documentation indicated problems with the FIFO blocks and stated that they had been obsoleted and should be "used with caution" [5]. The fact that Actel's Asynchronous FIFO cores would discard words occasionally was also confirmed in a private communication with Heiko Berner from SunSpace. This meant that the Xilinx ML501 board was used in the implementation of the payload prototype.

# 3.8 FPGA Design in Terms of the OSI Model

The FPGA deals primarily with the physical transport of data between the major subsystems in the payload. Also implemented on the FPGA are EDAC modules implemented by Wiid. The FPGA therefore spans the Physical and Data Link layers.

# 3.8.1 Physical Layer

It is noted that the ML501 FPGA board has two selectable I/O standards: LVCMOS-2.5 and LVCMOS-3.3. The LVCMOS-3.3 standard is what both the OBC and the DSP use. This means that FPGA I/O pins can be connected directly to both the OBC expansion port and the DSP expansion port. The ML501 has the following available interfaces:

- an ethernet interface,

- an expansion header,

- an RS-232 serial port,

- a Universal Serial Bus (USB) host port and

- a USB peripheral port.