# Satellite Data Transmission by means of a Multi-Channel System

David Smith

Department of Electrical and Electronic Engineering

University of Stellenbosch

Thesis presented in partial fulfilment of the requirements for the degree of Master of Engineering at the University of Stellenbosch

Supervisor: Prof. J.B. de Swardt December 2006

# Declaration

I, the undersigned, hereby declare that the work contained in this thesis is my own original work and that I have not previously in its entirety or in part submitted it at any university for a degree.

| Signature | Date                          |  |

|-----------|-------------------------------|--|

|           |                               |  |

|           |                               |  |

|           | Pectara colorant cultus recti |  |

# Abstract

The aim of this thesis is to find an affordable and upgradeable manner of increasing the data rate of current satellite systems. The compression, modulation and amplification techniques and telecommunication regulations restrict the data rate, which are bypassed by designing a parallel channel configuration.

In order to test this solution a system is developed that is based on the existing standards of DVB-S and MPEG-2. The combination of these standards protect the data from interference, package the data for ease of storage, modulate the data to more effectively radiate the signal and shape the spectrum to adhere to telecommunication regulations.

The spacing between the channels is reduced and the transmitted signal is amplified to inject interference into the system. The effect of this interference on the receiver is shown by transmitting image data and comparing the received image with the original.

Pectora roborant cultus recti

# Opsomming

Hierdie tesis poog om 'n bekostigbare en opgradeerbare metode te vind om die datatransmissietempo van 'n bestaande satellietstelsel te verbeter. Die kompressie-, modulasie- en versterkingstegnieke en telekommunikasie regulasies beperk die datatempo, wat omseil word deur 'n parallelle kanaal konfigurasie te ontwerp.

Om hierdie oplossing te toets, is 'n stelsel gebou wat gebaseer is op die bestaande standaarde van DVB-S en MPEG-2. Die kombinasie van hierdie standaarde beskerm die data teen steuring, verpak die data vir maklike berging, moduleer die data meer vir verbeterde uitstraling van die sein en vorm die spektrum volgens die vereistes van telekommunikasie regulasies.

Die spasiëring tussen kanale is verminder en die uitgaande sein is versterk om steuring binne die stelsel te veroorsaak. Die effek van steuring op die ontvanger word getoon deur beelddata te versend, en die ontvangde beeld te vergelyk met die oorspronklike.

Pectora roborant cultus recti

# Acknowledgements

I would like to thank the following people and institutes for their support:

- My Mom, for being a mother

- The Ashcroft Trust, for all their monetary support throughout my tertiary education

- ETSE, for the use of their equipment to test and complete the system

- Graham Hardie, for being my proof reader and photographer

- Jacques Malan, for the use of his board

- Jacques Roux, for all the late nights helping me test the system

- Johan Arendse, for soldering the components together

- Johan de Swardt, for being a supportive supervisor

- Mark Thomas, for being my proof reader

- Marlize Schoeman, for the use of her  $IAT_EX$  thesis layout

- SunSpace, for their monetary support and equipment to test the system

- Tinus Stander, for the Opsomming of my Abstract

- The University of Stellenbosch, for being my Alma Mater

# Contents

| Li       | st of | Tables                  | xii |

|----------|-------|-------------------------|-----|

| Li       | st of | Figures                 | civ |

| A        | bbrev | viations                | xx  |

| 1        | Intr  | roduction               | 1   |

|          | 1.1   | Problem Statement       | 2   |

|          | 1.2   | Proposed Solution       | 3   |

|          | 1.3   | Implementation          | 4   |

|          |       | 1.3.1 System            | 5   |

|          |       | 1.3.2 MPEG-2            | 6   |

|          |       | 1.3.3 DVB-S             | 6   |

|          |       | 1.3.4 LVDS              | 6   |

|          | 1.4   | Thesis Outline          | 7   |

| <b>2</b> | MP    | EG-2                    | 8   |

|          | 2.1   | Overview                | 8   |

|          | 2.2   | Elementary Stream       | 8   |

|          |       | 2.2.1 Video Compression | 9   |

|          |       | 2.2.2 Audio Compression | 9   |

|          |       | 2.2.3 Implementation    | 9   |

|   | 2.3  | Packetised Elementary Stream                                        | 10 |

|---|------|---------------------------------------------------------------------|----|

|   |      | 2.3.1 Implementation                                                | 10 |

|   | 2.4  | Program Association Table                                           | 10 |

|   |      | 2.4.1 PAT-Section Header                                            | 10 |

|   |      | 2.4.2 PAT-Section Payload                                           | 11 |

|   | 2.5  | Program Map Table                                                   | 11 |

|   |      | 2.5.1 PMT-Section Header                                            | 12 |

|   |      | 2.5.2 PMT-Section Payload                                           | 12 |

|   | 2.6  | Conditional Access Table                                            | 13 |

|   | 2.7  | Network Information Table                                           | 13 |

|   | 2.8  | Transport Stream                                                    | 14 |

|   |      | 2.8.1 TS-Packet Header                                              | 14 |

|   |      | 2.8.2    TS-Packet Adaptation Field      2.8.3    TS-Packet Payload | 15 |

|   |      | 2.8.3 TS-Packet Payload                                             | 15 |

|   | 2.9  | Implementation                                                      | 16 |

|   | 2.10 | Summary                                                             | 16 |

| 3 | DVI  | B-S                                                                 | 17 |

|   | 3.1  | Transport Multiplex Adaptation                                      | 17 |

|   | 3.2  | Energy Dispersal                                                    | 17 |

|   |      | 3.2.1 Spectra of PSK Digital Signals                                | 18 |

|   |      | 3.2.2 Implementation                                                | 18 |

|   | 3.3  | Reed-Solomon Coding                                                 | 19 |

|   |      | 3.3.1 Galois Fields                                                 | 20 |

|   |      | 3.3.2 Reed-Solomon Encoding                                         | 22 |

|   |     | 3.3.3   | Reed-Solomon Decoding      | 23 |

|---|-----|---------|----------------------------|----|

|   |     | 3.3.4   | Implementation             | 25 |

|   | 3.4 | Interle | aving                      | 25 |

|   |     | 3.4.1   | Convolutional Interleaving | 25 |

|   |     | 3.4.2   | Implementation             | 26 |

|   | 3.5 | Convol  | lutional Coding            | 27 |

|   |     | 3.5.1   | Convolutional Encoding     | 27 |

|   |     | 3.5.2   | Convolutional Decoding     | 28 |

|   |     | 3.5.3   | Implementation             | 30 |

|   | 3.6 | Punctu  | uring                      | 31 |

|   |     | 3.6.1   | Implementation             | 31 |

|   | 3.7 | Baseba  | and Shaping for Modulation | 31 |

|   |     | 3.7.1   | Implementation             | 31 |

|   | 3.8 | Phase   | Shift Keying Modulation    | 32 |

|   |     | 3.8.1   | Implementation             | 32 |

|   | 3.9 | Summa   | ary                        | 32 |

| 4 | LVI | DS      |                            | 33 |

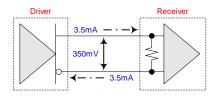

|   | 4.1 | LVDS    |                            | 33 |

|   |     | 4.1.1   | Configuration              | 33 |

|   |     | 4.1.2   | Functional Table           | 34 |

|   |     | 4.1.3   | Electrical Characteristics | 34 |

|   |     | 4.1.4   | Implementation             | 35 |

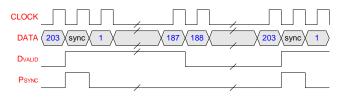

|   | 4.2 | DVB-S   | SPI                        | 35 |

|   |     | 4.2.1   | Signal Format              | 35 |

|          |     | 4.2.2   | Mechanical Details             | 36 |

|----------|-----|---------|--------------------------------|----|

|          |     | 4.2.3   | Implementation                 | 36 |

|          | 4.3 | Summ    | ary                            | 36 |

| <b>5</b> | Auc | lio and | l Video                        | 37 |

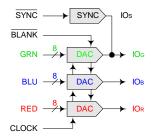

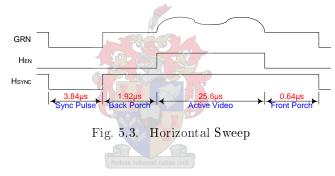

|          | 5.1 | Video   |                                | 37 |

|          |     | 5.1.1   | VGA Screen                     | 37 |

|          | 5.2 | Audio   |                                | 39 |

|          |     | 5.2.1   | Control Interface              | 39 |

|          |     | 5.2.2   | Digital Audio Interface        | 40 |

|          | 5.3 | Summ    | ary                            | 40 |

|          |     |         |                                |    |

| 6        | Mer | nory    |                                | 41 |

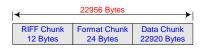

|          | 6.1 | Memo    | ry Initialisation File Format  | 41 |

|          |     | 6.1.1   | Bitmap File Format             | 41 |

|          |     | 6.1.2   | Wave File Format               | 42 |

|          |     | 6.1.3   | Hexadecimal Object File Format | 42 |

|          | 6.2 | Intern  | al Memory                      | 43 |

|          |     | 6.2.1   | ROM Mode                       | 43 |

|          |     |         |                                |    |

|          |     | 6.2.2   | FIFO Buffer Mode               | 43 |

|          | 6.3 | Extern  | nal Memory                     | 44 |

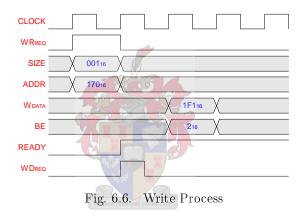

|          |     | 6.3.1   | Write Process                  | 44 |

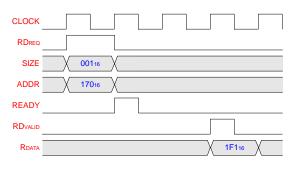

|          |     | 6.3.2   | Read Process                   | 44 |

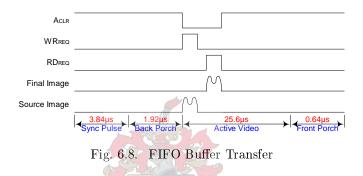

|          |     | 6.3.3   | Synchronisation                | 45 |

|          | 6.4 | Summ    | ary                            | 46 |

| 7        | FPO | GA Im   | plementation                   | 47 |

|   |      |                                                    | . – |

|---|------|----------------------------------------------------|-----|

|   | 7.1  | Controllers                                        | 47  |

|   |      | 7.1.1 System Timing Control                        | 47  |

|   |      | 7.1.2 External Memory Timing Control               | 47  |

|   |      | 7.1.3 User Input Control                           | 48  |

|   |      | 7.1.4 User Output Control                          | 48  |

|   | 7.2  | MPEG-2/DVB-S Synchronisation                       | 49  |

|   |      | 7.2.1 MPEG-2 Initialisation                        | 49  |

|   |      | 7.2.2 MPEG-2 Activation                            | 49  |

|   |      | 7.2.3 DVB-S Initialisation                         | 50  |

|   |      | 7.2.4 DVB-S Activation                             | 50  |

|   | 7.3  | Summary                                            | 50  |

| 8 | Set- | Up                                                 | 51  |

|   | 8.1  | Frequency Selection                                | 51  |

|   | 8.2  | Power Requirements                                 | 52  |

|   | 8.3  | Connections                                        | 52  |

|   | 8.4  | Software                                           | 54  |

|   |      | 8.4.1 Quartus Software Set-Up                      | 54  |

|   |      | 8.4.2 Si2110-EVB Software Set-Up                   | 55  |

|   | 8.5  | Summary                                            | 55  |

| 9 | Mea  | surements                                          | 56  |

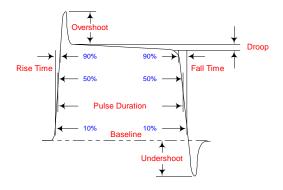

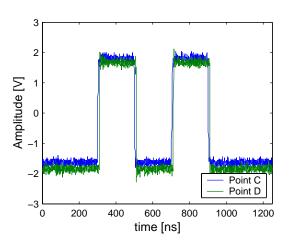

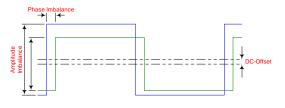

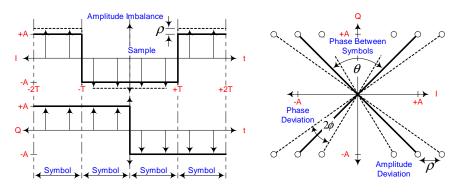

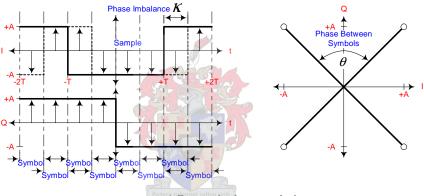

|   | 9.1  | Time Domain Measurements                           | 56  |

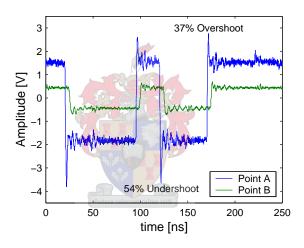

|   |      | 9.1.1 Signal Distortion                            | 57  |

|   |      | 9.1.2 Signal Imbalance                             | 61  |

|   |      | 9.1.3 Distortion and Imbalance Correction Measures | 63  |

|   |      |                                                    | 50  |

|              | 9.2  | Frequency Domain Measurements    | 64 |

|--------------|------|----------------------------------|----|

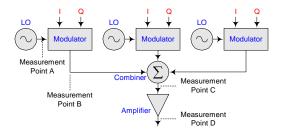

|              |      | 9.2.1 Local Oscillators          | 64 |

|              |      | 9.2.2 Signal Flow                | 65 |

|              | 9.3  | Summary                          | 72 |

| 10           | Con  | clusion and Recommendations      | 73 |

|              | 10.1 | Summary                          | 73 |

|              | 10.2 | Results                          | 73 |

|              | 10.3 | Recommendations                  | 74 |

|              | 10.4 | Conclusion                       | 74 |

| р:           | L 12 |                                  | 75 |

| BI           | bnog | raphy                            | 75 |

| Α            |      | GA Pin Assignments               | 80 |

|              |      | User Interface                   | 80 |

|              |      | VGA Interface                    | 81 |

|              | A.3  | LVDS Interface                   | 82 |

|              | A.4  | External RAM Interface           | 82 |

| в            | Add  | itional Boards                   | 84 |

|              | B.1  | Modifications                    | 84 |

|              |      | B.1.1 Power Supply Modifications | 84 |

|              |      | B.1.2 Data Signal Modifications  | 85 |

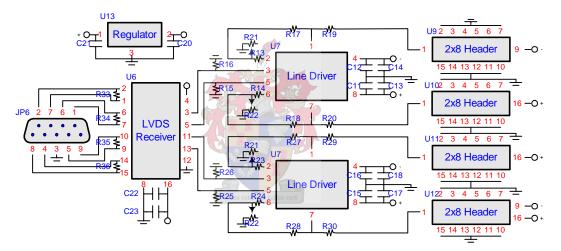

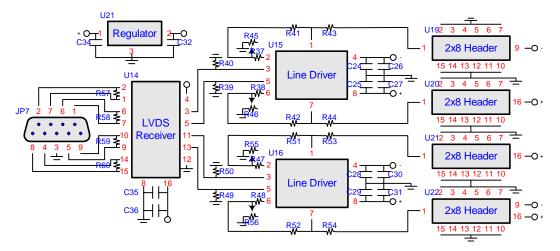

|              | B.2  | Schematics                       | 85 |

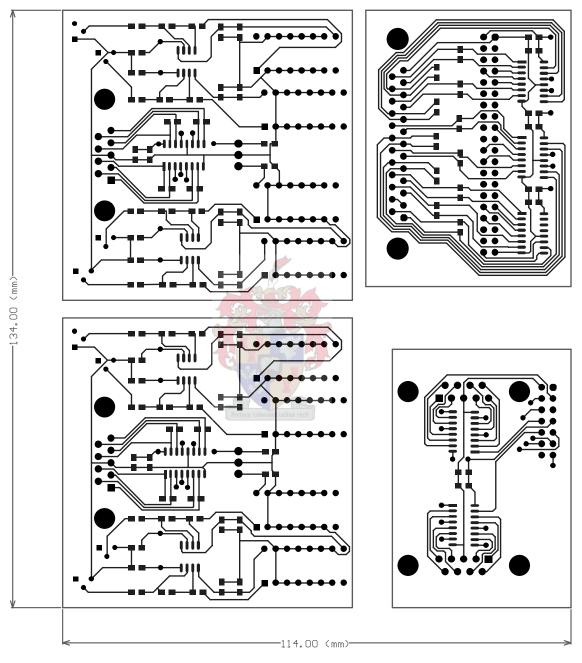

|              | B.3  | Bill of Materials                | 87 |

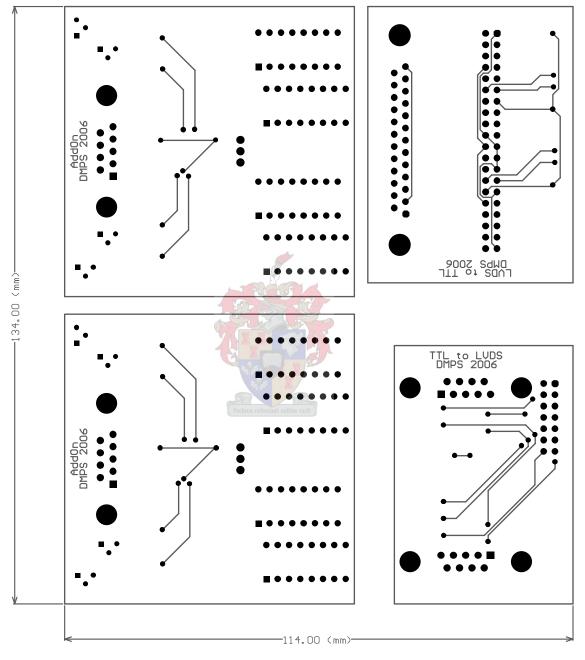

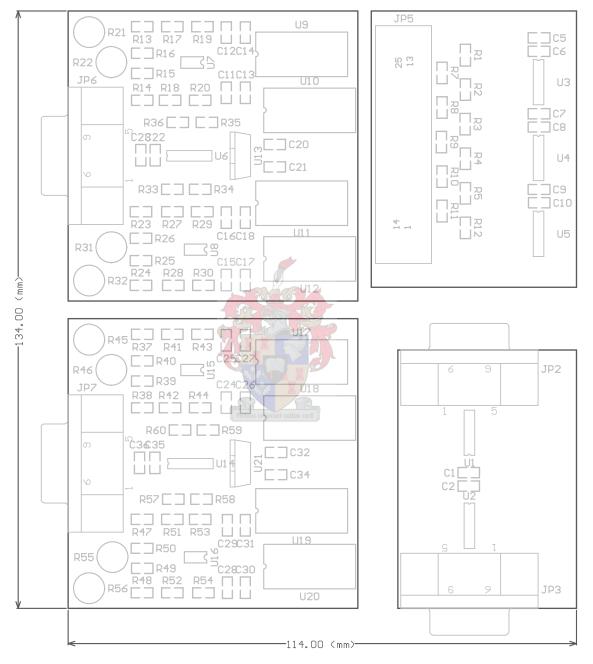

|              | B.4  | Board Layouts                    | 88 |

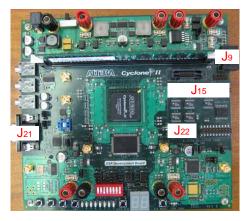

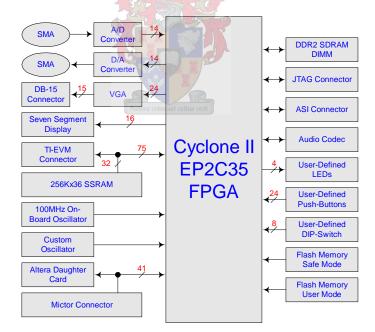

| $\mathbf{C}$ | FPG  | GA Development Kit               | 92 |

|   | C.1 FPGA Development Kit Contents          | 92 |

|---|--------------------------------------------|----|

|   | C.2 FPGA DevBoard Modifications            | 93 |

|   | C.3 FPGA DevBoard Components               | 93 |

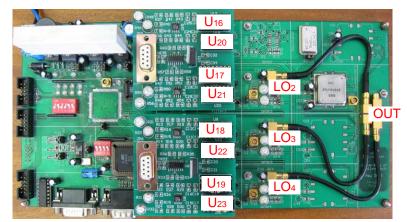

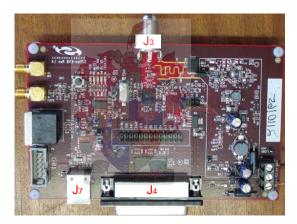

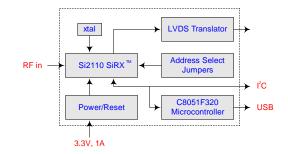

| D | DVB-S Receiver Evaluation Kit              | 95 |

|   | D.1 DVB-S Receiver Evaluation Kit Contents | 95 |

|   | D.2 DVB-S Receiver EvBoard Components      | 95 |

# List of Tables

| 2.1 | Program Number Assignments          | 11 |

|-----|-------------------------------------|----|

| 2.2 | PMT PID Assignments                 | 11 |

| 2.3 | ES Type Assignments                 | 12 |

| 2.4 | ES PID Assignments                  | 12 |

| 2.5 | PID Assignments                     | 14 |

| 2.6 | AF Control Assignments              | 14 |

| 3.1 | Punctured Code Definition           | 31 |

| 4.1 | LVDS Driver Functional Table        | 34 |

| 4.2 | LVDS Receiver Functional Table      | 34 |

| 4.3 | LVDS Driver Output Characteristics  | 34 |

| 4.4 | LVDS Receiver Input Characteristics | 34 |

| 4.5 | DVB-SPI Pin Assignments             | 36 |

| 5.1 | Audio Codec Register Assignment     | 39 |

| 7.1 | FPGA Push-Button Command Table      | 48 |

| 7.2 | FPGA DIP-Switch Command Table       | 48 |

| 7.3 | MPEG-2 Decoder Error Indication     | 48 |

| A.1 | Timing Control Pin Assignments      | 80 |

| A.2  | Push-Buttons Pin Assignments             | 80 |

|------|------------------------------------------|----|

| A.3  | DIP-Switch Pin Assignments               | 80 |

| A.4  | LED Pin Assignments                      | 81 |

| A.5  | LCD Pin Assignments                      | 81 |

| A.6  | VGA Control Pin Assignments              | 81 |

| A.7  | VGA Colour Pin Assignments               | 81 |

| A.8  | LVDS Device Control Pin Assignments      | 82 |

| A.9  | LVDS Driver Pin Assignments              | 82 |

| A.10 | LVDS Receiver Pin Assignments            | 82 |

| A.11 | External RAM Clock Pin Assignments       | 82 |

| A.12 | External RAM Address Pin Assignments     | 83 |

| A.13 | External RAM Control Pin Assignments     | 83 |

| A.14 | External RAM Data Mask Pin Assignments   | 83 |

| A.15 | External RAM Data Strobe Pin Assignments | 83 |

| A.16 | External RAM Data Bus Pin Assignments    | 83 |

| B.1  | Devices                                  | 87 |

| B.2  | Connectors                               | 87 |

| B.3  | Capacitors                               | 87 |

| B.4  |                                          | 87 |

# List of Figures

| 1.1  | Satellite System Functions                     | 1  |

|------|------------------------------------------------|----|

| 1.2  | Simplified Satellite System                    | 2  |

| 1.3  | Proposed Solution                              | 3  |

| 1.4  | Frequency Band Limitation Bypass               | 3  |

| 1.5  | Implemented System                             | 4  |

| 1.6  | System Block Diagram                           | 4  |

| 1.7  | System Implementation     MPEG-2 Block Diagram | 5  |

| 1.8  | MPEG-2 Block Diagram                           | 6  |

| 1.9  | DVB-S Block Diagram                            | 6  |

| 1.10 | LVDS Block Diagram                             | 6  |

| 2.1  | TS Format                                      | 8  |

| 2.2  | Video Redundancy                               | 9  |

| 2.3  | Audio Masking                                  | 9  |

| 2.4  | PES-Packet                                     | 10 |

| 2.5  | PAT-Section                                    | 10 |

| 2.6  | PAT-Section Header                             | 10 |

| 2.7  | PAT-Section Payload                            | 11 |

| 2.8  | PMT-Section                                    | 11 |

| 2.9  | PMT-Section Header                  | 12 |

|------|-------------------------------------|----|

| 2.10 | PMT-Section Payload                 | 12 |

| 2.11 | Video Stream Descriptor             | 13 |

| 2.12 | Audio Stream Descriptor             | 13 |

| 2.13 | TS-Packet                           | 14 |

| 2.14 | TS-Packet Header                    | 14 |

| 2.15 | Continuity Counter                  | 15 |

| 2.16 | Adaptation Field                    | 15 |

| 2.17 | Conversion of PES and PSI to TS     | 15 |

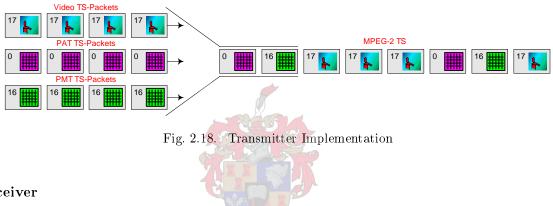

| 2.18 | Transmitter Implementation          | 16 |

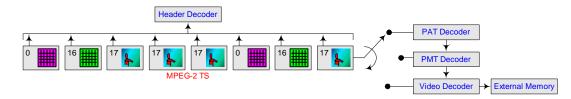

| 2.19 | Receiver Implementation             | 16 |

| 3.1  | TS-Packet                           | 17 |

| 3.2  | Energy Scrambler Diagram            | 18 |

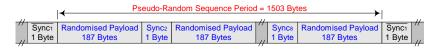

| 3.3  | Randomised Transport Packets        | 19 |

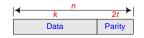

| 3.4  | Reed-Solomon Codeword               | 19 |

| 3.5  | Retrievable Codeword                | 20 |

| 3.6  | Irretrievable Codeword              | 20 |

| 3.7  | Reed Solomon Error Protected Packet | 25 |

| 3.8  | B-by- $N$ Convolutional Interleaver | 25 |

| 3.9  | Interleaved Frames                  | 26 |

| 3.10 | Encoder Implementation              | 26 |

| 3.11 | Convolutional Encoder               | 27 |

| 3.12 | State Diagram                       | 27 |

| 3.13 | Trellis Diagram of Possible States  | 27 |

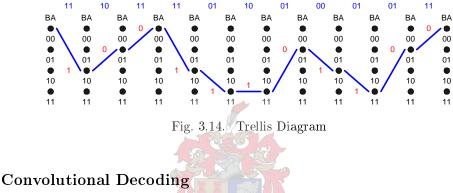

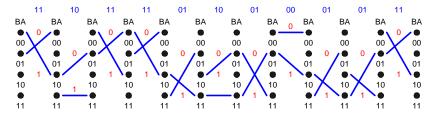

| 3.14 | Trellis Diagram                        | 28 |

|------|----------------------------------------|----|

| 3.15 | Trellis Diagram of Possible Paths      | 28 |

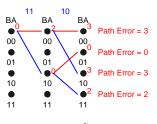

| 3.16 | Step One                               | 29 |

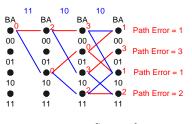

| 3.17 | Step Two                               | 29 |

| 3.18 | Step Three                             | 30 |

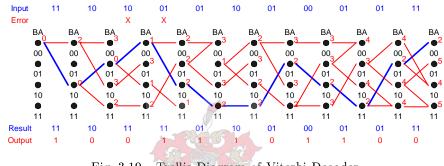

| 3.19 | Trellis Diagram of Viterbi Decoder     | 30 |

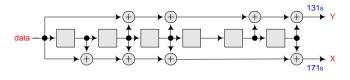

| 3.20 | Convolutional Encoder                  | 30 |

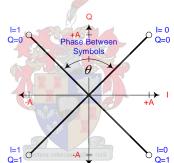

| 3.21 | QPSK Constellation                     | 32 |

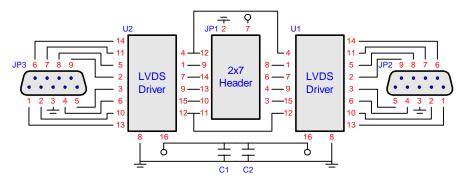

| 4.1  | LVDS Driver and Receiver Configuration | 33 |

| 4.2  | Synchronous Parallel Interface         | 35 |

| 4.3  | Signal Format                          | 35 |

| 5.1  | Video DAC Block Diagram                | 37 |

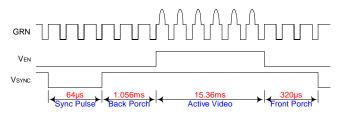

| 5.2  | CRT control                            | 38 |

| 5.3  | Horizontal Sweep                       | 38 |

| 5.4  | Vertical Sweep                         | 38 |

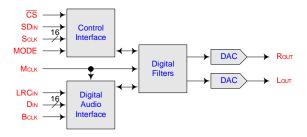

| 5.5  | Stereo Audio Codec Block Diagram       | 39 |

| 5.6  | SPI Timing                             | 39 |

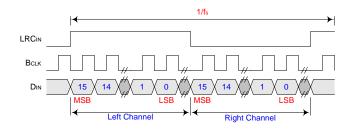

| 5.7  | Left-Justified Mode Timing             | 40 |

| 6.1  | Bitmap File Format                     | 41 |

| 6.2  | Wave File Format                       | 42 |

| 6.3  | Hexadecimal Object File Format         | 42 |

| 6.4  | Internal Memory ROM Control            | 43 |

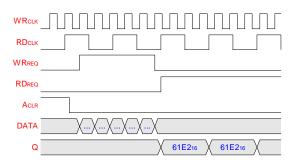

| 6.5  | Internal Memory FIFO Buffer Control    | 43 |

| 6.6  | Write Process                                                   | 44 |

|------|-----------------------------------------------------------------|----|

| 6.7  | Read Process                                                    | 44 |

| 6.8  | FIFO Buffer Transfer                                            | 45 |

| 6.9  | MPEG-2 Decoder Output Transfer                                  | 45 |

| 6.10 | Read and Write Contention                                       | 46 |

| 6.11 | Read and Write Contention with Read Commands having Precedence  | 46 |

| 6.12 | Read and Write Contention with Write Commands having Precedence | 46 |

| 7.1  | System Timing Controls                                          | 47 |

| 7.2  | External Memory Timing Control                                  | 47 |

| 7.3  | MPEG-2 Initialisation Synchronisation                           | 49 |

| 7.4  | MPEG-2 Activation Synchronisation                               | 49 |

| 7.5  | DVB-S Initialisation Synchronisation                            | 50 |

| 7.6  | DVB-S Activation Synchronisation                                | 50 |

| 8.1  | System Set-Up                                                   | 51 |

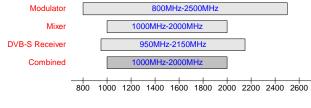

| 8.2  | Component Frequency Ranges                                      | 51 |

| 8.3  | System Connections                                              | 52 |

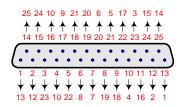

| 8.4  | FPGA DevBoard Connections                                       | 52 |

| 8.5  | Malan's Board Connections                                       | 53 |

| 8.6  | DVB-S EvBoard Connections                                       | 53 |

| 8.7  | FPGA DevBoard to Malan's Board Connections                      | 53 |

| 8.8  | Amplifier and Attenuator Connections                            | 54 |

| 8.9  | DVB-S EvBoard to FPGA DevBoard Connections                      | 54 |

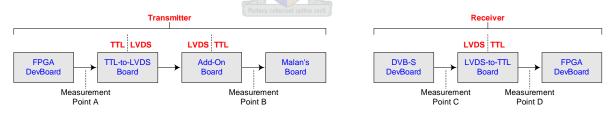

| 9.1  | Time Domain Measurement Points                                  | 56 |

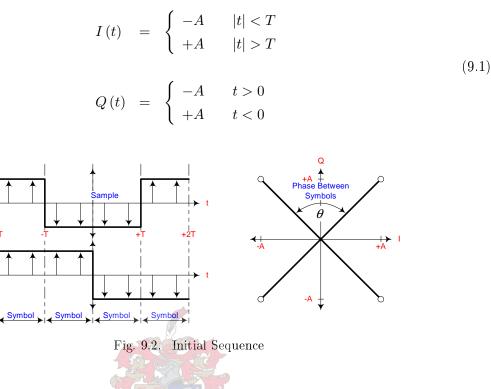

| 9.2  | Initial Sequence                                                                  | 57 |

|------|-----------------------------------------------------------------------------------|----|

| 9.3  | Signal Distortion                                                                 | 57 |

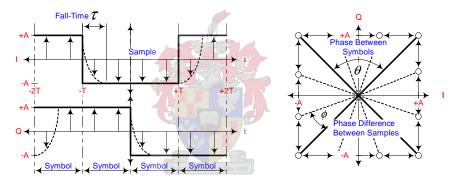

| 9.4  | Affects of Rime-Time and Fall-Time Distortion                                     | 58 |

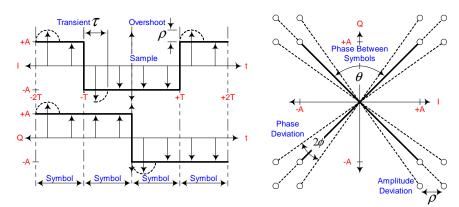

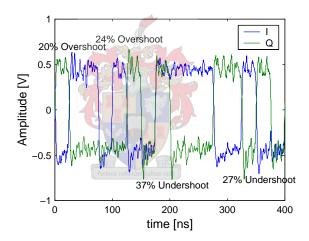

| 9.5  | Affects of Overshoot and Undershoot Distortion                                    | 59 |

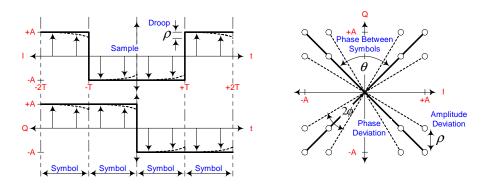

| 9.6  | Affects of Droop Distortion                                                       | 60 |

| 9.7  | Comparison between Transmitter Distortion Measurements                            | 60 |

| 9.8  | Comparison between Receiver Distortion Measurements                               | 60 |

| 9.9  | Signal Imbalance                                                                  | 61 |

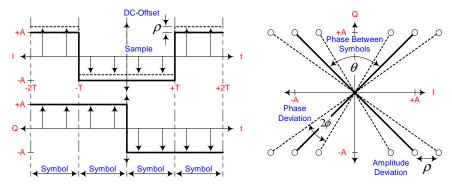

| 9.10 | Affects of Amplitude Imbalance                                                    | 61 |

|      | Affects of Phase Imbalance                                                        | 62 |

| 9.12 | Affects of DC-Offset                                                              | 63 |

| 9.13 | Comparison between Transmitter Imbalance Measurements                             | 63 |

| 9.14 | Frequency Domain Measurement Points                                               | 64 |

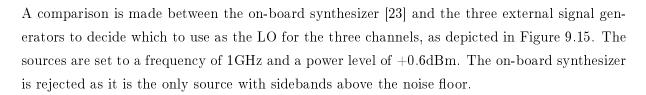

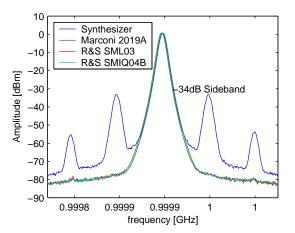

| 9.15 | Comparison of Signal Generators                                                   | 64 |

| 9.16 | Blind Scan Panel Screenshot for Unamplified 80MHz Channel Spacing                 | 65 |

| 9.17 | Easy Start Panel Screenshot for Unamplified 80MHz Channel Spacing $\ldots \ldots$ | 65 |

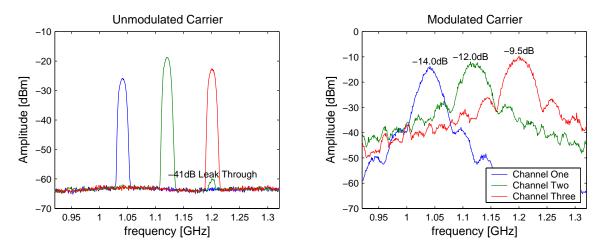

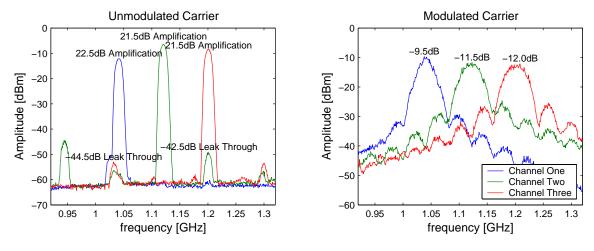

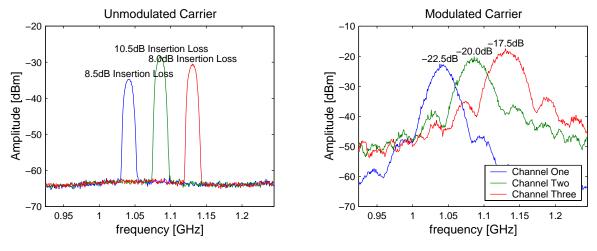

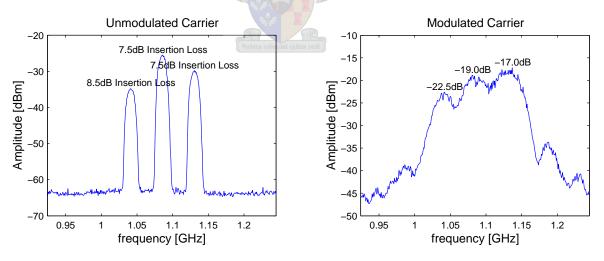

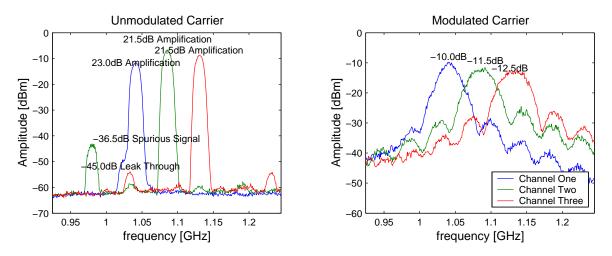

| 9.18 | Modulator Outputs for 80MHz Channel Spacing                                       | 66 |

| 9.19 | Combiner Outputs for 80MHz Channel Spacing                                        | 66 |

| 9.20 | Combiner Output for 80MHz Channel Spacing                                         | 67 |

| 9.21 | Easy Start Panel Screenshot for Amplified 80MHz Channel Spacing                   | 67 |

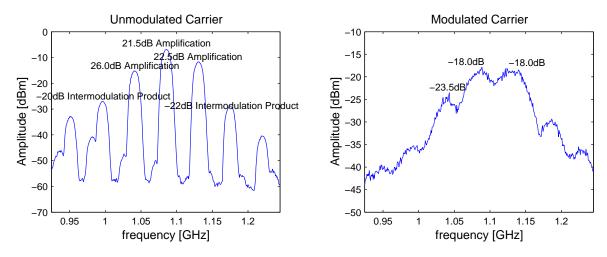

| 9.22 | Amplifier Outputs for 80MHz Channel Spacing                                       | 68 |

| 9.23 | Combined Amplifier Output for 80MHz Channel Spacing                               | 68 |

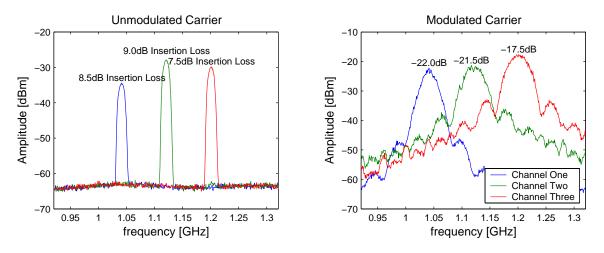

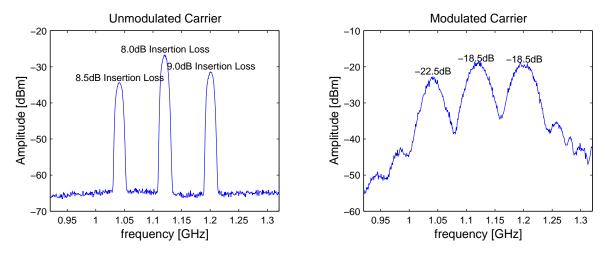

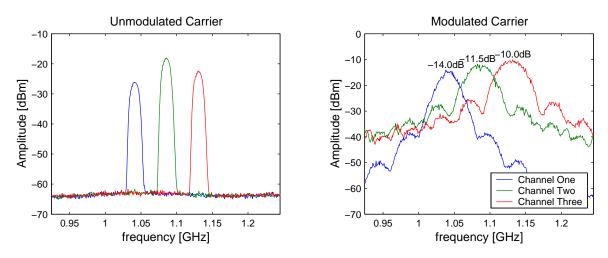

| 9.24 | Easy Start Panel Screenshot for Unamplified 45MHz Channel Spacing                 | 69 |

| 9.25 | Modulator Outputs for 45MHz Channel Spacing                                       | 69 |

| 9.26 | Combiner Outputs for 45MHz Channel Spacing                                        | 70 |

| 9.27 | Combiner Output for 45MHz Channel Spacing                       | 70 |

|------|-----------------------------------------------------------------|----|

| 9.28 | Easy Start Panel Screenshot for Amplified 45MHz Channel Spacing | 71 |

| 9.29 | Amplifier Outputs for 45MHz Channel Spacing                     | 71 |

| 9.30 | Combined Amplifier Output for 45MHz Channel Spacing             | 72 |

| B.1  | Corrected DVB-SPI Pin Assignments                               | 85 |

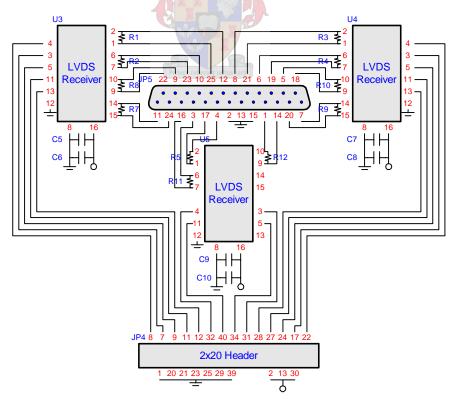

| B.2  | LVDS-to-TTL Board Schematic                                     | 85 |

| B.3  | TTL-to-LVDS Board Schematic                                     | 86 |

| B.4  | Add-On Board Schematic                                          | 86 |

| B.5  | Duplicate Add-On Board Schematic                                | 86 |

| B.6  | Top Layer                                                       | 88 |

| B.7  | Bottom Layer                                                    | 89 |

| B.8  | Top Silkscreen Overlay                                          | 90 |

| B.9  | Bottom Silkscreen Overlay                                       | 91 |

| C.1  | FPGA DevBoard Functional Diagram                                | 93 |

| D.1  | DVB-S EvBoard Functional Diagram                                | 96 |

# Abbreviations

| ADC                    | Analogue-to-Digital Converter                               |

|------------------------|-------------------------------------------------------------|

| AF                     | Adaptation Field                                            |

| AGC                    | Automatic Gain Control                                      |

| AU                     | Access Unit                                                 |

| BER                    | Bit Error Rate                                              |

| CAT                    | Conditional Access Table                                    |

| CNR                    | Carrier-to-Noise Ratio                                      |

| $\operatorname{codec}$ | coder-decoder                                               |

| CRT                    | Cathode Ray Tube                                            |

| DAC                    | Digital-to-Analogue Converter                               |

| DevBoard               | Development Board                                           |

| DIP                    | Dual In-line Package                                        |

| DVB-S                  | Digital Video Broadcasting for Satellite                    |

| DVB-SPI                | Digital Video Broadcasting - Synchronous Parallel Interface |

| EMM                    | Entitlement Management Message                              |

| $\mathbf{ES}$          | Elementary Stream                                           |

| EvBoard                | Evaluation Board                                            |

| $\operatorname{FEC}$   | Forward Error Correction                                    |

| FIFO                   | First-In, First-Out                                         |

# LIST OF FIGURES

| FPGA                | Field-Programmable Gate Array          |

|---------------------|----------------------------------------|

| GF                  | Galois Fields                          |

| ITU                 | International Telecommunication Union  |

| ITU                 | International Telecommunications Union |

| LCD                 | Liquid Crystal Display                 |

| LED                 | Light Emitting Diode                   |

| LEO                 | Low Earth Orbit                        |

| LO                  | Local Oscillator                       |

| LVDS                | Low Voltage Differential Signalling    |

| MPEG-2              | Motion Pictures Expert Group           |

| MSB                 | Most Significant Bit                   |

| NIT                 | Network Information Table              |

| PAT                 | Program Association Table              |

| $\mathbf{PC}$       | Personal Computer                      |

| PCB                 | Printed Circuit Board                  |

| PES                 | Packetised Elementary Stream           |

| PID                 | Packet Identifier                      |

| PLL                 | Phase-Lock Loop                        |

| PMT                 | Program Map Table                      |

| PSI                 | Program Specific Information           |

| PSK                 | Phase Shift Keying                     |

| PU                  | Presentation Unit                      |

| QPSK                | Quadrature Phase Shift Keying          |

| RAM                 | Random Access Memory                   |

| $\operatorname{RF}$ | Radio Frequency                        |

### Abbreviations

| RGB | Red-Green-Blue              |

|-----|-----------------------------|

| ROM | Read Only Memory            |

| RS  | Reed-Solomon                |

| SNR | Signal-to-Noise Ratio       |

| SPI | Serial Peripheral Interface |

| TS  | Transport Stream            |

| VGA | Video Graphics Adapter      |

# Chapter 1

# Introduction

Wireless communication is as old as or older than the first lighthouse or smoke signal, however man's desire for fast and accurate information greatly exceeds the capabilities of these primitive systems and shows every sign of continuing to demand for better, faster and more cost effective communication systems, of which satellite imaging systems is an example.

Satellite imaging systems require a wide-bandwidth, high-speed transmission link to cater for large high-resolution images. A better transmission link allows for more images to be downloaded and makes the system more productive. An investigation is made into current systems, which have the functions depicted in Figure 1.1, to find an affordable and upgradeable manner to increase the system's payload.

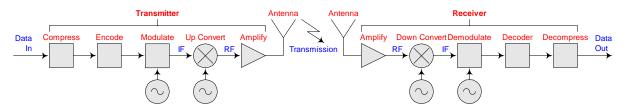

Fig. 1.1. Satellite System Functions

Imaging satellites are in Low Earth Orbit (LEO), they circle the earth in approximately 90 minutes taking pictures as they go along. Images are only downloaded while the LEO satellite is in line-of-sight of the ground station. The amount of data that is downloaded is defined as

$$payload = data rate [bits per second] \times link time [seconds]$$

(1.1)

The link time is determined by the orbit and link budget of the system, with the orbit chosen within the LEO range for a given type of image and time between revisiting a location. Therefore the link time is fixed and the only variable in Equation 1.1 is the data rate.

## 1.1 Problem Statement

The various processes within a satellite system are examined, with a block diagram of a simplified version depicted in Figure 1.2, to look at their effect on the data rate.

Fig. 1.2. Simplified Satellite System

The level of signal amplification required to obtain a given Signal-to-Noise Ratio (SNR) at the receiver is directly proportional to the signal's bandwidth [1]. The level of output power that devices can deliver decreases as the input signal's frequency increases. Therefore the available output power levels of existing components restrict an increase in data rate.

A transmitted signal's frequency, bandwidth and shape must conform to the telecommunication regulations set down by the International Telecommunication Union (ITU). These regulations limit health risks, prohibit encroachment into other signals' bands and divide the spectrum into bands for specific usages [2]. Therefore an increase in data rate is restricted by the maximum bandwidth within available frequency bands.

The form of modulation and the modulation devices' input frequency ranges limit the signal's data rate. Existing models have a maximum input frequency, which cannot be bypassed until new models are developed. Modulation techniques increase the system's baud rate by transmitting more symbols per carrier signal change, with a limit as to how miniscule the changes can be for the signal to be demodulated. Therefore existing modulation devices restricts an increase in data rate.

Data compression can be used to reduce the size of the images, thereby increasing the amount of information downloaded to the ground station for a given data rate. But, powerful compression algorithms are complex and work on multiple frames of data, with the risk of losing large chunks of irrecoverable data if the decoding process fails. Therefore the level of any compression used to increase the data rate is limited.

Unless linked to technological advances, any improvement in the devices that perform amplification, modulation and compression will only result in an extension of the system's capabilities and will not solve the data rate's reliance on these components. Therefore a solution is needed that is not based on improving upon existing devices, but rather on a technique that bypasses the limit places on the system by existing devices.

### 1.2 Proposed Solution

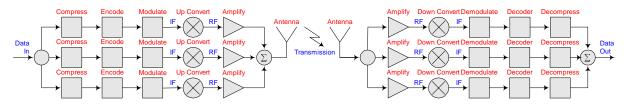

The chosen method is a parallel channel configuration, as depicted in Figure 1.3, designed in such a way that any demand for a further increase in the data rate would require little more than duplication of the existing architecture, thereby creating a system that supports an unlimited maximum data rate. A developer would be able to use the system to find the optimal number of channels for a specific application.

Fig. 1.3. Proposed Solution

Decreasing a channel's bandwidth reduces the required signal level to achieve a certain SNR. This makes available the options to use cheaper amplifiers and to place channels at higher frequencies. Whereas a single-channel system requires a high level of signal amplification, each channel in a multi-channel system would require only a fraction of this amplification.

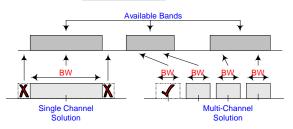

The channels can be split up into different frequency bands thereby bypassing any regulatory limit on a specific band. A single-channel system cannot be made larger than the largest available bandwidth, whereas the next channel within a multi-channel system can be allocated to another band, as depicted in Figure 1.4.

Fig. 1.4. Frequency Band Limitation Bypass

The configuration does not rely on any current modulation devices, therefore the system can always be upgraded with the latest available devices. The number of channels can be adjusted according to the price difference between a single wide-band device and multiple narrow-band devices.

The decrease in the frequency range per channel reduces the required circuitry sophistication, such as matching networks and amplifier gain flatness, thereby resulting in a cheaper system that is easier to design.

## **1.3** Implementation

To minimise costs and reduce development time only a subset of the whole system is implemented, as depicted in Figure 1.5.

Fig. 1.5. Implemented System

The antennae, frequency up-converters and frequency down-converters are excluded as no signal radiation is performed. The Radio Frequency (RF) stages and transmission link are simulated by the amplifier and attenuator placed between the transmitter and receiver.

The digital processing and modulation stages are duplicated for each channel, the results of which are combined before transmission. The signal amplification position is alternated between being before and after the signal combination to determine the best configuration.

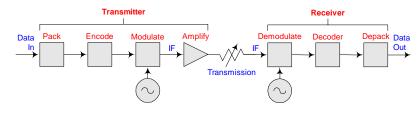

In order to be compared to current systems the system makes use of existing standards and is built from readily-available components, as depicted in Figure 1.6.

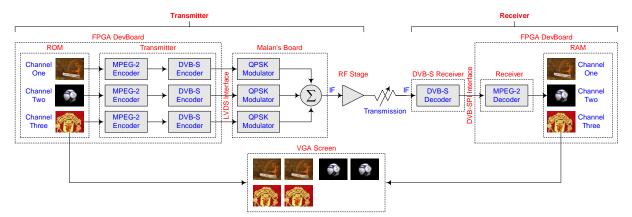

Fig. 1.6. System Block Diagram

Digital Video Broadcasting for Satellite (DVB-S) [3, 4] is the chosen method of data protection, signal modulation and signal dispersal. DVB-S combats internally created and externally encountered interference affecting satellite transmission, determines the modulation technique and shapes the signal to adhere to telecommunication regulations.

The DVB-S compliant [5] Motion Pictures Expert Group (MPEG-2) [6, 7, 8] is the chosen method of data packaging. Only the subset of the MPEG-2 standard that sorts the data according to type and the basic functions for operation are implemented, while the components that compress the audio, video and other data streams are excluded.

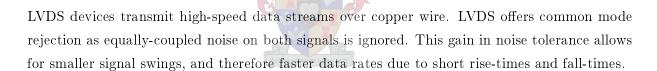

Low Voltage Differential Signalling (LVDS) [9, 10] and Digital Video Broadcasting - Synchronous Parallel Interface (DVB-SPI) [11] are the chosen method of data transfers. These standards are used to transfer digital signals between components in the system to prevent signal degradation.

#### 1.3.1 System

The system implementation is depicted in Figure 1.7.

Fig. 1.7. System Implementation

The transmitter' digital processing is implemented within a Field-Programmable Gate Array (FPGA) [12] and the analogue modulation is performed by modulators [13]. The DVB-S decoding is performed by a DVB-S Receiver [14] and the MPEG-2 decoding is implemented within the FPGA.

The effect of the spacing between channels and the non-ideal properties of the amplifier [15, 16] on the DVB-S data correction abilities are visible as a degradation in the receiver's image data displayed on the Video Graphics Adapter (VGA) screen.

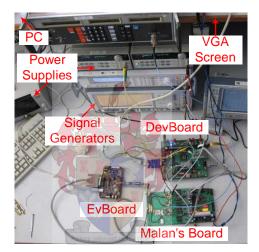

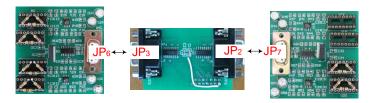

Three boards, containing components useful for debugging and testing purposes, are used to speed-up the realisation of a working model of the system. The FPGA Development Board (DevBoard) [17] contains external memory [18], video [19] and audio [20] devices. The DVB-S Evaluation Board (EvBoard) [21] contains an output interface. Malan's Board [22] contains a synthesizer [23] and mixer [24].

The FPGA DevBoard does not contain the necessary connectors and transmission lines to connect to the DVB-S EvBoard output interface of DVB-SPI. Malan's Board is not designed to directly port external data to the modulators. Therefore additional Printed Circuit Boards (PCB) containing components [25, 26] based on the LVDS standard were designed to implement these data transfers.

The current set-up of multiple boards is bulky and cumbersome. It would be wise to design a streamlined version of the system for use outside of this academic purpose. This improved version would be void of all the unnecessary components on the boards and would not require the additional boards and cabling due to the FPGA's support for LVDS [27, 28].

#### 1.3.2 MPEG-2

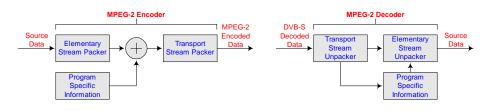

The functional block diagram of the MPEG-2 encoder and decoder is depicted in Figure 1.8. The encoder converts the source data into Elementary Streams (ES), which are placed in Transport Stream (TS) payloads together with Program Specific Information (PSI) and passed onto the DVB-S encoder. The decoder uses the PSI to separate the received DVB-S decoded data into the respective ES for conversion back into source data.

Fig. 1.8. MPEG-2 Block Diagram

### 1.3.3 DVB-S

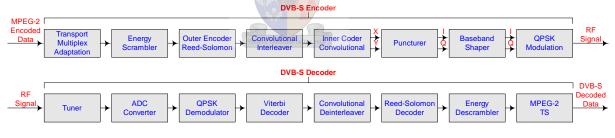

The functional block diagram of the DVB-S encoder and decoder is depicted in Figure 1.9. The encoder scrambles, encodes and modulates the received MPEG-2 encoded data. The decoder performs a reverse process on the received RF signal and passes the result onto the MPEG-2 decoder.

Fig. 1.9. DVB-S Block Diagram

#### 1.3.4 LVDS

The LVDS drivers and receivers are used as depicted in Figure 1.10. LVDS driver-receiver pairs are used to transfer data between the FPGA DevBoard and Malan's Board and a LVDS receiver is used in the data transfer from the DVB-S EvBoard to the FPGA DevBoard.

Fig. 1.10. LVDS Block Diagram

## 1.4 Thesis Outline

The first three chapters discuss the standards that the communication system is based on. Chapter 2 concentrates on the sections of the MPEG-2 standard that are implemented while only a brief overview on the sections that are not used is given. Chapter 3 explains each of the DVB-S processes with examples to help clarify the mathematical fields that they are based on. Chapter 4 explains the basics of the LVDS technology and the DVB-SPI standard and their implementation in the system.

The next three chapters discuss the audio, video, storage and synchronism mechanisms used within the system. Chapter 5 explains how the screen and audio coder-decoder (codec) are controlled to display the images and broadcast the audio. Chapter 6 describes the various memory units used, both the units within the FPGA and the units external to it, as well as the mechanism used to initialise the internal memory units with the audio and video data. Chapter 7 describes the processes within the FPGA with specific emphasis on their interconnections and synchronism.

The last three chapters discuss the completed system. Chapter 8 explains how the components are connected together and operated in order to complete the system. Chapter 9 discusses the system's successfulness based on measurements taken of the system. Chapter 10 is a summary of the system, stating conclusions and giving recommendations.

The appendices contain the PCB layouts, information about the kits and the environment settings on the FPGA DevBoard. Appendix A contains the pin assignments for the connections between the components on the FPGA DevBoard. Appendix B contains the manufactured PCB layout files. Appendix C contains information about the FPGA development kit. Appendix D contains information about the DVB-S evaluation kit.

The attached CD contains the Quartus source code for the program on the FPGA and the Delphi source code for the programs used to convert the image and audio files to a compatible format to be used to initialise the FPGA's internal memory units.

# Chapter 2

# MPEG-2

The Motion Pictures Expert Group (MPEG-2) standard [5, 6] is explained in this chapter. As MPEG-2 is only used as a packaging mechanism, which is explained in depth, the compression of the data streams is only briefly discussed. While only still pictures are used in this design, the system can be upgraded to moving pictures as MPEG-2 accommodates both data types.

# 2.1 Overview

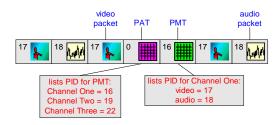

The Transport Stream (TS) contains separate programs each with their own set of data streams, as depicted in Figure 2.1. The encoder assigns each data stream an identifier which is transmitted in Program Specific Information (PSI) tables along with the programs. The decoder distinguishes between the programs, and groups their related data streams by making use of these tables [7, 8].

Fig. 2.1. TS Format

# 2.2 Elementary Stream

An Elementary Stream (ES) is a succession of Access Units (AU), which are encoded Presentation Units (PU). Different PU types and complexities lead to varying levels of compression and varying bit-rates. The most detailed information is selectively discarded to minimise the impact on quality and to obtain a fixed bit-rate [8].

#### 2.2.1 Video Compression

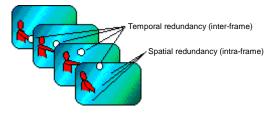

Video compression [29] exploits the chrominance and luminance sensitivity of the human visual system: the eye's inability to see quantisation noise under conditions of visual masking. Temporal masking removes the redundancy of pixel replication in successive frames and spatial masking removes the redundancy of pixel replication within a single frame, as depicted in Figure 2.2.

Fig. 2.2. Video Redundancy

The more similar subsequent images are the more references between images are possible and the better the level of compression.

### 2.2.2 Audio Compression

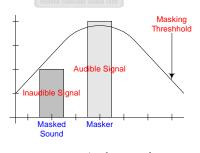

Audio compression [30, 31] exploits the psychoacoustic properties of the human auditory system: the ear's inability to hear quantisation noise under conditions of auditory masking. Faint sounds are frequency masked by louder spectral neighbours and weak sounds are temporal masked by stronger temporal neighbours, as depicted in Figure 2.3.

Fig. 2.3. Audio Masking

The more similar subsequent frames are the more references between frames are possible and the better the level of compression.

### 2.2.3 Implementation

Compression is excluded from the system and the PU are directly mapped to AU of equal size, due to the complexity of implementing compression in the FPGA exceeding the criterion of this thesis.

# 2.3 Packetised Elementary Stream

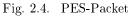

A Packetised Elementary Stream (PES) is a succession of PES-Packets made up of 6-byte headers, 3-byte optional headers and variable-length optional fields and payloads, as depicted in Figure 2.4.

| header<br>6 bytes | optional header<br>3 bytes | optional fields | payload |

|-------------------|----------------------------|-----------------|---------|

|                   |                            |                 |         |

The payload contains data from one ES, the header contains information about the ES and the optional header indicates which optional fields containing additional information are present.

#### 2.3.1 Implementation

As compression is not performed and PES primarily contains information about audio and video decoding packing of ES to PES is not implemented and the ES are fed directly to the TS.

# 2.4 Program Association Table

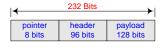

A Program Association Table (PAT) is 21-bytes long and contains a 1-byte pointer field, an 8-byte header and a 12-byte payload, as depicted in Figure 2.5.

Fig. 2.5. PAT-Section

The header contains information about the PAT-Section, the payload links the program numbers to their associated program and the pointer specifies the number of bytes between the pointer and the rest of the PAT-Section, namely zero.

### 2.4.1 PAT-Section Header

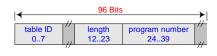

The header contains the following implemented fields, as depicted in Figure 2.6.

Fig. 2.6. PAT-Section Header

**TABLE ID** is assigned the value  $00_{16}$  to identify that this is a PAT-Section. **LENGTH** is assigned the value  $011_{16}$ , the number of bytes in the PAT-Section less 3 bytes.

### 2.4.2 PAT-Section Payload

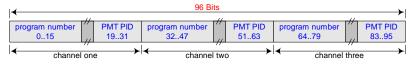

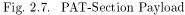

The payload contains the following two fields for each program, as depicted in Figure 2.7.

**PROGRAM NUMBER** is assigned the program that the PMT Packet Identifier (PID) is associated with, as defined in Table 2.1.

| TABLE 2.1 |        |             |

|-----------|--------|-------------|

| Program   | NUMBER | Assignments |

| Program Number | Assignment    |

|----------------|---------------|

| $0001_{16}$    | Channel One   |

| $0002_{16}$    | Channel Two   |

| $0003_{16}$ 🥢  | Channel Three |

| 000010         |               |

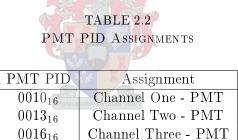

**PMT PID** is assigned the TS-Packet PID that contains the PMT-Sections, as defined in Table 2.2.

# 2.5 Program Map Table

A Program Map Table (PMT) is 29-bytes long and contains a 1-byte pointer field, a 12-byte header and a 16-byte payload, as depicted in Figure 2.8.

Fig. 2.8. PMT-Section

The header contains information about the PMT-Section, the payload links the ES to their associated program and the pointer specifies the number of bytes between the pointer and the rest of the PMT-Section, namely zero.

#### 2.5.1 PMT-Section Header

The header contains the following implemented fields, as depicted in Figure 2.9.

Fig. 2.9. PMT-Section Header

**TABLE ID** is assigned value  $02_{16}$  to identify that this is a PMT-Section. **LENGTH** is assigned the value  $019_{16}$ , the number of bytes in the PMT-Section less 3 bytes. **PROGRAM NUMBER** is assigned the program to which the PMT PID is applicable, as defined in Table 2.1.

### 2.5.2 PMT-Section Payload

The payload contains the following implemented fields for each ES within the channel, as depicted in Figure 2.10.

ES TYPE is assigned the ES type within the TS-Packet payload, as defined in Table 2.3.

TABLE 2.3ES TYPE ASSIGNMENTS

| ES Type          | Description        | ES Type          | Description        |

|------------------|--------------------|------------------|--------------------|

| C1 <sub>16</sub> | Audio Stream One   | E1 <sub>16</sub> | Video Stream One   |

| $C2_{16}$        | Audio Stream Two   | $E2_{16}$        | Video Stream Two   |

| C3 <sub>16</sub> | Audio Stream Three | $E3_{16}$        | Video Stream Three |

ES PID is assigned the TS-Packet PID carrying the ES, as defined in Table 2.4.

# TABLE 2.4ES PID Assignments

| ES PID      | Indication               | ES PID      | Indication               |

|-------------|--------------------------|-------------|--------------------------|

| $0011_{16}$ | Channel One - Video ES   | $0012_{16}$ | Channel One - Audio ES   |

| $0014_{16}$ | Channel Two - Video ES   | $0015_{16}$ | Channel Two - Audio ES   |

| $0017_{16}$ | Channel Three - Video ES | $0018_{16}$ | Channel Three - Audio ES |

**ES INFORMATION LENGTH** is assigned the value  $018_{16}$ , the number of bytes in the descriptors.

#### CHAPTER 2. MPEG-2

#### Video Stream Descriptor

The video stream descriptor identifies the coding parameters of the video ES. The video stream descriptor has the following implemented fields, as depicted in Figure 2.11.

Fig. 2.11. Video Stream Descriptor

**TAG** is assigned the value  $02_{16}$  to identify that it is a video stream descriptor. **LENGTH** is assigned the value  $01_{16}$ , the number of bytes in the descriptor less 2 bytes. **STILL PICTURE FLAG** is asserted to indicate that the video ES contains only still pictures.

#### Audio Stream Descriptor

The audio stream descriptor identifies the coding version of an audio ES. The audio stream descriptor has the following implemented fields, as depicted in Figure 2.12.

**TAG** is assigned the value  $03_{16}$  to identify that it is an audio stream descriptor. **LENGTH** is assigned the value  $01_{16}$ , the number of bytes in the descriptor less 2 bytes.

### 2.6 Conditional Access Table

The Conditional Access Table (CAT) lists the PID of the Entitlement Management Messages (EMM) used in conditional access systems. The PID and Table ID are assigned the value  $01_{16}$  to identify that it is a CAT-Section. The CAT is optional, is not defined by MPEG-2 and is not implemented in this system.

## 2.7 Network Information Table

The Network Information Table (NIT) is used to describe the physical network parameters, such as the channel frequencies, satellite transponder details and modulation characteristics. The PID and Table ID are assigned the value  $03_{16}$  to identify that it is a NIT-Section. The NIT is optional, is not defined by MPEG-2 and is not implemented in this system.

## 2.8 Transport Stream

A TS is organised into 188-byte packets made up of a 4-byte header and 184 bytes divided between the payload and Adaptation Field (AF), as depicted in Figure 2.13.

Fig. 2.13. TS-Packet

Each payload contains the data from a PES-Packet; the header contains information about this PES-Packet and the AF contains additional information about this PES-Packet.

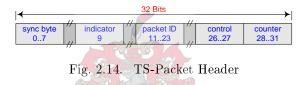

## 2.8.1 TS-Packet Header

The header contains the following implemented fields, as depicted in Figure 2.14.

**SYNC BYTE** is assigned the value 47<sub>16</sub> to synchronise the depacking of the TS. **PAYLOAD UNIT START INDICATOR** is asserted to indicate the start of a PES-Packet payload or the start of a PSI-Section. **PACKET ID** is assigned the payload's data type, as defined in Table 2.5.

## TABLE 2.5 PID Assignments

| PID         | Indication             | PID         | Indication               |

|-------------|------------------------|-------------|--------------------------|

| $0000_{16}$ | PAT                    | $0010_{16}$ | Channel One - PMT        |

| $0001_{16}$ | CAT                    | $0011_{16}$ | Channel One - Video ES   |

| $0003_{16}$ | NIT                    | $0012_{16}$ | Channel One - Audio ES   |

| $0013_{16}$ | Channel Two - PMT      | $0016_{16}$ | Channel Three - PMT      |

| $0014_{16}$ | Channel Two - Video ES | $0017_{16}$ | Channel Three - Video ES |

| $0015_{16}$ | Channel Two - Audio ES | $0018_{16}$ | Channel Three - Audio ES |

AF CONTROL is assigned the payload's contents, as defined in Table 2.6.

# TABLE 2.6AF Control Assignments

| AF Control | Indication   | AF Control | Indication             |

|------------|--------------|------------|------------------------|

| 002        | Reserved     | 102        | AF only                |

| $01_2$     | Payload only | $11_2$     | AF followed by Payload |

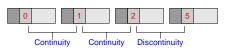

**CONTINUITY COUNTER** is incremented with each TS-Packet payload with the same PID. If sequential TS-Packets contain **CONTINUITY COUNTER** with a difference of greater than one, as depicted in Figure 2.15, an error state is reached as at least one TS-Packet has been lost in transmission.

Fig. 2.15. Continuity Counter

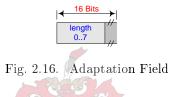

## 2.8.2 TS-Packet Adaptation Field

If present the AF is inserted between the packet's header and payload. The AF contains the following implemented fields, as depicted in Figure 2.16.

LENGTH is assigned the number of bytes in the AF less 1 byte.

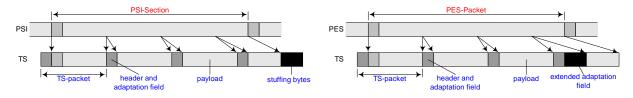

### 2.8.3 TS-Packet Payload

The PES and PSI are broken up into 184-byte blocks and placed sequentially in TS-packet payloads, as depicted in Figure 2.17.

Fig. 2.17. Conversion of PES and PSI to TS

For PES-Sections that do not fill an integral amount of TS-Packet payloads the AF of the last TS-Packet is extended to fill this gap, thereby aligning the end of the PSI-Section with the end of the TS-Packet. The AF **LENGTH** is incremented appropriately in order for the decoder to skip these bytes and the bytes are assigned the value FF<sub>16</sub>.

For PSI-Sections that do not fill an integral amount of TS-Packet payloads the remainder of the last TS-Packet payload is filled with bytes assigned the value  $FF_{16}$ . The PSI-Section header **LENGTH** is not incremented and the decoder skips these bytes.

#### 2.9Implementation

Transmitters and receivers based on the subset of the MPEG-2 system described in this chapter are coded for use in the FPGA.

## Transmitter

Each channel continually transmits the data stream depicted in Figure 2.18. The TS-Packet payloads are image pixels read in from the FPGA's internal memory and the PSI-Sections and TS-Packet headers are dynamically generated to describe the structure of the current payload. The synchronisation of these processes is discussed in Section 7.2

## Receiver

The receiver uses the TS-Packet header's PID field to separate the payload types, as depicted in Figure 2.19. The PAT decoder's output helps to decode the PMT, the PMT decoder's output helps to decode the video payloads and the video decoder's output is stored in external memory.

Fig. 2.19. Receiver Implementation

#### 2.10Summary

This chapter described the implemented subset of the MPEG-2 standard used to package the source data to facilitate the receiver's reconstruction of the original images for storage and postprocessing. The MPEG-2 encoded data in the source data for the DVB-S standard. The DVB-S standard is discussed in the next chapter.

## Chapter 3

# DVB-S

The Digital Video Broadcasting for Satellite (DVB-S) standard [3] is discussed in this chapter. DVB-S is used to counter interference, modulate the data and shape the signal to adhere to telecommunication regulations. How the various processes perform these functions, the mathematical fields that they are based on and their implementation in the system are described. Each section contains examples to help clarify the processes' purposes.

## 3.1 Transport Multiplex Adaptation

The DVB-S encoder's input is the MPEG-2 encoder's output and the DVB-S decoder's output is the MPEG-2 decoder's input, as depicted in Figure 3.1. In the transmitter the sync byte of every eighth Transport Stream (TS) packet is bit-wise inverted to  $B8_{16}$  for synchronisation purposes. In the receiver this inversion is mirrored to regain the original sync byte value of  $47_{16}$ .

| ←              | 188 Bytes            | <b>→</b> |

|----------------|----------------------|----------|

| sync<br>1 byte | payload<br>187 bytes |          |

|                |                      |          |

Fig. 3.1. TS-Packet

## 3.2 Energy Dispersal

A transmitted signal with a fixed pattern creates line components in the Radio Frequency (RF) carrier's spectrum that causes power flux-density peaks to occur at the surface of the Earth that exceed the International Telecommunication Union's (ITU) recommended level. Therefore an energy dispersal technique [32] is required to adequately randomise this signal to disperse the RF carrier's energy, while not degrading the quality of the data stream.

#### 3.2.1 Spectra of PSK Digital Signals

The power spectrum of a carrier modulated by ideal phase reversals consists of lines separated by  $\frac{1}{Nt}$  Hz, where N is the number of symbols of the pseudo-random sequence and t is the seconds per symbol. The power spectrum of these lines is given by Equation 3.1

$$W(f) \approx \frac{1}{N} \left\{ \frac{\sin \pi \left( f - f_c \right) t}{\pi \left( f - f_c \right) t} \right\}^2 \delta \left( f - f_c - \frac{n}{Nt} \right)$$

(3.1)

where n is an integer,  $f_c$  is the RF carrier frequency and  $\delta$  is the Dirac-delta function.

The largest line is at n = 1. As the sequence length approaches infinity the line separation approaches zero, the power spectrum becomes continuous and the maximum spectral-density occurs at the carrier frequency. Equation 3.2 refers to the idealised situation of a random sequence, while an actual modulating signal may be far from random.

$$W(f) = t \left\{ \frac{\sin \pi (f - f_c) t}{\pi (f - f_c) t} \right\}^2$$

(3.2)

To ensure the desired degree of dispersal a sequence of Nt duration is added to the information stream. For a reference bandwidth of x Hz the energy dispersal factor, D, is defined by Equation 3.3.

$$D = 10 \log \frac{\text{total power}}{\text{maximum power per } x \text{ Hz}}$$

(3.3)

The degree of dispersal is estimated by Equation 3.1 and Equation 3.3 when  $\frac{1}{Nt} \ge x$  Hz and by Equation 3.2 and Equation 3.3 when  $\frac{1}{Nt} < x$  Hz. The degree of dispersal is proportional to N as long as the sequence duration is less than the reciprocal of the reference bandwidth. Little additional dispersal is gained after the sequence duration passes this point.

## 3.2.2 Implementation

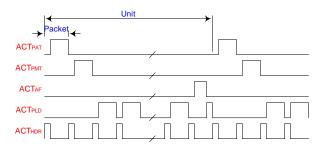

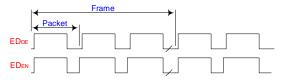

A scrambler generates a sequence to convert the data stream, as depicted in Figure 3.1, into a pseudo-random pattern, depicted in Figure 3.2.

Fig. 3.2. Energy Scrambler Diagram

The polynomial  $1 + X^{14} + X^{15}$  organises the exclusive-or gate connections and the initialisation sequence  $100101010000000_2$  is loaded into the shift register after every eighth TS-Packet.

The first bit of the sequence is applied to the first bit of the first byte following the inverted sync byte. For synchronisation purposes the sequence's output is disabled for the subsequent seven sync bytes thereby leaving these bytes unchanged. Thus the sequence has a 1503-byte period, as depicted in Figure 3.3.

Fig. 3.3. Randomised Transport Packets

A descrambler of identical design is used to remove the energy dispersal to recover the original data stream.

#### Example

The energy scrambler in Figure 3.2 is used to scramble the fixed pattern data stream of 1111 1111 1111 11112. The sequence  $0000\ 0011\ 1111\ 0100_2$  is generated and converts the data stream into the random pattern 1111 1100 0000 10112. Instead of the 16 consecutive '1' bits a more evenly distributed signal is transmitted.

An identical descrambler is used to descramble the random pattern. The descrambler generates the same sequence of 0000 0011 1111  $0100_2$  to convert the random pattern back into the original data stream of 1111 1111 1111 1111\_2.

## 3.3 Reed-Solomon Coding

Reed-Solomon (RS) [33, 34] is a form of Forward Error Correction (FEC) that is used in data transmission to counter burst errors by handling errors on a symbol-length basis.

The RS encoder breaks the digital data into equal-sized blocks and appends parity symbols to each block. The RS decoder attempts to recover the original block by finding and correcting any errors that occurred during transmission.

RS is specified as RS(n, k, t) with *m*-bit symbols, where *n* is the codeword length, *k* is the number of data symbols, *t* is the number of errors that can be found and corrected, 2t = n - k is the number of parity symbols and  $n \leq 2^m + 1$ , as depicted in Figure 3.4.

Fig. 3.4. Reed-Solomon Codeword

If a continuous burst of errors is bound within t symbols in a block the RS decoder is able to decode that block. This is depicted for a RS(7,3,2) decoder with 3-bit symbols in Figure 3.5.

6-bit error Symbolo Symbola Symbola Symbola Symbola Symbols Symbole

Fig. 3.5. Retrievable Codeword

If the errors occur in a random fashion where more than t symbols are affected, then the RS decoder is unable to decode that block. This is depicted for a RS(7,3,2) with 3-bit symbols in Figure 3.6.

1-bit error

1-bit error

Symbolo

Symbols

Symbols

Symbols

Symbols

Symbols

Fig. 3.6. Irretrievable Codeword

Therefore RS coding is used in conjunction with convolutional coding, as discussed in Section 3.5, which performs well with random errors.

#### 3.3.1 Galois Fields

RS coding is based on an area of finite fields known as Galois Fields (GF). In finite fields the arithmetic operations of addition, subtraction, multiplication and division on field elements results in an element in the field.

For any prime number, p, there exists a finite field, GF(p), that contains p elements. The extension field,  $GF(p^m)$ , extends this to a field of  $p^m$  elements, where m is a nonzero positive integer and  $GF(p^m)$  contains the elements of GF(p). RS symbols are constructed from  $GF(2^m)$ .

Each nonzero element in  $GF(2^m)$  can be represented by a power of  $\alpha$ . An infinite set of elements, F, is formed by starting with the elements  $\{0, \alpha^0, \alpha^1\}$  and generating additional elements by progressively multiplying the last entry by  $\alpha$ , which yields

$$F = \left\{0, \alpha^0, \alpha^1, \alpha^2, \dots, \alpha^j, \dots\right\}$$

(3.4)

To obtain the finite set of elements of  $GF(2^m)$  from F the condition  $\alpha^{2^m-1} = \alpha^0$  is imposed on F to limit it to only  $2^m$  elements. Therefore any field element with a power greater than  $2^m - 1$  is reduced to an element with a power less than  $2^m - 1$ . This reduces F to the finite field  $F^*$ , with

$$F^* = \{0, \alpha^0, \alpha^1, \alpha^2, \dots, \alpha^{2^m - 2}, \alpha^0, \alpha^1, \alpha^2\}$$

(3.5)

and the elements of  $GF(2^m)$  are

$$GF(2^{m}) = \left\{0, \alpha^{0}, \alpha^{1}, \alpha^{2}, \dots, \alpha^{2^{m}-2}\right\}$$

(3.6)

Each of the  $2^m$  elements of  $GF(2^m)$  can be represented as a distinct polynomial of degree m-1 or less. Each of the nonzero elements of  $GF(2^m)$  is a polynomial,  $a_i(X)$ , where at least one of the *m* coefficients is nonzero. For  $i = 0, 1, 2, ..., 2^m - 2$ ,

$$\alpha^{i} = a_{i}(X) = a_{i,0} + a_{i,1}X + \ldots + a_{i,m-1}X^{m-1}$$

(3.7)

Addition (with subtraction being equivalent) of two elements of  $GF(2^m)$  is modulo-two sum of each of the polynomial coefficients of like powers, therefore

$$\alpha^{i} + \alpha^{j} = (a_{i,0} + a_{j,0}) + (a_{1,1} + a_{j,1}) X + \ldots + (a_{i,m-1} + a_{j,m-1}) X^{m-1}$$

(3.8)

Multiplication of two field elements is the addition of the exponents modulo  $2^m - 1$ .

Primitive polynomials define the extension finite fields that define the RS codes. An irreducible polynomial, f(X), of degree m is said to be primitive if the smallest positive integer n for which f(X) divides  $X^n + 1$  is  $n = 2^m - 1$ , yielding a nonzero quotient and a zero remainder.

#### Example

$GF(2^3)$  is defined by  $f(X) = 1 + X + X^3$ . There are  $2^m = 8$  finite elements and m = 3 roots. To solve for the roots of f(X) the values of X that correspond to f(X) = 0 must be found. The binary elements of 1 and 0 do not satisfy f(X) since f(1) = 1 and f(0) = 1. Therefore the roots lie in  $GF(2^3)$ . Define  $\alpha$ , an element of  $GF(2^3)$ , to be a root of f(X). Therefore

$$f(\alpha) = 0$$

$$1 + \alpha + \alpha^{3} = 0$$

$$\alpha^{3} = -1 - \alpha$$

(3.9)

Since in the binary field  $+1 = -1 \alpha^3$  can be represented as

$$\alpha^3 = 1 + \alpha \tag{3.10}$$

Similarly the other powers are determined to be

$$\begin{aligned}

\alpha^4 &= \alpha \times \alpha^3 &= \alpha + \alpha^2 \\

\alpha^5 &= \alpha \times \alpha^4 &= 1 + \alpha + \alpha^2 \\

\alpha^6 &= \alpha \times \alpha^5 &= 1 + \alpha^2 \\

\alpha^7 &= \alpha \times \alpha^6 &= \alpha^0

\end{aligned}$$

(3.11)

As  $\alpha^7 = \alpha^0$  the eight finite field elements of  $GF(2^3)$  are

$$GF(2^3) = \{0, \alpha^0, \alpha^1, \alpha^2, \alpha^3, \alpha^4, \alpha^5, \alpha^6\} = \{0, 1, 2, 4, 3, 6, 7, 5\}$$

(3.12)

## 3.3.2 Reed-Solomon Encoding

The generator polynomial, g(X), for a RS code takes the form of

$$g(X) = g_0 + g_1 X + g_2 X^2 + \dots + g_{2t-1} X^{2t-1} + X^{2t}$$

(3.13)

There are 2t successive powers of  $\alpha$  that are the roots of the polynomial,  $\alpha, \alpha^2, \ldots, \alpha^{2t}$ . We describe g(X) in terms of its 2t roots as

$$g(X) = (X - \alpha) \left( X - \alpha^2 \right) \dots \left( X - \alpha^{2t} \right)$$

(3.14)

The codeword polynomial, U(X), for a RS encoder is

$$U(X) = p(X) + X^{n-k}m(X), \qquad (3.15)$$

where m(X) is the message polynomial,  $X^{n-k}$  is the algebraic manipulation to right-shift m(X)n-k positions in the codeword and p(X) is the parity polynomial that is placed in the leftmost n-k stages of the codeword. p(X) is defined as

$$p(X) = X^{n-k}m(X) \mod g(X)$$

(3.16)

### Example

A RS(7,3,2) encoder is used to encode the data stream  $111011010_2 = \alpha^5 + \alpha^3 + \alpha^1$ , which is equivalent to  $m(X) = \alpha^5 X^2 + \alpha^3 X + \alpha^1$ . From Equation 3.14 g(X) is calculated to be

$$g(X) = (X - \alpha) (X - \alpha^{2}) (X - \alpha^{3}) (X - \alpha^{4})$$

=  $(X^{2} - \alpha^{4} + \alpha^{3}) (X^{2} - \alpha^{6} + \alpha^{0})$

=  $X^{4} - \alpha^{3}X^{3} + \alpha^{0}X^{2} - \alpha^{1}X + \alpha^{3}$  (3.17)

Since in the binary field +1 = -1 g(X) can be represented as

$$g(X) = \alpha^3 + \alpha^1 X + \alpha^0 X^2 + \alpha^3 X^3 + X^4$$

(3.18)

From Equation 3.16 m(X) is multiplied by  $X^4$  to yield  $\alpha^5 X^6 + \alpha^3 X^5 + \alpha^1 X^4$  and then divided by g(X) in Equation 3.18 to yield a p(X) of

$$p(X) = \alpha^{6} X^{3} + \alpha^{4} X^{2} + \alpha^{2} X + \alpha^{0}$$

(3.19)

From Equation 3.15 U(X) is

$$U(X) = \alpha^5 X^6 + \alpha^3 X^5 + \alpha^1 X^4 + \alpha^6 X^3 + \alpha^4 X^2 + \alpha^2 X + \alpha^0$$

(3.20)

#### 3.3.3 Reed-Solomon Decoding

The RS decoder's received polynomial, r(X), is the sum of the transmitted codeword and any error-pattern, e(X), encountered in transmission, therefore

$$r(X) = U(X) + e(X)$$

(3.21)

Non-binary symbols require that both the error locations be found and the correct symbols at those locations be determined. If there are v errors in the codeword at location  $X^{j_1}, X^{j_2}, \ldots, X^{j_v}$ e(X) would be

$$e(X) = e_{j_1} X^{j_1} + e_{j_2} X^{j_2} + \ldots + e_{j_v} X^{j_v}$$

(3.22)

where the indices 1, 2, ..., v refer to the first, second, ...,  $v^{th}$  errors and the index j refers to the error location. To correct the corrupted codeword each error value  $e_{j_l}$  and its location  $X^{j_l}$ , where l = 1, 2, ..., v, must be determined. An error locator number is defined as  $\beta_1 = \alpha^{j_l}$ .

U(X) and g(X) have the same roots as U(X) is a multiple of g(X). Therefore a parity check performed on r(X) results in a zero value to indicate a valid members of the codeword set and a nonzero value to indicate the presence of errors. The syndrome, S, is the result of this parity check and is computed as

$$S_{i} = r\left(\alpha^{i}\right) = e_{j_{1}}\beta_{1}^{i} + e_{j_{2}}\beta_{2}^{i} + \ldots + e_{j_{v}}\beta_{v}^{i}$$

(3.23)

with i = 1, 2, ..., 2t.

There are 2t unknowns, made up of t error values and t locations, and 2t simultaneous equations. These equations can not be solved in the conventional way as they are non-linear. To find the location of these errors an error-locator polynomial,  $\sigma(X)$ , is defined as

$$\sigma(X) = (1 + \beta_1 X) (1 + \beta_2 X) \dots (1 + \beta_v X), \qquad (3.24)$$

where its roots are  $1/\beta_1, 1/\beta_2, \ldots, 1/\beta_v$ . Using autoregressive-modelling techniques a matrix is formed from S, where the first t syndromes are used to predict the next syndrome:

$$\begin{bmatrix} \sigma_t \\ \sigma_{t-1} \\ \vdots \\ \sigma_2 \\ \sigma_1 \end{bmatrix} = \begin{bmatrix} S_1 & S_2 & \cdots & S_{t-1} & S_t \\ S_2 & S_3 & \cdots & S_t & S_{t+1} \\ \vdots & \vdots & & \\ S_{t-1} & S_t & \cdots & S_{2t-3} & S_{2t-2} \\ S_t & S_{t+1} & \cdots & S_{2t-2} & S_{2t-1} \end{bmatrix}^{-1} \begin{bmatrix} -S_{t+1} \\ -S_{t+2} \\ \vdots \\ -S_{2t-1} \\ -S_{2t} \end{bmatrix}$$

(3.25)

We determine these roots by exhaustive testing of  $\sigma(X)$  with each of the field elements. An element X that yields  $\sigma(X) = 0$  is a root and its reciprocal is the location of an error.

Substitution of the location values into the syndrome equations yields the values of the errors. As the RS decoder is limited to finding t error locations and correcting t errors, t syndrome equations are required. This results in the estimated error polynomial,  $\hat{e}(X)$ , where

$$\hat{e}(X) = e_{j_1} X^{j_1} + e_{j_2} X^{j_2} + \ldots + e_{j_v} X^{j_v}, \qquad (3.26)$$

The estimated codeword polynomial,  $\hat{U}(X)$ , is the combination of r(X) and  $\hat{e}(X)$  and is equal to U(X) as long as r(X) does not contain more than t errors.

### Example

In Section 3.3.2 a RS(7,3,2) is used to encode a data stream that resulted in the codeword in Equation 3.20. During transmission the maximum number of symbols, t = 2, are corrupted to create the received codeword

$$r(X) = \alpha^{5} X^{6} + \alpha^{3} X^{5} + \underline{\alpha^{6}} X^{4} + \underline{\alpha^{0}} X^{3} + \alpha^{4} X^{2} + \alpha^{2} X + \alpha^{0}$$

(3.27)

From Equation 3.23 the four syndrome symbols are found to be

$$S_{1} = r(\alpha^{1}) = \alpha^{3}$$

$$S_{2} = r(\alpha^{2}) = \alpha^{5}$$

$$S_{3} = r(\alpha^{3}) = \alpha^{6}$$

$$S_{4} = r(\alpha^{4}) = 0$$

$$(3.28)$$

From Equation 3.25 the autoregressive model is found to be

$$\begin{bmatrix} \sigma_2 \\ \sigma_1 \end{bmatrix} = \begin{bmatrix} \alpha^1 & \alpha^0 \\ \alpha^0 & \alpha^5 \end{bmatrix} \begin{bmatrix} \alpha^6 \\ 0 \end{bmatrix} = \begin{bmatrix} \alpha^0 \\ \alpha^6 \end{bmatrix}$$

(3.29)

From Equation 3.24 and Equation 3.29  $\sigma(X)$  is found to be

$$\sigma(X) = \alpha^0 + \alpha^6 X + \alpha^0 X^2 \tag{3.30}$$

From Equation 3.30 the roots and the error locations are found to be

From Equation 3.22 and Equation 3.31 the error values are found to be

$$\begin{bmatrix} e_1 \\ e_2 \end{bmatrix} = \begin{bmatrix} \alpha^2 & \alpha^5 \\ \alpha^0 & \alpha^4 \end{bmatrix} \begin{bmatrix} \alpha^3 \\ \alpha^5 \end{bmatrix} = \begin{bmatrix} \alpha^2 \\ \alpha^5 \end{bmatrix}$$

(3.32)

From Equation 3.26  $\hat{e}(X)$  is found to be

$$\hat{e}(X) = \alpha^2 X^3 + \alpha^5 X^4$$

(3.33)

From Equation 3.33 and Equation 3.27  $\hat{U}(X)$  is found to be

$$\hat{U}(X) = \alpha^5 X^6 + \alpha^3 X^5 + \alpha^1 X^4 + \alpha^6 X^3 + \alpha^4 X^2 + \alpha^2 X + \alpha^0$$

(3.34)

This estimated codeword is equal to the transmitted codeword in Equation 3.20.

#### 3.3.4 Implementation

The RS(255, 239, 8) shortened code RS(204, 188, 8) with  $f(X) = X^8 + X^4 + X^3 + X^2 + 1$  and  $g(X) = (X - \alpha^0) (X - \alpha^1) \dots (X - \alpha^{15})$  is implemented.

The compiler [35] encodes each randomised transport packet, as depicted in Figure 3.3, to generate an error protected packet, as depicted in Figure 3.7. The decoder decodes the RS encoded packets and outputs the randomised transport packets to the descrambler.

| 14   | 204 Bytes                       | <b>&gt;</b>               |

|------|---------------------------------|---------------------------|

|      |                                 |                           |

| Sync | Randomised Payload<br>187 Bytes | RS(204,188,8)<br>16 Bytes |

Fig. 3.7. Reed Solomon Error Protected Packet

## 3.4 Interleaving

The data stream is interleaved to reduce the chance of a burst error from affecting consecutive symbols. A convolutional interleaver scrambles the symbols as a periodic function of time.

## 3.4.1 Convolutional Interleaving

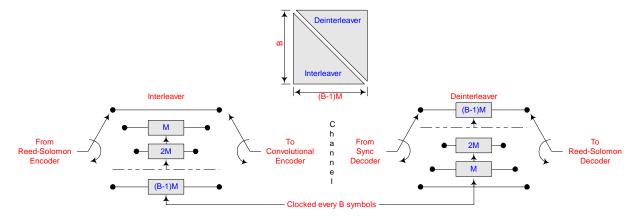

Convolutional interleaving [4, 36] is created by diagonally splitting a B-by-N rectangular array into two halves, where B is the number of shift registers and N is the error protection frame length, as depicted in Figure 3.8. One half is the interleaver and the other half is the deinterleaver.

Fig. 3.8. B-by-N Convolutional Interleaver

At the transmitter the coded sequence is fed into a *B*-by-*N* triangular array of shift registers. The  $i^{th}$  shift register has a depth of (1-i)M stages, where  $1 \le i \le B$  and M = N/B. The registers are clocked once every *B* symbols and the oldest symbols in the registers are shifted out to the channel. The received sequence is restored to its original ordering using an inverse structure of shift registers. Symbols that are delayed by (i-1)M stages at the transmitter are delayed by (B-i)Mstages at the receiver. All symbols receive a total delay of (B-1)M stages and the total memory space requirement is N(B-1) symbols.

A *B*-by-*N* convolutional interleaver increases a random error correction code's efficiency as any channel burst of  $\gamma M$  symbols affects no more than  $\gamma$  of the *B* register output sequences at a time. The deinterleaver spaces these sequences to give bursts of  $\gamma$  symbols spaces by  $(B - \gamma) M$  error free symbols.

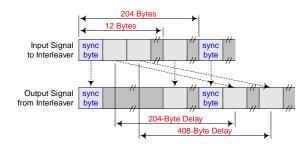

#### 3.4.2 Implementation

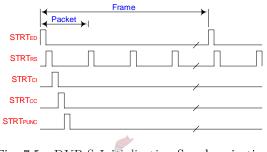

A 12-by-204 convolutional interleaver processes the error-protected packets, as depicted in Figure 3.7, to create the interleaved frame of overlapping error-protected packets, as depicted in Figure 3.9.

To preserve the 204-byte periodicity the sync bytes are routed to the i = 1 shift register, which corresponds to a null delay, as depicted in Figure 3.10. Similarly the first byte following the sync byte is routed to the i = 2 shift register, resulting in a 204-symbol delay, the second byte following the sync byte is routed to the i = 3 shift register, resulting in a 408-byte delay, etc...

Fig. 3.10. Encoder Implementation

The deinterleaver routes the first recognised sync byte to the i = 1 shift register, which corresponds to a 1224-symbol delay and a total interleaver-deinterleaver delay of 1224 symbols. Similarly the first byte following the sync byte is routed to the i = 2 shift register, resulting in a 2004-symbol delay and a total interleaver-deinterleaver delay of 1224 symbols, the second byte following the sync byte is routed to the i = 3 shift register, resulting in a 1836-byte delay and a total interleaver-deinterleaver, resulting in a 1836-byte delay and a total interleaver-deinterleaver, resulting in a 1836-byte delay and a total interleaver delay of 1224 symbols, the second byte following the sync byte is routed to the i = 3 shift register, resulting in a 1836-byte delay and a total interleaver-deinterleaver delay, resulting in a 1836-byte delay and a total interleaver-deinterleaver delay, resulting in a 1836-byte delay and a total interleaver-deinterleaver delay, resulting in a 1836-byte delay and a total interleaver-deinterleaver delay, resulting in a 1836-byte delay and a total interleaver-delay of 1224 symbols, etc...

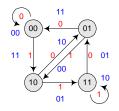

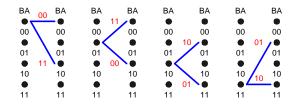

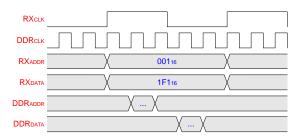

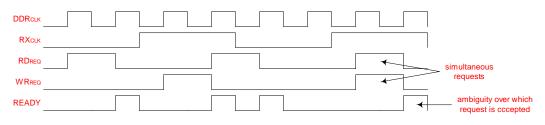

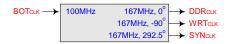

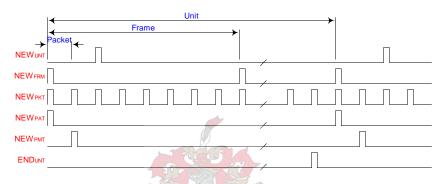

## 3.5 Convolutional Coding