UNIVERSITEIT•STELLENBOSCH•UNIVERSITY jou kennisvennoot • your knowledge partner

# A Cryogenic CMOS-based Control System for Testing Superconductor Electronics

by

Philip Charl van Niekerk

Thesis presented in partial fulfilment of the requirements for the degree of Master of Science in Engineering at the University of Stellenbosch

> Department of Electrical and Electronic Engineering University of Stellenbosch Private Bag X1, 7602 Matieland, South Africa

> > Supervisor: Dr. C. J. Fourie

March 2008

Copyright © 2008 University of Stellenbosch All rights reserved.

# Declaration

I, the undersigned, hereby declare that the work contained in this thesis is my own original work and that I have not previously in its entirety or in part submitted it at any university for a degree.

Date: .....

# Abstract

## A Cryogenic CMOS-based Control System for Testing Superconductor Electronics

P.C. van Niekerk

Department of Electrical and Electronic Engineering University of Stellenbosch Private Bag X1, 7602 Matieland, South Africa

Thesis: M.Sc.Eng. (E&E)

March 2008

A complete control system, with accompanying software, is designed to interface superconductive digital and sensory circuits for use in cryogenic vacuumed environments. It acts as an inter-mediator between superconductor electronics and room temperature electronics for research purposes.

In order to facilitate low bit-error rate communications with superconductive electronics, the system is designed to have ultra low-noise current and voltage sources for transmitting data to superconductor electronics. Very high sensitivity voltage inputs are also implemented for data extraction from superconductor electronics. It implements both digital as well as analog design components, including ADC and DAC devices. The data is transmitted via a USB cable connection at 1Mbaud to a computer where the data is processed by specially designed software and graphically displayed for user interfaced research.

Extensive research is done on the electronic components, such as CMOS devices, for functioning in an average temperature of 70 Kelvin inside cryogenic environments. This is done to reduce the thermal noise and heat transfer to superconductor electronics. An integrated temperature control system also ensures a stable environment for the electronics to operate at 70 K.

# Uittreksel

## A Cryogenic CMOS-based Control System for Testing Superconductor Electronics

P.C. van Niekerk

Department of Electrical and Electronic Engineering University of Stellenbosch Private Bag X1, 7602 Matieland, South Africa

Tesis: M.Sc.Eng. (E&E)

Maart 2008

'n Volledige beheerstelsel met meegaande sagteware is ontwerp om supergeleierlogika en sensorstroombane te toets in kriogeniese vakuumtoestande. Die beheerstelsel tree op as 'n tussenganger vir supergeleierelektronika en gewone kamertemperatuurelektronika vir navorsingsdoeleindes.

Om lae bisfout-tempokommunikasie te fasiliteer met supergeleierelektronika is die beheerstelsel ontwerp met ultra-laeruisstroom- en spanningsbronne vir data versending na supergeleierelektronikabane. Hoë sensitiewe spannings-intree kanale is ook geïmplementeer om data te onttrek van die supergeleierbane. Die ontwerp bevat digitaal en analoogkomponente, insluitend A/D en D/A omskakelaars. Data oordrag na 'n rekenaar word deur 'n USB-kabel teen 1 Mbaud gedoen, waar die data verwerk word deur die spesiaal-ontwikkelde sagteware. Hier word die data dan grafies voorgestel vir navorsings doeleindes deur die gebruiker.

Deeglike navorsing is ook gedoen op verskeie elektroniese komponente, soos CMOS-tegnologie, om in 'n kriokoeler by 'n temperatuur van 70 Kelvin te kan funksioneer. Dit word gedoen om termiese ruis- en hitte-oordrag te verminder. 'n Geïntegreerde temperatuurbeheerstelsel verseker 'n stabiele omgewing vir die elektronika om te werk by 'n temperatuur van 70 K.

# Acknowledgements

Thank you to:

- The University of Stellenbosch, specifically the Department of Electrical and Electronic Engineering for the use of the resources and equipment required to complete this thesis.

- The National Research Foundation (NRF) for their financial contributions to this thesis.

- Dr. C. J. Fourie for his inspirational guidance, support and endless ideas throughout the progress of this thesis.

- CES (Central Electronic Services), specifically Mr. U. Büttner and Mr. W. Croukamp for their help with ideas for the mechanical implementations of my designs inside the cryocooler.

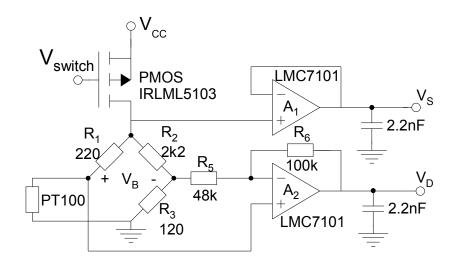

- Mr. P. de Kock for insight and help with the design of the pre-amp stage of the PT100 temperature sensor.

- Mr. A. Cupido for manufacturing almost all the prototype PCB designs used in this thesis.

- Mr. J. Arendse for his patience with populating the final PCB design for the control system.

- Mr. P. Lötter for his ideas on microprocessors and pulse width modulation.

- Mr. H de Villiers for computer setup and Linux insight.

- Ms. R. van As and Ms. M. Doman for proof reading and language corrections.

- Riaan du Toit for a lot of moral support, encouragement, good laughs and solid prayers.

- Willem Burger with a lot of technical insight and help and for keeping the caffeine levels at the right levels.

- Aan pa en ma vir julle motivering en belangstelling en al julle gebede wat my gedra het. So ook aan my tweede pa en ma, oom Willie en tannie Wilna Lambrechts, vir julle motivering en gebede deur die moelike tye, baie dankie.

#### ACKNOWLEDGEMENTS

• All the credit for this thesis goes to my heavenly Father and Lord, Jesus Christ, for granting me the ability to stretch my limits and for providing me with strength, wisdom and insight.

# Contents

| D             | eclar        | ation           |                                   |  | ii    |

|---------------|--------------|-----------------|-----------------------------------|--|-------|

| $\mathbf{A}$  | Abstract iii |                 |                                   |  | iii   |

| U             | ittrel       | ksel            |                                   |  | iv    |

| A             | cknov        | wledge          | ements                            |  | v     |

| С             | onter        | $\mathbf{nts}$  |                                   |  | vii   |

| $\mathbf{Li}$ | st of        | Figur           | es                                |  | xi    |

| $\mathbf{Li}$ | st of        | Table           | s                                 |  | xv    |

| $\mathbf{Li}$ | st of        | Abbre           | eviations                         |  | xvi   |

| $\mathbf{Li}$ | st of        | $\mathbf{Symb}$ | ols                               |  | xviii |

| 1             | Intr         | oducti          | ion                               |  | 1     |

| <b>2</b>      | Bac          | kgrou           | nd and Specifications             |  | 3     |

|               | 2.1          | Cryog           | enic Environments                 |  | 3     |

|               | 2.2          | CMOS            | S Technology                      |  | 5     |

|               | 2.3          | Contro          | ol System                         |  | 5     |

|               | 2.4          | Guide           | lines and Specifications          |  | 6     |

| 3             | Pro          | posed           | Control System Configurations     |  | 7     |

|               | 3.1          | Comp            | uter Interface and Communications |  | 7     |

|               |              | 3.1.1           | USB Interface                     |  | 7     |

|               |              | 3.1.2           | USART                             |  | 9     |

|               |              | 3.1.3           | SPI Communication                 |  | 10    |

|               | 3.2          | Micro           | chip PIC Control System           |  | 11    |

|               |              | 3.2.1           | Component Choices                 |  | 11    |

|   |     | 3.2.2   | Initial Cryogenic Test Setup                                                                                     |

|---|-----|---------|------------------------------------------------------------------------------------------------------------------|

|   |     | 3.2.3   | Results                                                                                                          |

|   |     | 3.2.4   | Conclusion                                                                                                       |

|   | 3.3 | ATME    | L PWM Subsystems                                                                                                 |

|   |     | 3.3.1   | Component Choices                                                                                                |

|   |     | 3.3.2   | Pulse Width Modulation                                                                                           |

|   |     | 3.3.3   | Cryogenic Tests                                                                                                  |

|   |     | 3.3.4   | System Design                                                                                                    |

|   |     | 3.3.5   | Conclusion                                                                                                       |

|   | 3.4 | Final I | Proposed Cryogenic Control System                                                                                |

|   | 3.5 | Conclu  | usion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $27$                                                          |

| 4 | Des | ign of  | Subsystems 29                                                                                                    |

| - | 4.1 | 0       | Circuitry                                                                                                        |

|   |     | 4.1.1   | Voltage Regulation                                                                                               |

|   |     | 4.1.2   | Voltage References                                                                                               |

|   |     | 4.1.3   | Current Sensing                                                                                                  |

|   |     | 4.1.4   | Voltage Sensing                                                                                                  |

|   |     | 4.1.5   | Summary                                                                                                          |

|   | 4.2 | Fibre ( | Optical USB Connection                                                                                           |

|   |     | 4.2.1   | FT232R                                                                                                           |

|   |     | 4.2.2   | Fibre Optical Conversion                                                                                         |

|   |     | 4.2.3   | Summary                                                                                                          |

|   | 4.3 | Impler  | nented D/A and A/D Converters                                                                                    |

|   |     | 4.3.1   | DAC and ADC Voltage Rails 40                                                                                     |

|   |     | 4.3.2   | Digital to Analogue Converter                                                                                    |

|   |     | 4.3.3   | Analogue to Digital Converters                                                                                   |

|   |     | 4.3.4   | Summary                                                                                                          |

|   | 4.4 | Multip  | blexed Chip Select Lines                                                                                         |

|   |     | 4.4.1   | MAX398 44                                                                                                        |

|   |     | 4.4.2   | Conclusion                                                                                                       |

|   | 4.5 | Microp  | processor $\ldots \ldots 45$ |

|   |     | 4.5.1   | ATmega16                                                                                                         |

|   |     | 4.5.2   | Summary 46                                                                                                       |

|   | 4.6 | Tempe   | erature Control System                                                                                           |

|   |     | 4.6.1   | Temperature Sensor    47                                                                                         |

|   |     | 4.6.2   | Design Procedure                                                                                                 |

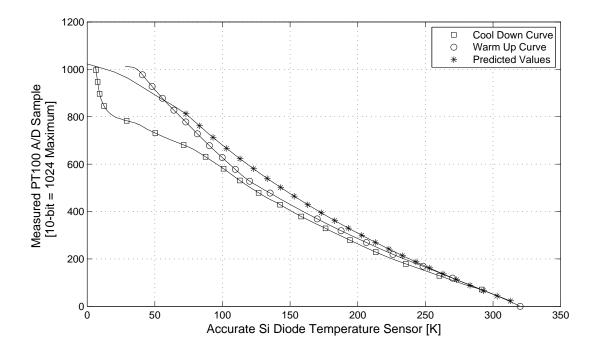

|   |     | 4.6.3   | PT100 Calibration                                                                                                |

|   |     | 4.6.4   | PT1000 Improvements                                                                                              |

|          |      | 4.6.5   | PT1000 Calibration                                                                                                       |

|----------|------|---------|--------------------------------------------------------------------------------------------------------------------------|

|          |      | 4.6.6   | Heater Design                                                                                                            |

|          |      | 4.6.7   | Conclusion                                                                                                               |

|          | 4.7  | High (  | Current Channels                                                                                                         |

|          |      | 4.7.1   | Implemented Design                                                                                                       |

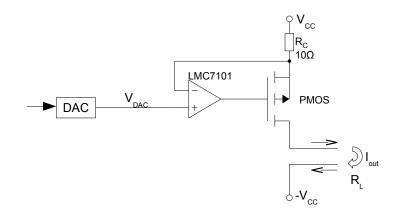

|          |      | 4.7.2   | PMOS Design                                                                                                              |

|          |      | 4.7.3   | Conclusion                                                                                                               |

|          | 4.8  | Low C   | urrent and Voltage Output Channel Combination                                                                            |

|          |      | 4.8.1   | Bipolar Conversion                                                                                                       |

|          |      | 4.8.2   | Digital Switch                                                                                                           |

|          |      | 4.8.3   | Low Current Channel                                                                                                      |

|          |      | 4.8.4   | Low Voltage Channel                                                                                                      |

|          |      | 4.8.5   | Output Current and Voltage Monitoring                                                                                    |

|          |      | 4.8.6   | Summary                                                                                                                  |

|          | 4.9  | High S  | ensitivity Voltage Input Channels                                                                                        |

|          |      | 4.9.1   | Instrumentation Amplifier                                                                                                |

|          |      | 4.9.2   | Implementation                                                                                                           |

|          |      | 4.9.3   | Summary                                                                                                                  |

|          | 4.10 | Daugh   | terboard Identification System                                                                                           |

|          |      | 4.10.1  | Unique Identification                                                                                                    |

|          |      | 4.10.2  | Conclusion                                                                                                               |

|          | 4.11 | Conclu  | $sion \dots \dots$ |

| <b>5</b> | Syst | em In   | plementation 72                                                                                                          |

|          | 5.1  | Hardw   | are Implementation                                                                                                       |

|          |      | 5.1.1   | Fibre Optical Connections and Overview                                                                                   |

|          |      | 5.1.2   | Outside Connections                                                                                                      |

|          |      | 5.1.3   | Mechanics                                                                                                                |

|          |      | 5.1.4   | Motherboard Construction                                                                                                 |

|          |      | 5.1.5   | Daughterboard Constructions                                                                                              |

|          |      | 5.1.6   | Conclusion                                                                                                               |

|          | 5.2  | Softwa  | re Implementation                                                                                                        |

|          |      | 5.2.1   | Embedded Firmware Development                                                                                            |

|          |      | 5.2.2   | User Interface Software Development                                                                                      |

|          |      | 5.2.3   | Conclusion                                                                                                               |

|          | 5.3  | Summ    | ary                                                                                                                      |

| 6        | Con  | trol Sy | vstem Tests and Results 10                                                                                               |

|          | 6.1  | High (  | Current Output Channels                                                                                                  |

|          |      | 6.1.1   | Linearity and Accuracy                                                                                                   |

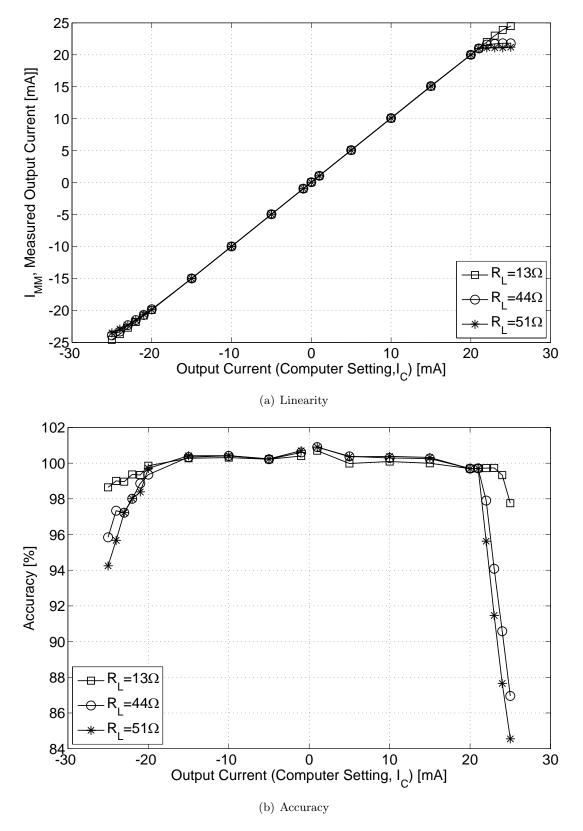

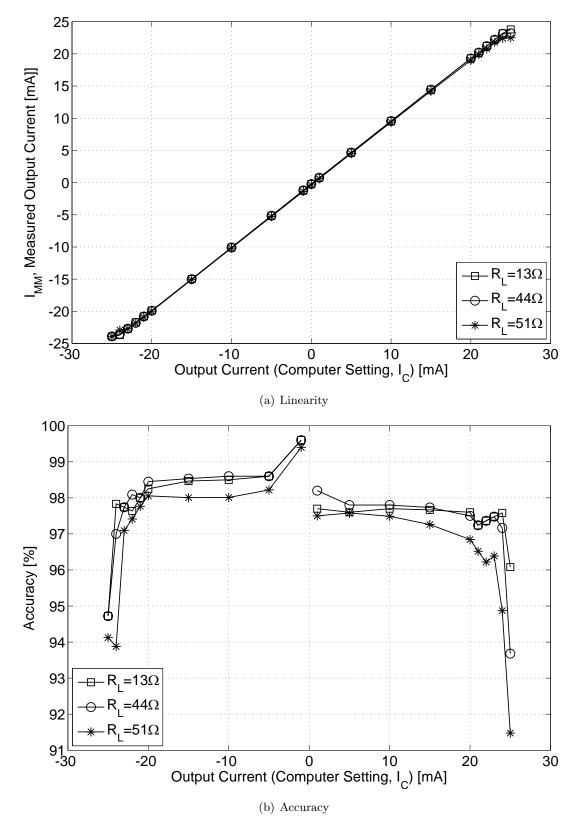

|              | 6.2   | Low Current Output Channels                    | . 110      |

|--------------|-------|------------------------------------------------|------------|

|              |       | 6.2.1 Linearity and Accuracy                   | . 110      |

|              |       | 6.2.2 Feedback Monitor Accuracy                | . 113      |

|              |       | 6.2.3 Oscilloscope Measurements                | . 116      |

|              | 6.3   | Low Voltage Output Channels                    | . 117      |

|              |       | 6.3.1 Linearity and Accuracy                   | . 117      |

|              |       | 6.3.2 Feedback Monitor Accuracy                | . 120      |

|              |       | 6.3.3 Oscilloscope Measurements                | . 123      |

|              | 6.4   | High Sensitivity Voltage Input Channels        | . 123      |

|              | 6.5   | Temperature Control System                     | . 126      |

|              | 6.6   | Control System Power Usage                     | . 127      |

|              | 6.7   | Conclusion                                     | . 129      |

| 7            | Con   | clusion, Recommendations and Future Prospects  | 131        |

|              | 7.1   | Conclusion                                     | . 131      |

|              | 7.2   | Recommendations                                | . 132      |

|              | 7.3   | List of Contributions                          | . 134      |

|              | 7.4   | Future Prospects                               | . 134      |

| Bi           | bliog | graphy                                         | 135        |

| $\mathbf{A}$ | PCI   | B Designs                                      | A-1        |

|              | A.1   | Schematics                                     | . A–1      |

|              | A.2   | PCB Layouts                                    | . A–11     |

| в            | Har   | dware Designs                                  | B-1        |

| С            | Pro   | gramming Code                                  | C–1        |

|              | C.1   | Assembler Code for PWM                         | . C–1      |

|              | C.2   | Firmware Programming                           | . C–1      |

|              | C.3   | Graphical User Interface                       | . C–1      |

|              |       |                                                |            |

| D            | PT1   | 1000 Calibration Tables                        | D-1        |

| D<br>E       |       | 1000 Calibration Tables<br>ocooler Time Cycles | D–1<br>E–1 |

# List of Figures

| 2.1  | A two-stage, 4 K cryocooler                                                             | 4  |

|------|-----------------------------------------------------------------------------------------|----|

| 3.1  | FTDI system implementation for first generation tests                                   | 8  |

| 3.2  | Fibre optical FTDI implementation for computer interface                                | 9  |

| 3.3  | A UART serial transmission of two bytes.                                                | 10 |

| 3.4  | SPI master-slave interconnection.                                                       | 10 |

| 3.5  | Test boards and a<br>luminium boxes for the DAC and ADC (left) and the $\rm PIC16F876A$ |    |

|      | (right)                                                                                 | 12 |

| 3.6  | An illustration of the PIC test setup                                                   | 13 |

| 3.7  | The ADS7807U ADC results while sampling 1 volt in cryogenic temperatures                | 13 |

| 3.8  | PWM example of an ATMEL AVR device                                                      | 16 |

| 3.9  | The ATtiny26 PWM connection wires for tests in the cryocooler.                          | 17 |

| 3.10 | Internal clock frequency deviation of two ATtiny26 devices plotted against temper-      |    |

|      | ature drop                                                                              | 19 |

| 3.11 | The AD5262 digital potentiometer cryogenic test results                                 | 21 |

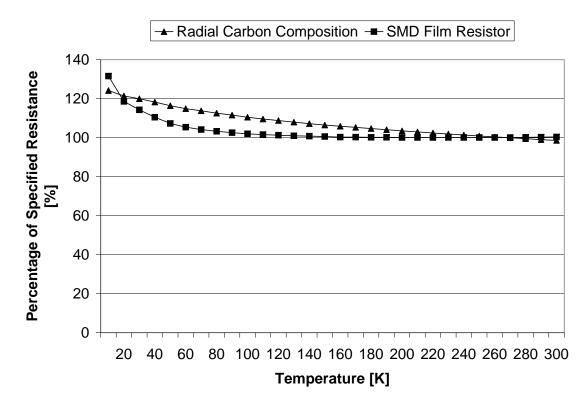

| 3.12 | Tested resistor types with characteristic plots against cryogenic temperature range.    | 22 |

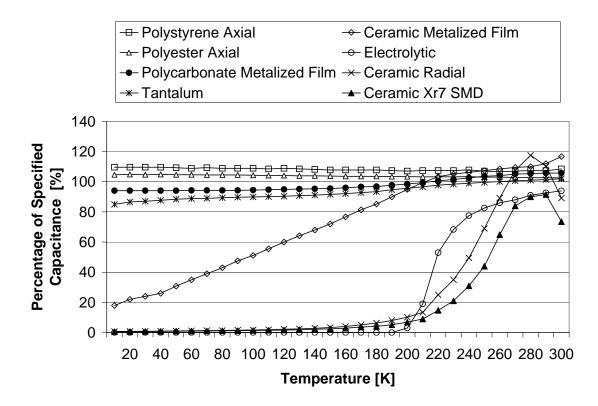

| 3.13 | Tested capacitor types with characteristic plots against cryogenic temperature range.   | 23 |

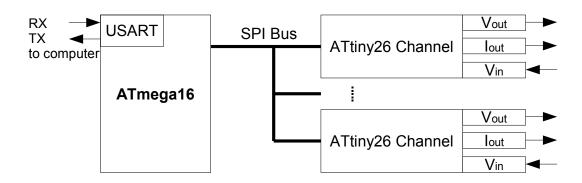

| 3.14 | The ATtiny26 PWM subsystems                                                             | 24 |

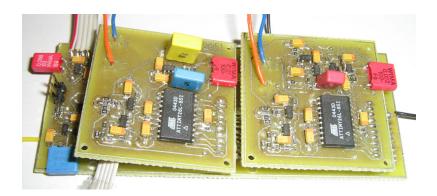

| 3.15 | Prototype system with ATtiny26 subsystem boards.                                        | 25 |

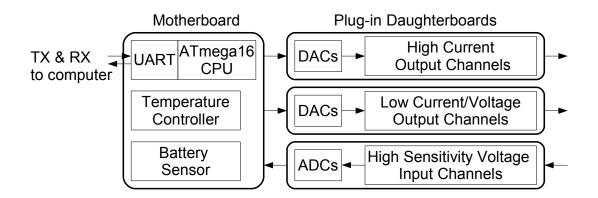

| 3.16 | Cryocooler stages with extension chamber                                                | 26 |

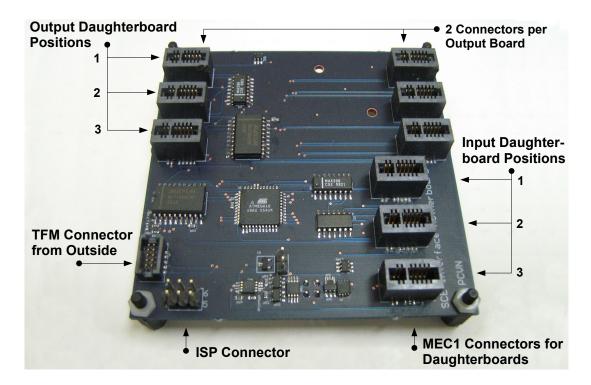

| 3.17 | Motherboard with input and output daughterboards                                        | 27 |

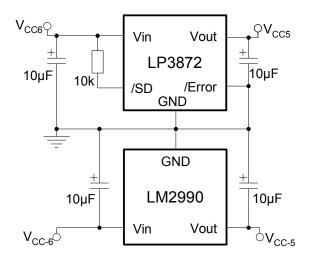

| 4.1  | Regulator configurations                                                                | 30 |

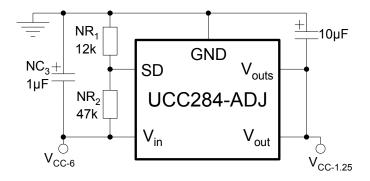

| 4.2  | The UCC284-ADJ negative regulator setup                                                 | 31 |

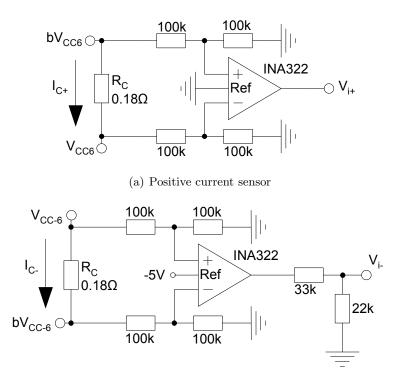

| 4.3  | Current sensing circuits                                                                | 32 |

| 4.4  | Battery voltage measurement adjustment                                                  | 34 |

| 4.5  | The FTDI USB-USART to fibre optical converter.                                          | 35 |

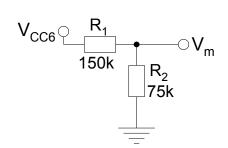

| 4.6  | (a) The proposed circuit design and (b) the implemented circuit design for modu-        |    |

|      | lating the TX signal.                                                                   | 36 |

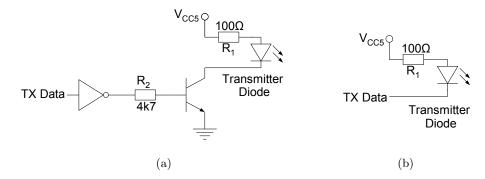

| 4.7  | Simulations of the light modulator signals for the designs shown in Fig. $4.6(a)$ and   |    |

|      | (b)                                                                                     | 38 |

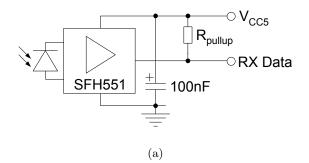

| 4.8  | The SFH551/1-1V photo detector connection diagram                               |

|------|---------------------------------------------------------------------------------|

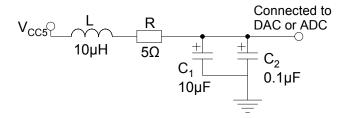

| 4.9  | DC power filter for each implemented DAC and ADC                                |

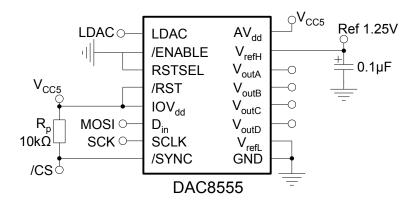

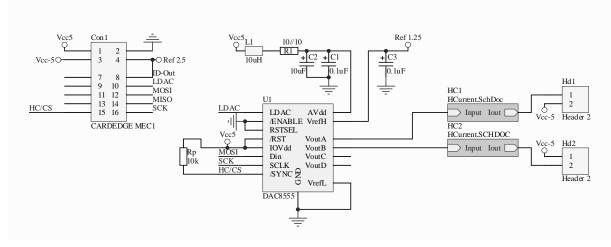

| 4.10 | The DAC8555 circuit configuration for the <i>high current channel</i>           |

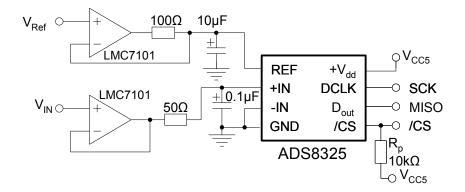

| 4.11 | The ADS8325 implementation circuit                                              |

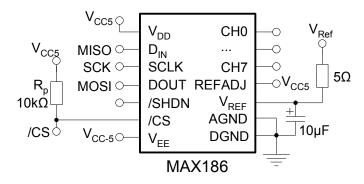

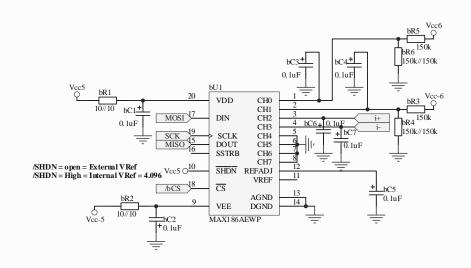

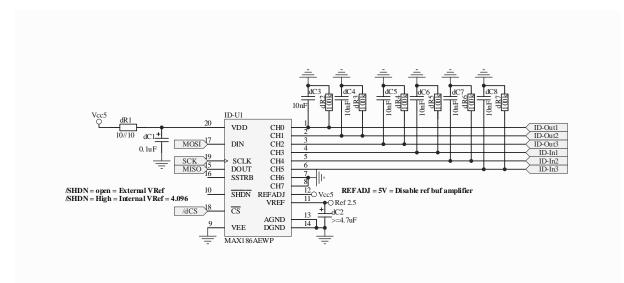

| 4.12 | The MAX186 configuration circuit                                                |

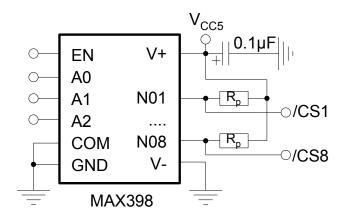

| 4.13 | Implementation of the MAX398                                                    |

| 4.14 | PT100 temperature sensor bridge 44                                              |

| 4.15 | PT100 calibration plots                                                         |

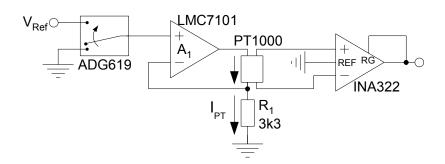

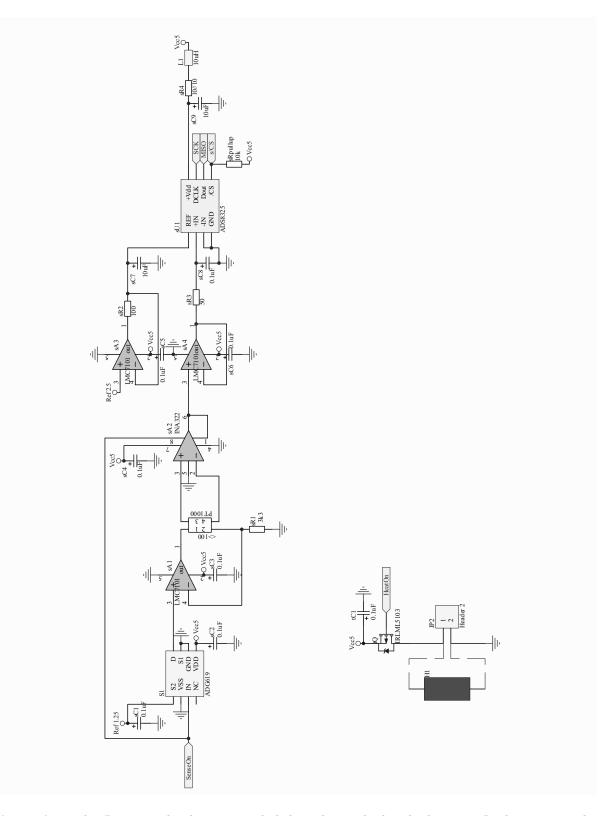

| 4.16 | PT1000 measurement circuit                                                      |

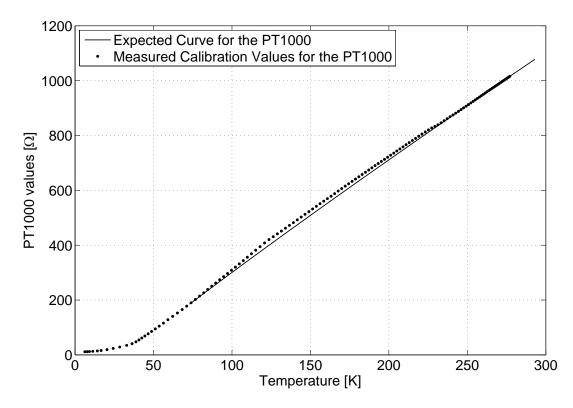

| 4.17 | PT1000 calibrated values                                                        |

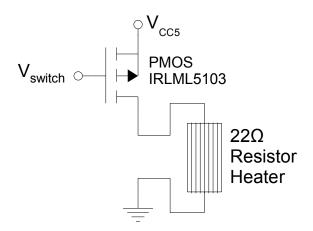

| 4.18 | The resistor heater implementation                                              |

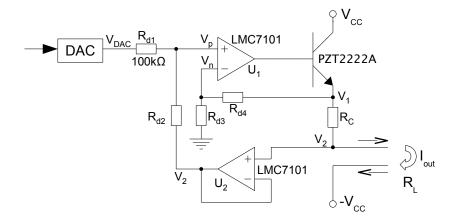

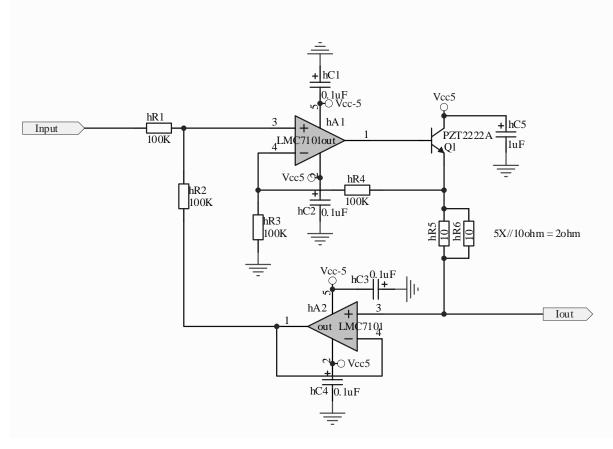

| 4.19 | The implemented high current source circuit                                     |

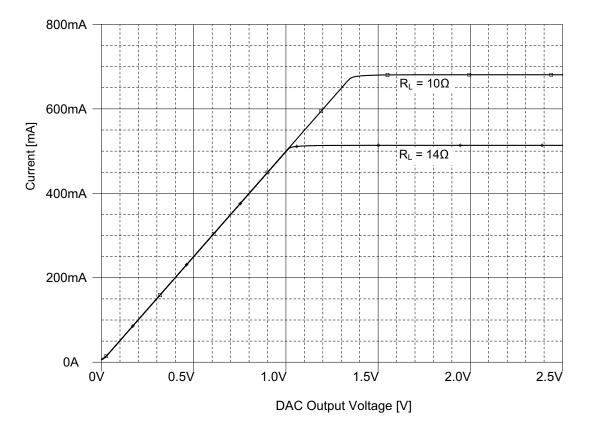

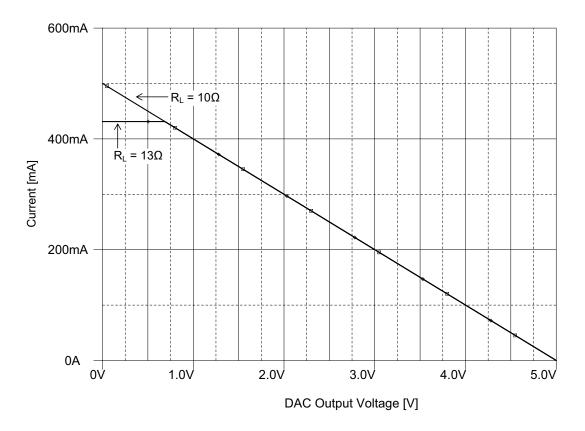

| 4.20 | Simulation results of the <i>high current source</i>                            |

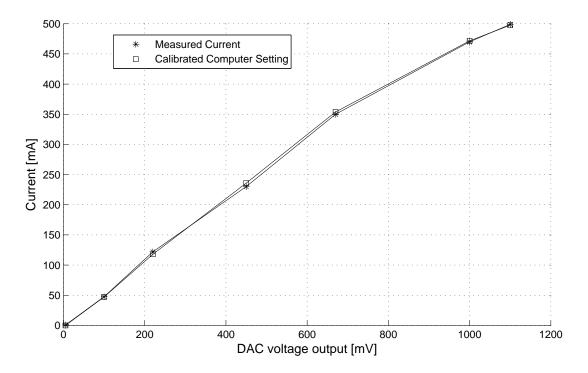

| 4.21 | Measured results of the <i>high current channel</i>                             |

| 4.22 | High current channel                                                            |

| 4.23 | Simulation of the PMOS design current channel                                   |

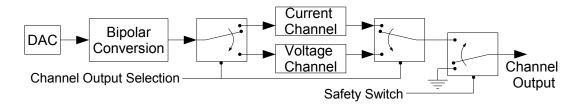

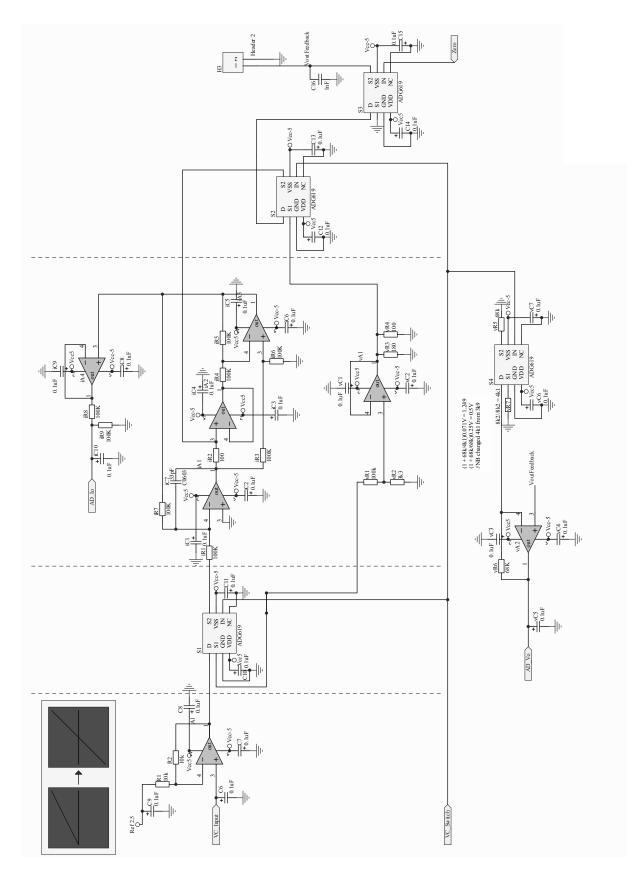

| 4.24 | Low current and voltage channel combination                                     |

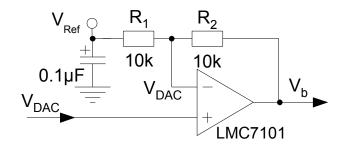

| 4.25 | The bipolar conversion circuit                                                  |

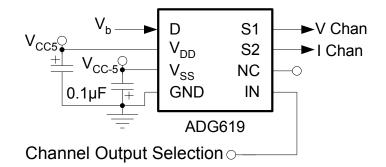

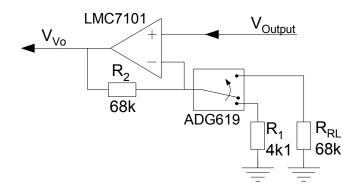

| 4.26 | The ADG619 switch circuit.                                                      |

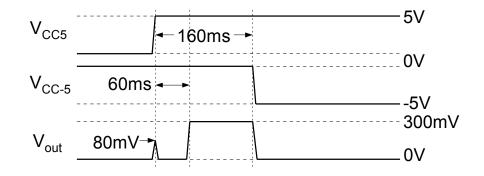

| 4.27 | Measured offset voltage on output channel with unsynchronized voltage rails 6   |

| 4.28 | Low current channel                                                             |

| 4.29 | Simulation of the output from the <i>low current channel</i>                    |

| 4.30 | AC sweep simulation of the current source with the LPF                          |

| 4.31 | Low voltage channel                                                             |

| 4.32 | Current monitor feedback system                                                 |

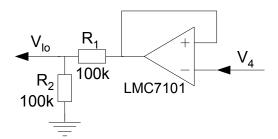

| 4.33 | Output voltage monitor feedback system                                          |

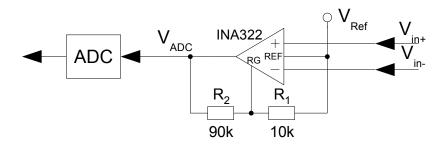

| 4.34 | Voltage input channel                                                           |

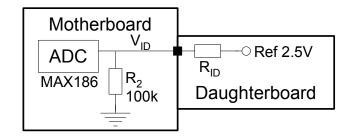

| 4.35 | Implementation of the daughterboard identification system                       |

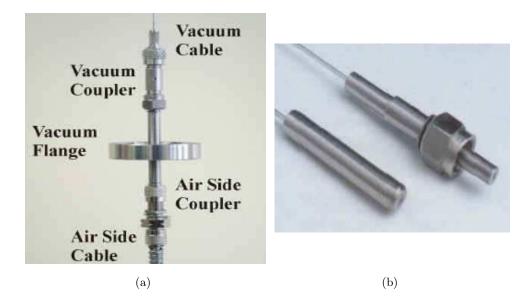

| 5.1  | (a) Fibre optical vacuum feedthrough with (b) the SMA and straight ferrule con- |

|      | nector options                                                                  |

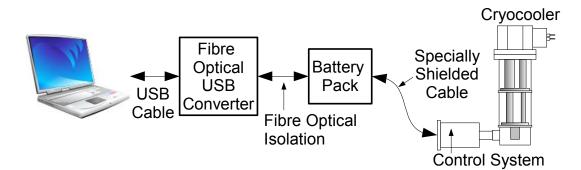

| 5.2  | Hardware connection overview diagram                                            |

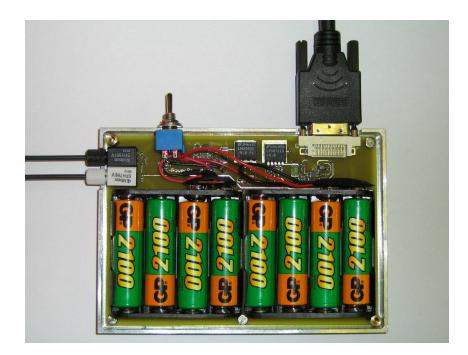

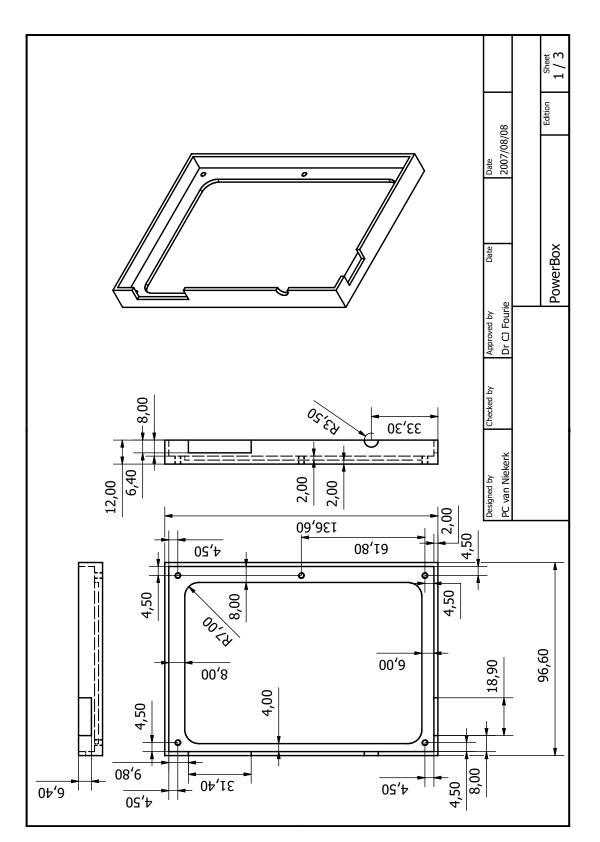

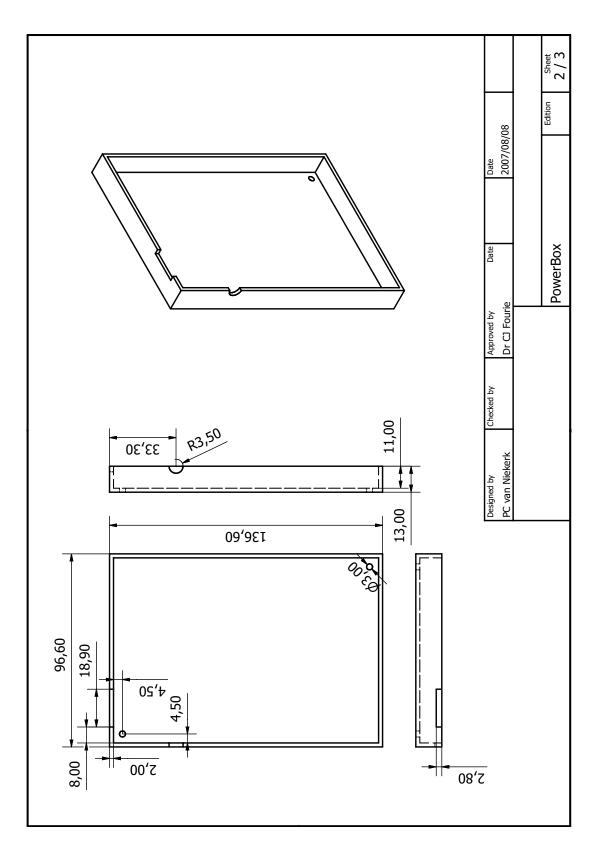

| 5.3  | Aluminium power box for the batteries                                           |

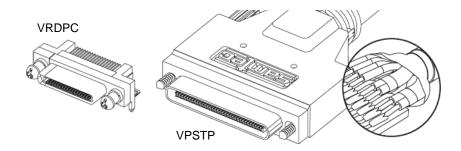

| 5.4  | The shielded VPSTP cable with its accompanying VRDPC connector from SAMTEC. 74  |

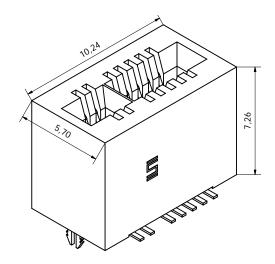

| 5.5  | The MEC1 connector (Dimensions in mm)                                           |

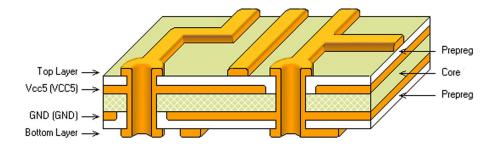

| 5.6  | Side view of a 4-layer PCB constructed at TraX                                  |

| 5.7  | Motherboard with the indicated connectors                                       |

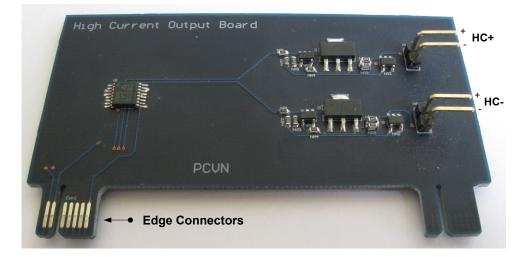

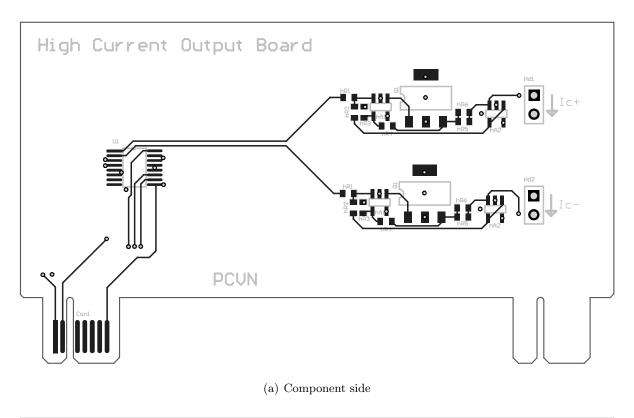

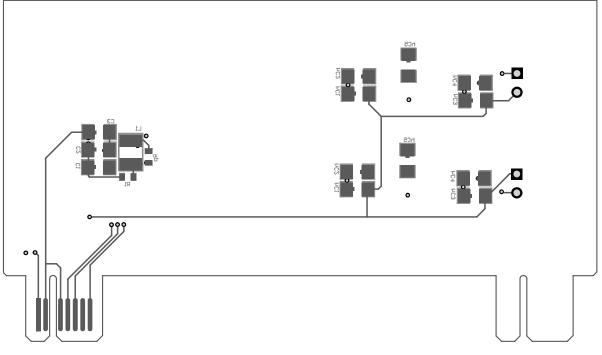

| 5.8  | High current daughterboard with two channels                                    |

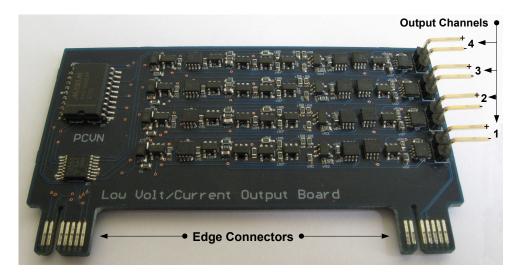

| 5.9  | Low current and voltage output daughterboard with four channels                 |

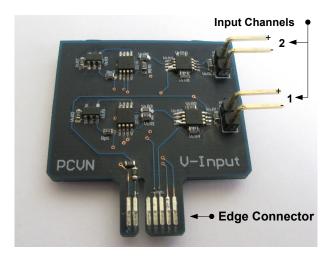

| 5.10 | High sensitivity voltage input daughterboard.                                              | 82  |

|------|--------------------------------------------------------------------------------------------|-----|

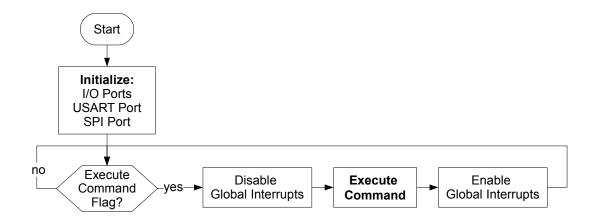

| 5.11 | The main program on the ATmega16 microprocessor                                            | 84  |

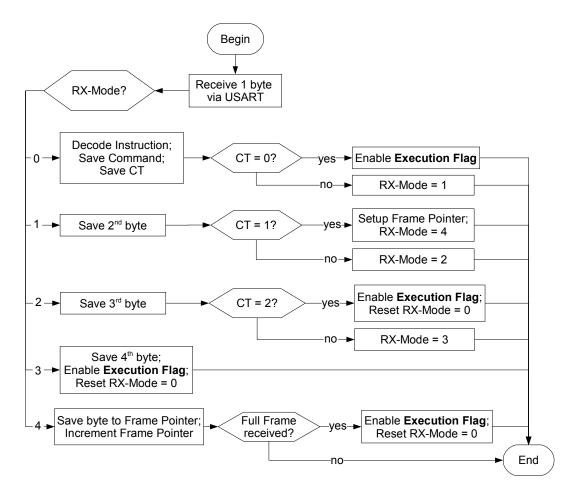

| 5.12 | Receiving a command through the USART interrupt procedure                                  | 85  |

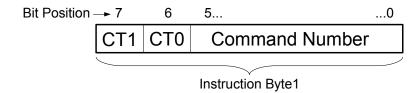

| 5.13 | The bit layout of the $1^{st}$ instruction byte.                                           | 85  |

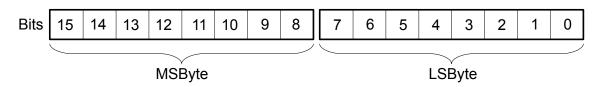

| 5.14 | Two-byte return value format                                                               | 88  |

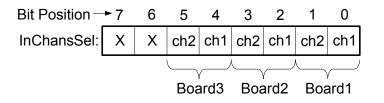

| 5.15 | Bit positions of <i>InChansSel</i> for selecting specific input channels                   | 91  |

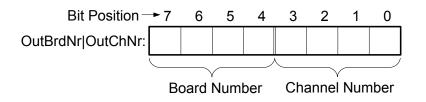

| 5.16 | The byte allocation of $OutBrdNr/OutChNr$ for selecting a specific board and channel       |     |

|      | number                                                                                     | 91  |

| 5.17 | Bit positions of <i>OutChansSel</i> for selecting a specific output channel                | 92  |

| 5.18 | Send and receive of the data frames.                                                       | 93  |

| 5.19 | Timing diagram for command execution on the ATmega16 microprocessor                        | 94  |

| 5.20 | An example of the GUI application for the control system                                   | 98  |

| 5.21 | Output and input channel settings                                                          | 100 |

| 5.22 | GUI for the temperature control system and battery status monitor                          | 101 |

| 5.23 | The flow diagram for the temperature control system                                        | 102 |

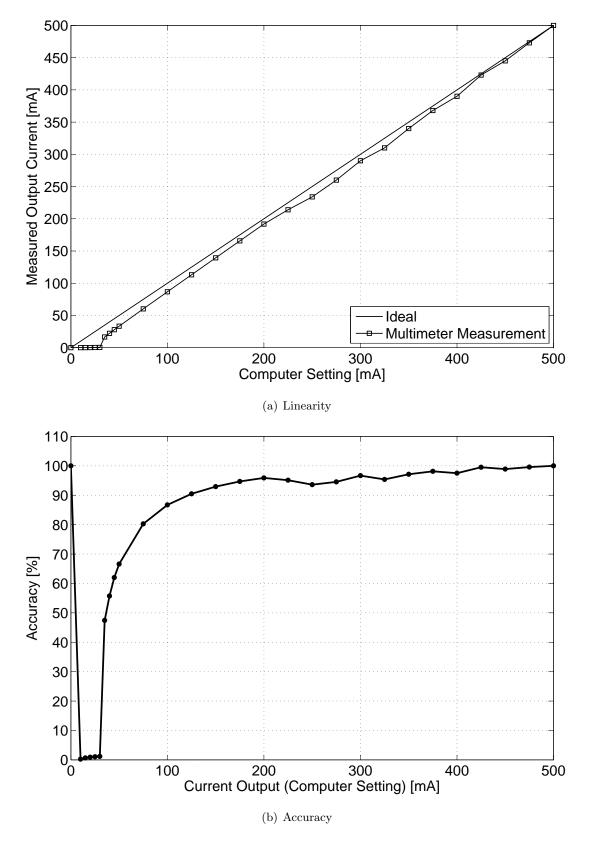

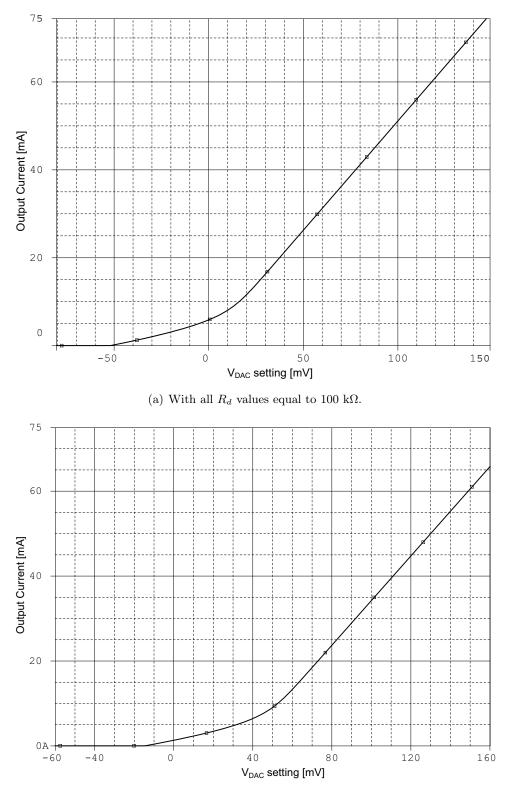

| 6.1  | The (a) linearity and (b) accuracy of the <i>high current channel</i> output at 300 K      | 106 |

| 6.2  | The (a) linearity and (b) accuracy of the high current channel output at 85 K. $$ .        | 107 |

| 6.3  | Simulations of the <i>high current channel</i> , showing the non-linear response at low    |     |

|      | output values                                                                              | 109 |

| 6.4  | The (a) linearity and (b) accuracy of the <i>low current channel</i> outputs for different |     |

|      | load resistances at 300 K                                                                  | 111 |

| 6.5  | The (a) linearity and (b) accuracy of the <i>low current channel</i> outputs for different |     |

|      | load resistances at 85 K                                                                   | 112 |

| 6.6  | The feedback monitor (a) deviation from actual measurement, and (b) accuracy at            |     |

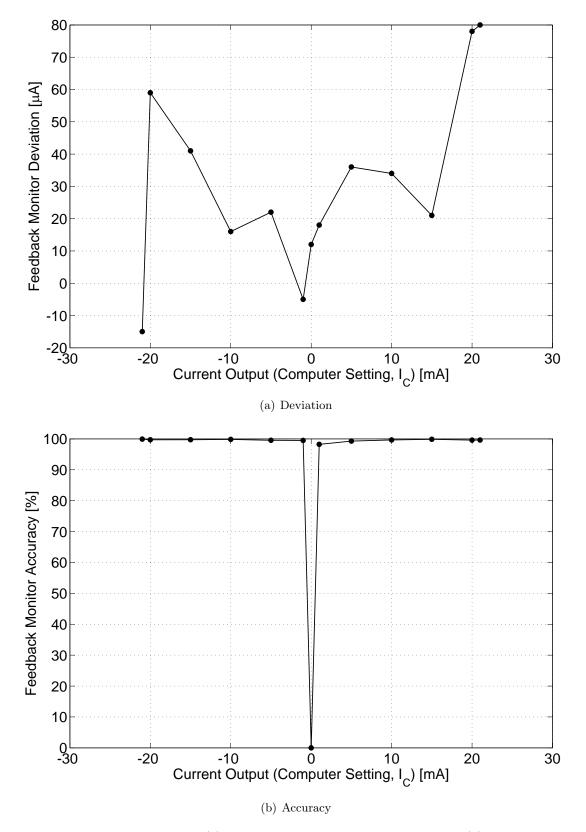

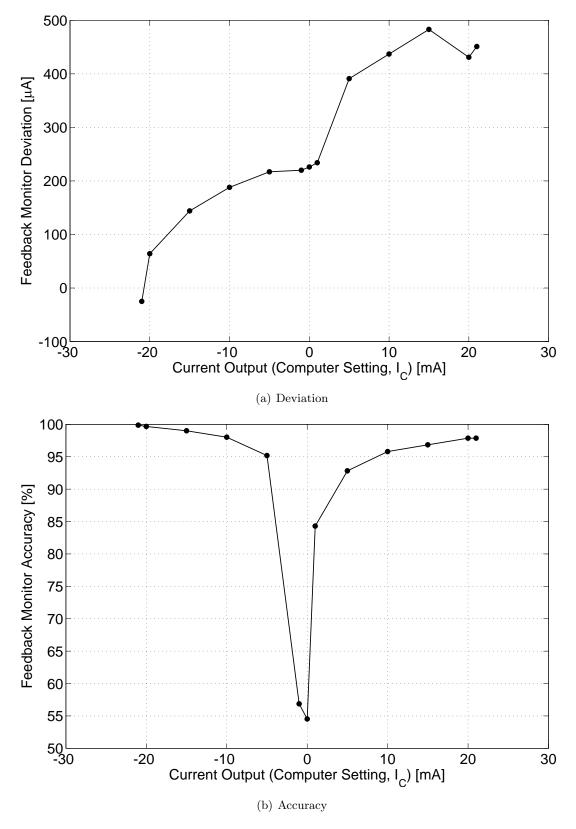

|      | 300 K                                                                                      | 114 |

| 6.7  | The feedback monitor (a) deviation from actual measurement, and (b) accuracy at            |     |

|      | 85 K                                                                                       | 115 |

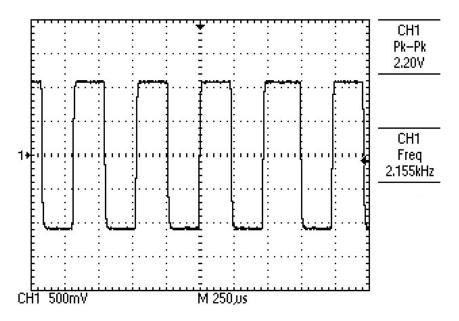

| 6.8  | $\pm 21.6$ mA bit-pattern sent on the current channel                                      | 116 |

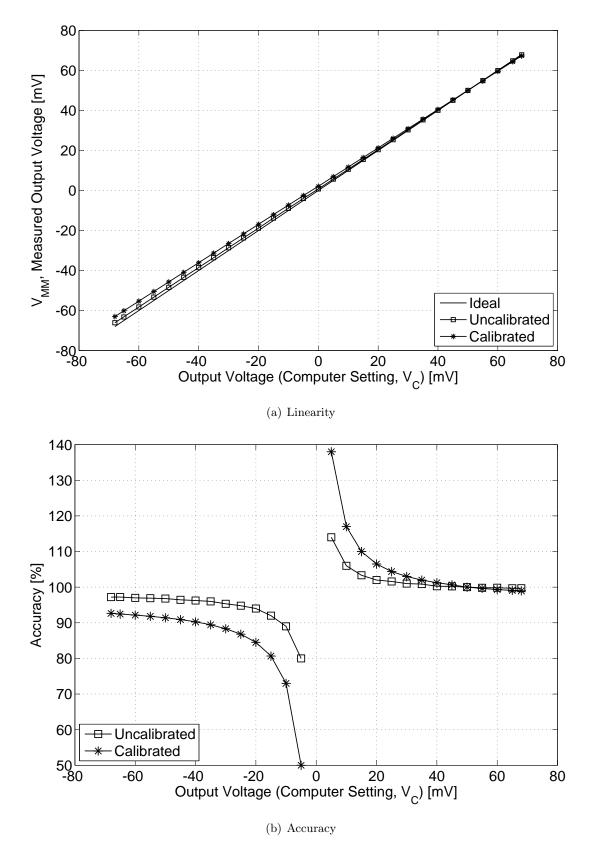

| 6.9  | The (a) linearity and (b) accuracy of the low voltage channel outputs at 300 K             | 118 |

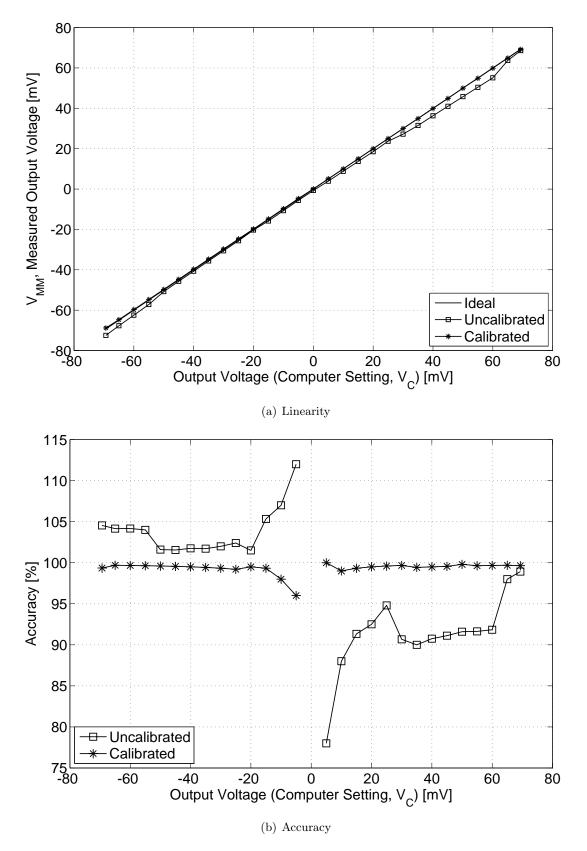

| 6.10 | The (a) linearity and (b) accuracy of the low voltage channel outputs at 85 K              | 119 |

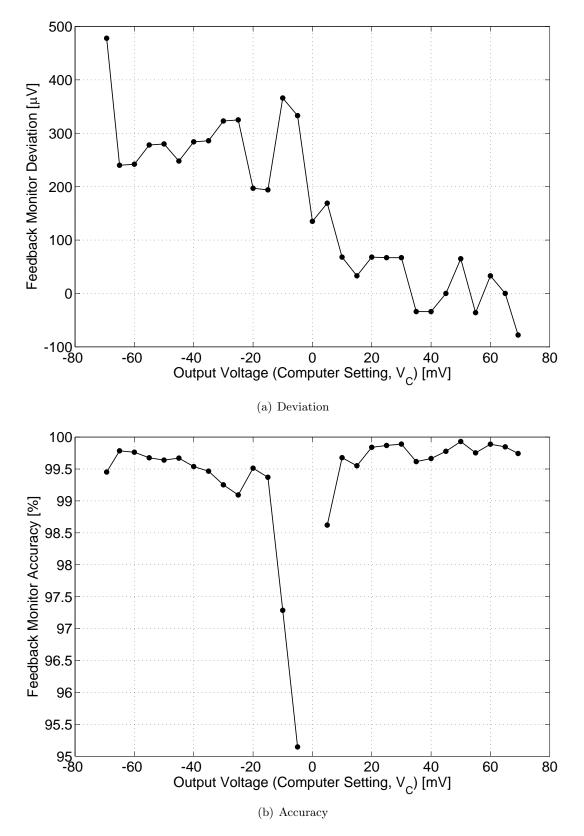

| 6.11 | The (a) deviation and (b) accuracy of the low voltage output feedback monitor at           |     |

|      | 300 K                                                                                      | 121 |

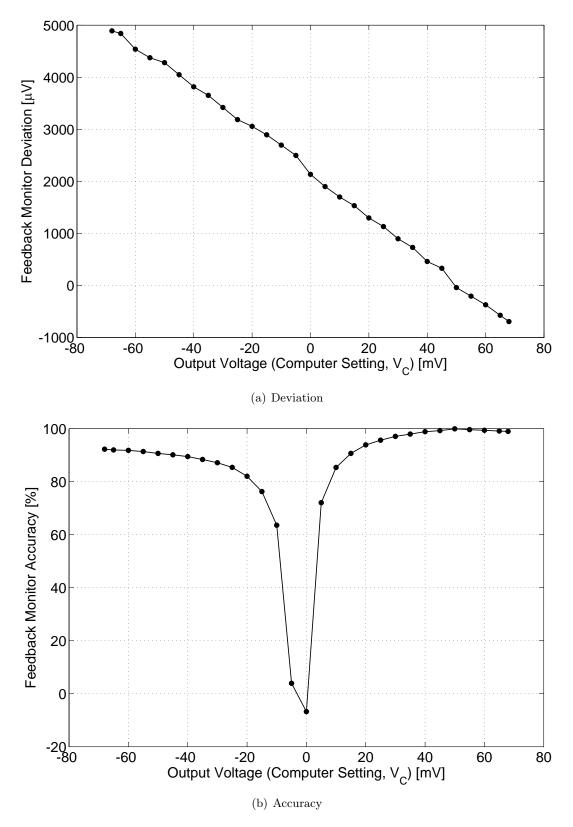

| 6.12 | The (a) deviation and (b) accuracy of the low voltage output feedback monitor at           |     |

|      | 85 K                                                                                       | 122 |

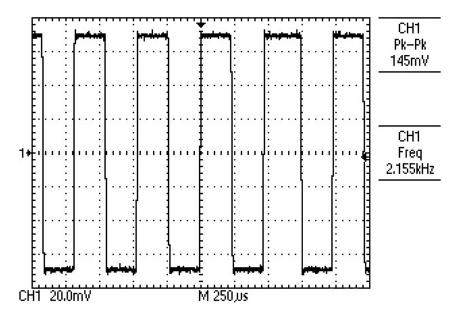

| 6.13 | $\pm 70$ mV bit-pattern on the voltage output channel                                      | 123 |

| 6.14 | Input channel sampling of output channel bit-patterns, with different amplitudes of        |     |

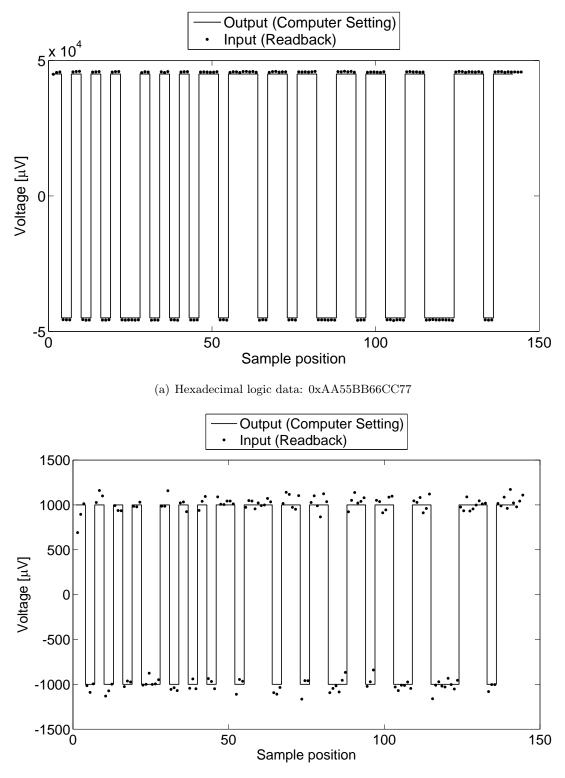

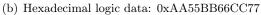

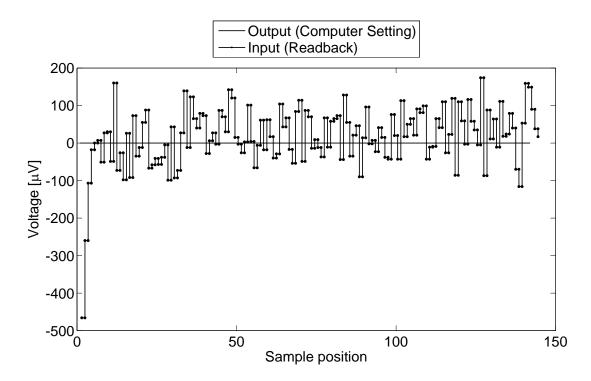

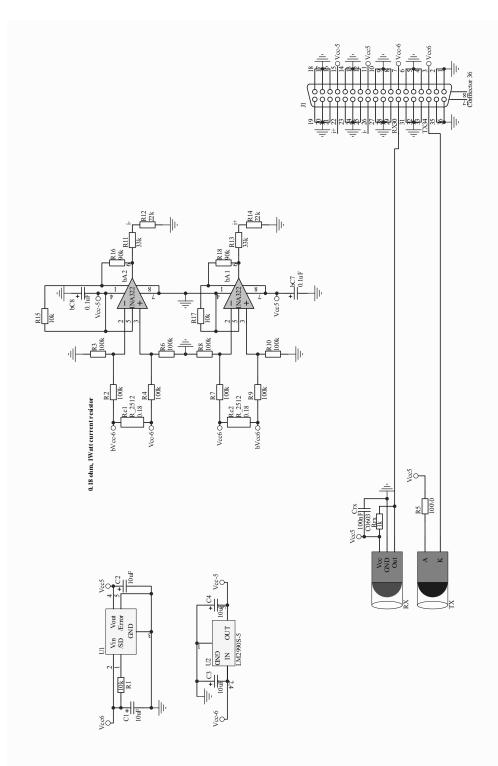

|      | (a) $\pm 45~000~\mu$ V and (b) $\pm 1~000~\mu$ V. Measurements were taken at 300 K         | 125 |

| 6.15 | Grounded <i>input channel</i> measurement at 300 K                                         | 126 |

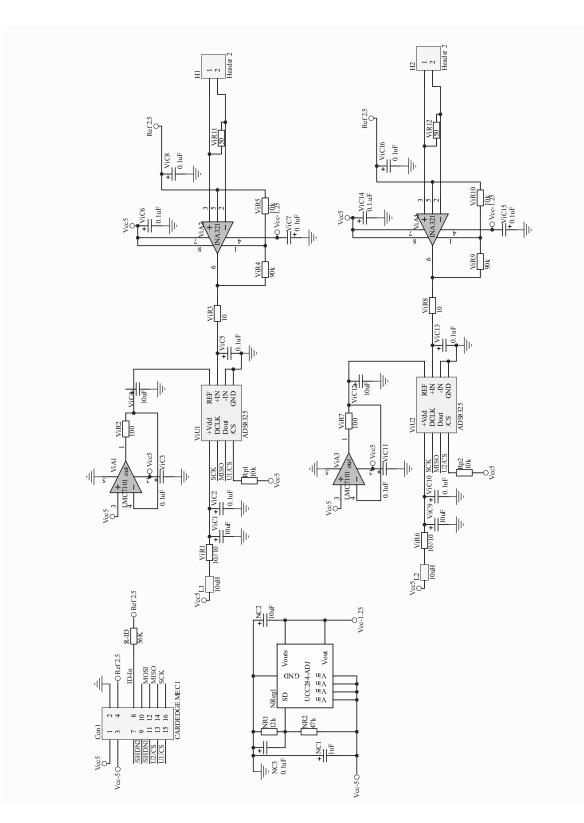

| A.1  | The battery and power PCB schematic, including the current sensing circuits and            |      |

|------|--------------------------------------------------------------------------------------------|------|

|      | the fibre optical USART connections                                                        | A-2  |

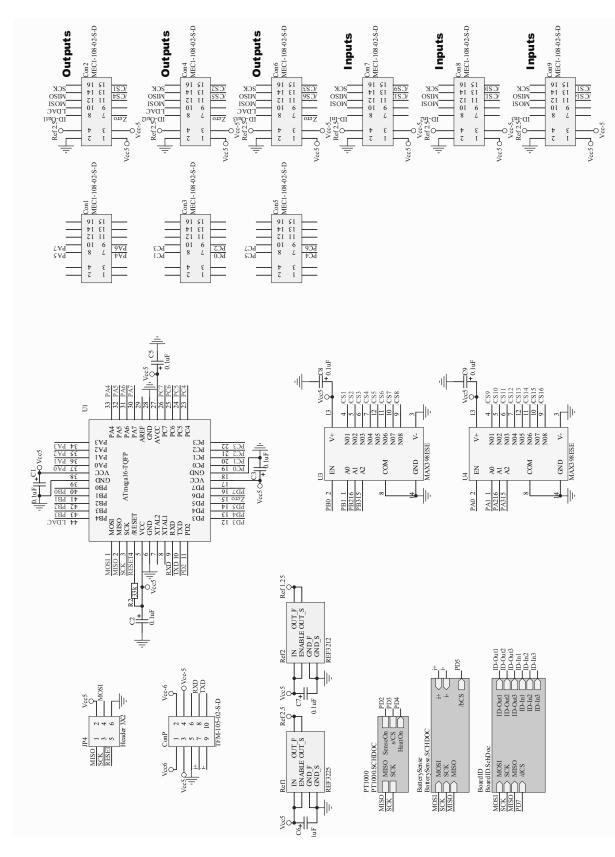

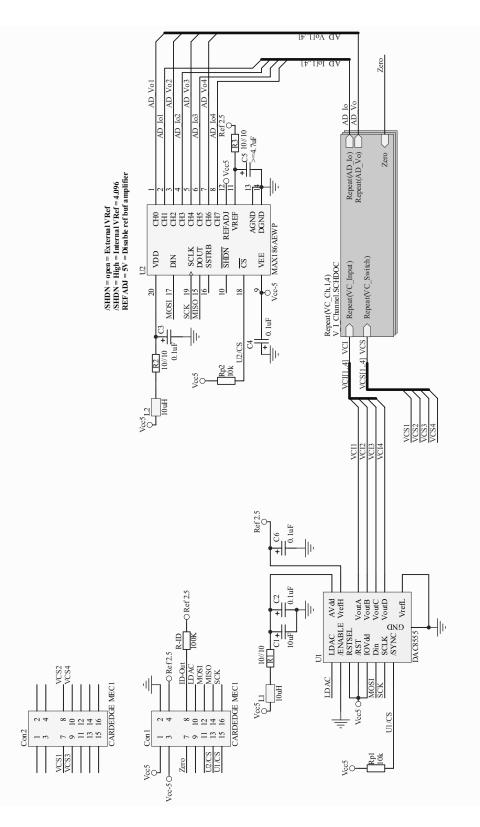

| A.2  | The <i>motherboard</i> PCB schematic, including 3 sub-schematics                           | A–3  |

| A.3  | The (a) BatterySense and (b) BoardID sub-schematics included on the motherboard            |      |

|      | schematic.                                                                                 | A-4  |

| A.4  | The $PT1000$ sub-schematic, included on the <i>motherboard</i> schematic. It also contains |      |

|      | the heater design                                                                          | A-5  |

| A.5  | The (a) high current channel daughterboard and (b) the detail of one high current          |      |

|      | <i>channel.</i>                                                                            | A–6  |

| A.6  | The 4-channel low current and voltage output daughterboard schematic                       | A-7  |

| A.7  | The low current and voltage channel schematic.                                             | A-8  |

| A.8  | The high sensitivity voltage input daughterboard schematic                                 | A–9  |

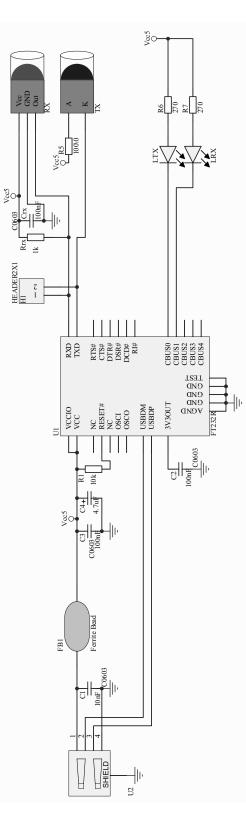

| A.9  | The <i>FTDI USB-RS232</i> fibre optical converter schematic                                | A-10 |

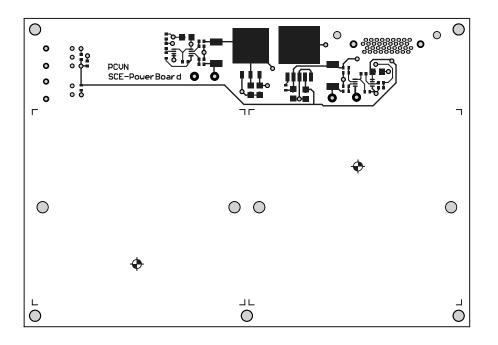

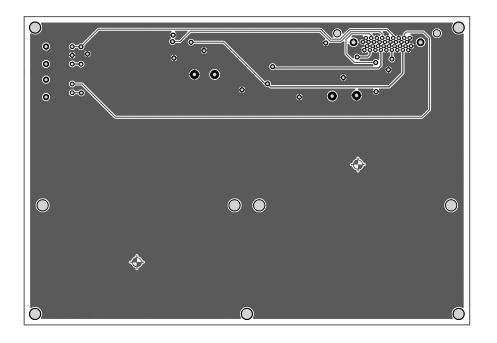

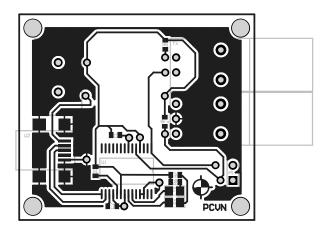

| A.10 | The (a) component side and (b) bottom side of the power board PCB, containing              |      |

|      | the battery holders, regulators, fibre optical converters and current sensing circuitry.   | A-12 |

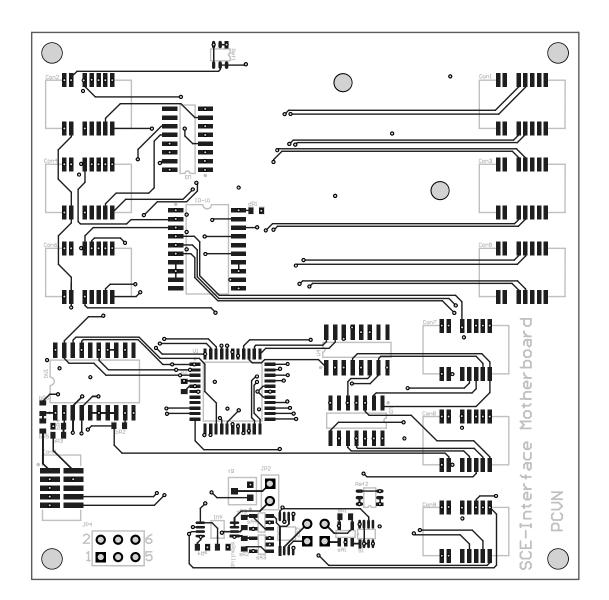

| A.11 | The component side of the <i>motherboard</i> PCB layout                                    | A-13 |

| A.12 | The bottom side of the <i>motherboard</i> PCB layout                                       | A-14 |

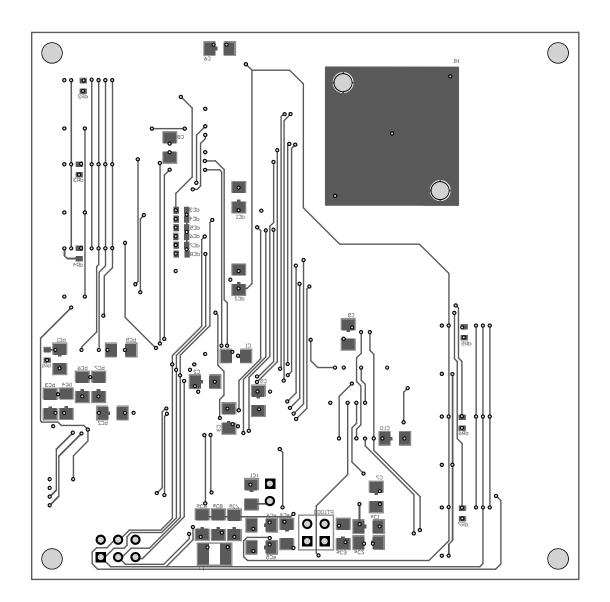

| A.13 | The (a) component side and (b) bottom side of the $high\ current\ daughterboard.$          | A-15 |

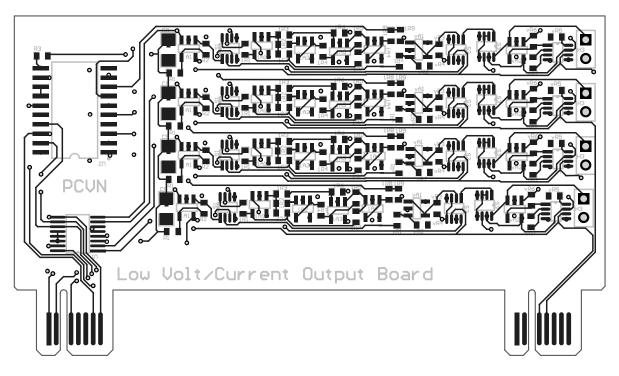

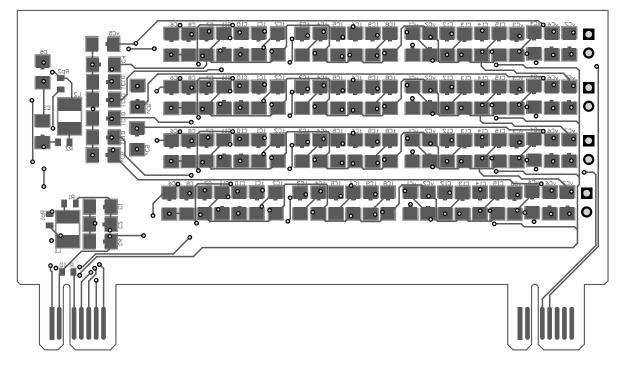

| A.14 | The (a) component side and (b) bottom side of the <i>low current and voltage daugh</i> -   |      |

|      | terboard                                                                                   | A-16 |

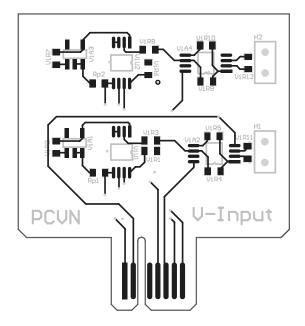

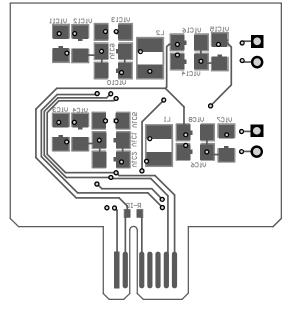

| A.15 | The (a) component side and (b) bottom side of the <i>high sensitivity input voltage</i>    |      |

|      | daughterboard                                                                              | A-17 |

| A.16 | The (a) component side and (b) bottom side of the <i>FTDI USB-RS232</i> fibre optical      |      |

|      | converter                                                                                  | A-18 |

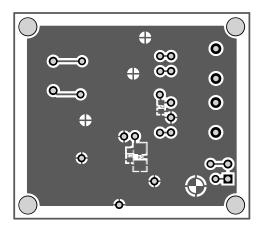

| B.1  | The bottom part of the FTDI USB-RS232 fibre optical converter box, containing              |      |

|      | the PCB in Fig. A.16.                                                                      | B-2  |

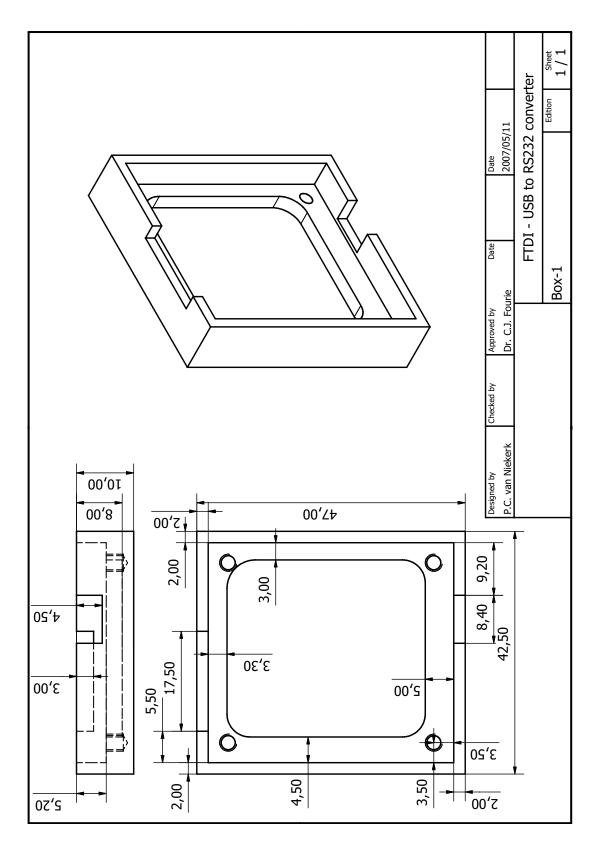

| B.2  | The top part of the <i>FTDI USB-RS232</i> fibre optical converter box                      | B–3  |

| B.3  | The bottom part of the power box, containing the power PCB in Fig. A.10                    |      |

| B.4  | The top part of the power box, containing the power PCB in Fig. A.10                       |      |

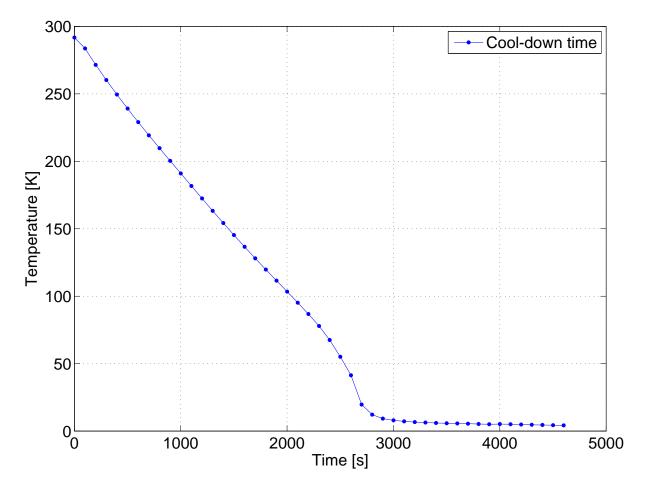

| E.1  | Cool-down time for the Cryomech PT405.                                                     | E-1  |

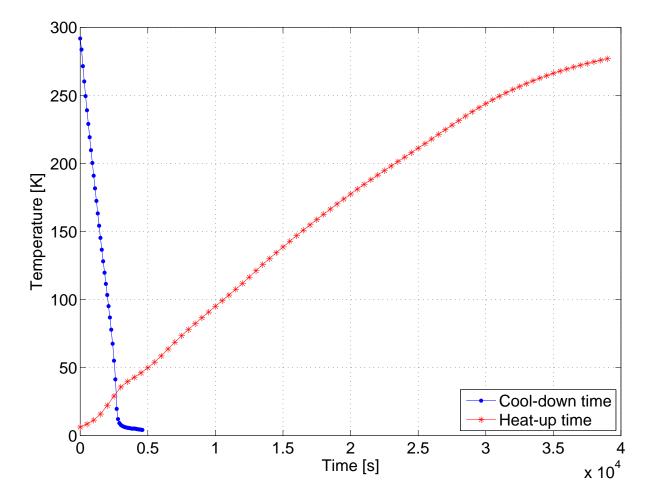

| E.2  | Cool-down and natural heat-up time for the Cryomech PT405.                                 | E-2  |

# List of Tables

| 3.1 | ATtiny selection options                                                           | 15  |

|-----|------------------------------------------------------------------------------------|-----|

| 3.2 | Lower Temperature Limit of Tested Op-amps                                          | 20  |

| 4.1 | Pin connections of the ATmega16 microprocessor                                     | 46  |

| 4.2 | Daughterboard identification table                                                 | 70  |

| 5.1 | Oxford Electronics price quote for fibre optical accessories.                      | 73  |

| 5.2 | VPSTP shielded cable wire usage                                                    | 76  |

| 5.3 | Command-type bit description.                                                      | 86  |

| 5.4 | ATmega16 microcontroller command descriptions and return values                    | 87  |

| 5.5 | Command instruction set protocol.                                                  | 90  |

| 5.6 | The time needed for sending one data bit in a data frame                           | 95  |

| 5.7 | The time needed for sampling one data bit in a data frame                          | 95  |

| 6.1 | The actual measured values of the $R_d$ resistors in a <i>high current channel</i> | 108 |

| 6.2 | Current drawn by the regulators on the battery PCB                                 | 127 |

| 6.3 | Current drawn by the <i>motherboard</i>                                            | 127 |

| 6.4 | Current drawn by the high current daughterboard                                    | 128 |

| 6.5 | Current drawn by the low current and voltage daughterboard                         | 128 |

| 6.6 | Current drawn by the voltage input daughterboard                                   | 128 |

| 6.7 | Current drawn by other devices                                                     | 128 |

| 6.8 | Measured currents of the cryogenic CMOS-based control system                       | 129 |

| D.1 | PT1000 Calibration Values                                                          | D–1 |

| D.2 | PT1000 Calibration Values (continues)                                              | D-2 |

| F.1 | Datasheets                                                                         | F–2 |

# List of Abbreviations

| AC                      | Alternating Current                     |

|-------------------------|-----------------------------------------|

| ADC                     | Analogue to Digital Converter           |

| A/D                     | Analogue to Digital                     |

| BeCu                    | Beryllium Copper                        |

| CDMA                    | Code Division Multiple Access           |

| CMOS                    | Complementary Metal-Oxide Semiconductor |

| COSL                    | Complementary Output Switching Logic    |

| CPU                     | Central Processing Unit                 |

| $/\mathrm{CS}$          | Chip Select Not                         |

| CT                      | Command Type                            |

| DAC                     | Digital to Analogue Converter           |

| $\mathrm{D}/\mathrm{A}$ | Digital to Analogue                     |

| DC                      | Direct Current                          |

| EM                      | Electro Magnetic                        |

| GBW                     | Gain Bandwidth                          |

| GND                     | Ground                                  |

| GUI                     | Graphical User Interface                |

| HF                      | High Frequency                          |

| IC                      | Integrated Circuit                      |

| I/O                     | Input/Output                            |

|                         |                                         |

## LIST OF ABBREVIATIONS

| ISP                  | In-System Programmable                                      |

|----------------------|-------------------------------------------------------------|

| LCD                  | Liquid Crystal Display                                      |

| LED                  | Light Emitting Diode                                        |

| LPF                  | Low Pass Filter                                             |

| LSB                  | Least Significant Bit                                       |

| MOSFET               | Metal Oxide Semiconductor Field Effect Transistor           |

| MSB                  | Most Significant Bit                                        |

| MUX                  | Multiplexer                                                 |

| OCR                  | Output Compare Register                                     |

| Op-amp               | Operational Amplifier                                       |

| PCB                  | Printed Circuit Board                                       |

| $\operatorname{ppm}$ | Parts per million                                           |

| PWM                  | Pulse Width Modulator                                       |

| RF                   | Radio Frequency                                             |

| RSFQ                 | Rapid Single Flux Quantum                                   |

| RX                   | Receive                                                     |

| SCE                  | Superconductor Electronics                                  |

| SIS                  | Superconductor-insulator-superconductor                     |

| SMD                  | Surface Mount Device                                        |

| SMT                  | Surface Mount                                               |

| SO                   | Small Outline                                               |

| SOIC                 | Small Outlined Integrated Circuit                           |

| SQUID                | Superconducting Quantum Interference Device                 |

| /SS                  | Slave Select Not                                            |

| TTL                  | Transistor-Transistor-Logic                                 |

| ТХ                   | Transmit                                                    |

| USART                | Universal Synchronous and Asynchronous Receiver Transmitter |

# List of Symbols

### **Constants:**

| n     | nano, scale constant, 1 x 10 <sup>-9</sup>            |

|-------|-------------------------------------------------------|

| $\mu$ | micro, scale constant, 1 x $10^{\text{-}6}$           |

| m     | milli, scale constant, 1 x $10^{\text{-}3}$           |

| k     | kilo, scale constant, 1 x $10^3$                      |

| М     | mega, scale constant, 1 x $10^6$                      |

| G     | giga, scale constant, 1 x $10^9$                      |

| k     | Boltzmann's constant = $1.38 \ge 10^{-23} \text{J/K}$ |

### Units of Measure:

| А | Ampère |

|---|--------|

|---|--------|

- °C Degrees Celsius

- Hz Hertz

- J Joule

- K Kelvin

- $\Omega \qquad {\rm Ohm}$

- s Seconds

- min Minutes

- V Volt

- W Watt

### Variables:

- $\Delta T$  Temperature difference

- $T_{\rm C} ~~ {\rm Critical ~temperature~of~a~superconductor}$

# Chapter 1

# Introduction

One of the great and important discoveries made in the previous century would be that of superconductivity. This field is rapidly expanding with various new and promising possibilities, especially in the field of electronics.

Superconductivity is generally described as the disappearance of electrical resistance at very low temperatures. This phenomenon happens when certain metals, for instance mercury or compositions such as niobium nitride or Yba<sub>2</sub>Cu<sub>3</sub>O<sub>7</sub> (YBCO), are cooled down to their critical temperatures,  $T_C$ . Due to the low values of  $T_C$ , they are cooled down in cryogenic environments. These environments are usually created by liquid helium cryostats or cryocoolers which produce very low temperatures. Below a temperature of  $T_C$ , the material takes on new electrical properties where the electrical resistance of the specific material drops to zero.

One example of implementing this technology is seen in superconductor Josephson Junctions [1, 2, 3]. These Josephson Junctions are used as building blocks in designing RSFQ logic devices, proposed by Likharev and Semenov [4], for designing sub-terahertz-clock-frequency digital systems. They are also used as building blocks in devices such as the SQUID magnetometer [5].

Other implementations of superconductors can be seen in the SIS mixer [6] for millimetre wavelength astronomy telescopes as well as in the superconducting hot electron bolometer [7] for measuring the energy of electromagnetic radiation.

Promising future applications for superconductor electronics (SCE) are in the telecommunications industry. Here RSFQ logic can be used to reduce interference in CDMA-based systems [8], and thereby allowing more users on the system. Wireless communications also benefit from this technology where RF front-ends [9] are designed with ultra fast superconducting analogue to digital converters (ADCs) [10].

Although the concept of SCE technology holds great potential for the future, it is still difficult to interface. The clock frequencies of SCE circuits can range from 10 GHz to 300 GHz and operate at very low amplitude input and output signals, typically in the lower millivolt range. Noise could easily clutter these signals. Measurement systems therefore need to be as noise free as possible to extract valid data from SCE circuits.

For laboratory tests of SCE circuits, lower frequency inputs and outputs are required. SCE test equipment could be interfaced below 1 kHz, but to speed up bit-error rate measurements, test frequencies of around 100 kHz would be ideal. Test signals at much higher frequencies, carrying higher frequency noise, could easily interfere with the very sensitive RSFQ devices.

This thesis focuses on building a device for interfacing and testing SCE circuits, such as RSFQ [11] and COSL [12, 13, 14] devices.

A brief discussion of the following chapters are given below:

- Chapter 2 gives a background overview of why a cryogenic CMOS-based control system is needed, along with a specification list for designing such a system.

- Chapter 3 shows initial designs that explore three possibilities for designing a control system that would work at 70 K.

- Chapter 4 shows a detailed design for each subsystem that is implemented in the control system.

- Chapter 5 shows how all the subsystem building blocks fit together when implementing the control system. It also shows how the software was developed and implemented to control the system.

- In Chapter 6 results of various tests are given for evaluating the operation of the control system.

- Chapter 7 concludes this thesis, where recommendations are made and future prospects are discussed.

The appendix contains additional design information as well as developed software code. A calibration table for the calibrated PT1000 temperature sensor is shown and datasheet references are also given.

# Chapter 2

# **Background and Specifications**

As mentioned in Chapter 1, SCE technology holds great potential for the future, but critical research still needs to be done on this technology. Although expensive devices [15], such as Octopux [16] have been built for testing superconductive devices, this research attempts to design a simpler, cost effective interface for SCE devices. Octopux, designed at the State University of New York (SUNY), is also relatively slow, interfacing at approximately 1 kHz.

The necessity for designing a *cryogenic CMOS-based control system* will become clear when considering the meaning of the three separate terms.

## 2.1 Cryogenic Environments

Cryogenic is understood as producing very low temperatures such as those required for natural gas liquefaction.

Operating conditions for RSFQ and COSL families are not very favourable for normal semiconductors. They usually operate inside vacuumed cryocoolers or liquid helium cryostats at very low temperatures. Niobium based RSFQ and COSL families operate at 4.2 K or below [11, 17].

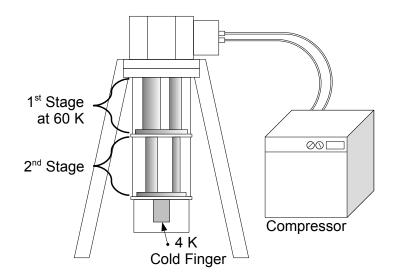

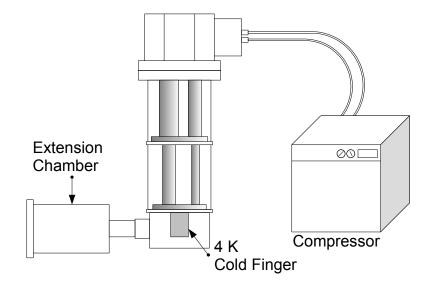

At the University of Stellenbosch a *Cryomech PT405* cryocooler is used for testing SCE devices. This is a two-stage, 4 K cryocooler where the first stage reaches a temperature slightly less than 60 K. Unless otherwise noted, this cryocooler was used in this thesis for experiments and tests in cryogenic environments. A representation of such a cryocooler is given in Fig. 2.1.

Figure 2.1: A two-stage, 4 K cryocooler.

A typical two-stage cryocooler delivers 0.5 W of cooling power at 4 K which must sustain this temperature against electric power dissipation, thermal radiation losses, poorly vacuumed space and heat transferring cables [18]. Multiple thermal shields and a good vacuum (10<sup>-5</sup> atmosphere), significantly reduce heating, but the heat flow through cabling from the outside of the cryocooler still injects heat into the system.

The idea was proposed to test normal semiconductor electronic devices in the 1<sup>st</sup> stage of the cryocooler to see whether it is possible to implement a control system in this 60 K environment for interfacing SCE devices. The design also needs to be compact in order to fit into the very confined space of the 1<sup>st</sup> stage of the cryocooler.

The reason for lowering the operating temperature of the control system is to minimize the heat-load on the SCE devices. If the electronics of the control system is outside the cryocooler, the heat-load on the SCE circuits would be great because of the large temperature difference  $(\Delta T)$  of 300 K between the outside and the inside of the cryocooler.

On the other hand, if the control system could be implemented inside the 1<sup>st</sup> stage of the cryocooler, thereby cooling down the semiconductor electronics, the heat-load on the SCE circuits would be significantly less, as the  $\Delta T$  would minimize to approximately 55 K.

Cooling down the semiconductor electronics would also have another beneficial effect. Internal noise on a system is generated by various sources with thermal noise being one of these sources. A theorem by Nyquist, in Appendix A of [19], states that the mean-square noise voltage appearing across the terminals of a resistor of R ohms at temperature T Kelvin in a frequency band B hertz is given by

$$v_{rms}^2 = 4kTRBV^2, \tag{2.1}$$

where k = Boltzmann's constant, relating temperature to energy.

Thus, when temperature is reduced, the noise will also be reduced thereby creating a more sensitive measurement system.

## 2.2 CMOS Technology

Complementary metal-oxide-semiconductors (CMOS) are used in developing various semiconductor electronic devices. CMOS devices are developed with p-type and n-type MOSFETs for logic functioning.

One of the objectives of this thesis is to develop a system that can operate in cryogenic environments with great stability and integrity. CMOS technology has very low power dissipation and very high noise immunity, making it ideal for the given task of cryogenic operation.

Datasheets of manufactured semiconductor electronic devices usually specify that the absolute maximum rating for the operating temperature is between -55 °C (218 K) and 125 °C (398 K). This is mainly because these devices are not tested and are not required to operate outside of these specifications. Various reports [20, 21, 22, 23] however indicate that CMOS technology can operate at very low temperatures. Several tests on CMOS components in cryogenic environments proved that CMOS technology has great potential for operation in very low temperatures.

Although there are different processes of developing different kind of CMOS devices, datasheets do not indicate which CMOS technology processes were used in the development of these devices. Therefore, in this thesis, off-the-shelf CMOS components were ordered and tested to implement in the control system.

### 2.3 Control System

SCE circuits operate at very low input and output amplitudes in the order of micro to millivolts. The difference between a logical '0' and '1' could typically be as low as 150  $\mu$ V in RSFQ-to-DC converted outputs. It becomes difficult to distinguish the signals in this range from electrical noise. In order to minimize noise from external power supply sources, batteries should be used as independent power supplies for the control system. Regularly used bench power supply sources, used for driving normal semiconductor electronics, add HF noise to signals and should therefore be avoided.

A system needs to be developed to easily and accurately test SCE devices. A user should be able to manipulate data signals from a user interface on a computer and send this data signals to a SCE device. As signals are sent, data also needs to be sampled from the SCE outputs and graphically displayed on the computer for the user to interpret.

Therefore a software interface module needs to be developed to accommodate the designed hardware, combining them to form a control system to interface and test cutting edge SCE technology for research purposes.

## 2.4 Guidelines and Specifications

A complete USB-compatible hardware system with several input and output channels should be designed with the necessary amplification stages. Accompanying the hardware, a complete software package should be developed to enable a user to control a cryogenic SCE experiment.

In order to control SCE circuits, output channels should contain programmable current and voltage sources, implemented by DACs and analogue electronics. ADCs should also be implemented as part of the input channels to sample data from SCE circuits. An on-board microprocessor could be implemented to act as the system CPU and control the data signals to and from the SCE devices as well as the communication to and from the computer. The user should also be able to calibrate these channels.

Noise levels need to be kept to a minimum, therefore very low noise components should be implemented to ensure very high signal quality. In order to shield the control system from external HF noise, the necessary aluminium container packages could be designed to fit the designed electronic PCBs.

As discussed in Section 2.1, it would be ideal if the control system could be designed to operate in cryogenic environments with temperatures as low as 70 K.

A more detailed specification list is given below for the hardware design of such a control system:

- Adjustable positive and negative high current output channels between  $\pm 500$  mA.

- Adjustable bipolar low current output channels between  $\pm 25\ 000\ \mu\text{A}$  for sending DC or logic signals with step sizes of 1  $\mu\text{A}$ .

- Adjustable bipolar low voltage output channels between  $\pm 65~000~\mu$ V for sending DC or logic signals with step sizes of 2  $\mu$ V.

- High sensitivity bipolar voltage input channels between  $\pm 50\ 000\ \mu\text{V}$  with a sensitivity of  $2\ \mu\text{V}$ .

- A computer interface via a USB port.

- Fibre optical communication connection to reduce external noise.

- Components cryogenically specified for operation at 70 K.

- Temperature read-out and on-board heater for temperature control around 70 K.

- Operation from battery pack to reduce external noise.

- Battery voltage & current sensing.

# Chapter 3

# Proposed Control System Configurations

Due to the extreme environment, and the lack of data for devices at cryogenic temperatures, several prototypes were built and tested.

In this chapter more than one design approach is considered and discussed. Each proposed design, with implementation and evaluation, will progress to the subsystems that will eventually be implemented in the final design. As the design concepts improve and evolve, new ideas force some of the specifications to slightly bend in a different direction, but brings with it a more refined specification list.

The complete design of subsystems for the final implemented control system will be discussed in Chapter 4.

## 3.1 Computer Interface and Communications

A quick and easily connectable interface always simplifies the usability of a design. The USB standard has become the most popular connectivity feature of the modern computer. For universal connectivity, a USB connectible interface has been designed.

### 3.1.1 USB Interface

In order to create the USB interface, a USB to RS232 converter has been implemented. The RS232 serial communication system is a widely used protocol for most data transferring devices, including the ATmega16 microcontroller, which is implemented and discussed in Section 4.5. This serial protocol is also easy to implement in the software programming of the design.

The FT232BM is a USB-USART device from *FTDI Ltd.*, which was chosen for the USB to RS232 conversion. It complies with the USB standard by interpreting the USB protocol and converting the signal to the well-known serial protocols such as RS232, RS422 or RS485. The USART concept is described in Section 3.1.2.

By installing the FTDI device on the USB port, the computer recognises it as an additional COM port. The user can then implement this port exactly as per normal COM port methodology and can programme the software accordingly.

Data can then easily be sent over this communication line with maximum speeds of up to 1 Megabaud (RS232) or 3 Megabaud (RS422/RS485), depending on the clock speed and setup of the communicated device.

An USB-RS232 converter has been designed on a small PCB, implemented with the FT232BM device. This board was used for testing the proposed configurations described in this chapter. It is quite easily implemented with a few additional components and is powered by the 5 V single supply rail of the USB connection.

The additional components that are required to implement the FT232BM device consists of an external 6 MHz crystal, an EEPROM memory device, some resistors and capacitors and a ferrite bead. Two optional LEDs can also be connected to assigned pins on the FTDI device to indicate when data is transmitted and received.

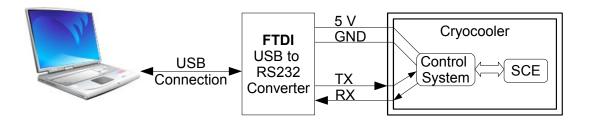

Figure 3.1: FTDI system implementation for first generation tests.

Fig. 3.1 shows the conceptual implementation of the FTDI interface that was used for communication with the control system in the cryocooler. The 5 V power is directly supplied by the USB port and can deliver up to 500 mA of current. This was used to deliver power to the prototype boards of the control system.

With this interface design, conceptual prototyping of a control system could be done, but it was found that external noise could also be coupled onto the system through the direct 5 V line as well as through the direct copper TX and RX lines. A better design, which provided more shielding, was required.

The single rail 5 V supply from the USB was inadequate for driving the *high current channels* of the design and a double rail power supply was also required for most of the operational amplifiers in the later designs.

The power supply was thus implemented by using batteries, shielded in a metal box, placed just outside the cryocooler. It was placed outside because the vacuum inside the cryocooler could cause the batteries to outgas. Outgassing happens when embedded gasses in a solid material is removed by the reduction of pressure. Fibre optical cable provided a solution for shielding the data transfers. If data could be transferred into the cryocooler by means of fibre optical cable, then the control system would be completely shielded from any outside electrical noise sources.

Another advantage of using fibre optical cable is that it also prevents thermal conduction. It does not transfer heat as copper wires would. It reduces the heat transfer from the outside of the cryocooler to the control system at 70 K.

In Fig. 3.2, this more advanced conceptual design is illustrated. Data is sent from the computer via the USB connection, transformed to the RS232 UART protocol and then immediately converted to light signals travelling on the fibre optical cables. The data is then reconverted to electrical pulses on the inside of the cryocooler.

Figure 3.2: Fibre optical FTDI implementation for computer interface.

A more advanced USB-USART converter board has been built for the final design, using the newer FT232R device. The advanced board design is described in more detail in Section 4.2.

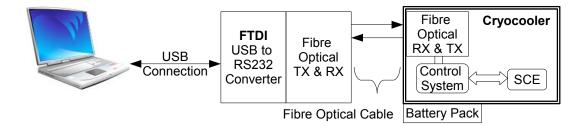

#### 3.1.2 USART

By using the USB-RS232 COM port described in Section 3.1.1, the Universal Synchronous and Asynchronous serial Receiver and Transmitter (USART) communication system is used in communicating with the cryogenic control system. The asynchronous mode of the USART is used throughout this thesis. This means that no data is sent when the transmitting device has nothing to send, thereby reducing communication traffic.

The USART system operates with two data wires, one to send or transmit data and the other to receive data. In asynchronous mode, a transfer is started by sending a *start* bit, followed by five to eight data bits, an optional parity bit and a *stop* bit. These settings as well as the transfer speed are pre-configured, so that both devices know how and at what speed to interpret the received signal.

Figure 3.3: A UART serial transmission of two bytes.

Fig. 3.3 shows a typical transmission of two bytes, both having a *start* and *stop* bit, without the parity bit. With each *start* bit, the transmission is synchronized.

According to the pre-configured transfer speed, the receiving device will interpret each bit precisely halfway through the period assigned for each bit position to determine if the bit is a '1' or a '0'. If one of the clock frequencies of either the receiver or transmitter has an error of up to  $\pm 2\%$  [24], the data will still be transmitted correctly, because each byte is synchronized with each *start* bit.

### 3.1.3 SPI Communication

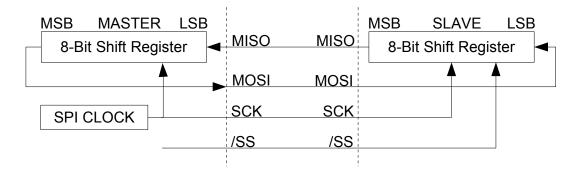

The serial peripheral interface (SPI) is a protocol that uses three wires for high-speed synchronous data transfer between devices such as microcontrollers and ADCs. The three wires on the SPI bus are SCK, MOSI and MISO respectively, which will be clarified in this section. There is usually one master device with the possibility of one or more slave devices that are addressed.

A fourth wire is usually needed as a *slave select not* (/SS) or *chip select not* (/CS) control line to ensure communication with the correct device. This /SS line must be selected and pulled down to a logic low before communication can begin. An unlimited amount of devices can thus be connected to the SPI bus as long as each slave device has its own /SS line.

The master sends data to the slave device on the MOSI (Master Out Slave In) line, while at the same time data bits are transferred from the slave to the master on the MISO (Master In Slave Out) line.

Figure 3.4: SPI master-slave interconnection.

As seen in Fig. 3.4, each device has its own 8-bit shift register. With each clock pulse on the SCK line, initiated by the master device, an exchange transaction is being done. Each device shifts out the most significant bit (MSB). This MSB is received by the other device and is saved in the least significant bit (LSB) position of the 8-bit shift register. After every 8-bit exchange, a new byte can be transmitted on the SPI bus.

It should be noted that the master device can be configured to start the SCK either on a logic high or a logic low. It can also be configured to transfer data either on the first or second edge of the clock. This all depends on how the slave device was built to operate, and therefore necessitates a careful design with the proper SPI configurations, done in software, for SPI communication.

## 3.2 Microchip PIC Control System

The first step towards designing a cryogenic control system was to test various CMOS devices inside the cryocooler to see what kind of technology would work in cryogenic environments.

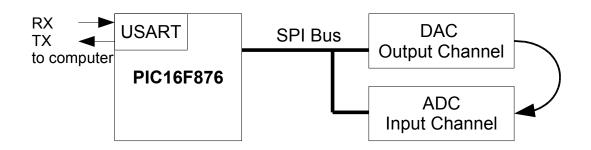

The aim was to find a microprocessor to function as the system CPU, where data can be sent for interpretation and then redirected to specific output channels. These output channels would contain DACs to submit analogue data to SCE circuits. The data sent to the CPU would come from a personal computer by means of the interface described in Section 3.1.

The CPU would then also contain ADCs as input channels for reading in data from the SCE devices and then send each channel's data back to the computer for interpretation.

### 3.2.1 Component Choices

The PIC16F876A microprocessor from Microchip was used in previous designs and seemed to be a good candidate for cryogenic tests. It is specified as a 8-bit CMOS FLASH Microcontroller, thus some CMOS technology is definitely implemented in this device. The DIP package type was used.

The ADS7807U is a low-power ADC with 16-bit sampling capability using state-of-the-art CMOS structures. The only drawback is that this device is rather large because of the 28-pin SO package, containing only one sampling channel. Nevertheless, this device was chosen and tested.

For the DAC, the TLV5618A low power, 12-bit converter was chosen. This device is small with a 8-pin SOIC package and is also implemented with a CMOS process.

#### 3.2.2 Initial Cryogenic Test Setup

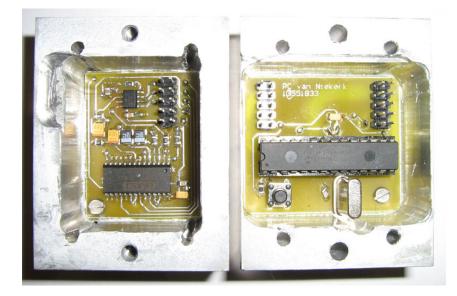

A test setup was created by cooling down the PIC, DAC and ADC inside a 4-Kelvin, 2-stage *Gifford McMahon* cryocooler. An aluminium box was designed, as seen in Fig. 3.5, to contain the two PCB parts, with the PIC on one board and the DAC and ADC on another. They were

interconnected by a SPI bus. The pins of the DIP package of the PIC was soldered to the socket to ensure connectivity even at low temperatures.

The clock frequency of the PIC was produced by an external 11.0592 MHz crystal.

Figure 3.5: Test boards and aluminium boxes for the DAC and ADC (left) and the PIC16F876A (right).

The two parts of the box fit together to form a cube, where the metal provides shielding as well as heat transference away from the PCBs, as the electronic ground underneath the PCB is connected to the metal box.

A thermocouple was placed in a small hole on the outside of the metal box, with some heat sink thermal paste, to measure the temperature while the system cooled down. The *Dow Corning 340* heat sink compound was used on all thermal connection points for better heat transference. This compound does not have any oily substances or gasses and stays in a paste form at vacuumed cryogenic temperatures. Therefore this compound is preferred for the use in cryogenic environments above any normal heat sink compounds.

One of the PIC timers was programmed to interrupt and send data to the DAC, on the SPI bus protocol, to output a unity voltage. As seen in Fig. 3.6, this voltage was then immediately redirected back to the ADC and sampled.

Figure 3.6: An illustration of the PIC test setup.

In turn, the SPI bus was used again by the PIC to read out the sampled voltage from the ADC to continuously send it back to the computer.

### 3.2.3 Results

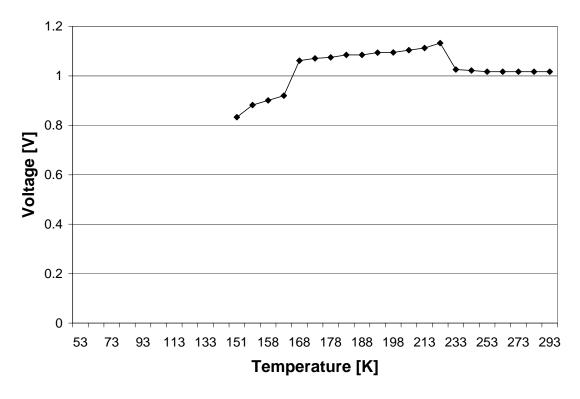

Data from the ADC were recorded according to the temperature decrease and shown in Fig. 3.7. Here it can be seen that the ADC is quite stable as the temperature lowers to about 220 K, where it suddenly measured a higher voltage. Then at 160 K, the ADC measurement drops very steep and continues to drop down as the temperature lowers to 150 K.

Figure 3.7: The ADS7807U ADC results while sampling 1 volt in cryogenic temperatures.

At this stage, the PIC microprocessor stopped functioning, failing to continuously transmit the ADC values. This could be observed by the non-responsive TX and RX LEDs on the FTDI interface that stopped blinking. Blinking of LEDs indicate that data is being transmitted and received and that the PIC is still active.

As the temperature was increased gradually, the PIC only started functioning again at a temperature of 198 K. The reason for this is that the temperature measured by the thermocouple on the outside of the metal box did not reflect the true temperature of the inside of the electronics. A temperature hysteresis could be observed.

This configuration was cooled down more than once with the same results for each test.

#### 3.2.4 Conclusion

Upon closer inspection of the PIC data pages, it was observed that only the FLASH and EEP-ROM memories were implemented with CMOS technology and that the rest of the PIC, such as the inputs and outputs were implemented with TTL technology.

From these results it can be concluded that the PIC16F876A is not suitable for cryogenic operation. A new device was thus required.

Measured results have shown that the ADC showed a nonlinear response with temperature drop. The package type also proved too big for implementing more than one channel in a confined space such as in the cryocooler. Either a smaller single channel device or a multi-channel device is required and therefore the ADS7807U is not used further in this research.

Although the DAC worked fine, a higher resolution DAC is required. A 16-bit DAC would be ideal for real fine adjustments. Therefore the TLV5618A will not be used in the further design of the control system.

Positive results from this experiment were the verification of the SPI interface and the FTDI USB-RS232 computer interface, which were used in the experiments to follow.

### 3.3 ATMEL PWM Subsystems

In order to improve the design, the ATMEL AVR microcontrollers were considered. The AVR family devices are CMOS 8-bit microprocessors, based on the advanced RISC architecture.

Some of these devices have on-board pulse width modulators (PWM) which could be used for creating sine waves to send data to SCE devices.

A discussion of the component choices is given, followed by an overview of how the on-board PWM works. The ATMEL AVR devices as well as analogue components were tested in the cryocooler and the results are shown here. This is followed by a prototype control system design that was built and tested, where PWM signals were implemented. It is then concluded with a discussion of the results of the control system design.

#### 3.3.1 Component Choices

The ATMEL AVR family has three basic groups of devices. They are the tinyAVR, megaAVR and more application specific AVRs such as LCD and USB controllers.

The tinyAVRs are more general purpose microprocessors with up to 8 kB of Flash program memory and 128 bytes of SRAM and EEPROM with limited peripherals.

The megaAVRs are more powerful with up to 256 kB of Flash program memory, 4 kB EEPROM and SRAM with an extensive peripheral set. Peripherals includes SPI and USART communication, PWMs and on-board ADCs and DACs.

| Devices    | USART [Qty] | SPI [Qty] | PWM [Qty] | 10-Bit ADCs [Qty] | RAM [Bytes] |

|------------|-------------|-----------|-----------|-------------------|-------------|

| ATtiny13   | 0           | 0         | 2         | 4                 | 64          |

| ATtiny26   | 0           | 1         | 2         | 11                | 128         |

| ATtiny2313 | 1           | 0         | 4         | 0                 | 128         |

Table 3.1: ATtiny selection options.

Table 3.1 shows some ATtiny selection options. The ATtiny26 device was chosen because of the SPI functionality so that in-system programming could be done.

Two devices were considered for implementation of a system CPU for the control system. The one is the AT90USB128 device which offers a new USB 2.0 full-speed interface where greater transfer speeds could be attained. It later became clear that the computer side software programming, to connect with this device, was too complex and required expensive software packages to implement completely. Since a USB interface was already implemented by the FTDI device, the AT90USB128 was obsolete. A separate new project, apart from this thesis, was created to specifically implement the USB 2.0 full-speed interface and to report [25] on how it is to be implemented.

The other CPU option was the ATmega16 device. It was chosen because it has both SPI and USART communication ports, 32 I/O pins and can operate at an internal clock speed of up to 8 MHz. This device is described in more detail in Section 4.5.

#### 3.3.2 Pulse Width Modulation

Pulse Width Modulation (PWM) is the creation of a square wave at a certain frequency, where the duty cycle can be changed to control the amount of power it produces. By changing or modulating the duty cycle, the average power of the signal is also changed. If the duty cycle is increased, meaning that the signal is high for longer than it is low, the average power will also be increased.

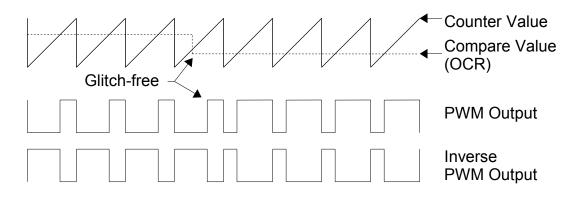

ATMEL AVR devices come standard with a feature to create an 8-bit PWM signal by toggling an I/O pin between a logic low, '0', and high, '1'. It is implemented with an 8-bit counter/timer and an 8-bit output compare register (OCR). This OCR contains a value that is compared by the counter as shown in Fig. 3.8. This device also has a glitch-free transition if the OCR value is changed while in operation.

Figure 3.8: PWM example of an ATMEL AVR device.

The output of the I/O pin is low until the counter reaches the compared value, stored in the OCR. It then switches the I/O pin to high and keeps it high until the counter overflows and restarts the counting. The ATtiny26 device also has an inverse of this I/O pin, where the pin is kept high until the counter reaches the OCR value. It then switches the I/O pin value low and keep it low for the remainder of the period. When the counter overflows, the output of the I/O pins are reset and the process is started again.

Using this concept, a DAC can thus be implemented by filtering the PWM output with a low pass filter (LPF), consequently averaging the output. Likewise, a sine wave can be generated if the duty cycle is varied according to a sine wave formation, by changing the OCR value on each counter reset. An actual sine wave can then be extracted by this varying PWM signal if it is filtered by a LPF. The cut-off frequency of the LPF should be higher than that of the produced sine wave but lower than the 8-bit counter timer frequency of the square wave.

The PWM square wave frequency can be varied, but in this design it was set to the device's maximum of 250 kHz on the full 8-bit counter value. The sine wave frequency then depends on how many data points are used to create it. If only 10 data points are used and the OCR is changed on every counter reset, the sine wave frequency would then be 25 kHz. If more data points are used, the sine wave frequency would decrease but will result in a smoother signal output.

#### 3.3.3 Cryogenic Tests

Before any system designs could continue, some cryogenic tests needed to be done. In this section ATMEL AVR devices, op-amps as well as some analogue components were tested in cryogenic environments to see what components could be used.

#### 3.3.3.1 ATMEL AVR

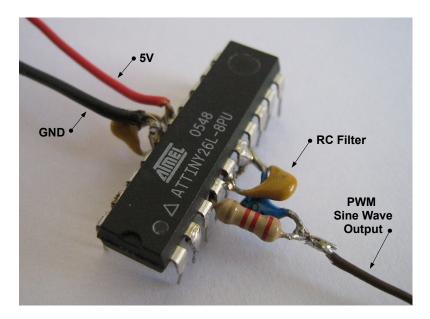

An ATtiny26 DIP package was programmed in AVR Studio 4 in assembler language. It was programmed to use the on-board PWM to create a sine wave form, from a pre-calculated sine wave lookup table. The assembler code for this implementation can be found in Appendix C.1.

The device can be programmed to operate from an external crystal, with a maximum value of up to 16 MHz or an internal RC clock with a maximum value of up to 8 MHz. For this experiment the internal clock of the ATtiny26 was programmed for operation at 8 MHz.

This PWM signal was then filtered by a 1<sup>st</sup> order RC low pass filter (LPF) to obtain a sine wave. The cut-off frequency was calculated by choosing the RC values as in Eq. 3.2.

$$f = \frac{1}{2\pi RC} \tag{3.1}$$

$$= \frac{1}{2\pi (2.2 \times 10^3)(2.7 \times 10^{-9})}$$

(3.2)

= 26.8 kHz

The sine wave had an amplitude of just less than 5 V with a DC offset of 2.5 V. No PCB was designed for this test. As seen in Fig. 3.9, the LPF was implemented by soldering a ceramic capacitor and a carbon resistor directly onto the pins of the microcontroller.

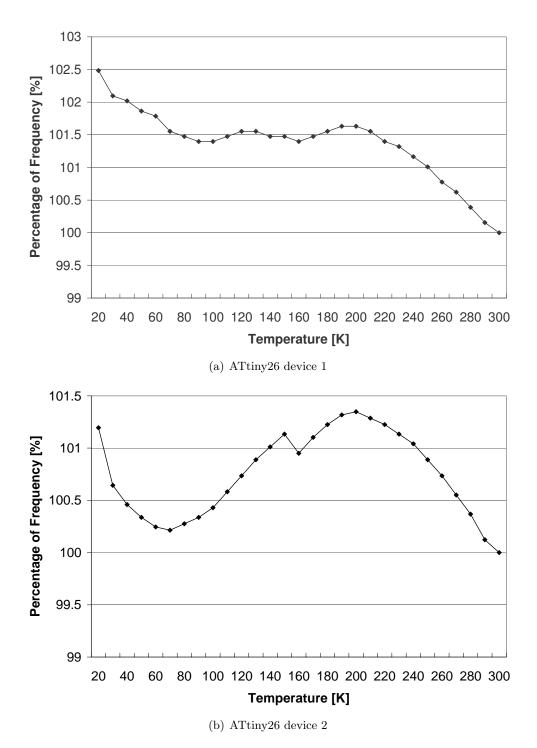

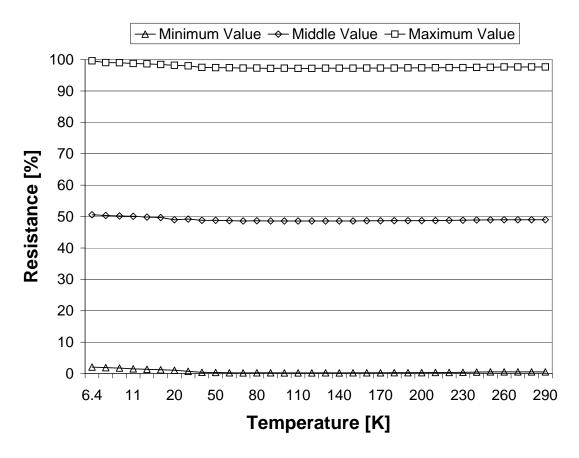

Figure 3.9: The ATtiny26 PWM connection wires for tests in the cryocooler.

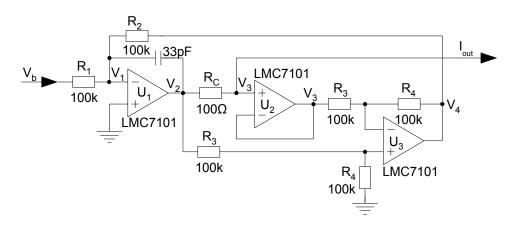

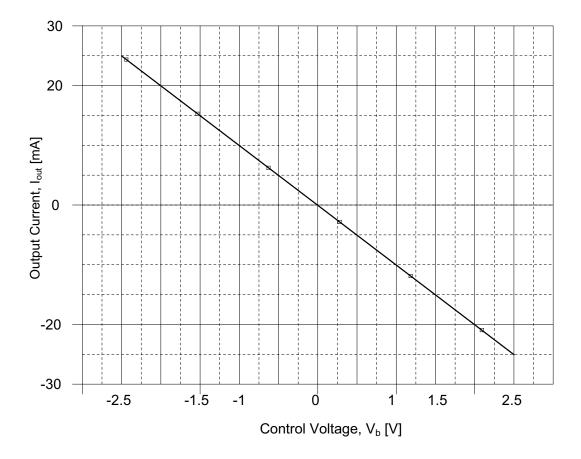

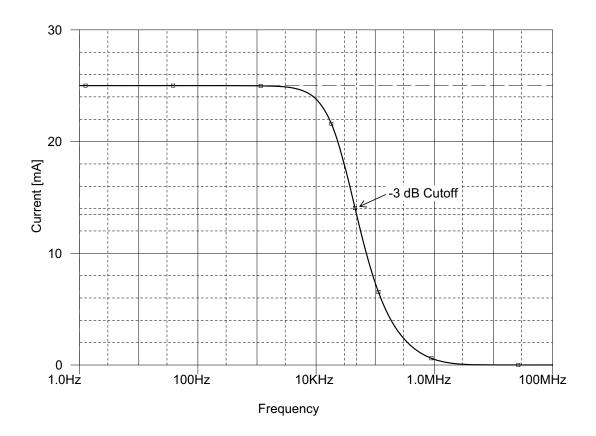

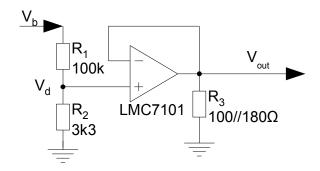

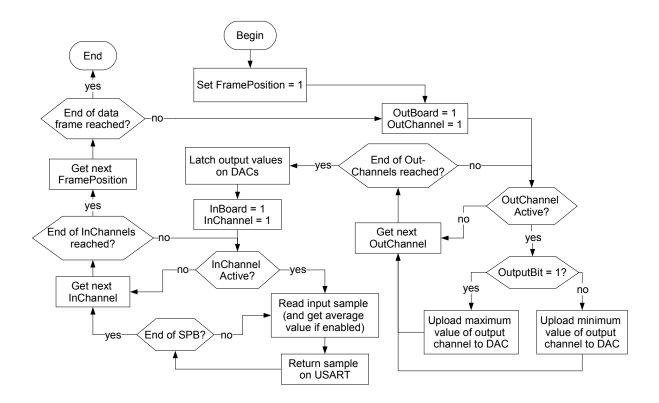

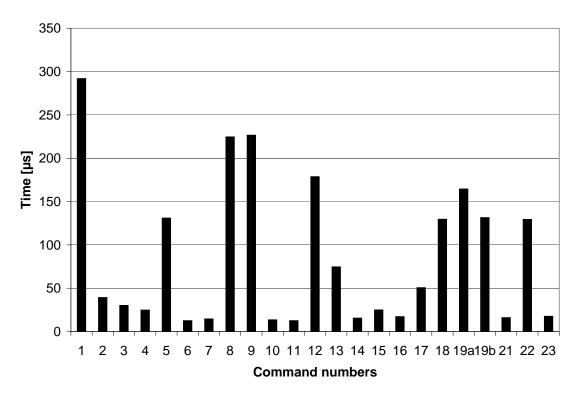

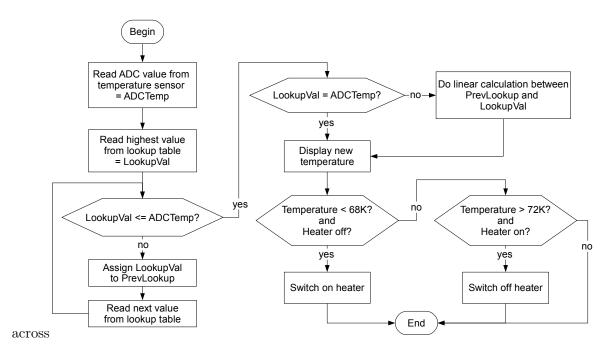

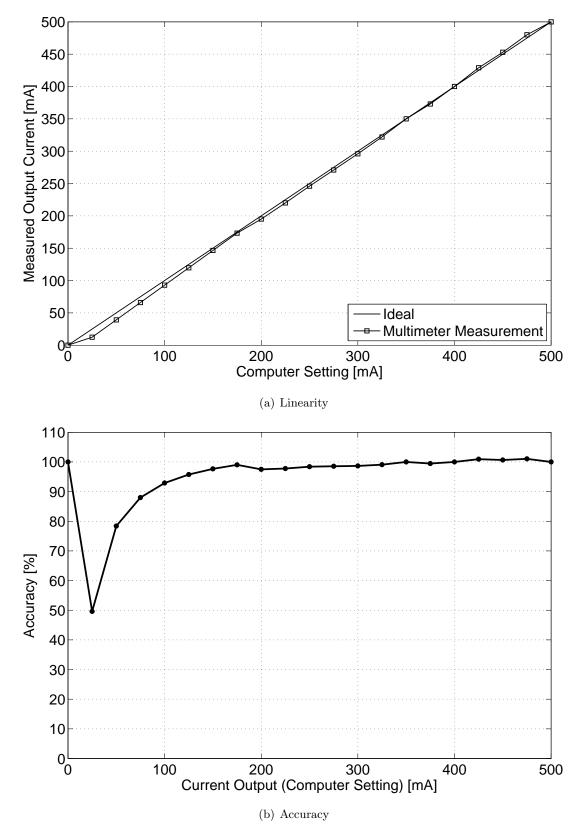

Three wires were directly attached to the pins of the ATtiny26. One supplied a positive 5 V, another the ground of 0 V and the last was the output which produced the sine wave. The microcontroller was programmed to automatically initialize and set up the watchdog timer and then produce a constant sine wave.