# Kernel support for embedded reactive systems

#### A THESIS

SUBMITTED TO THE DEPARTMENT OF COMPUTER SCIENCE

OF THE UNIVERSITY OF STELLENBOSCH

IN PARTIAL FULFILMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

MASTER OF SCIENCE

By MC Ackerman October 1993

Supervised by: Mr P.J.A. de Villiers

| Declaration |                                                                                               |

|-------------|-----------------------------------------------------------------------------------------------|

|             | rk contained in this thesis is my own original in part been submitted at any university for a |

| Signature:  | Date:                                                                                         |

# Abstract

Reactive systems are event driven state machines which usually do not terminate, but remain in perpetual interaction with their environment. Such systems usually interact with devices which introduce a high degree of concurrency and some real time constraints to the system. Because of the concurrent nature of reactive systems they are commonly implemented as communicating concurrent processes on one or more processors. Jeffay introduces a design paradigm which requires consumer processes to consume messages faster than they are produced by producer processes. If this is guaranteed, the real time constraints of such a system are always met, and the correctness of the process interaction is guaranteed in terms of the message passing semantics. I developed the ESE kernel, which supports Jeffay systems by providing lightweight processes which communicate over asynchronous channels. Processes are scheduled non-preemptively according to the earliest deadline first policy when they have messages pending on their input channels. The Jeffay design method and the ESE kernel have been found to be highly suitable to implement embedded reactive systems. The general requirements of embedded reactive systems, and kernel support required by such systems, are discussed.

# **Opsomming**

Reaktiewe stelsels is toestandsoutomate wat aangedryf word deur gebeure in hul omgewing. So 'n stelsel termineer gewoonlik nie, maar bly in 'n voortdurende wisselwerking met toestelle in sy omgewing. Toestelle in die omgewing van 'n reaktiewe stelsel veroorsaak in die algemeen 'n hoë mate van gelyklopendheid in die stelsel, en plaas gewoonlik sekere intydse beperkings op die stelsel. Gelyklopende stelsels word gewoonlik as stelsels van kommunikerende prosesse geïmplementeer op een of meer prosessors. Jeffay beskryf 'n ontwerpsmetodologie waarvolgens die ontvanger van boodskappe hulle vinniger moet verwerk as wat die sender hulle kan stuur. Indien hierdie gedrag tussen alle pare kommunikerende prosesse gewaarborg kan word, sal die stelsel altyd sy intydse beperkings gehoorsaam, en word die korrektheid van interaksies tussen prosesse deur die semantiek van die boodskapwisseling gewaarborg. Die "ESE" bedryfstelselkern wat ek ontwikkel het, ondersteun stelsels wat ontwerp en geïmplementeer word volgens Jeffay se metode. Prosesse kommunikeer oor asinkrone kanale, en die ontvanger van die boodskap met die vroegste keertyd word altyd eerste geskeduleer. Jeffay se ontwerpsmetode en die "ESE" kern blyk in die praktyk baie geskik te wees vir reaktiewe stelsels wat as substelsels van groter stelsels uitvoer. Die vereistes van reaktiewe substelsels, en die kernondersteuning wat daarvoor nodig is, word bespreek.

# Acknowledgements

## My thanks to:

- my supervisor, Pieter de Villiers, for his ideas, advice and guidance;

- Prof Tony Krzesinski for goading me whenever he saw me, none the less remaining patient; and

- Charlotte Ackerman for having unwavering faith in my completion of this thesis, constantly supporting me, and for cheerfully putting up with the disruption and stress caused by it.

# **Contents**

| A | betra | ct .                                                                       | iii |

|---|-------|----------------------------------------------------------------------------|-----|

| O | psom  | ming                                                                       | iv  |

| A | ckno  | wledgements                                                                | v   |

| 1 | Intr  | roduction                                                                  | 1   |

|   | 1.1   | The subject of this thesis                                                 | 2   |

|   | 1.2   | Outline of this thesis                                                     | 2   |

| 2 | Bac   | kground                                                                    | 3   |

|   | 2.1   | Scheduling algorithms for multiprogramming in a hard-real-time environment | 3   |

|   |       | 2.1.1 Rate monotonic scheduling                                            | 4   |

|   |       | 2.1.2 Deadline driven scheduling                                           | 5   |

|   |       | 2.1.3 Hybrid scheduling algorithms                                         | 6   |

|   |       | 2.1.4 Run-time vs. pre-run-time scheduling                                 | 7   |

|   | 2.2   | Specification and analysis techniques for real-time systems                | 8   |

|   | 2.3   | Operating systems for real-time systems                                    | 10  |

|   | 2.4   | The real-time producer/consumer paradigm                                   | 12  |

|   | 2.5   | Discussion                                                                 | 12  |

| 3 | The | real-time producer/concumer (RT/PC) paradigm         | 15 |

|---|-----|------------------------------------------------------|----|

|   | 3.1 | Introduction                                         | 15 |

|   | 3.2 | System components and graphical notation             | 16 |

|   |     | 3.2.1 Processes and channels                         | 18 |

|   |     | 3.2.2 Input and output devices                       | 19 |

|   |     | 3.2.3 Mutual exclusion regions and data repositories | 20 |

|   |     | 3.2.4 Well-formedness of design graphs               | 21 |

|   | 3.3 | Message passing semantics                            | 22 |

|   |     | 3.3.1 Message transmission rates                     | 22 |

|   |     | 3.3.2 Restrictions on process construction           | 22 |

|   | 3.4 | Calculating channel input rates                      | 23 |

|   |     | 3.4.1 Calculating message output rates               | 23 |

|   |     | 3.4.2 Calculating message input rates                | 24 |

|   | 3.5 | Scheduling results                                   | 24 |

|   | 3.6 | Implementing RT/PC designs                           | 26 |

| 4 | The | ESE Kernel                                           | 29 |

|   | 4.1 | Embedded Reactive Systems                            | 29 |

|   | 4.2 | Events                                               | 32 |

|   | 4.3 | Preemptive and Non-preemptive Scheduling             | 34 |

|   |     | 4.3.1 Support for RT/PC                              | 34 |

|   |     | 4.3.2 Scheduling efficiency                          | 34 |

|   |     | 4.3.3 Support for state machines                     | 35 |

|   |     | 4.3.4 Design decision                                | 35 |

|   | 4.4 | Periodic vs Sporadic Processes                       | 36 |

|   | 4.5  | Data Repositories and Synchronous Message Passing | 38 |

|---|------|---------------------------------------------------|----|

|   | 4.6  | Synchronous vs Asynchronous Channels              | 38 |

|   | 4.7  | Mutual Exclusion Regions                          | 39 |

|   | 4.8  | Interrupts and Events                             | 40 |

|   | 4.9  | Timers                                            | 43 |

|   | 4.10 | Implementation of Scheduling                      | 44 |

|   |      | 4.10.1 System clock granularity                   | 48 |

|   | 4.11 | Performance of ESE                                | 50 |

| 5 | Dev  | reloping Reactive Systems                         | 54 |

|   | 5.1  | Introduction                                      | 54 |

|   | 5.2  | X.25 case study — requirements definition         | 54 |

|   | 5.3  | System design                                     | 58 |

|   |      | 5.3.1 Block design of X.25 system                 | 58 |

|   |      | 5.3.2 Process decomposition                       | 60 |

|   | 5.4  | Design and analysis of RT/PC systems              | 61 |

|   |      | 5.4.1 Realisability of a design graph             | 61 |

|   |      | 5.4.2 Realisability of the X.25 design            | 62 |

|   |      | 5.4.3 Implementing the design graph               | 67 |

|   |      | 5.4.4 Implementation mapping of the X.25 example  | 70 |

|   |      | 5.4.5 Viability analysis                          | 73 |

|   |      | 5.4.6 Viability of the X.25 example               | 74 |

|   | 5.5  | RT/PC and ESE in practice — some observations     | 79 |

|   |      | 5.5.1 The area of applicability of ESE            | 81 |

|   |      | 5.5.2 The effort of designing for RT/PC and ESE   | 81 |

|   |            | 5.5.3         | Realisability and viability analysis | 81 |

|---|------------|---------------|--------------------------------------|----|

|   |            | 5.5.4         | Performance of ESE implementations   | 82 |

|   | 5.6        | Summ          | ary of method                        | 82 |

|   |            | 5.6.1         | Requirements definition              | 82 |

|   |            | 5.6.2         | System design                        | 82 |

|   |            | 5.6.3         | RT/PC design                         | 83 |

|   |            | 5.6.4         | Realisability analysis               | 83 |

|   |            | 5.6.5         | Implementation mapping               | 83 |

|   |            | 5.6.6         | Viability analysis                   | 83 |

|   |            | 5.6.7         | Implementation                       | 84 |

| 6 | Con        | clusio        | n.                                   | 85 |

| A | ESE        | inter         | face types and commands              | 89 |

|   | <b>A.1</b> | Турев         | •••••                                | 89 |

|   |            | A.1.1         | Alarm                                | 89 |

|   |            | A.1.2         | AsyncChannel                         | 89 |

|   |            | A.1.3         | InputPort                            | 90 |

|   |            | A.1.4         | Mailbox                              | 90 |

|   |            | A.1.5         | Message                              | 90 |

|   |            | A.1.6         | Name                                 | 90 |

|   |            | A.1.7         | Octet                                | 90 |

|   |            | A.1.8         | Process                              | 90 |

|   |            | A.1.9         | Thread                               | 91 |

|   |            | <b>A.1.10</b> | Time                                 | 91 |

|   |            | A 1 11        | Timer                                | Q1 |

|              | A.1.12 UserRef  | •   | ٠   | •  | •  | •  | ٠  | ٠  | • | ٠ | • | • | • | • | ٠ | • | • | ٠ | • | • | • | • | ٠ | ٠ | • | ٠ | ٠ | ٠ | ٠ | • | • | • | ٠ | • | • | 9  | 1 |

|--------------|-----------------|-----|-----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|---|

| <b>A.2</b>   | CreateProcess . | •   | •   | •  |    |    | •  |    |   | • | • | • | • |   |   | • | • |   | • |   | • |   | • | • | • | • | • | • | • |   | • |   | • | • | • | 9  | 1 |

| <b>A.3</b>   | CreateAsyncCh   | an  | ne  | 1  |    |    |    | •  | • | • | • | • | • | • |   |   |   | • | • |   |   |   |   |   |   |   | • | • |   |   | • |   | • |   | • | 9: | 2 |

| <b>A.4</b>   | CreateMailbox   | •   |     |    |    | •  |    | •  | • | • | • |   |   | • |   |   |   | • | • | • | • |   | • |   |   | • | • | • | • | • | • |   | • | • |   | 9: | 2 |

| <b>A.</b> 5  | CreateInputPor  | t   | •   | •  | •  | •  | •  | •  | • | • |   |   | • | • | • | • |   | • | • | • | • |   | • |   |   | • | • |   |   |   | • |   | • | • | • | 9: | 2 |

| <b>A.</b> 6  | StartSystem     | •   |     |    |    |    | •  |    |   | • | • |   | • | • | • | • |   |   | • | • | • |   | • | • |   |   | • | • | • |   |   |   | • | • | • | 9  | 3 |

| A.7          | SendMessageOr   | ιAε | sy: | nc | Cł | aj | nn | el |   | • | • |   |   | • | • |   | • |   | • | • | • |   | • | • |   |   |   | • | • | • |   |   | • | • | • | 9  | 3 |

| <b>8.A</b>   | PutIntoMailbox  | ٠.  |     |    | •  | •  |    |    | • |   | • |   |   |   | • |   |   |   | • | • | • | • |   |   |   |   |   | • | • | • |   |   |   | • |   | 9: | 3 |

| <b>A.9</b>   | SignalInputPort | : . | •   |    | •  |    | •  |    |   | • | • |   | • | • | • | • | • | • | • |   | • | • | • | • |   |   |   | • | • |   | • |   | • | • | • | 9- | 4 |

| <b>A.</b> 10 | Receive         | •   |     |    | •  | •  | •  | •  | • | • | • | • | • | • | • | • | • | • | • |   | • | • | • | • |   |   | • | • | • | • | • | • |   | • | • | 9  | 4 |

| <b>A</b> .11 | SetTimer        | •   |     |    |    |    | •  | •  |   |   | • |   | • | • |   | • | • | • |   | • | • |   | • | • |   |   | • | • | • |   | • |   | • | • | • | 9  | 5 |

| A.12         | SetAlarm        | -   | •   |    | •  | •  | •  |    | • |   | • | • |   | • | • | • | • | • |   |   | • | • | • | • | • |   |   | • | • |   | • |   | • | • |   | 9  | 5 |

| A.13         | StopTimer       | •   |     |    | •  | •  | •  |    | • | • | • |   | • | • | • | • | • |   | • | • | • | • | • | • | • |   |   | • | • |   | • |   | • | • | • | 9  | 5 |

| <b>A</b> .14 | StopAlarm       |     |     |    |    |    | _  |    | _ | _ | _ | _ | _ |   | _ | _ | _ | _ | _ | _ | _ |   | _ | _ | _ | _ | _ | _ | _ |   | _ |   | _ | _ |   | 96 | ƙ |

# List of Tables

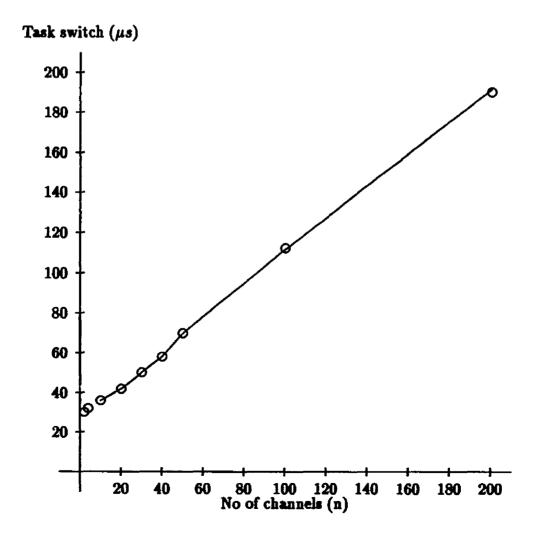

| 1 | Task Switching Overhead                       | 52 |

|---|-----------------------------------------------|----|

| 2 | Timer Processing Overhead                     | 53 |

| 3 | Viability Condition 1 — Maximum Channel Rate  | 77 |

| 4 | Viability Condition 1 — Adjusted Channel Rate | 78 |

# List of Figures

| 1  | Real-11me producer/consumer paradigm            | 16 |

|----|-------------------------------------------------|----|

| 2  | An RT/PC design graph                           | 17 |

| 3  | Schema for an RT/PC process                     | 19 |

| 4  | A schema for an RT/PC data repository           | 21 |

| 5  | Message transmission rate function              | 24 |

| 6  | Input rate definition for MP/SC processes       | 24 |

| 7  | Reactive system                                 | 30 |

| 8  | Information frame format                        | 41 |

| 9  | Fast Interrupting Device: Unrealisable System   | 41 |

| 10 | Fast Interrupting Device: Realisable System     | 42 |

| 11 | Scheduling with course clock ticks              | 50 |

| 12 | Scheduling with inserted fine grain clock ticks | 51 |

| 13 | Task switching cost of channels                 | 52 |

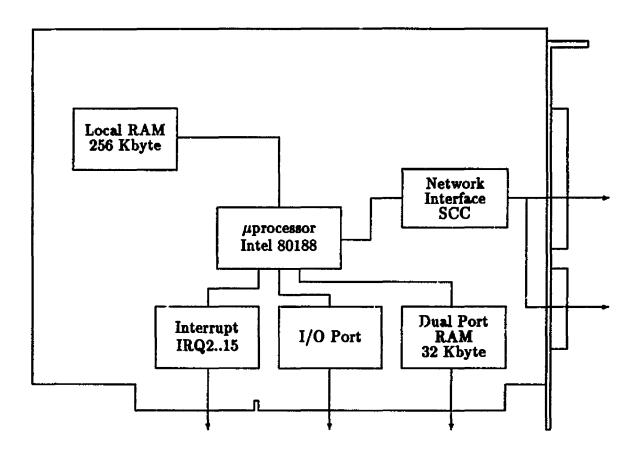

| 14 | Block diagram of iX.25 hardware                 | 56 |

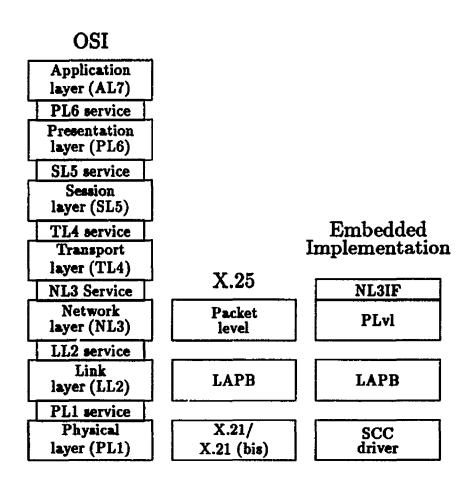

| 15 | OSI/X.25/implementation correspondence          | 59 |

| 16 | Protocol machine implementations                | 60 |

| 17 | Nested cycles                                   | 62 |

| 18 | RT/PC design of X.25                            | 63 |

| 19 | Reduced, annotated RT/PC design for X.25                | 6  |

|----|---------------------------------------------------------|----|

| 20 | Refined model of X.25 for implementation                | 71 |

| 21 | Input File for Viability Condition 2 Checker            | 79 |

| 22 | Output File of Viability Condition 2 Checker            | 86 |

| 23 | Output File of Viability Condition 2 Checker: Continued | 80 |

# Chapter 1

# Introduction

The proliferation of cheap microprocessors over the past decade has led to a trend of distributing intelligence in a computer system, and to embed intelligent applications in subsystems. Integrated single chip and chip set solutions has made it cheap and easy to produce relatively powerful embedded and stand-alone platforms. These platforms are used in a variety of applications: from bus expansion cards, such as intelligent communications controllers, to stand-alone devices such as process controllers and hand held computers.

The intelligence available in embedded platforms, today, facilitates very powerful embedded applications. At the same time, economical considerations often dictate that commercial and industrial systems be built on the cheapest possible platform. This usually results in a less powerful processor, and less memory, than the software engineer would have preferred. In contrast, operating systems are becoming more complex, and small embedded platforms can often not support their resource requirements.

An embedded system usually interacts with devices in its environment. Such devices often introduce real-time constraints on the device drivers controlling them. By real-time we mean that the correctness of the system depends on its processing of certain events within a known interval, in other words: before a deadline. In some real-time systems a missed deadline may have catastrophic results. Such systems are usually called hard real-time systems. Examples of hard real-time systems are on-board flight control systems, medical control systems, etc. Other real-time systems can recover from missed deadlines, and are know as soft real-time systems.

Pnueli [45] describes two basically different views of computerised systems. The first, called transformational systems, refers to systems which accept their inputs at the beginning of

their operation, and yield their outputs at termination. The second, called reactive systems, are systems which typically don't terminate, but remain in perpetual interaction with their environment. Reactive systems are not used to obtain a final result, but rather to control ongoing processes. Embedded systems are often reactive systems.

# 1.1 The subject of this thesis

Small commercial and industrial embedded systems are often built on uniprocessor platforms. The processor and RAM resources of these platforms usually do not permit the use of sophisticated state of the art operating systems, but their reactive nature is best supported as a system of communicating processes. Furthermore, these systems interact with devices, and therefore often have real-time constraints.

The purpose of this study is to find a design and implementation methodology which is suitable for the type of systems described above. The implementation strategy should ensure that the temporal correctness of a design is preserved in its implementation.

#### 1.2 Outline of this thesis

This chapter introduces the concepts of real-time, embedded and reactive systems, and describes the subject of the thesis.

Chapter 2 describes the state of the art in real-time scheduling techniques, operating systems and design and analysis methods. One method is chosen for an experimental implementation.

Chapter 3 summarises the RT/PC paradigm: a design and analysis method for real-time systems. The paradigm, its graphical design notations, scheduling results, and realisability analysis are described.

Chapter 4 examines the design, features and performance of the ESE kernel, which supports implementations of RT/PC designs.

Chapter 5 describes the design, analysis and implementation of a real system. The RT/PC method is used to design the system, which is then implemented on an embedded ESE kernel.

Finally, chapter 6 discusses the conclusions drawn from using RT/PC and the ESE kernel in practice.

2

# Chapter 2

# **Background**

In chapter 1, the goal of this study was stated to be an investigation into a design and implementation methodology, which is appropriate for uniprocessor based embedded systems. We also saw that the concepts of real-time and reactive systems are pertinent to this study. The implementation of embedded systems, on the target platforms in which we are interested, will require specific kernel support for reactive, real-time systems. To understand the background to this study we must therefore survey the literature pertaining to real-time scheduling, reactive and embedded systems, analysis and modeling techniques for real-time systems, and operating system support for real-time systems.

# 2.1 Scheduling algorithms for multiprogramming in a hardreal-time environment

This was also the title of a landmark paper by Liu and Layland [39] in 1973, in which the authors compared two preemptive priority scheduling techniques: a fixed priority and a dynamic priority scheduling algorithm. In the fixed priority algorithm, priorities are assigned to tasks according to the rate monotonic priority assignment method. In the dynamic priority algorithm, the priority of a task is determined by its deadline. Liu and Layland's results are for periodic tasks scheduled on a uniprocessor, and tasks are independent. That is, requests for a certain task do not depend on the initiation or completion of requests for other tasks.

#### 4

## 2.1.1 Rate monotonic scheduling

Let  $\tau = \{T_1, T_2, \ldots, T_m\}$  be a set of m periodic tasks. Let each task  $T_i = (c_i, p_i)$  be characterised by its execution cost,  $c_i$ , and its request period,  $p_i$ . The request rate  $r_i$  of a task is the reciprocal of its request period, and represents the frequency at which the task must be scheduled. A rate monotonic priority assignment to  $\tau$  implies that for all  $T_i, T_j \in \tau$ , the priority assigned to  $T_i$  is higher than the priority assigned to  $T_j$  iff  $p_i < p_j$ . Liu and Layland proved that the rate monotonic priority assignment is optimal in the sense that if a feasible priority assignment exists for a task set, the rate monotonic priority assignment is feasible for that task set.

Definition 1 A feasible set of tasks can be scheduled on a uniprocessor in such a way that every execution request of every task is guaranteed to have completed execution at or before its deadline.

Definition 2 An optimal scheduling discipline can correctly schedule any task set that is feasible.

Liu and Layland defined a processor utilisation factor,  $U_i = \frac{c_i}{p_i}$ , for tasks. The total processor utilisation for a set of tasks is given by

$$U_{\tau} = \sum_{i=1}^{m} \frac{c_i}{p_i}$$

For a given fixed priority scheduling algorithm, the *least upper bound* of the utilisation factor is the minimum of the utilisation factors over all task sets that fully utilise the processor. If the utilisation factor of a task set is below this bound, there exists a feasible priority assignment for it. If the utilisation factor of a task set is above the least upper bound, it is feasible only if the request periods of its tasks are related suitably. Liu and Layland proved that the least upper bound of the utilisation factor for a fixed priority assignment is

$$U\leq m(2^{\frac{1}{m}}-1),$$

and for large m

$$U \simeq ln2 = 0.69$$

Liu and Layland's original work has been extended significantly. Dhall and Liu [14], for example, studied the performance of the rate monotonic first fit and rate monotonic next

fit scheduling algorithms for multiprocessor systems. Sha and Goodenough [50] discuss rate monotonic analysis and give necessary and sufficient feasibility conditions for task sets which exceed the least upper bound for fixed priority processor utilisation. They also discuss how aperiodic tasks can be supported, and give a sufficient feasibility condition for tasks which synchronise.

When tasks which are scheduled according to the rate monotonic algorithm synchronise, i.e. the requests for a certain task may depend on the initiation or completion of requests for other tasks, a situation called *priority inversion* arises. Priority inversion occurs when tasks with different priorities come into contention for a shared resource, and a higher priority task is blocked by a lower priority task. Davari and Sha [12] examine common sources of priority inversion and outline a number of solutions to the problem.

The rate monotonic scheduling algorithm is popular today for scheduling sets of tasks with hard real-time constraints [36, 60, 6], and rate monotonic analysis can be used in conjunction with other scheduling algorithms [6].

## 2.1.2 Deadline driven scheduling

The effect of using a deadline driven scheduling algorithm is to dynamically adjust the priorities of tasks according to their deadlines. For a periodic task set Liu and Layland [39] derived the following necessary and sufficient feasibility condition for a deadline driven scheduling algorithm:

For a given set of m periodic tasks, the deadline driven scheduling algorithm is feasible if and only if

$$\sum_{i=1}^m \frac{c_i}{p_i} \le 1$$

This means that the least upper bound for processor utilisation is uniformly 100%. Two deadline driven algorithms are commonly used:

1. The least slack first algorithm selects the task with the least amount of slack before its deadline. The difference between the remainder of a task's period (before its deadline) and its computational cost is known as its slack. This algorithm has been proved to be optimal for uniprocessor systems [37].

2. The earliest deadline first algorithm selects the task with the earliest deadline to be executed next. This algorithm has been proved to be optimal for both uniprocessor and multiprocessor systems [37].

Deadline driven scheduling is optimal for both periodic and aperiodic tasks [8, 28, 9, 39]. Jeffay [28] proved necessary and sufficient feasibility conditions for preemptive and non-preemptive earliest deadline first scheduling of periodic and aperiodic tasks on a uniprocessor.

## 2.1.3 Hybrid scheduling algorithms

Hybrids of fixed and dynamic priority algorithms are used for many reasons. Liu and Layland [39] observed that interrupt controllers impose a static priority assignment on interrupt events, even when deadline driven scheduling is used. Processor utilisation cannot be 100% for mixed scheduling algorithms, but on average can be much higher than the least upper bound of the processor utilisation for fixed priority schedulers [39].

In rate monotonic schedulers the priority of critical tasks may be temporarily adjusted to accommodate transient overload conditions [50]. Miller [43] cites the necessity to have functional prioritisation in the presence of deadline scheduling. Schwan and Zhou [49] describe a preemptive earliest deadline first scheduler which performs dynamic feasibility analysis when a task request is received. Since all deadlines cannot be guaranteed in this environment a secondary metric, called *criticalness* is used to determine which task is scheduled when two tasks cannot simultaneously meet their deadlines.

Because deadlines must be met in the worst case behaviour or hard real-time systems, analysis of hard real-time systems is usually based on the theoretical worst case behaviour of the system. The average case behaviour may differ significantly from the worst case, and if schedules are computed based on worst case, under utilisation of resources may result. Hardware and software monitors may be used to measure the real-time behaviour of real-time systems, and adapt the scheduling policy accordingly. Haban and Shin [19] describe issues relating to real-time monitoring, and their experience with using a hardware monitor, while Kenny and Lin [30] describe software monitoring in the Flex language and C++. Some real-time operating systems include monitors to improve average system performance [58].

### 2.1.4 Run-time vs. pre-run-time scheduling

Because it is imperative for a hard real-time system to meet its deadlines, task schedules for hard real-time systems are sometimes computed before run-time. A very simple run-time scheduler is then used to select the next task from the pre-calculated schedule. Scheduling a task set before run-time can reduce the run-time scheduling overhead, because feasibility analysis is not done when the task is scheduled, and it ensures that a feasible schedule exists before the task set is run. This approach is called pre-run-time scheduling, or static scheduling. Another approach is run-time or dynamic scheduling, where the schedule for a task set is calculated as task requests arrive. Except for a closed task set, run-time scheduling implies that feasibility analysis is required when a task request arrives. Burns [5] reviews current scheduling techniques for hard real-time systems.

Xu and Parnas [65] argue that pre-run-time scheduling is essential to guarantee that a system will meet all its timing constraints. In their experience most tasks in a hard real-time environment are periodic, and any asynchronous (aperiodic) task can be translated into an equivalent periodic task. For instance, let  $T_a = (c_a, p_a, d_a)$  be an asynchronous task, with  $c_a$  the worst case computational cost,  $p_a$  the minimum period between successive requests for  $T_a$ , and  $d_a$  its deadline.  $T_a$  can be translated [65] into an equivalent periodic task,  $T_p = (r_p, c_p, p_p, d_p)$ , with release time  $r_p = 0$ , computational cost  $c_p = c_a$ , deadline  $d_a \ge d_p \ge c_p$ , period  $p_p \le min(d_a - d_p + 1, p_a)$ . In this way it is possible to schedule asynchronous tasks using pre-run-time scheduling. Xu and Parnas [64] give a pre-run-time scheduling algorithm for processes with release times, deadlines, precedence and exclusion relations. Shepard [53] gives a pre-run-time multiprocessor scheduling algorithm for the same class of processes. The original algorithm by Xu and Parnas was later also extended by Xu [63] to include multiprocessor architectures.

Schwan and Zhou [49] argue that dynamic hard real-time systems, in their experience, have to cope with unexpected sporadic (aperiodic) processes with hard deadlines. A schedule of periodic tasks computed pre-run-time cannot adapt adequately to frequent unexpected task requests with hard deadlines. Such task sets should be scheduled dynamically, but this means that a feasible executing task set may be rendered infeasible by the arrival of a new task request. Run-time feasibility analysis is therefore required before a new task request can be scheduled. Schwan and Zhou present a preemptive earliest deadline first algorithm with run-time feasibility analysis. A secondary metric, criticalness is used to determine which tasks are scheduled when the arrival of a new task request causes an infeasible schedule. When a new task request arrives, only those tasks which are in contention with the new task are

rescheduled. This keeps the run-time overhead of the scheduler low.

Chetto and Chetto [8, 9] use a combination of static and dynamic scheduling for fault tolerant hard real-time systems. For each task it is possible to schedule either a primary or an alternative process. If a primary process fails, an alternative may be used to recover from the failure. The primary processes are scheduled pre-run-time, and alternatives sporadically when a primary fails.

# 2.2 Specification and analysis techniques for real-time systems

Embedded systems are hard to develop and test for a number of reasons. Because the hard-ware platform of an embedded system is usually customised to the specific purpose of the system, the usual development aids such as character I/O and interactive debuggers can often not be used. Because an embedded system is often a subsystem of a larger system, it may not be possible to test in isolation, and more seriously, it may have real-time constraints which are hard or impossible to create outside the actual target environment. In some critical hard real-time systems, such as weapons systems, the problem with testing and correcting errors under operational conditions is self evident.

De Roever [13] urges the development of a design specification which satisfies a "full requirements specification", followed by implementation according to fail-safe, fault tolerant techniques. Rigorous specification development is only possible when a formal specification method is used, and preferably automated. Fault tolerant techniques are becoming more constant [8, 9, 33, 37, 41, 54], and many analysis techniques have appeared. Although the definition of the term real-time depends on the perspective of the practitioner using it, there are clear categories and trends. The explicit use of time in the specification of real-time systems evokes a wide range of responses. Turski [59] advocates total avoidance of the explicit use of time, while others prefer stepwise addition of timing constraints [23, 35]. At the other extreme are totally time based design and analysis methods, such as rate monotonic analysis.

The following papers provide review aspects of design and analysis of real-time systems: Heath [22] argues in favour of multiprocessor design architectures; Joseph and Goswami [29] review formal description techniques used for real-time systems; and Hull, et al [26] compare four methods for real-time system development. We shall now briefly examine some current trends.

State machines. Harel [20] describes an extension of finite state machines, called State-charts. Statecharts is a visual formalism which allows the specification of concurrent components, as well as their refinement and abstraction. It is well suited to the rigorous specification of reactive systems and since the semantics of statecharts are formally specified, automated analysis of statecharts can be done [21].

Communicating Real-Time State Machines [52] is a notation for specifying the requirements of real-time systems. It allows the definition of a system of state machines that communicate over unidirectional channels.

- Temporal logic and model checking have been used successfully in the verification of concurrent systems [10]. Extended temporal logics can be defined [44, 45] to allow quantitative temporal operators over bounded intervals. The resultant logics are used to specify real-time properties for models of finite state systems. These models are extended with a mechanism which allows the expression of bounds on the delays between state transitions. Model checking can be used to verify that the model satisfies the specification.

- Graph theory. Graphs can be used to model real-time systems [27, 28]. Real-time constraints can be specified for elements of a graph and used in a mathematical analysis of the temporal behaviour of the system. The design method of the MARS real-time operating system uses graphs to specify real-time transactions [34, 33].

- Process algebra. CSP-R [40] is an extension of Hoare's Communicating Sequential Processes [24, 25] by a real-time construct, wait t. Programs with real-time constraints can be written and statically analysed for temporal correctness. The maximal parallelism approach to real-time programming, taken in CSP-R, is criticised by Kurki-Suonio [35] because of the interdependencies on the relative speed of processes which it introduces into models.

- Real-time analysis for programming languages. Fugetta et al [15] extend Haase's [18] extension of Dijkstra's guarded commands by parallel guarded commands (PARCs) for real-time programs. Execution times for PARCs are specified as weakest preconditions. Shaw [51] describes a methodology similar to that of Fugetta, et al. He extends Hoare logic to prove assertions about deadlines and timing constraints in high level language programs.

Stoyenko et al [56] describe a system which supports guaranteed schedulability of Real-time Euclid programs. The system includes a Real-Time Euclid compiler, schedulability

analyser, and a kernel which schedules tasks according to the Earliest Deadline First policy on a multiprocessor hardware platform. It is capable of guaranteeing real-time response.

I have tried to give a brief overview of trends in real-time system design. As we shall see in section 2.3, the trend in hard real-time operating systems is towards distributed and multi-processor architectures.

# 2.3 Operating systems for real-time systems

A large number of real-time operating systems have been developed over the last decade. The latest systems reflect the state of the art in hardware (distributed and multi-microprocessor architectures) and the theory of analysis and scheduling of real-time systems. We shall briefly review some of the well documented examples.

- ARTS [58] is an object oriented distributed real-time operating system kernel and a real-time toolset which consists of a schedulability analyser and a real-time monitor. ARTS has a time driven rate monotonic scheduler and priority inheritance protocol to prevent unbounded priority inversion. The scheduler can guarantee hard periodic tasks, and perform criticality based soft real-time task scheduling, as well as overload control based on value functions of aperiodic tasks.

- CHAOS<sup>arc</sup> [17] is an object based real-time operating system designed for a multiprocessor architecture. It can run on bare hardware, or on an existing operating system [47, 48]. Chaos supports lockable resources, and uses a run-time earliest deadline first scheduling policy. Schedulability analysis is done dynamically and a priority assignment, based on the "criticalness" of the task, is used to determine a feasible task set [4, 48].

- Real-time threads [47, 48] is a package which supports the programming of concurrent threads on a UNIX platform. Since the package is built on top of a standard UNIX platform, it is portable. Scheduling is earliest deadline, and schedulability analysis is done when the thread is created. Threads communicate via lockable shared data structures or signals. See also Chaos<sup>arc</sup>.

- FAIRCHILD [42] is a real-time operating system which runs on an embedded Intel 80386 system. It employs a predictive deadline scheduling policy [43] and supports multiprocessing, semaphores and event management. In [42] Miller gives performance statistics

for the system.

- HARTS [54] (Hexagonal Architecture for Real-Time Systems) is a mesh of 19 nodes, each consisting of application processors, a network processor and a RISC processor. Each node connects to 6 other nodes via its network processor. A distributed operating system, HARTOS, consists of a single processor kernel running on each application processor. A distributed name service and both blocking and non-blocking inter-process communication is provided. The scheduling policy is priority based and processes can change their priority dynamically.

- MARS [34, 33] (Maintainable Real-Time System) is a fault tolerant distributed real-time operating system. The MARS architecture consists of a number of MARS components inter-connected on a synchronous real-time bus. Each component is a computer on which tasks are executed, and components are clustered to manage network complexity. Messages in MARS are not consumed then read. Instead, a message may be read multiple times, and is overwritten when the system state changes. Tasks as well as communication on the MARS bus is scheduled pre-run-time, and hard real-time tasks are periodic. Aperiodic tasks usually have soft deadlines, and are handled in system idle time.

- Maruti [38, 37] is an object oriented distributed real-time operating system which supports fault tolerance through replication. Maruti supports reactive systems in that task requests may be entered dynamically when a previously guaranteed schedule is already executing. Run-time schedulability analysis determines whether a new task request can be guaranteed to complete before its deadline. Tasks with no deadline guarantees execute "off-line" when no real-time tasks are ready.

- Spring [55] is a distributed real-time operating system kernel which guarantees deadlines. It supports tasks with lockable resources, which are scheduled at run-time. Run-time schedulability analysis determines whether a task's deadline can be guaranteed.

- Thoth [7] is a single processor real-time operating system which was designed to be portable. It runs on Data General Nova and Texas Instruments minicomputers. Tasks are scheduled on a priority basis, and a task is not preempted unless a higher priority task becomes ready, or the task is blocked.

- Commercially available real-time operating systems. VRTX [46] is a commercially available real-time operating system for embedded microprocessor applications. Tasks

are scheduled by a preemptive priority based scheduler on a uniprocessor. Tasks communicate through signals, mailboxes and queues. Various real-time versions of the *UNIX* operating system have been developed [16]. Intel Corporation's RMK kernel and RMX operating system [1] are also widely used. QNX [31] is a distributed real-time operating system which provides inter-process communication through remote procedure calls.

The review of real-time operating systems provided here is by no means complete. The intention is to reflect the current trends, and to highlight how both deadline driven and priority based scheduling is employed both pre-run-time and at run-time.

# 2.4 The real-time producer/consumer paradigm

In 1989 Kevin Jeffay published his Ph.D. thesis [28] in which he describes a design method for real-time systems. The method is based on the premise that a real-time system can be understood in terms of producer/consumer relationships on system components. Jeffay's paradigm requires that the  $k^{th}$  message sent on any channel must be consumed before the  $k+1^{th}$  message is sent. He calls this the Real-Time Producer/Consumer (RT/PC) paradigm.

Jeffay proves that both preemptive and non-preemptive deadline scheduling could be used to realise his paradigm. This makes it well suited to reactive real-time systems which are driven by aperiodic (sporadic) events. The message passing semantics of the RT/PC paradigm makes it possible to reason about time, and make accurate performance predictions.

In his thesis Jeffay describes a graphical design method which supports RT/PC, and determines certain conditions under which an RT/PC design can be implemented with guarantees of temporal correctness. These conditions can be used to support a design and development method for real-time reactive systems which spans requirements analysis to implementation. Given appropriate run-time kernel support, the real-time behaviour of a design can be guaranteed at run-time.

#### 2.5 Discussion

It should be clear from the brief survey of scheduling techniques that there are distinct camps in the field of scheduling for hard real-time systems. Both rate monotonic and deadline driven scheduling can be used to guarantee deadlines. Both techniques can be used in a static as well

as dynamic scheduling mechanism. Hybrid techniques (mixed priority and deadline driven scheduling, and dynamic priority adaption) are used widely.

The choice of scheduling algorithm (priority based or deadline driven) and whether scheduling is none pre-run-time or at run-time, is dictated by the nature of the real-time environment in which the system will run. In environments where sensors are regularly sampled, a periodic task approach is suitable. In environments where a system has to react to frequent sporadic events, a deadline driven approach is appropriate.

If it is imperative that hard deadlines be met, pre-run-time scheduling can guarantee a feasible schedule. In a closed task set deadlines can be guaranteed by both deadline and rate monotonic scheduling, but rate monotonic is preferred in periodic task environments. If task requests can arrive dynamically, all deadlines cannot be guaranteed — a new task request can render the current schedule infeasible. This means that run-time feasibility analysis must be done. If the new task set is infeasible, some tasks will not meet their deadlines. In a hard real-time environment, critical tasks must therefore be ensured to remain in the feasible schedule. This can be done by ensuring that they have a higher priority in a rate monotonic scheduler, or to use a second priority metric in deadline driven schedulers.

Next generation real-time platforms tend to have multiprocessor or distributed architectures with processors dedicated to specific purposes. Processor nodes sometimes consist of a cluster of special purpose processors: application processor, network processor, off-line scheduler, monitor, etc. The design and features of next generation real-time operating systems depend on the environment in which it is used. Systems which support periodic tasks are used in periodic environments, such as pure control systems. Operating systems which support aperiodic processes are normally used in asynchronous environments, usually with deadline scheduling. Fault tolerance is usually supported through replication. Failures of primary tasks scheduled pre-run-time are recovered by backup tasks which are activated aperiodically, and usually scheduled by deadline.

The goal of this study was stated in chapter 1 to be an investigation into a method of design, analysis and implementation for small, uniprocessor based embedded reactive systems. Run-time support for the method should allow guaranteed real-time behaviour, and the implementation method should use resources such as CPU and RAM economically.

Since the systems in which we are interested consist of closed reactive task sets, deadline scheduling can be used to guarantee real-time behaviour. Jeffay's method suits the environments for which the method is intended very well. In RT/PC messages flow through

14

the system from input devices, through communicating processes to output devices. Deadline driven scheduling makes it well suited to aperiodic environments, and RT/PC semantics allow rigorous reasoning about the timing of a system's real-time behaviour. Finally, kernel support for RT/PC can be economically provided on the platforms for which it is intended. Jeffay's method was therefore chosen to be the subject of an experimental kernel support implementation, as well as a nontrivial reactive application. The rest of this thesis describes the kernel implementation, and the application of RT/PC in the design, analysis and implementation of a real reactive application.

# Chapter 3

# The real-time producer/consumer (RT/PC) paradigm

## 3.1 Introduction

In this chapter we will examine Jeffay's method of design and analysis for hard real-time systems [28]. Jeffay defines a model of hard real-time systems, which he calls the real-time producer/consumer paradigm, and uses it as a semantic basis for a design discipline of real-time systems. The method consists of a graphical design notation for describing RT/PC systems, and a sequence of analysis steps during which the semantic correctness of the system is determined. This chapter discusses the various components of the design method, and the different aspects of analysis. More emphasis is laid in this chapter on the design method than analysis, since the analysis of RT/PC systems is the subject of chapter 5.

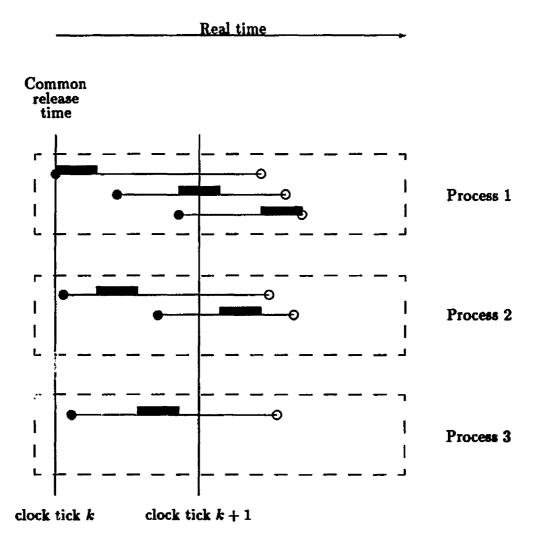

Jeffay models a real-time system as a system of message producers which communicate with message consumers via unidirectional channels. Assuming that there is no propagation delay, the consumer of a message receives it immediately after it was sent by the producer. If a producer produces messages faster than the consumer can consume them, then no amount of buffering is sufficient to prevent the loss of messages. To guarantee the correctness of the system the consumer must process messages at least at the rate at which they are produced. Based on this observation Jeffay defines the real-time producer/consumer paradigm (RT/PC) as follows:

Definition 3 The consumer must process the ith output of the producer before the producer

#### CHAPTER 3. THE REAL-TIME PRODUCER/CONSUMER (RT/PC) PARADIGM

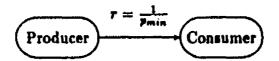

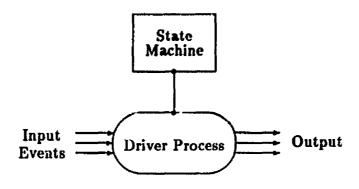

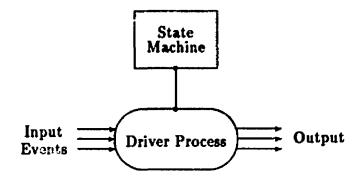

Figure 1: Real-time producer/consumer paradigm

produces the  $(i+1)^{st}$  output.

Figure 1 illustrates the RT/PC paradigm. Producer and Consumer are processes, connected by a unidirectional channel. The rate (r) at which messages can flow on the channel between Producer and Consumer, is the reciprocal of the minimum period between any two messages on the channel  $(p_{min})$ .

# 3.2 System components and graphical notation

In this section we shall examine the components of Jeffay's design discipline, and describe his graphical notation. The method is based on the producer/consumer model of communicating processes, and the design of a real-time system may be expressed as a directed graph, G = (V, E). V is the set of vertices, and can represent processes, input devices, output devices or data repositories. E the set of edges, and can represent unidirectional synchronous or asynchronous channels between the vertex components. A design can therefore contain:

- Processes machines which process messages. Processes are graphically denoted as ovals.

- Channels unidirectional asynchronous connections between processes, or synchronous

connections between processes and data repositories. An asynchronous channel is graphically denoted by a single-headed arrow, a synchronous channel by a double-headed

arrow.

- Data repositories machines which control access to data objects which are shared between two or more processes. Data repositories are graphically denoted by two concentric ovals.

<sup>&</sup>lt;sup>1</sup>I have modified Jeffay's original graphical notation slightly with regard to input and output devices. Jeffay's original graphical notation uses a darkened circle for input devices, and a darkened and shaded circle for output devices. I use a bar for both input and output devices. Input and output devices can still be uniquely identified: input devices by their single outgoing directed edge, and output devices by their single incoming edge. The notational change was necessitated by a lack of graphical tools, and incurs no loss of meaning, power or clarity.

### CHAPTER 3. THE REAL-TIME PRODUCER/CONSUMER (RT/PC) PARADIGM

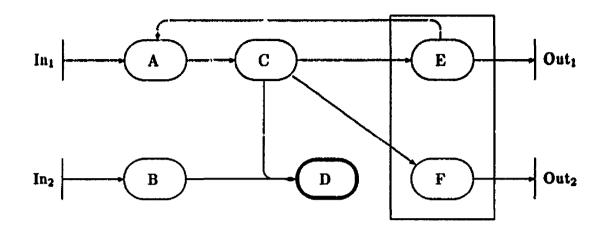

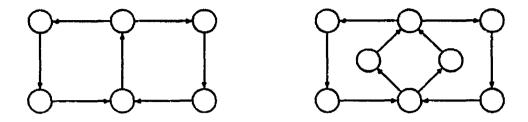

Figure 2: An RT/PC design graph

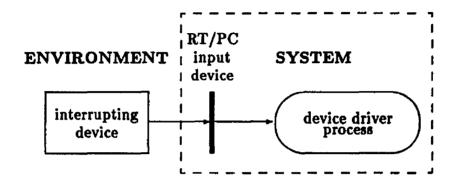

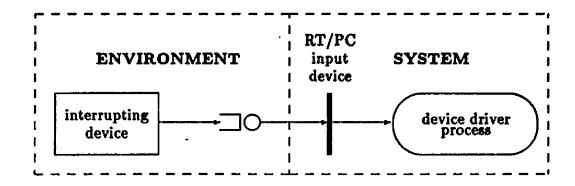

- Input devices process abstractions of physical devices which cause messages to flow into the system; denoted graphically by a bar.

- Output devices process abstractions of physical devices into which messages flow out of the system; denoted graphically by a bar.

- Mutual exclusion regions sets of processes or data repositories which are implicitly or explicitly required to execute mutually exclusively in time. An explicitly defined mutual exclusion region is graphically denoted by enclosing its members in a box.

Figure 2 is an example of an RT/PC design graph. In the figure we can identify the following components:

- A, B, C, E and F are processes;

- D is a data repository;

- In1 and In2 are input devices;

- Out<sub>1</sub> and Out<sub>2</sub> are output devices;

- The directed edges of the graph represent unidirectional channels.

- The box enclosing vertices E and F defines an explicit mutual exclusion region, consisting of E and F.

#### 18

#### 3.2.1 Processes and channels

An RT/PC model represents a reactive system which performs certain actions in response to events that occur in its environment. In the model events are represented by messages which are transmitted to processes by input devices or other processes. When a process receives a message it may perform certain operations, and send one or more messages in response to other processes, data repositories or output devices.

An RT/PC process consists of a single execution thread, with a single entry point, which always starts with the reception of a message, and is defined by its behaviour in response to each message it may receive. Each time a process completes its execution thread it blocks until it receives another message.

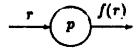

Figure 3 shows a schema for an RT/PC process. The ACCEPT command blocks the process until it receives a message (msg). It then executes the body of the process, and may call A\_EMIT and S\_EMIT one or more times. A\_EMIT is used to send a message to another process or output device on an asynchronous channel. S\_EMIT is used to send a synchronous message to a data repository, and to receive a reply from it.

A process can receive messages on only one logical input port, but several asynchronous channels may connect to the same input port. A process may emit messages on a set of output ports, but only one message may be emitted on each asynchronous output channel per execution of the process thread. The input and output ports of a process are statically bound to communication channels for the lifetime of the system.

A channel is a connection between the output port of one process and the input port of another process or data repository. If a process sends a message on a synchronous channel, it awaits and will receive a response. A process which sends a message on an asynchronous channel does not block, and does not receive a response to the message. All messages sent on a channel will be received by the receiving process. As long as a process does not emit two messages on the same asynchronous channel during the same execution of the process thread, and if the system obeys RT/PC, no asynchronous channel will ever overflow. A synchronous channel cannot be overflowed because the sending process is blocked until it receives the reply from the receiver, at which point the receiver is ready to receive another message.

Apart from the RT/PC paradigm, message passing in RT/PC has the following semantics:

• A process can only consume one message at a time; and

```

Process:

BEGIN

ACCEPT (msg);

:

A_EMIT (m1); /* Asynchronous emit */

:

S_EMIT (m2, reply); /* Synchronous emit */

:

END;

```

Figure 3: Schema for an RT/PC process

- messages may be sent to a process on several input channels; therefore

- the reception of messages has to be interleaved in time.

- The receiving process cannot select which input channel it wishes to receive a message from. The ACCEPT command will present it with the next message to process.

Because of the above, the temporal behaviour of a process is not determined by how it handles its connections, but by the input rate of its input port (bear in mind that all input channels of a process connect to one logical input port). One can therefore reason about the temporal behaviour of a process in terms of only the rate of its input port.

## 3.2.2 Input and output devices

Input and output devices are abstractions of the behaviour of the physical devices in the environment of a system. Because an RT/PC system is reactive it is driven by the events generated by devices in its environment. These events enter the system in the form of messages sent by input devices on asynchronous channels. Reactive systems usually control devices, and this is modeled in RT/PC by sending messages on asynchronous channels to output devices.

An input device behaves like a process which intermittently sends messages on an output channel. We assume that there is a nonzero interval between any two messages emitted by an input device, with a known lower bound. It is important to know the worst case (shortest) interval between messages from an input device, because it determines the rate of down tream channels.

An output device behaves like a process which is always ready to receive a message on an asynchronous channel, but does not emit messages back into the system. The reason for having output devices in a design is to determine the temporal behaviour of the system with regard to each device it controls.

### 3.2.3 Mutual exclusion regions and data repositories

Some processes which share access to data or devices have critical sections in their execution threads, which require exclusive access to the shared resource in order to execute correctly. RT/PC allows the definition of mutual exclusion regions which are sets of processes which must be guaranteed to execute mutually exclusively. A set of processes may be denoted explicitly to constitute a mutual exclusion region, by enclosing them in a box as shown in figure 2.

A data repository encapsulates data which are shared between processes. It behaves like a reactive process with a single input port for one or more synchronous channels. Processes send requests to the data repository, which processes each request atomically, and replies to the requesting process. In this way it serialises concurrent accesses to shared data, thus ensuring mutual exclusion. A data repository may not emit asynchronous messages — it may only respond synchronously to received synchronous messages. Data repositories therefore do not have any output ports. Figure 4 shows a schema for a data repository.

A process or data repository logically performs a single function. To ensure the predictable completion of each execution of this function, messages from multiple sources are not allowed to be processed simultaneously. Processes and data repositories are therefore allowed only one entry point where messages can be accepted. A process or data repository with multiple input channels forms an implicit mutual exclusion region.

Jeffay sets two restrictions on the use of mutual exclusion regions:

- Each component (process or data repository) may occur in at most one mutual exclusion region; and

- processes and data repositories may not be combined in one mutual exclusion region.

Jeffay does not give reasons for these restrictions, but deadlocks may occur if vertices are freely combined in mutual exclusion regions. A process and data repository in the same mutual exclusion region would be unable to communicate, because their execution is always

#### CHAPTER 3. THE REAL-TIME PRODUCER/CONSUMER (RT/PC) PARADIGM

Figure 4: A schema for an RT/PC data repository

interleaved in time.

## 3.2.4 Well-formedness of design graphs

Jeffay imposes two restrictions on the interconnections of processes:

- 1. There must exist a path from at least one input device to each process in the system.

- 2. A process may have any number of synchronous or asynchronous output channels; however, no two asynchronous output channels of a process may have the same receiver.

Jeffay calls a design that satisfies both restrictions well-formed. He also states that the first condition simplifies the analysis of RT/PC designs, the second implementation of RT/PC systems.

Every message in an RT/PC system ultimately originates from an input device. Therefore, if condition 1 does not hold, it means that a process in the design graph is unreachable. If a process is unreachable, its input channel rate functions cannot be solved, with the result that it is impossible to determine analytically whether the system will obey the RT/PC paradigm.<sup>2</sup> An unreachable process does not contribute to the system, but complicates the analysis.

Jeffay's statement about condition 2 presumably refers to the amount of buffering required. Recall that all input channels of a process logically connect to a single input port. If condition 2 holds a process cannot send more than one message to another process during the same execution cycle. This would mean that only one message needs to be buffered per input port if condition 2 is met; one per input channel if condition 2 is not met.

<sup>&</sup>lt;sup>2</sup>It is possible to determine analytically whether a system will obey the RT/PC paradigm if all the channel rate functions can be solved. This will be discussed in sections 3.4 and 3.6, as well as chapter 5.

# 3.3 Message passing semantics

Jeffay's design method specifies special temporal semantics for message passing. Every channel has one producer and one consumer of messages. All connected pairs of processes obey the RT/PC paradigm, which requires that whenever a message is produced on a channel, it will be consumed by the receiving process before the next message is produced on the same channel. The time interval in which a consumer may consume a message is therefore defined by the arrival rate of messages on the input port of that consumer.

### 3.3.1 Message transmission rates

Each channel in a design graph has an associated message transmission rate which is defined in terms of the worst case (shortest) inter arrival time of messages at the receiving process of the channel. If  $p_{min}$  is the shortest inter arrival time of messages on a channel, its rate is

$$r=\frac{1}{p_{min}},$$

where  $p_{min}$  is an integer multiple of a time unit of suitable granularity.

## 3.3.2 Restrictions on process construction

In order to ensure that a process can be guaranteed to obey RT/PC, Jeffay defines a number of restrictions on the construction of processes and data repositories in implementations.

- Process and data repositories are implemented in a sequential language in such a way that the execution time of each programming construct can be statically determined. In order to determine whether an RT/PC implementation is guaranteed to be temporally correct, the execution cost (timing) of each process must be determined accurately. Ideally the cost of each construct should be automatically determinable, possibly by the compiler for the implementation language. As such tools do not exist for most compilers used in real systems (such as C, Modula-2, etc), one has to revert to other tools to measure the timings of processes. This can be done accurately as long as the implementation language is sequential, and the execution of a thread is not interleaved with other threads.

- Potentially nonterminating constructs, such as loops, must contain a mechanism to ensure termination. An unbounded loop can easily occur when a loop is used to test for a

23

specific condition in a hardware device. If the condition never occurs (due to hardware malfunction, for example) the loop will not terminate. The worst case (longest) execution time for a loop must be used in the analysis of RT/PC systems. An upper bound must therefore exist on the number of times any loop may be executed. If a bound is not explicit in the loop condition, a special condition is required. One way of guaranteeing a bounded loop is to increment and test a special loop counter, and terminate the loop if an upper bound is exceeded. Another method would be to set and test a timer.

During the processing of a message, a process may emit only one message per asynchronous channel. This ensures that the receiver can be scheduled to process the message before another message is sent on the same channel.

# 3.4 Calculating channel input rates

In order to determine the precise semantics of an RT/PC system one must be able to calculate the transmission rates of all channels accurately. Synchronous channels are only used to connect processes with data repositories. To adhere to RT/PC a process must consume each message it receives within  $\frac{1}{r}$  time units, if r is the rate of its input port. If a process communicates with data repositories, all synchronous communications must be completed within  $\frac{1}{r}$  time units as well. The rate of synchronous channels are therefore determined by the rate of asynchronous channels.

# 3.4.1 Calculating message output rates

A channel's transmission rate is the rate at which the sending process connected to it transmits messages on that channel. The transmission rate of the process depends upon the rate at which it processes messages on its own input port. A transmission rate function is defined for each asynchronous channel, which maps the rate at which the sender process receives messages to the rate at which it emits messages on that channel. The time required to execute the code to process messages received on its input port, and the rate of the input port of a process determines the transmission rate function of each of the output channels of the process.

### CHAPTER 3. THE REAL-TIME PRODUCER/CONSUMER (RT/PC) PARADIGM

Figure 5: Message transmission rate function

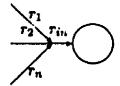

$$r_{in} = \sum_{i=1}^{n} r_i$$

Figure 6: Input rate definition for MP/SC processes

## 3.4.2 Calculating message input rates

The input rate of a process with only one input channel is equal to the message transmission rate of that channel. A process which receives messages on a set of input channels is required to obey RT/PC on each of those channels. Messages can arrive simultaneously on any number of the input channels of a process. A single buffer is therefore required for each input channel. If messages are buffered for input channels, the input rate of a multi-producer/single-consumer (MP/SC) process is equal to the aggregate rate of its input channels.

The rate of a channel connecting an input device to a process is simply the worst case rate at which the input device can produce messages.

If a design graph is acyclic and well-formed, the transmission rates on all asynchronous channels can always be calculated. These equations may be solved numerically or symbolically.

## 3.5 Scheduling results

In an implementation of an RT/PC design, the RT/PC system is represented by a set of communicating tasks<sup>3</sup>. To ensure that the implementation satisfies the temporal requirements

<sup>&</sup>lt;sup>3</sup>To differentiate between a design and its implementation, we refer to processes in a design graph, and tasks in an implementation task set.

of the design, it is necessary to find a way to schedule the traks in such a way that the RT/PC paradigm is preserved. Since RT/PC requires that a message is consumed before a certain deadline, a scheduling mechanism which can guarantee deadlines is required.

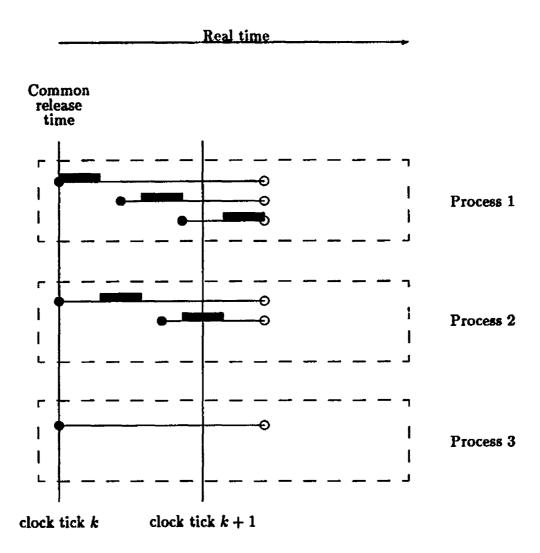

If a set of tasks is feasible it is possible to find a scheduling discipline which will ensure that every task will always meet its deadline. In order to find an optimal scheduling discipline which can support RT/PC systems, Jeffay examined the earliest deadline first (EDF) scheduling discipline with regard to RT/PC. The repetitive behaviour of RT/PC systems suggests the characterisation of an RT/PC process as a cyclic task, where a cyclic task is one that makes repeated requests for execution.

### Definition 4 A cyclic task T is a 3-tuple (s, c, p) were

- 1. s = start time (also called release time): the time of the first request for execution of T;

- 2. c = computational cost: the time to execute T to completion on a dedicated uniprocessor; and

- 3. p = period: the interval between requests for execution of task T.

Jeffay distinguishes between two types of cyclic task: sporadic and periodic. If a task makes requests for execution at regular intervals it is periodic, else sporadic. These two types of tasks are typical of two important characterisations of real-time systems: periodic in time driven and sporadic in event driven state machines [32].

In chapter 3 of his thesis, Jeffay proves feasibility and optimality results for the EDF scheduling discipline with regard to the RT/PC paradigm. The results of his investigation can be summarised as follows. For preemptive scheduling:

- EDF is an optimal discipline (see definition 2) if preemption is allowed at arbitrary points in a process. If a feasible schedule exists for a task set, and every process can be preempted at any point, the EDF discipline will correctly schedule the tasks.

- Feasibility of a task set can be determined analytically for arbitrary release times of both sporadic and periodic tasks.

#### For non-preemptive scheduling:

• EDF is an optimal discipline for sporadic tasks; but

- EDF is not an optimal discipline for periodic tasks with arbitrary release times.

- For sporadic tasks, feasibility can be determined efficiently for arbitrary release times; but

- for periodic tasks, feasibility is dependent on knowledge of release times, and the problem of determining the feasibility of a set of periodic tasks with arbitrary release times is intractable.

These results will be used in chapter 4, when the design of a kernel which supports RT/PC is considered.

# 3.6 Implementing RT/PC designs

The RT/PC paradigm requires that for every channel in a system, the receiver of the channel consumes messages faster than its producer emits messages on that channel. In order to determine whether a system is guaranteed to obey RT/PC, we have to reason about the temporal properties of a design graph. We do this in terms of the message transmission rates of the asynchronous channels of the design graph.

If the set of equations which describe the message transmission rate functions of a design graph can be solved, it means that the maximum input rate of messages on the input port of each process is known. We know from section 3.5 that the earliest deadline first (EDF) scheduling discipline is optimal for sporadic tasks. Therefore, given a fast enough processor, we can always schedule the processes of the design graph with the guarantee that each pair of connected processes will obey the RT/PC paradigm. Such a design graph is said to be realisable, meaning that there exists a mapping from it to a feasible task set.

**Definition 5** An implementation of a design graph is temporally correct if every pair of vertices connected with an asynchronous channel is guaranteed to adhere to the RT/PC paradigm.

**Definition 6** A design graph is realisable on a uniprocessor if it is possible to implement the design on a uniprocessor so that the design will be temporally correct.

Realisability is an absolute measure of temporal correctness. A realisable design graph can always be implemented given a fast enough processor, while a design graph which is not realisable cannot be implemented with guarantees of temporal correctness.

27

Jeffay proved that the following conditions are necessary and sufficient for realisability of design graphs:

- 1. Acyclic, well-formed design graphs are realisable.

- 2. Design graphs with disjoint cycles are realisable iff at least one channel in each cycle has a nonidentity transmission rate function. This will be discussed informally in chapter 5.

**Definition 7** Two cycles in a design graph are disjoint if no process appears in both cycles.

**Definition 8** If the transmission rate function, f(r), of a channel is defined by  $\frac{1}{x}r$ , then the slope of the transmission rate function is  $\frac{1}{x}$ .

We can now formally define the condition for realisability of a graph with disjoint cycles as follows:

**Definition 9** Let G be a design graph with a cycle C of n distinct processes and asynchronous channels. Let  $\frac{1}{x_1}, \frac{1}{x_2}, \ldots, \frac{1}{x_n}$  be the slopes for the transmission rate functions for the channels in C. If C is disjoint from other cycles in the graph, then the transmission rate functions for the channels in C can be solved iff

$$\prod_{i=1}^n x_i > 1$$

- 3. Design graphs with non-disjoint cycles are realisable only if the following two conditions are met:

- (a) At least one channel in each cycle has a nonidentity transmission rate function.

- (b) There must exist a process or sequence of processes in one of the cycles in a nondisjoint set of cycles, in which at least three messages must be sent to the first process in the sequence before a message can be emitted from the last process in the sequence. Formally:

Definition 10 A simple cycle in a design graph is a cycle in which all vertices are disjoint.

**Definition 11** Let G be a design graph with non-disjoint cycles. Let  $C_1$  and  $C_2$  be two non-disjoint, simple cycles. Assume that  $C_1$  and  $C_2$  contain n and m processes respectively. If processes in  $C_1$  are interconnected with channels whose transmission

rate functions have slopes  $\frac{1}{x_1}, \frac{1}{x_2}, \ldots, \frac{1}{x_n}$ , and processes in  $C_2$  are interconnected with channels whose transmission rate functions have slopes  $\frac{1}{y_1}, \frac{1}{y_2}, \ldots, \frac{1}{y_m}$ , then the transmission rate functions for the channels in  $C_1$  and  $C_2$  can be solved only if

28

$$(\prod_{i=1}^{n} x_i - 1)(\prod_{j=1}^{m} y_j - 1) > 1$$

We do not have sufficient conditions for when the transmission rate functions can be solved for arbitrary patterns of non-disjoint cycles. However, if each pair of simple cycles has at most a single process that receives messages from a distinct process in each cycle, then the necessary condition given above is also sufficient for solving the transmission rate functions.

Realisability analysis is called processor independent analysis because a realisable design graph can always be implemented on a fast enough uniprocessor. Temporal correctness is a measure of the correctness of an implementation of a design graph. The following chapters describe an experiment to investigate how realisable RT/PC design graphs can be implemented to be temporally correct.

# Chapter 4

# The ESE Kernel

In chapter 3 we discussed Jeffay's method of developing real-time systems with guaranteed temporal behaviour. He showed that his RT/PC<sup>1</sup> paradigm can be used to design systems with hard real-time constraints in such a way that all deadlines can be guaranteed. He also showed that RT/PC is realisable by developing a kernel which supports RT/PC design graphs, and by implementing a number of systems with hard real-time constraints on it [28].

Jeffay's system runs on the UNIX operating system on a Sun workstation, and interacts with devices at a very high level. I propose that RT/PC is also suitable for the design and implementation of general embedded reactive systems. In order to investigate this, I developed a nontrivial example on an industrial embedded platform. In chapter 5 we shall examine the implementation of the case study. To support RT/PC systems on an embedded platform I developed a kernel, called *Embedded Systems Executive* (ESE — pronounced "easy"), which runs on Intel 80x86 based hardware platforms. In this chapter we shall examine the design of this kernel.

# 4.1 Embedded Reactive Systems

Embedded systems are usually reactive. A reactive system is idle until an event occurs in its environment. The system performs certain actions in response to the event, and then awaits the next event. A state machine can be used to determine the reactive system's response to a particular event, given the current state of the system. The action taken by the reactive system in response to an event can change the state of the system. We can define a reactive

<sup>&</sup>lt;sup>1</sup>Real-Time Producer/Consumer

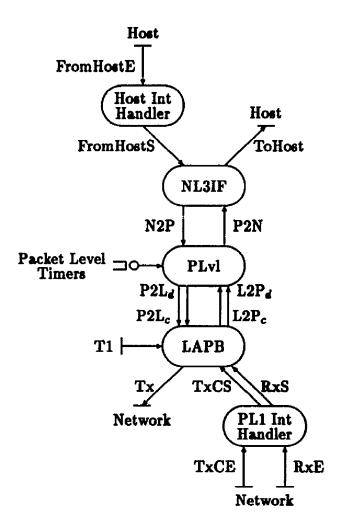

Figure 7: Reactive system

system as follows:

#### **Definition 12** A reactive system is an event driven state machine.

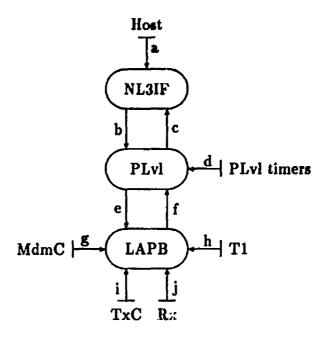

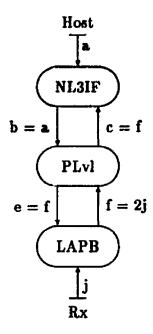

Figure 7 shows the components of a reactive system. Input events are generated by devices in the environment of the system. The driver process receives the events, and executes the state machine. The execution of the state machine typically causes output to be generated. The output may be control signals to a device, data written to a persistent data store, or messages sent to other processes in the system.

An embedded system is an autonomous component of a larger system. It can run on an autonomous hardware platform embedded in the hardware of the larger system. Examples of such systems are intelligent communications adapters, disk subsystems, etc.

Autonomous stand-alone systems often suffer the same problems as the embedded systems: hard real-time constraints, limited CPU, RAM and other resources, etc. Examples of such systems are robots with autonomous control systems.

A software system can also be embedded within a larger software system — in other words, run on the same hardware platform of the larger system. Examples of such systems are real-time systems which are embedded in general purpose operating systems.

The main characteristics of embedded systems are:

• Devices introduce concurrency — embedded systems usually interact with several autonomous devices. These devices introduce concurrency which is best modeled as a system of communicating processes.

- Devices have real-time requirements devices usually have to be serviced within specified temporal limits, otherwise information is lost. Many problems in embedded systems are timing related: a missed event because the system was engaged in another action, an overflowed buffer because a message consumer was too slow, etc.

- Reactive systems an event driven reactive system can be modeled very conveniently as

a system of communicating state machines. This requires inter process communication

and the guarantee of atomicity of state machine commands.

- Because of their "black box" nature, embedded systems can often be tested only in terms of their response to events from their actual environment. Certain sequences of events may be timing dependent, and very difficult to reproduce. It can therefore be very hard to find errors in embedded systems.

- Memory and CPU requirements are usually tight in embedded systems, and resources

have to be used optimally.

Conventional multi tasking operating systems do not adequately address the problems of embedded systems. The memory requirements of a general purpose operating system (UNIX, for example) is usually prohibitive, and the processing overhead it introduces, unacceptable. Furthermore, the process scheduling policy of general purpose operating systems is usually a variant of time sliced round robin scheduling with multiple levels of priority. This has the following implications:

- Real-time constraints cannot be guaranteed;