UNIVERSITEIT.STELLENBOSCH.UNIVERSITY jou kennisvennoot.your knowledge partner

### The Design and Testing of a Superconducting Programmable Gate Array

by

Hein van Heerden

Thesis presented at the University of Stellenbosch in partial fulfilment of the requirements for the degree of

Master of Science in Electronic Engineering

Department of Electrical and Electronic Engineering University of Stellenbosch Private Bag X1, 7602 Matieland, South Africa

Study leader: Dr. C.J. Fourie

December 2005

# Declaration

I, the undersigned, hereby declare that the work contained in this thesis is my own original work and that I have not previously in its entirety or in part submitted it at any university for a degree.

| Signature: |                            |

|------------|----------------------------|

| H. van H   |                            |

| Date:      | Peters reborant rathus ret |

## Abstract

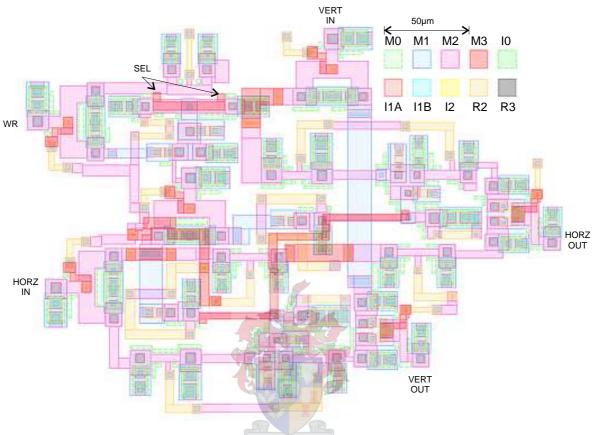

This thesis investigates to the design, analysis and testing of a Superconducting Programmable Gate Array (SPGA). The objective was to apply existing programmable logic concepts to RSFQ circuits and in the process develop a working prototype of a superconducting programmable logic device. Various programmable logic technologies and architectures were examined and compared to find the best solution. Using Rapid Single Flux Quantum (RSFQ) circuits as building blocks, a complete functional design was assembled incorporating a routing architecture and logic blocks. The Large-Scale Integrated circuit (LSI) layout of the final chip is presented and discussed followed by a discussion on testing. This thesis demonstrates the successful implementation of a fully functional reprogrammable logic device using RSFQ circuitry.

# Opsomming

Hierdie tesis handel oor die ontwerp, analise en toets van 'n SPGA (Superconducting Programmable Gate Array). Die doel is om huidige programeerbare logika konsepte aan te pas en in die proses 'n werkende prototipe te ontwikkel wat beskryf kan word as 'n supergeleier programeerbare logiese toestel wat se werking soortgelyk is aan dié van FPGAs. 'n Verskeidenheid van programeerbare logika tegnologieë en argitekture is ondersoek en met mekaar vergelyk om die beste oplossing te vind. Met RSFQ (Rapid Single Flux Quantum) stroombane as boublokke is 'n hele funksionele ontwerp aanmekaar gesit wat beide 'n verspreidingsargitektuur en logieseblokke inkorporeer. Die grootskaalse geïntegreerde stroombaan uitleg van die finale vlokkie word bespreek en voorgelê. Daarna volg 'n bespeking oor toetsing van die ontwerp. Hierdie tesis demonstreer die suksesvolle implementering van 'n werkende herprogrameerbare logika toestel bestaande uit RSFQ stroombane.

# Acknowledgements

I would like to express my sincere gratitude to the following people and organisations who have contributed to making this work possible:

- Steve R. Whiteley for his invaluable simulation tools, which made this project feasible.

- Hypres Inc. for providing the fabrication platform on which the physical implementation of this project is based. Especially Dr. S. Tolpygo, head of fabrication, for his help and direction.

- The National Research Foundation of South Africa (and Prof. D.B. Davidson as grantholder) for providing some financial assistance during my research.

- My fellow students and good friends, Hennie de Villiers and Wynand van Staden for providing inspiration and support during difficult times.

- Prof. Willem J. Perold for giving me the inspiration and opportunity to pursue my quest for further enrichment in the field of engineering. Also, for his eternal optimism and enthusiasm.

- Lastly, but most of all, Dr. Coenrad J. Fourie as my study leader for the countless hours of advice and guidance and also for providing me with a good background and basis on which to build this project.

# Dedications

This thesis is dedicated to my mother for her support, encouragement and eternal love. Sadly, she passed away before the completion of this project. She will be missed.

# Contents

| D  | eclara          | ation                            | ii  |  |

|----|-----------------|----------------------------------|-----|--|

| A  | bstrac          | ct                               | iii |  |

| 0  | psom            | ming                             | iv  |  |

| A  | cknov           | wledgements                      | v   |  |

| D  | edica           | tions                            | vi  |  |

| Co | onten           | its                              | vii |  |

| Li | st of ]         | Figures                          | xi  |  |

| Li | st of '         | Tables                           | xiv |  |

| N  | Nomenclature xv |                                  |     |  |

| 1  | Intr            | oduction                         | 1   |  |

|    | 1.1             | Semiconductor programmable logic | 1   |  |

|    | 1.2             | Superconducting logic            | 1   |  |

|    | 1.3             | SPGA                             | 2   |  |

|    | 1.4             | Summary of thesis                | 2   |  |

| 2  | SPG             | GA background and RSFQ basics    | 3   |  |

|    | 2.1             | SPGA background                  | 3   |  |

|    | 2.2             | RSFQ basics                      | 4   |  |

| 3  | Prog            | grammable logic                  | 7   |  |

|    | 3.1             | Field-programmable gate array    | 7   |  |

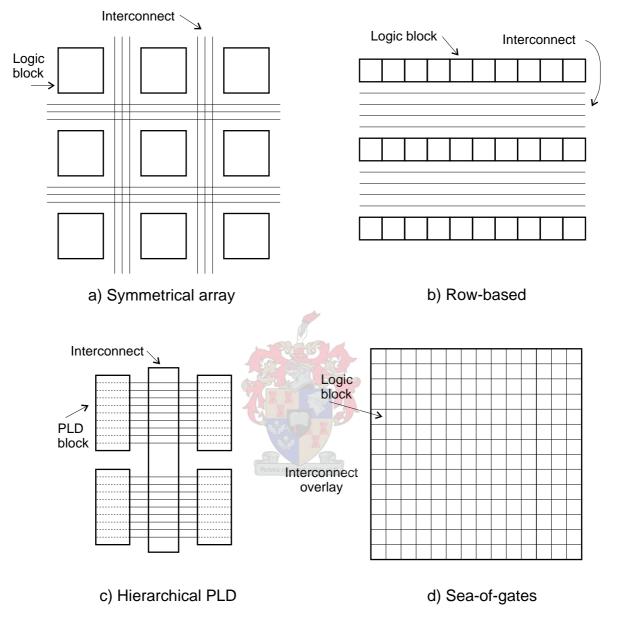

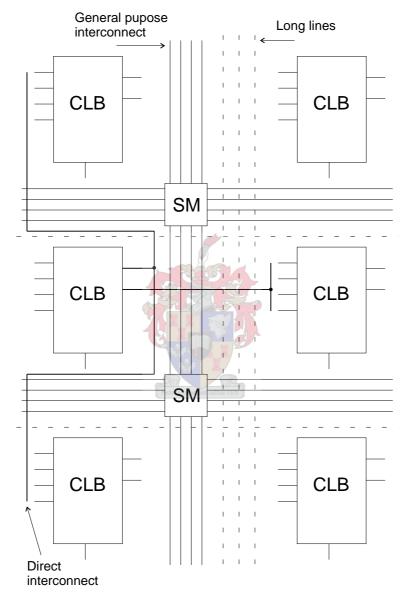

|    |                 | 3.1.1 Architectures              | 7   |  |

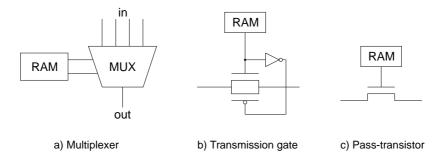

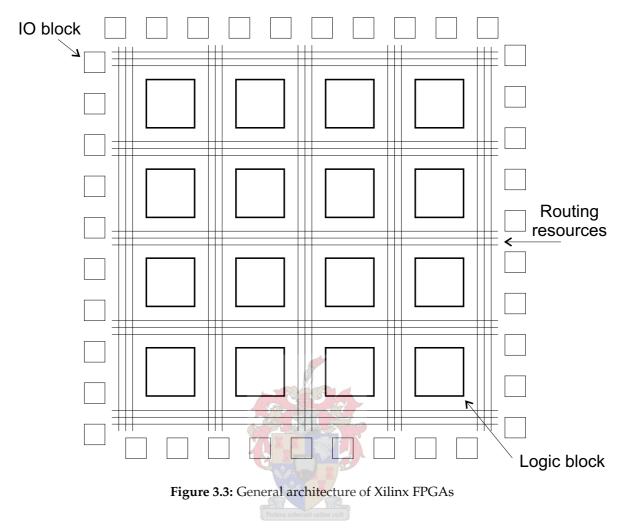

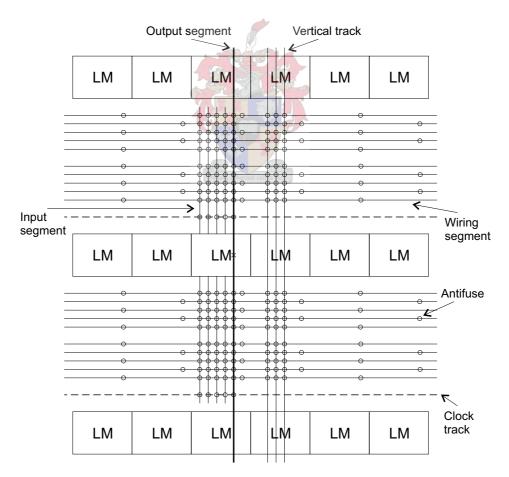

|    |                 | 3.1.2 Programming technologies   | 9   |  |

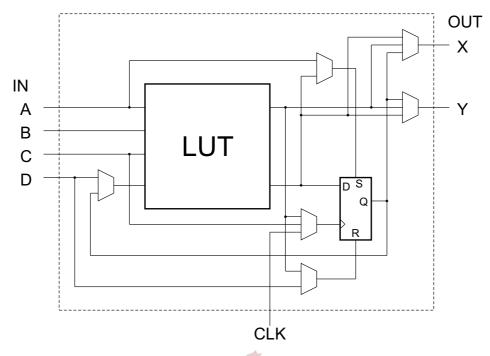

|    |                 | 3.1.3 Implementation             | 11  |  |

|   | 3.2        | Technology mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6         |

|---|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|   |            | 3.2.1 Lookup table mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6         |

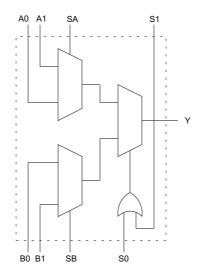

|   |            | 3.2.2 Multiplexer mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7         |

|   |            | 3.2.3 Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7         |

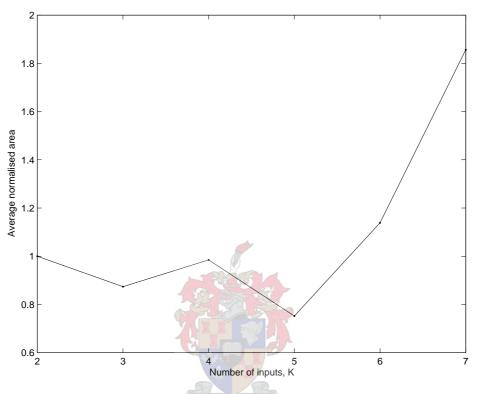

|   | 3.3        | Area vs Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4         |

|   |            | 3.3.1 Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .4        |

|   |            | 3.3.2 Logic block area and routing model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .4        |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25        |

|   | 3.4        | SPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28        |

|   | 3.5        | Chapter summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9         |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| 4 |            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>80</b> |

|   | 4.1        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0         |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60        |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32        |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4         |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5         |

|   |            | I THE PARTY OF THE | 6         |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8         |

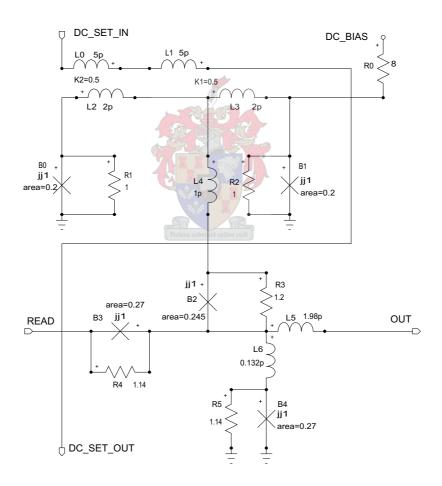

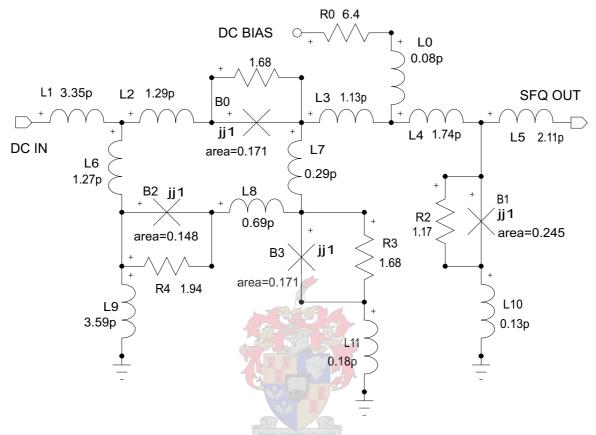

|   | 4.2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9         |

|   | 4.3        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9         |

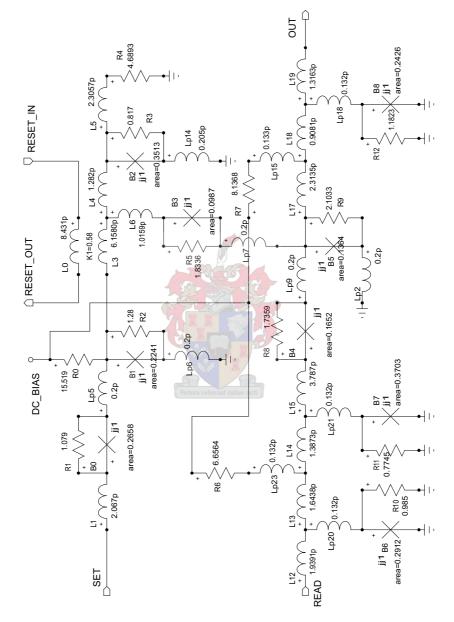

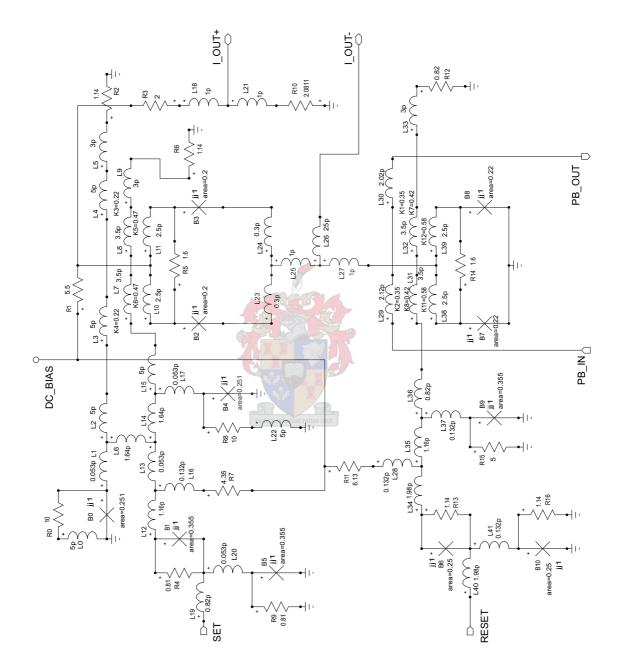

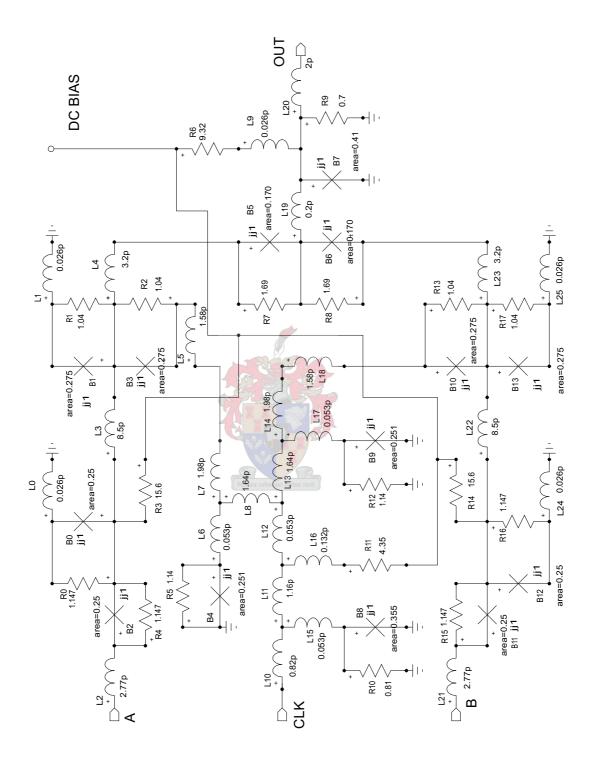

|   | 4.4        | Composite blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0         |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0         |

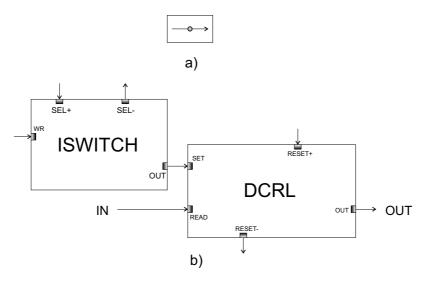

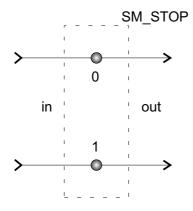

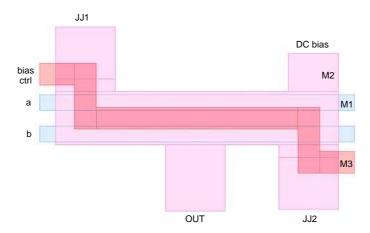

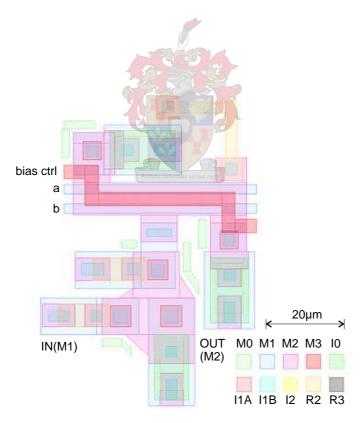

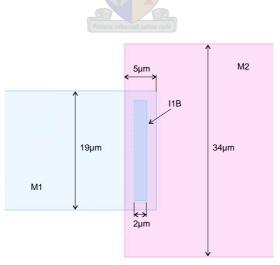

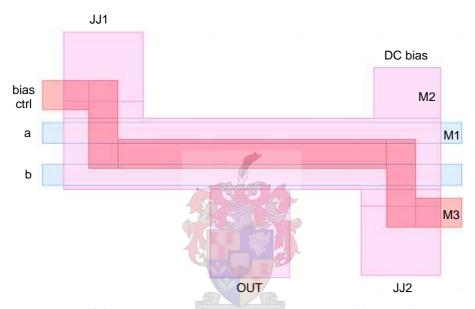

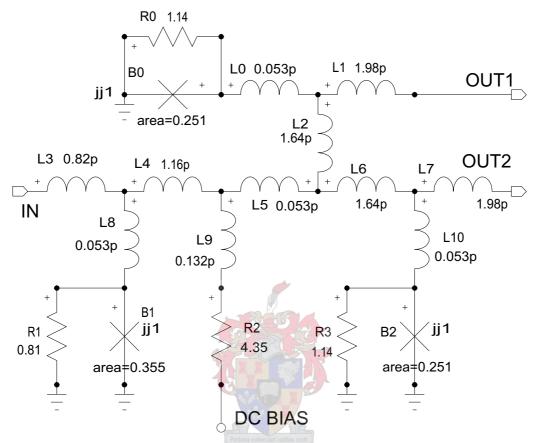

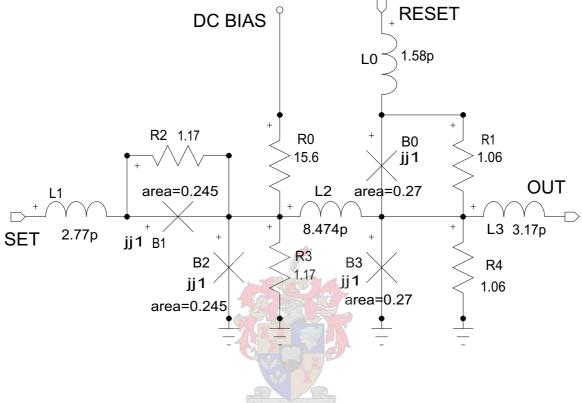

|   |            | 4.4.2 Junction Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0         |

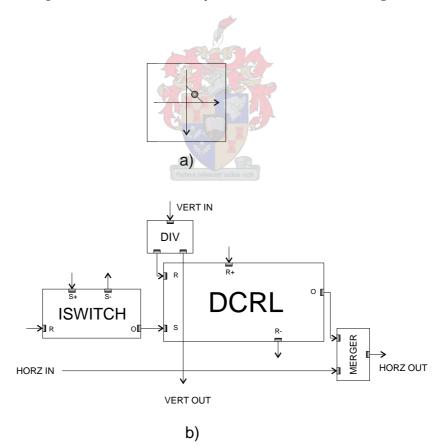

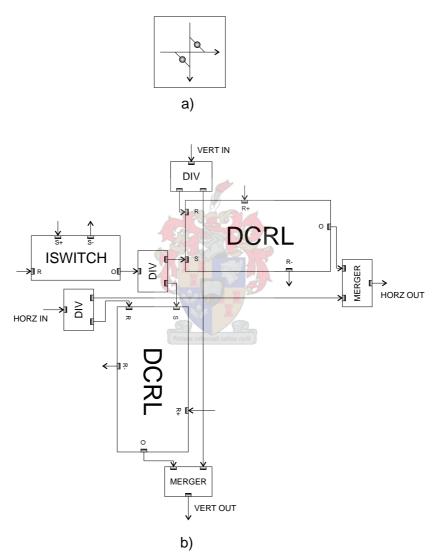

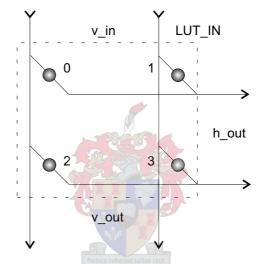

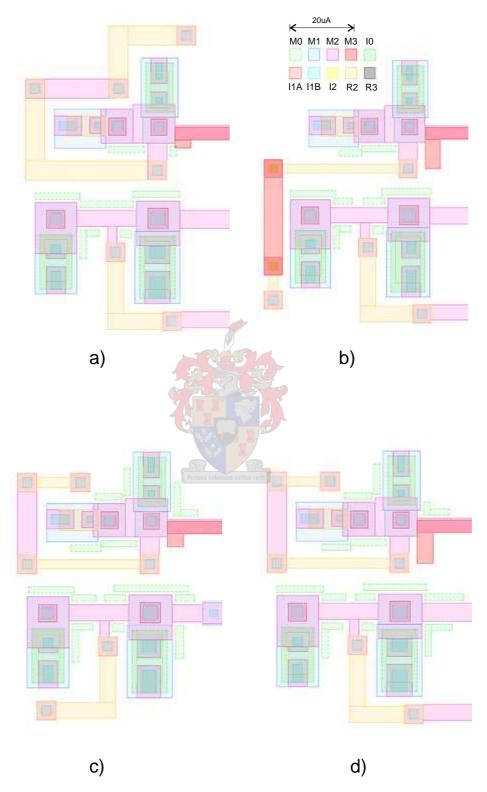

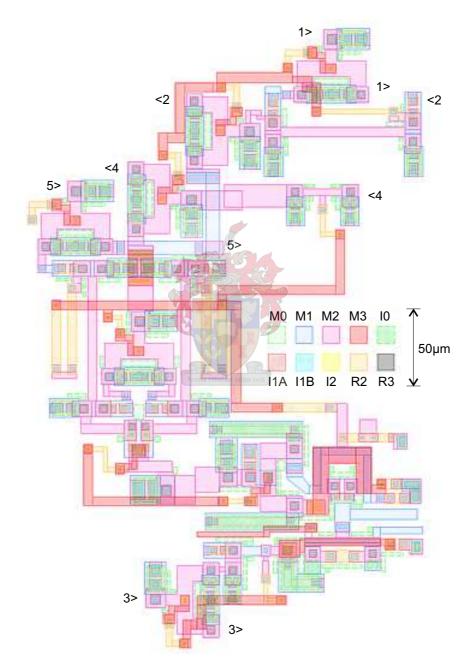

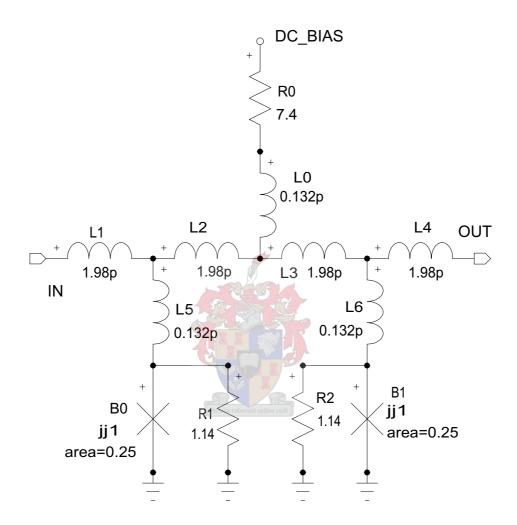

|   |            | 4.4.3 Crossbar Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2         |

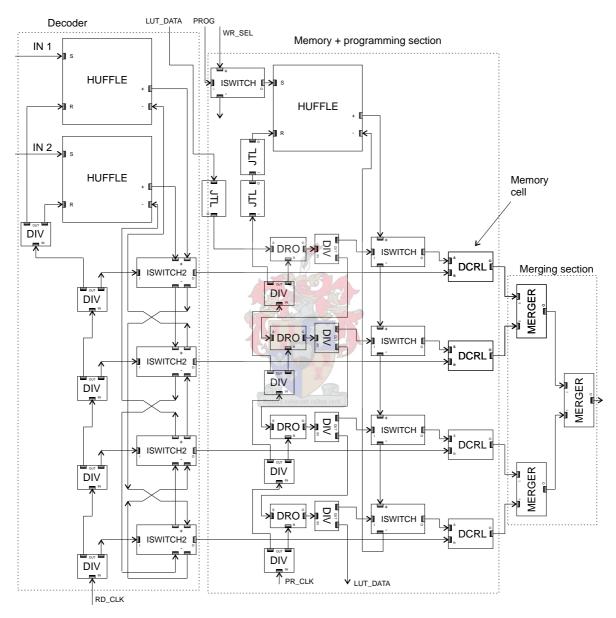

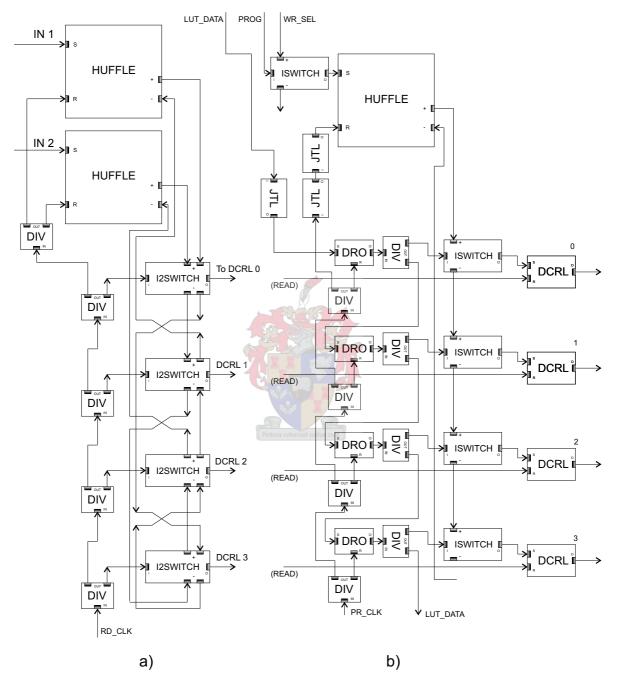

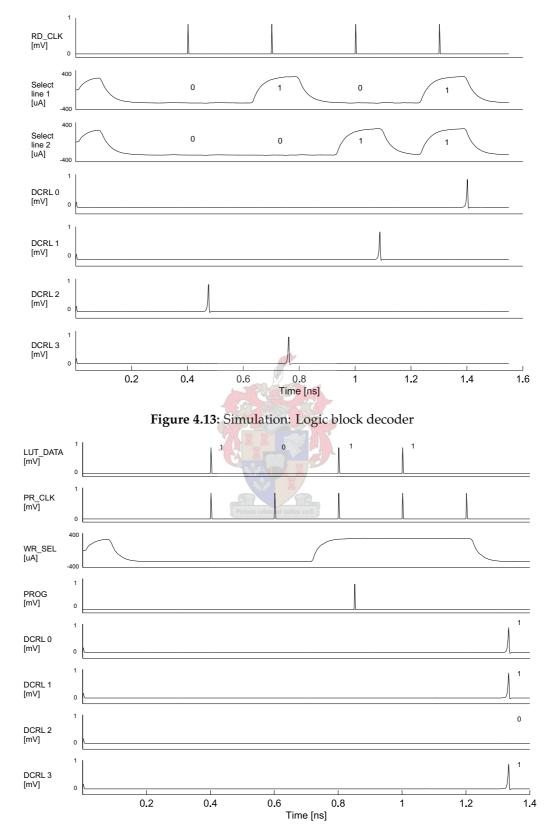

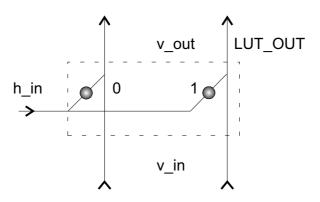

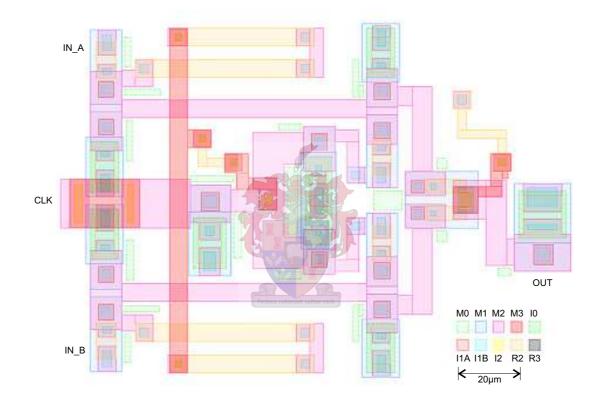

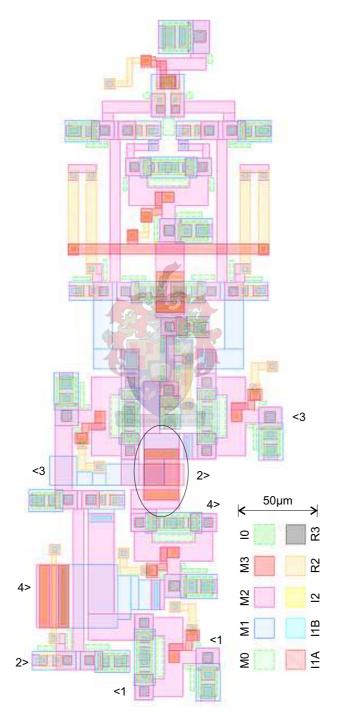

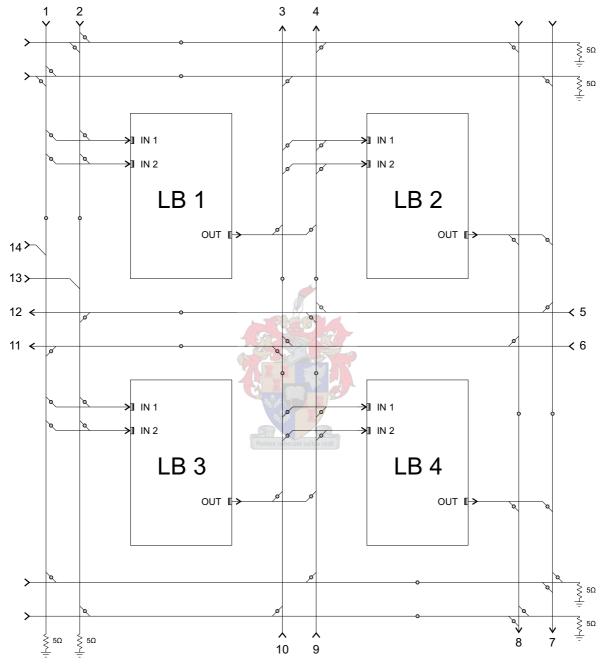

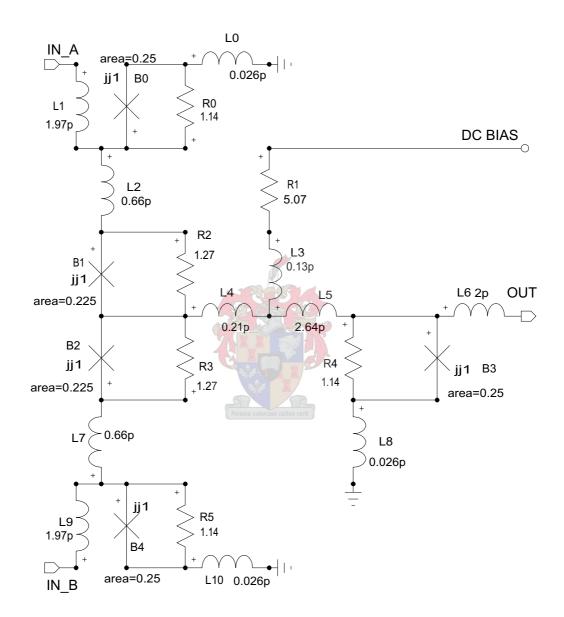

|   |            | 4.4.4 Logic Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3         |

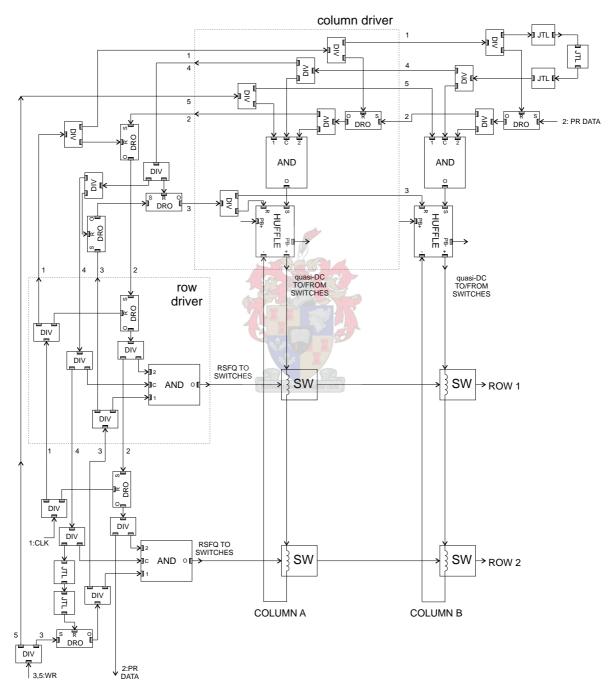

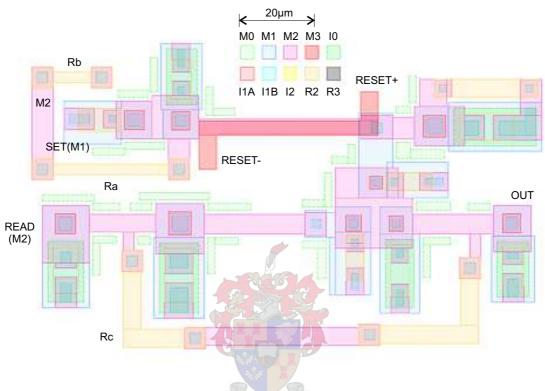

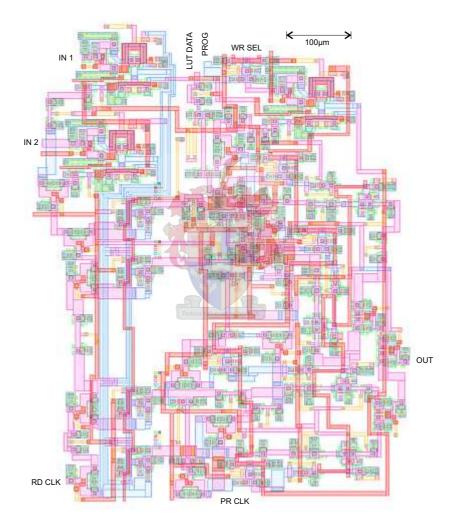

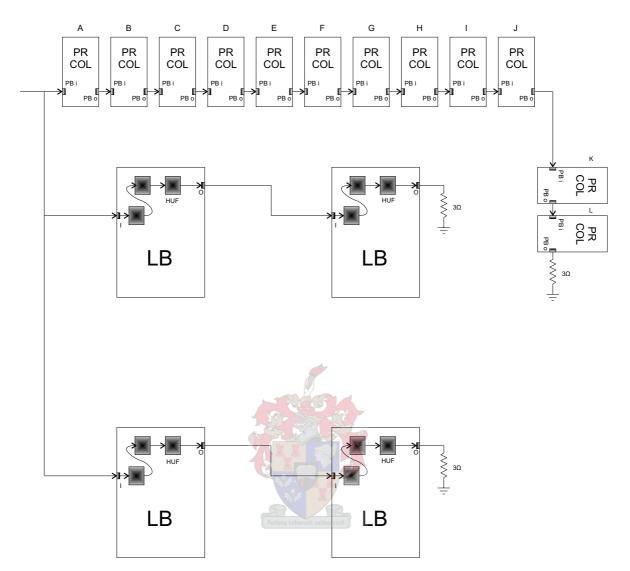

|   |            | 4.4.5 Programming Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7         |

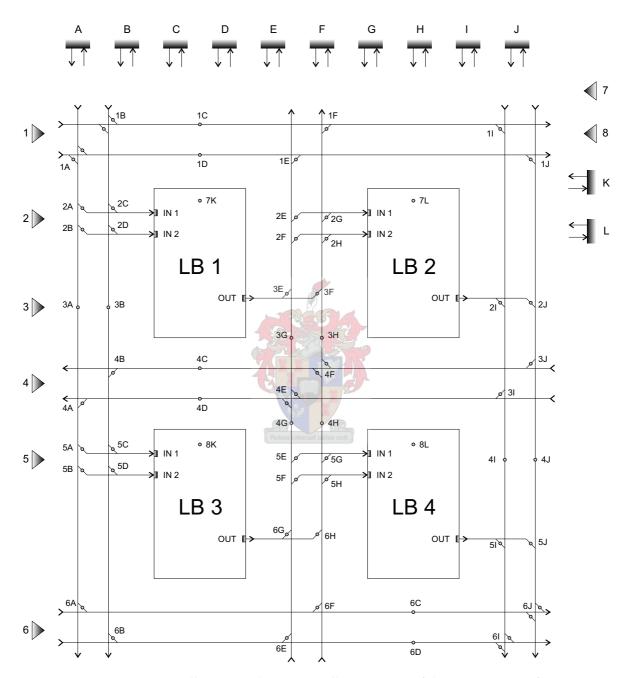

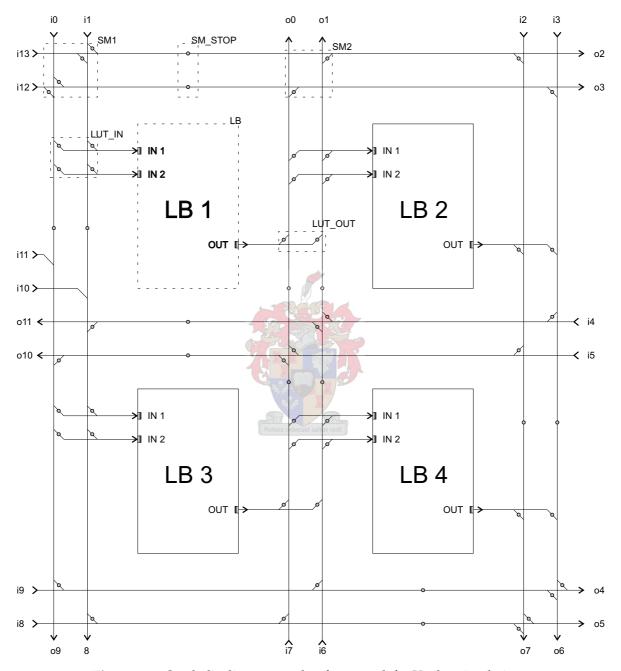

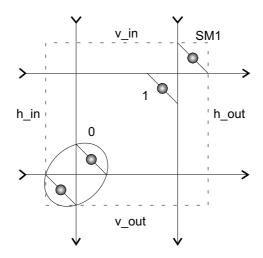

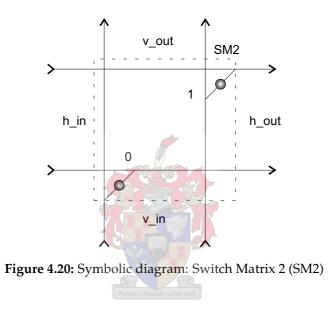

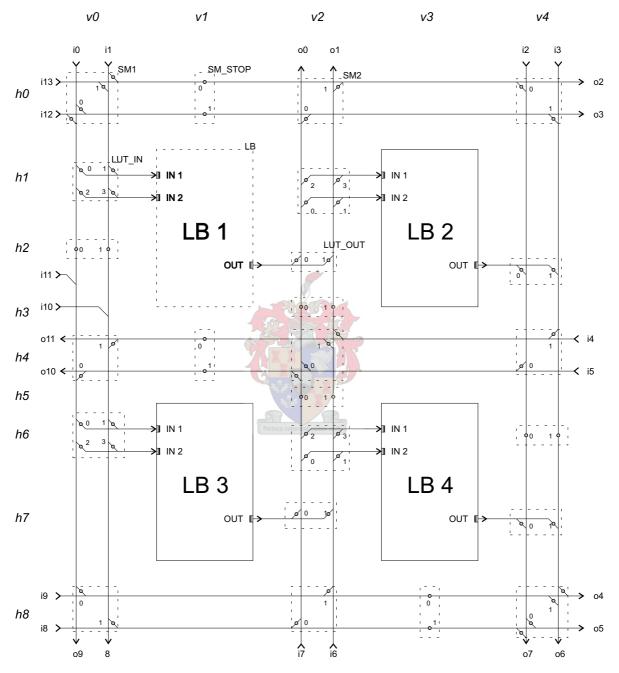

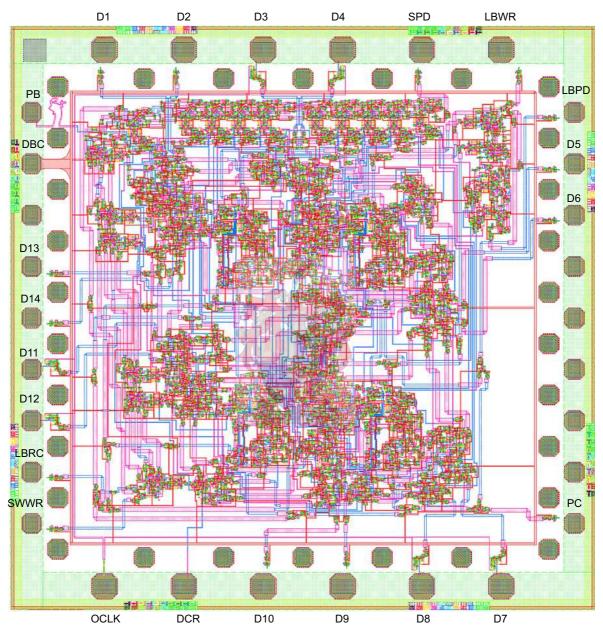

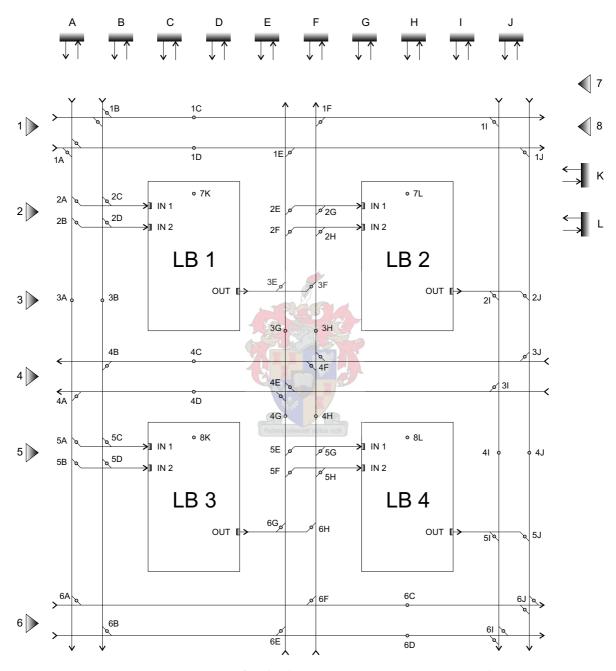

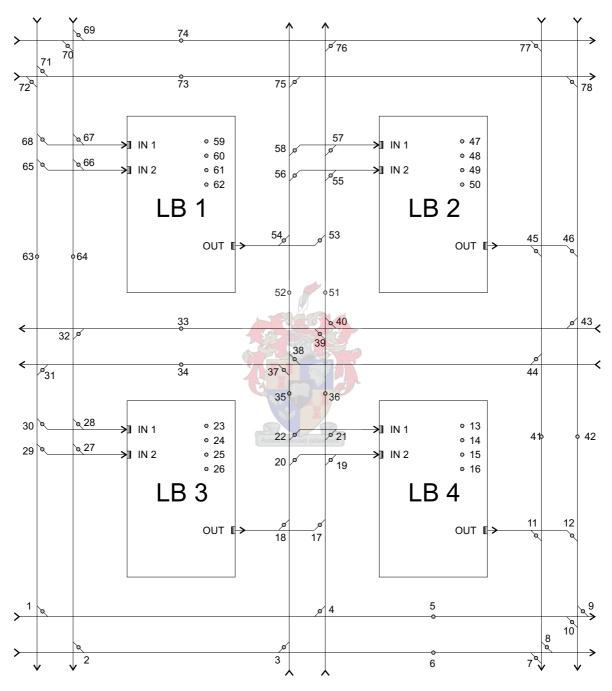

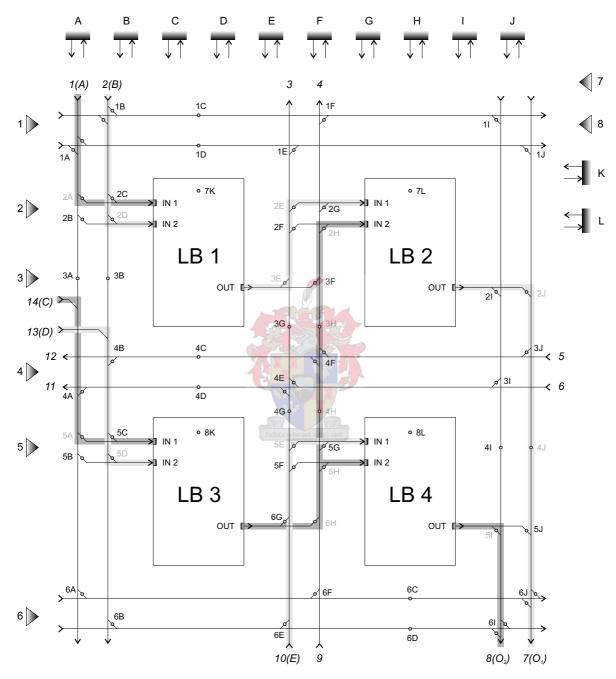

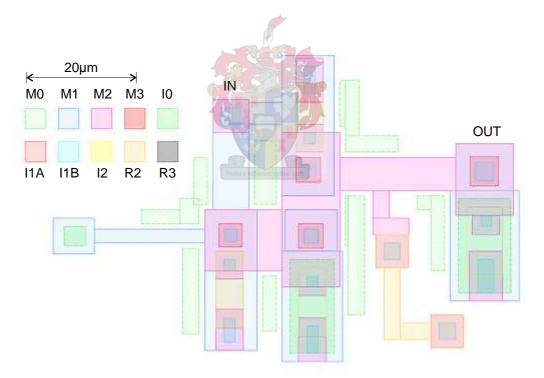

|   | 4.5        | SPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50        |

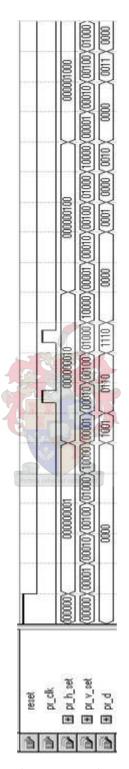

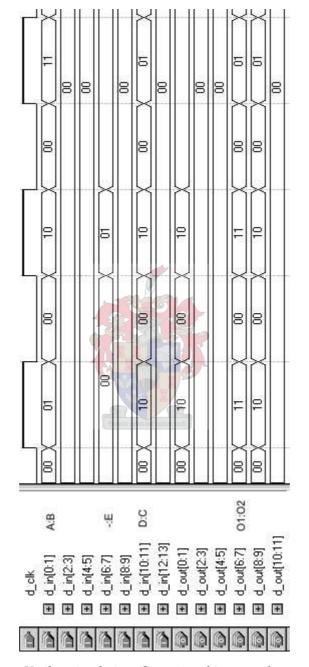

|   | 4.6        | Functional Verilog simulation of the SPGA 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1         |

|   |            | 4.6.1 Functional models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51        |

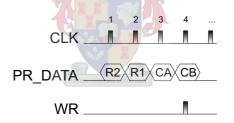

|   |            | 4.6.2 Programming and simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6         |

|   | 4.7        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52        |

| _ | D1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ~         |

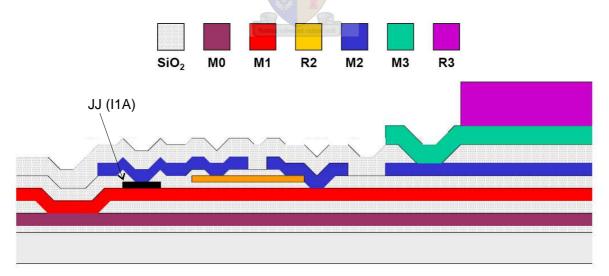

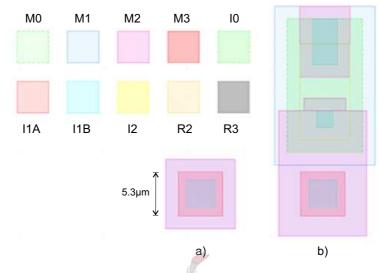

| 5 |            | ,<br>,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53<br>E   |

|   | 5.1<br>5.2 | 5 6 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5         |