# GaN Microwave Power FET Nonlinear Modelling Techniques

by

**Clive Raymond Brooks**

Thesis presented in partial fulfilment of the requirements for the degree of Master of Science in Engineering at Stellenbosch University

Supervisor: Dr. Cornell van Niekerk Department of Electrical and Electronic Engineering

March 2010

## Declaration

By submitting this thesis electronically, I declare that the entirety of the work contained therein is my own, original work, that I am the owner of the copyright thereof (unless to the extent explicitly otherwise stated) and that I have not previously in its entirety or in part submitted it for obtaining any qualification.

March 2010

Copyright © 2010 Stellenbosch University

All rights reserved

#### Abstract

The main focus of this thesis is to document the formulation, extraction and validation of nonlinear models for the on-wafer gallium nitride (GaN) high-electron mobility (HEMT) devices manufactured at the Interuniversity Microelectronics Centre (IMEC) in Leuven, Belgium. GaN semiconductor technology is fast emerging and it is expected that these devices will play an important role in RF and microwave power amplifier applications. One of the main advantages of the new GaN semiconductor technology is that it combines a very wide band-gap with high electron mobility, which amounts to higher levels of gain at very high frequencies. HEMT devices based on GaN, is a fairly new technology and not many nonlinear models have been proposed in literature. This thesis details the design of hardware and software used in the development of the nonlinear models. An intermodulation distortion (IMD) measurement setup was developed to measure the second and higher-order derivative of the nonlinear drain current. The derivatives are extracted directly from measurements and are required to improve the nonlinear model IMD predictions. Nonlinear model extraction software was developed to automate the modelling process, which was fundamental in the nonlinear model investigation. The models are implemented in Agilent's Advanced Design System (ADS) and it is shown that the models are capable of accurately predicting the measured S-parameters, large-signal singletone and two-tone behaviour of the GaN devices.

### Opsomming

Die hoofdoel van hierdie tesis is om die formulering, ontrekking en validasie van nie-lineêre modelle vir onverpakte gallium nitraat (GaN) hoë-elektronmobilisering transistors (HEMTs) te dokumenteer. Die transistors is vervaaardig by die Interuniversity Microelectronics Centre (IMEC) in Leuven, België. GaN-halfgeleier tegnologie is besig om vinnig veld te wen en daar word voorspel dat hierdie transistors 'n belangrike rol gaan speel in RF en mikrogolf kragversterker toepassings. Een van die hoof voordele van die nuwe GaN-halfgeleier tegnologie is dat dit 'n baie wyd band-gaping het met hoë-elektronmobilisering, wat lei tot hoë aanwins by mikrogolf frekwensies. GaN HEMTs is 'n redelik nuwe tegnologie en nie baie nie-lineêre modelle is al voorgestel in literatuur nie. Hierdie tesis ondersoek die ontwerp van die hardeware en sagteware soos gebruik in die ontwikkeling van nie-lineêre modelle. 'n Intermodulasie distorsie-opstelling (IMD-opstelling) is ontwikkel vir die meting van die tweede en hoër orde afgeleides van die nie-lineêre stroom. Die afgeleides is direk uit die metings onttrek en moet die nie-lineêre IMD-voorspellings te verbeter. Nie-lineêre onttrekking sagteware is ontwikkel om die modellerings proses te outomatiseer. Die modelle word geïmplementeer in Agilent se Advanced Design System (ADS) en bewys dat die modelle in staat is om akkurate afgemete S-parameters, grootsein enkeltoon en tweetoon gedrag van die GaN-transistors te kan voorspel.

### Acknowledgements

I would like to convey my deepest and sincere gratitude to the following people who have made a significant contribution to making this thesis possible:

- Dr. Cornell van Niekerk for the endless effort in supporting me in every possible way and affording me the opportunity to complete my practical measurements at IMEC in Leuven, Belgium. The experience was truly unforgettable and I will always be truly thankful for this opportunity. Finally, thank you for your enthusiasm and patience in explaining difficult concepts over a hot cup of Plakkies coffee. Working with you was truly motivational.

- Dominique Schreurs and Giovani Crupi from the department of electrical engineering (ESAT) at the Catholic University Leuven, Belgium, for helping me to understand the difficult concepts of nonlinear modelling and for assisting in nonlinear measurements in Leuven.

- Ughem and Frederik for helping me find my feet at IMEC and for assisting in making the practical measurements, as well as the opportunity to learn from your expertise.

- Prof. J.C Pedro for helping me with the IMD measurement setup and giving me the opportunity to visit the University of Averio.

- Wessel Croukamp and Lincoln Saunders for the advice and manufacturing of the test fixtures.

- Martin Siebers for always being available to help with the tricky measurements in the high frequency laboratory.

- To all my friends and people that I have forgotten to mention that have made a contribution, no matter how small, in supporting me through my life.

- Finally, to my parents, Raymond and Estelle Brooks, for putting up with my extended university career, for your overwhelming support and love throughout the years. You have truly given me an incredible opportunity and I shall always be thankful.

# Content

| Declarationi                                              |

|-----------------------------------------------------------|

| Abstractii                                                |

| Opsommingiii                                              |

| Acknowledgementsiv                                        |

| List of Figures                                           |

| List of Tables xix                                        |

| Chapter 1: Introduction 1                                 |

| 1.1 Introduction                                          |

| 1.2 Overview of Nonlinear Modelling Techniques 1          |

| 1.3 Introduction to Nonlinear Equivalent Circuit Models   |

| 1.4 Scope and Layout of this Study                        |

| Chapter 2: Device Characterisation and Measurement Setups |

| 2.1 Introduction                                          |

| 2.2 GaN HEMT Technology                                   |

| 2.3 Device Characterisation                               |

| 2.4 Linear and Nonlinear Measurement Setups               |

| 2.4.1 Vector Network Analyser                             |

| 2.4.2 Large-Signal Network Analyser                       |

| 2.5 Conclusion                                            |

| Chapter 3:Intermodulation Distortion Characterization     |

| 3.1 Introduction                                          |

| 3.2 Origin of Nonlinear Distortion Behaviour              |

| 3.3 Principles of Volterra Series Analysis                |

| 3.3.1 Nonlinear Currents Method                           |

| 3.3.2 The Substitution Theorem                            |

| 3.4 Nonlinear Taylor Series IMD Model                     |

| 3.5 IMD Characterization Procedure                        |

| 3.5.1 IMD Measurement Setups                              |

| 3.5.2 Phase Information                                                  | 33  |

|--------------------------------------------------------------------------|-----|

| 3.5.3 De-Embedding Procedure                                             | 34  |

| 3.5.4 Measurement Extraction Procedure                                   | 37  |

| 3.6 Extraction Methodology                                               | 43  |

| 3.7 Extraction Results                                                   | 47  |

| 3.8 Conclusion                                                           | 49  |

| Chapter 4: Nonlinear Model Formulation                                   | 50  |

| 4.1 Introduction                                                         | 50  |

| 4.2 Nonlinear Modelling Procedure                                        | 51  |

| 4.3 Linear Modelling                                                     | 52  |

| 4.3.1 Small-Signal Equivalent Circuit Model                              | 53  |

| 4.3.2 Extrinsic and Intrinsic Parameter Extraction                       | 55  |

| 4.4 Nonlinear Modelling                                                  | 59  |

| 4.4.1 Nonlinear Model Formulation                                        | 59  |

| 4.5 Nonlinear Model Investigation and Construction                       | 64  |

| 4.5.1 Construction of Table-Based Integration Function                   | 64  |

| 4.5.2 Investigation of the Integration Starting Points                   | 66  |

| 4.5.3 Root Model versus Modified Root Model                              | 74  |

| 4.5.4 Analytical Modelling of the Drain Current Source                   |     |

| 4.5.5 Incorporating Measured Gradient into the Fager Drain Current Model | 83  |

| 4.6 Conclusion                                                           | 90  |

| Chapter 5: Nonlinear Model Validation                                    | 91  |

| 5.1 Introduction                                                         | 91  |

| 5.2 Error Functions                                                      | 91  |

| 5.3 Simulation Models                                                    | 93  |

| 5.4 Nonlinear Model Verification                                         | 96  |

| 5.4.1 Linear S-Parameters                                                |     |

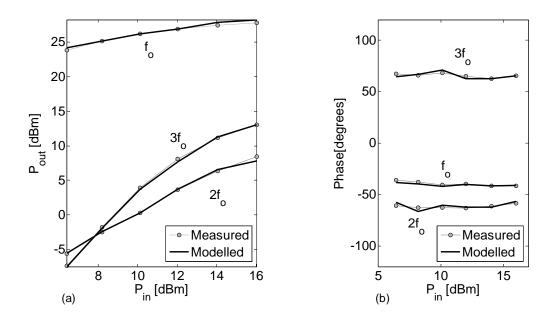

| 5.4.2 Large-Signal Single-Tone                                           | 106 |

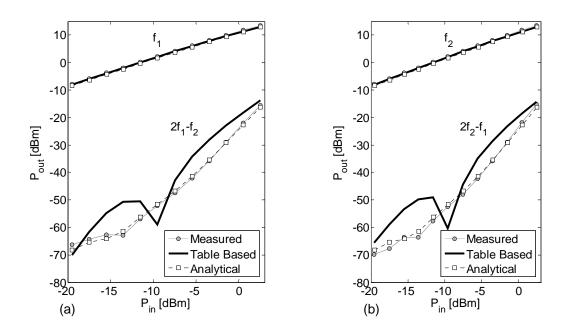

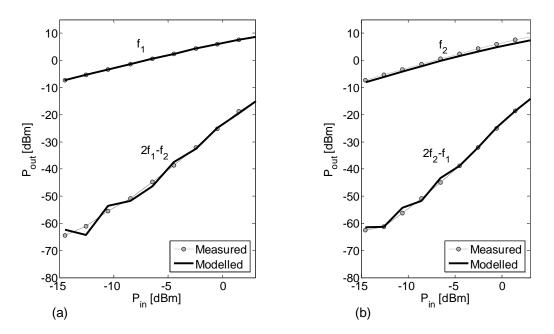

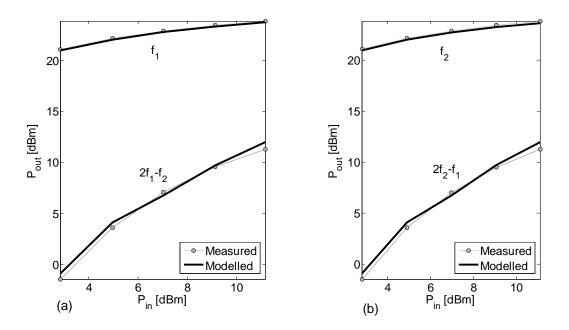

| 5.4.3 Large-Signal Two-Tone IMD                                          | 110 |

| 5.5 Conclusion                                                           | 112 |

| Chapter 6: Conclusion               | 114 |

|-------------------------------------|-----|

| 6.1 Introduction                    | 114 |

| 6.2 Overview and Conclusions        | 114 |

| 6.3 Future Work and Recommendations | 116 |

|                                     |     |

| References                          | 117 |

|   | ٠ | ٠ |

|---|---|---|

| V | 1 | 1 |

| • | - | - |

# List of Figures

# Chapter 1

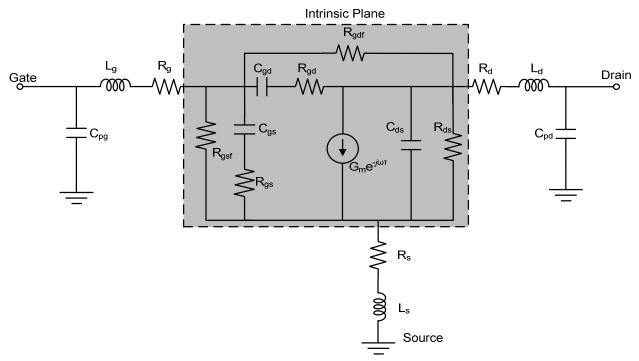

| Figure 1.1 | The typical small-signal equivalent circuit for a field effect transistor (FET) | 3 |

|------------|---------------------------------------------------------------------------------|---|

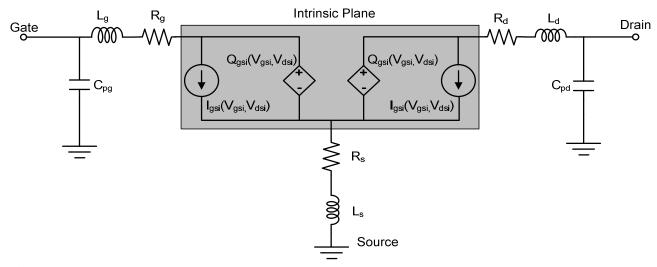

| Figure 1.2 | The transformed state-space nonlinear model representation.                     | 4 |

# Chapter 2

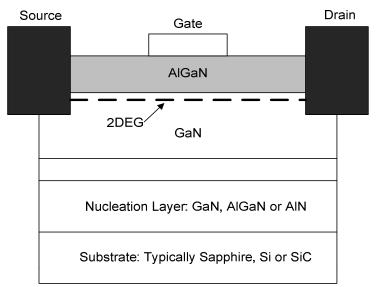

| Figure 2.1 The basic structure of a HEMT device                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

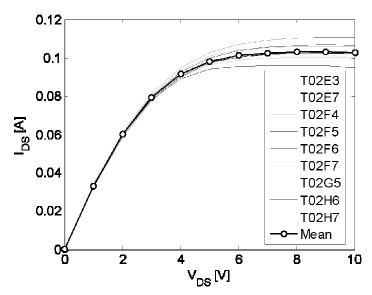

| Figure 2.2 The different DC drain current curves for devices of the same topology                                                                                                                    |

| Figure 2.3 The vector network analyser (VNA) measures both the magnitude and phase of all the complex S-parameters at the fundamental frequency of a device under test (DUT) 11                      |

| Figure 2.4 The HP8510C vectorial network analyser (VNA) was used to measure the linear S-<br>parameters of the on-wafer GaN HEMT devices at IMEC 11                                                  |

| Figure 2.5 The measurement probes are placed at the gate and drain terminal of the device. A microscope is used to display the image on a monitor in order to help with the placement of the probes  |

| Figure 2.6 The image of the magnified $T_{02}$ device topology is displayed on the monitor, which is used to accurately place the probes at the precise locations at the gate and drain terminals.12 |

| Figure 2.7 The vector large-signal vector network analyser (LSNA) measures both the magnitude and phase of all the complex S-parameters at all the harmonics of a device under test (DUT)            |

| Figure 2.8 A photograph of the large-signal network analyser (LSNA) set-up used at the ESAT-<br>TELEMIC lab. The system has a RF bandwidth of 600MHz to 20GHz                                        |

| Figure 2.9 The modified LSNA with the external Picosecond bias-tee used to perform the large-<br>signal two tone measurements                                                                        |

# Chapter 3

| Figure 3.1 (a) Shows the plot of measured DC drain current $I_{DS}$ , while (b) shows a noisy $G_m$ which was obtained by directly differentiating $I_{DS}$ . In (c) an extremely noise $G_{m2}$ is plotted which was determined by differentiating $G_m$                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.2 A nonlinearity excited by voltage source V <sub>s</sub> with the current a nonlinear function of the voltage V, across the nonlinear device is used to demonstrate the mathematical origin of intermodulation distortion                                                                                                                                                         |

| Figure 3.3 The distribution of harmonics and intermodulation products are plotted versus frequency for a two-tone excitation $\omega_1$ and $\omega_2$ . It can be seen that intermodulation products fall within the pass band                                                                                                                                                             |

| Figure 3.4 The circuit used to demonstrate the nonlinear currents method consists of a voltage source $v_s(t)$ , a linear resistor R and a weakly defined nonlinearity with a voltage drop of $v(t)$                                                                                                                                                                                        |

| Figure 3.5 In (a) the nonlinear resistor has been converted to a linear resistor and a set of nonlinear current sources. In (b) the current sources have been rearranged so that each represents a single order of mixing products                                                                                                                                                          |

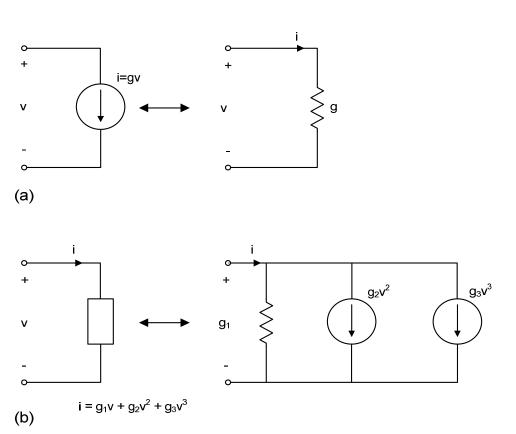

| Figure 3.6 (a) A linear-voltage controlled source $i = gv$ can be substituted by a current source<br>with a conductance g and the current will be unchanged. In (b) a nonlinear conductance<br>described by the power series $i = g_1 v + g_2 v^2 + g_3 v^3$ is replaced by a linear conductance $g_1$<br>and controlled current sources representing the higher degree terms in the series |

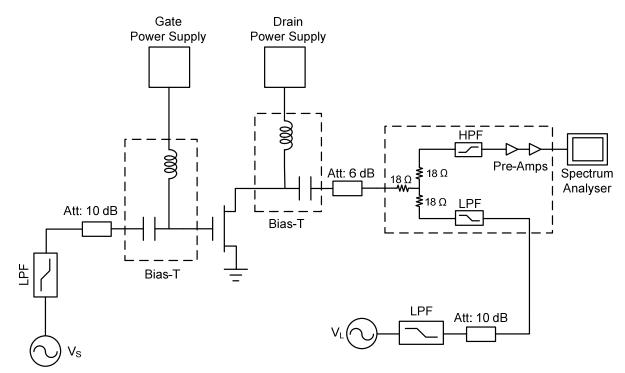

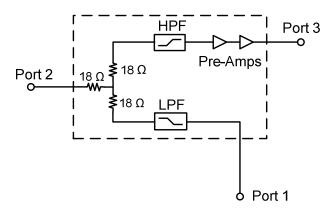

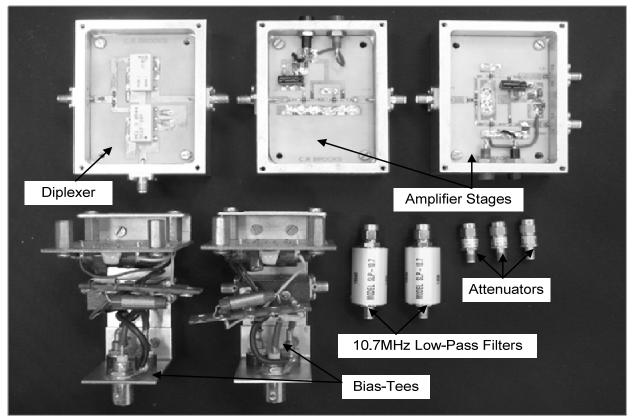

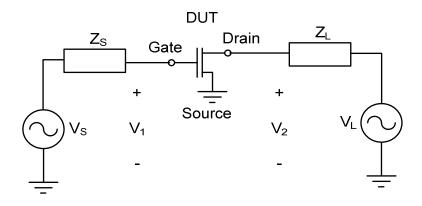

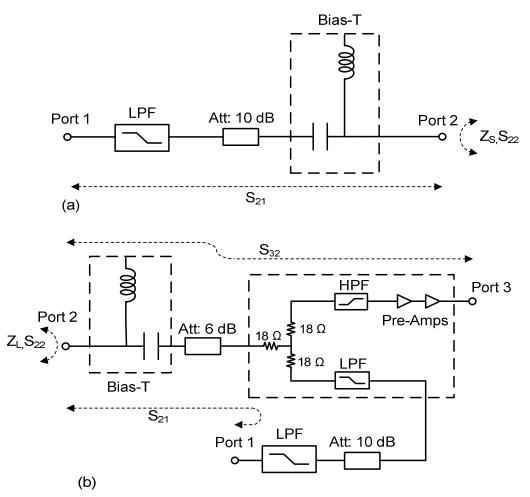

| Figure 3.7 The block diagram of the low frequency IMD measurement setup used to extract the nonlinear coefficients of the drain current $I_{ds}(V_{gs}, V_{ds})$                                                                                                                                                                                                                            |

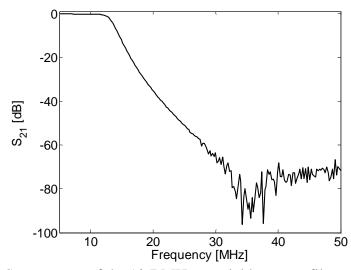

| Figure 3.8 The $S_{21}$ response of the 10.7 MHz coaxial low-pass filter                                                                                                                                                                                                                                                                                                                    |

| Figure 3.9 The circuit diagram of the diplexer and amplifier stages with the port allocations measured on the Network analyser                                                                                                                                                                                                                                                              |

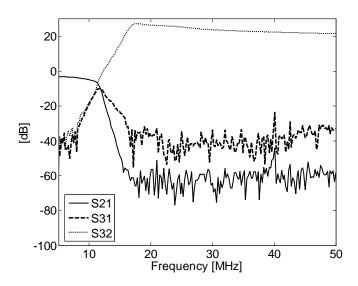

| Figure 3.10 The transmission coefficients S <sub>21</sub> , S <sub>31</sub> and S <sub>32</sub> measurements of the diplexer and the amplifier stage combined                                                                                                                                                                                                                               |

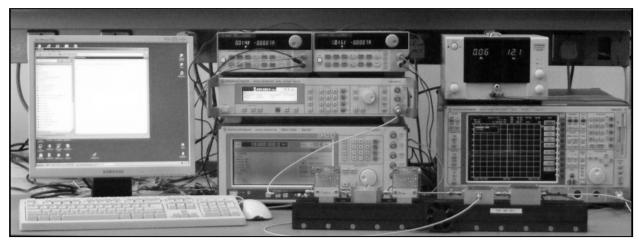

Figure 3.12 A photo of the IMD system used for test fixture measurements at the University of Stellenbosch to extract the higher order current derivatives of the CFY-30 GaAs FET. ..... 32

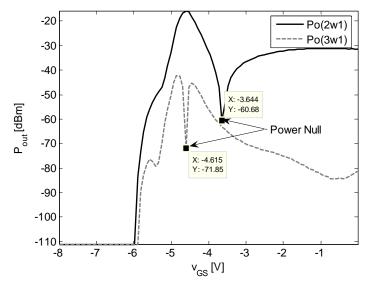

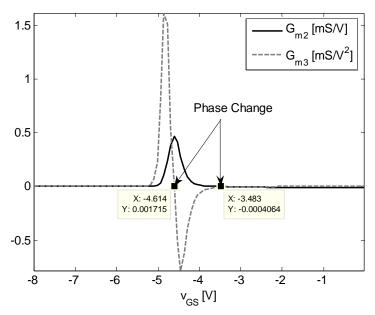

- Figure 3.14 The measured second  $P_0(2\omega_1)$  and third  $P_0(3\omega_1)$  harmonic output power levels with the each experiencing a power null, from which the phase information can be extracted. ... 33

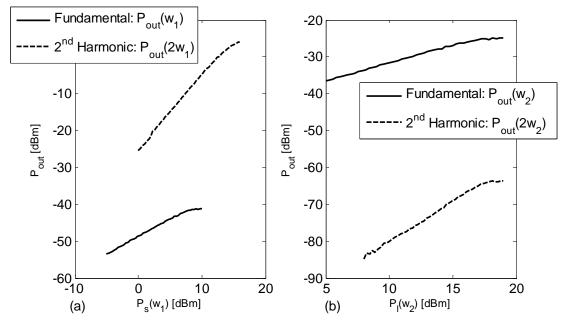

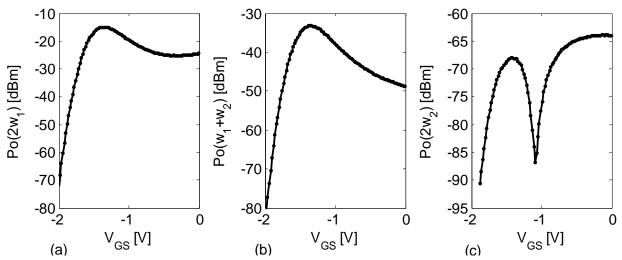

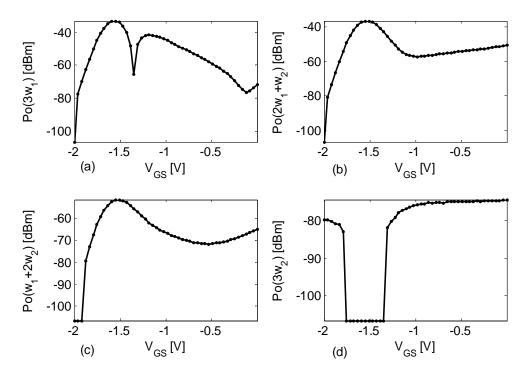

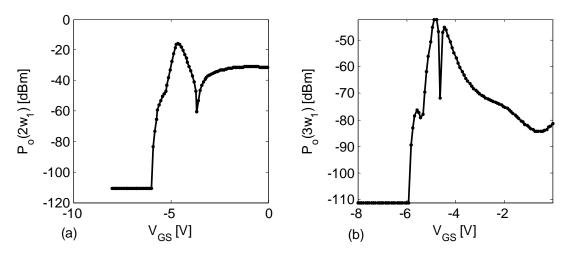

Figure 3.22 The typical second and third order output powers measured for the GaN HEMT, where (a) is output power second order product at  $P_O(2\omega_1)$  and (b) the third order product at  $P_O(3\omega_1)$ . The output power products are measured as a function of the gate voltage  $V_{GS}$ ... 41

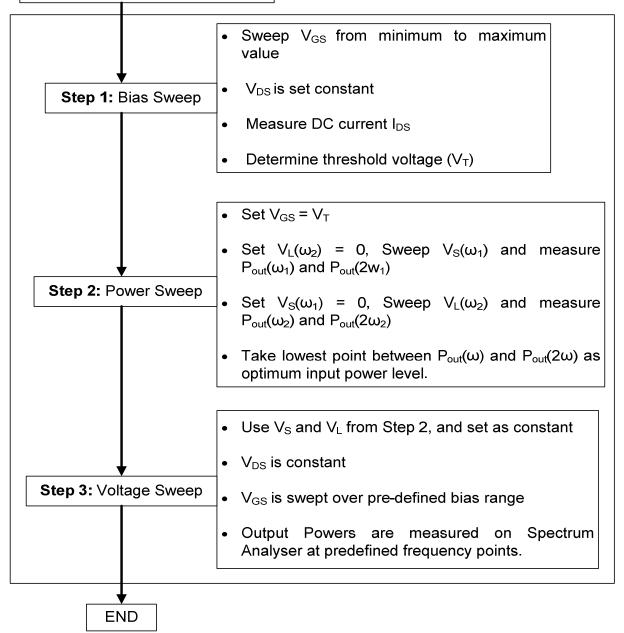

| Figure 3.2 | 23 T   | The block   | t diagram   | of the  | complete   | measurem    | nent proced | lure is | divided    | into | three |

|------------|--------|-------------|-------------|---------|------------|-------------|-------------|---------|------------|------|-------|

| steps      | s. The | e first ste | p is a bias | s sweep | , the seco | nd is a pov | wer sweep   | and the | e third is | a vo | ltage |

| swee       | ep     |             | ••••••      |         |            |             |             |         |            |      | 42    |

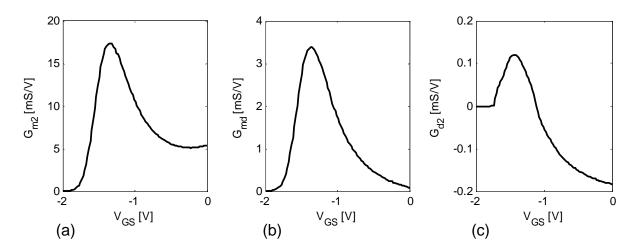

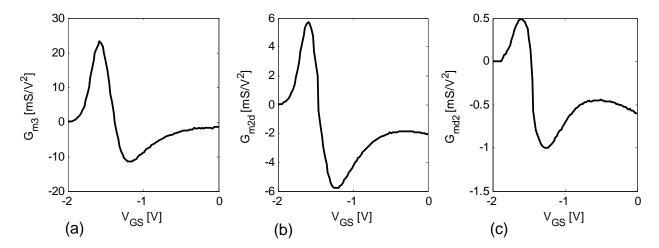

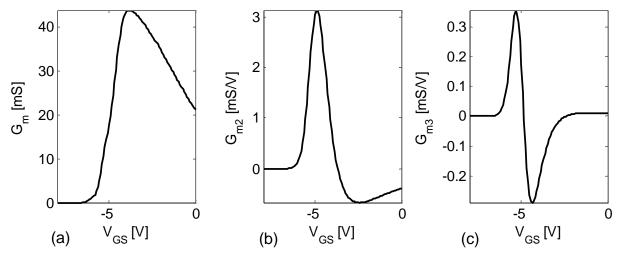

Figure 3.26 The typical second order extracted Taylor series coefficients for the CFY-30 GaAs FET, where (a) is G<sub>m2</sub>, (b) G<sub>md</sub> and (c) G<sub>d2</sub> The coefficients are extracted as a function of the gate voltage V<sub>GS</sub>.

#### Chapter 4

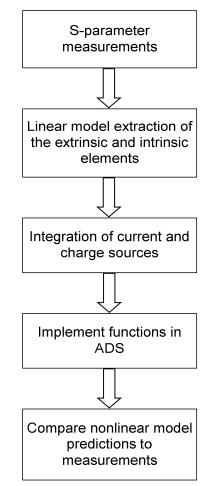

| Figure 4.1 The flow diagram of the nonlinear modelling procedure                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

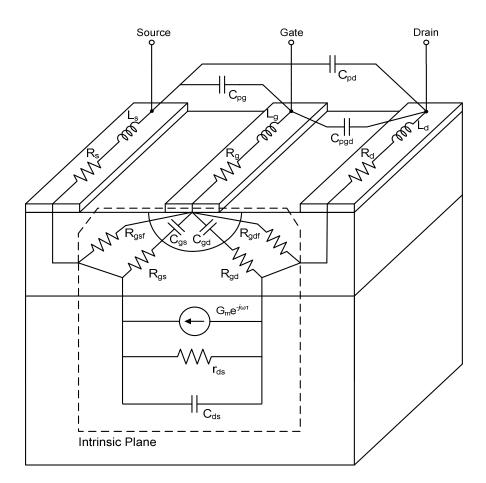

| Figure 4.2 The physical origin of the small-signal equivalent circuit parameters of a HEMT device                                                                                                                                  |

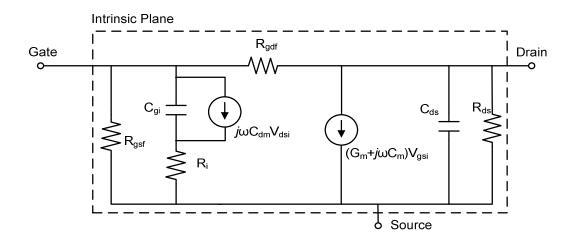

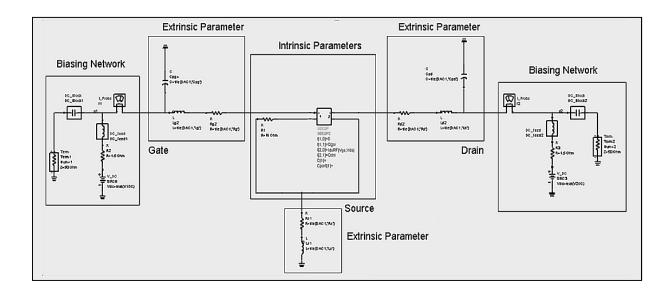

| Figure 4.3 The small-signal equivalent circuit topology used to model an on-wafer GaM HEMT                                                                                                                                         |

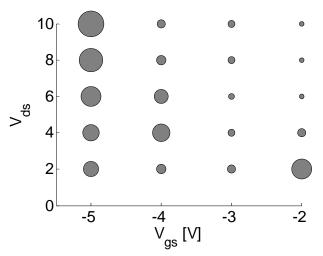

| Figure 4.4 (a) The result of applying the user defined filters to a complete set of extracted bia points, while in (b) the intelligent bias point selection reduces the data set to an optimal o five cold and ten hot bias points |

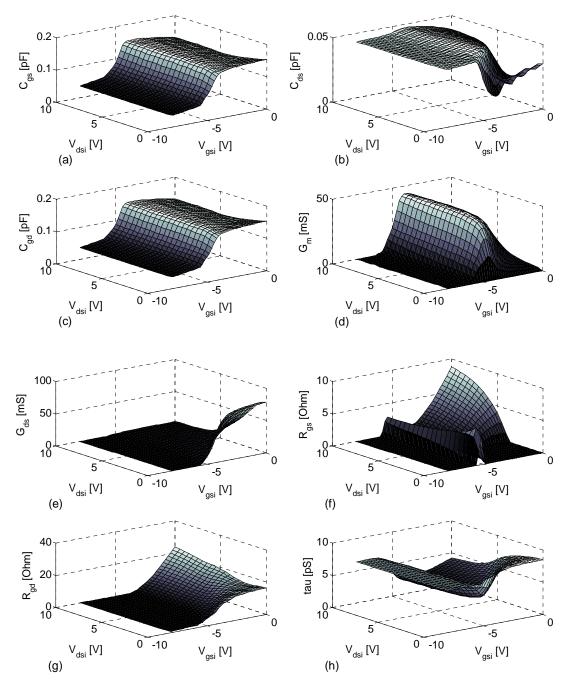

| Figure 4.5 The plots of the extracted bias dependant intrinsic elements of the T <sub>03</sub> device, where (a) is C <sub>gs</sub> , (b) C <sub>ds</sub> , (c) C <sub>gd</sub> , (d) G <sub>m</sub> , (e) G <sub>ds</sub> , (f) R <sub>i</sub> , (g) R <sub>gd</sub> and (h) tau versus the intrisic gate V <sub>gsi</sub> and drain V <sub>dsi</sub> voltages |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gor doi C                                                                                                                                                                                                                                                                                                                                                       |

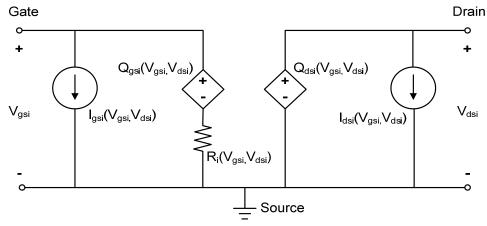

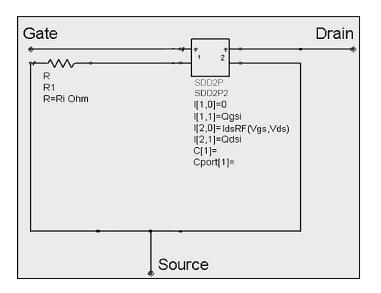

| Figure 4.6 The intrinsic quasi-static nonlinear HEMT model, referred to as the Root model 62                                                                                                                                                                                                                                                                    |

| Figure 4.7 The intrinsic small-signal equivalent circuit of the modified Root model is shown. 62                                                                                                                                                                                                                                                                |

| Figure 4.8 The modified Root nonlinear model with a charging resistance R <sub>i</sub>                                                                                                                                                                                                                                                                          |

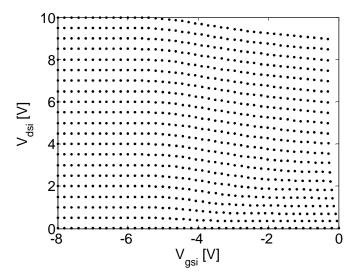

| Figure 4.9 The plots of the intrinsic gate $V_{gsi}$ versus drain $V_{dsi}$ voltages are non uniform as a result of the de-embedding process                                                                                                                                                                                                                    |

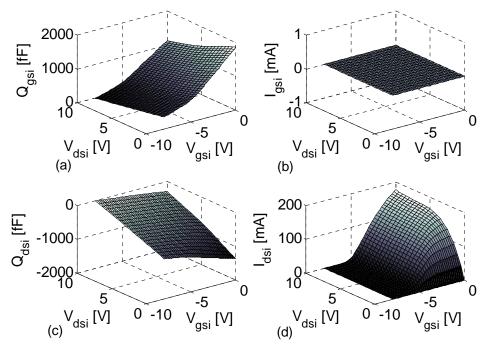

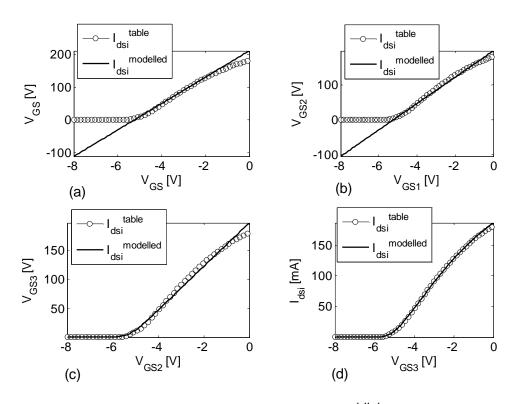

| Figure 4.10 The table-based nonlinear functions extracted for the $T_{03}$ device, where (a) is the gate charge $Q_{gsi}$ , (b) the gate current $I_{gsi}$ , (c) the drain charge $Q_{dsi}$ and (d) the drain current $I_{dsi}$ function                                                                                                                        |

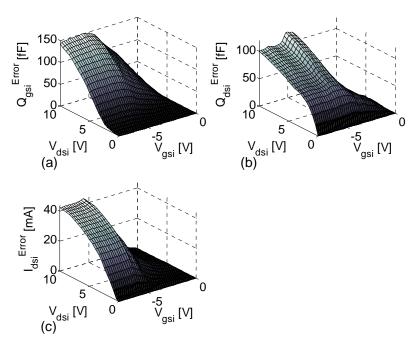

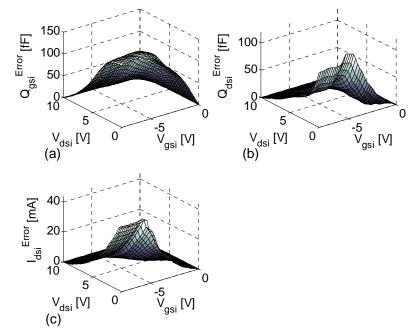

| Figure 4.11 The absolute difference of (a) $Q_{gsi}$ , (b) $Q_{dsi}$ , and (c) $I_{dsi}$ , associated with the integration process when an integration starting point of $V_{gs0} = 0V$ , $V_{ds0} = 0V$ is selected. 68                                                                                                                                        |

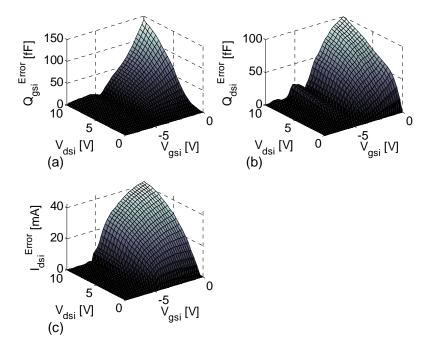

| Figure 4.12 The absolute difference of (a) $Q_{gsi}$ , (b) $Q_{dsi}$ , and (c) $I_{dsi}$ , associated with the integration process when an integration starting point of $V_{gs0} = -8V$ , $V_{ds0} = 0V$ is selected                                                                                                                                           |

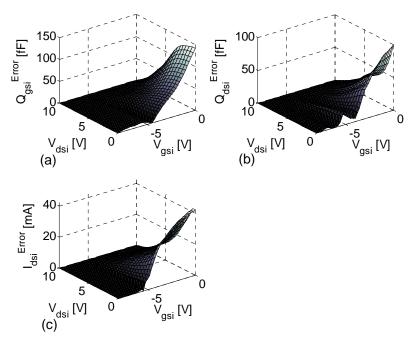

| Figure 4.13 The absolute difference of (a) $Q_{gsi}$ , (b) $Q_{dsi}$ , and (c) $I_{dsi}$ , associated with the integration process when an integration starting point of $V_{gs0} = -8V$ , $V_{ds0} = 10V$ is selected                                                                                                                                          |

| Figure 4.14 The absolute difference of (a) $Q_{gsi}$ , (b) $Q_{dsi}$ , and (c) $I_{dsi}$ , associated with the integration process when an integration starting point of $V_{gs0} = 0V$ , $V_{ds0} = 10V$ is selected                                                                                                                                           |

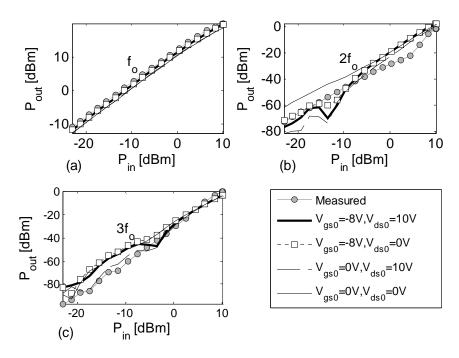

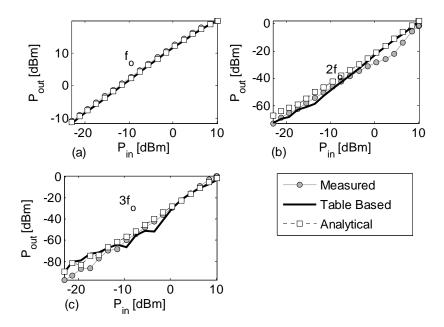

| Figure 4.15 The large-signal single-tone measurements of the (a) fundamental, (b) second harmonic and (c) third harmonic for different integration starting point                                                                                                                                                                                               |

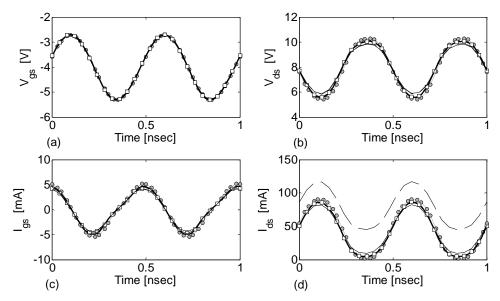

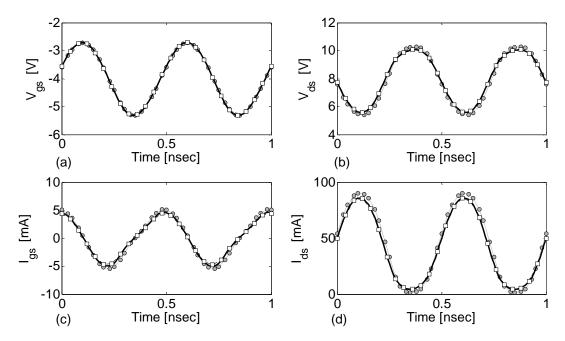

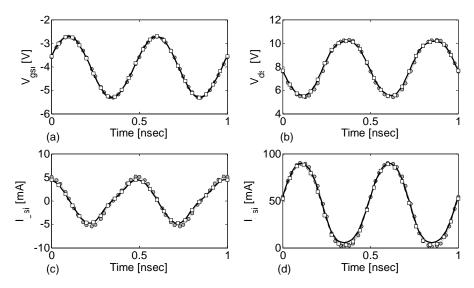

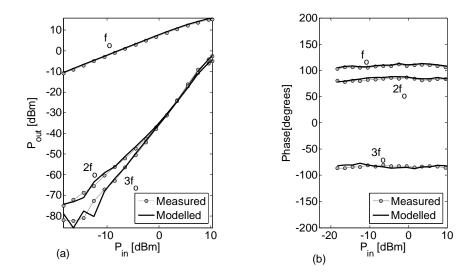

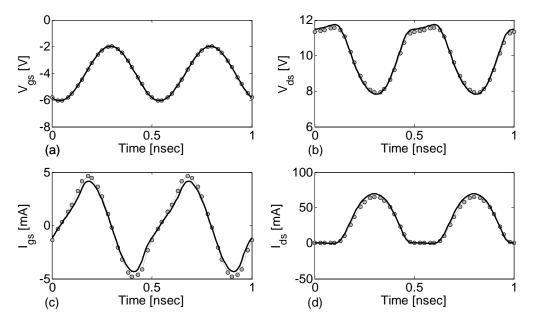

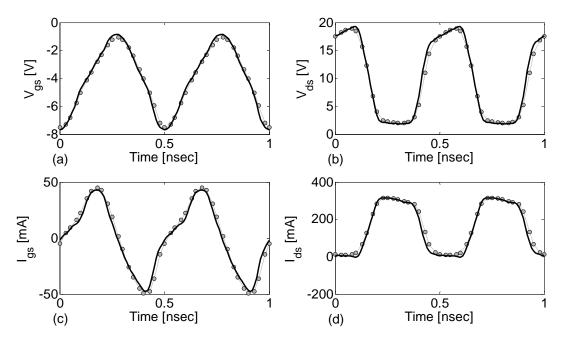

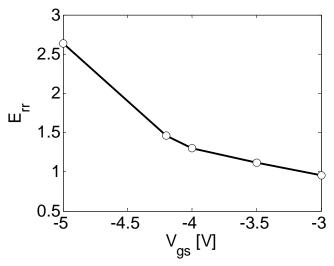

| Figure 4.16 The time wave forms of the gate (a) and drain (b) voltages, as well as the gate (c) and drain (d) current wave forms. An excitation with an input power level of $P_{in} = 2.45$ dBm and fundamental frequency $f_0 = 2$ GHz is applied                                                                                                             |

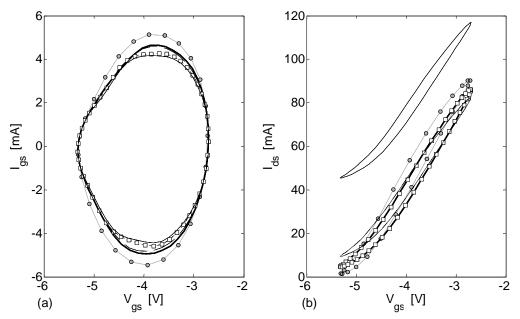

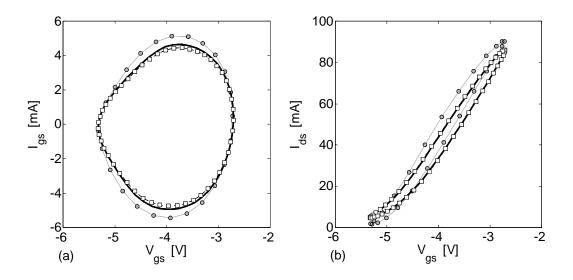

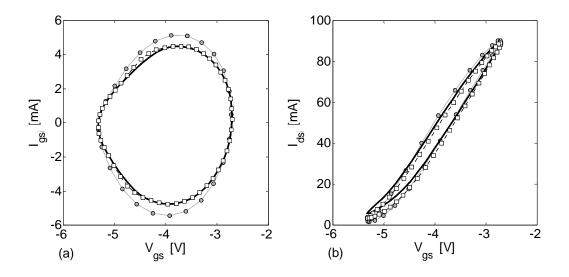

| Figure 4.17 The voltage versus current plots at the gate (a) and drain (b) ports, for input power level of $P_{in} = 2.45$ dBm and fundamental frequency of $f_o = 2$ GHz                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

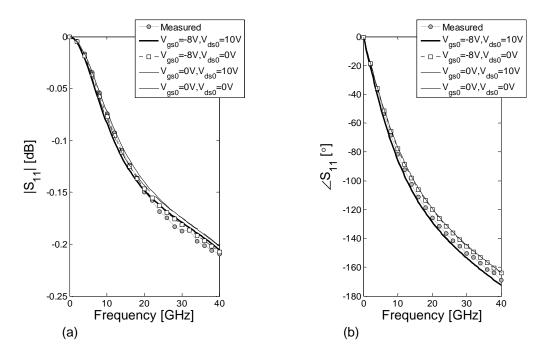

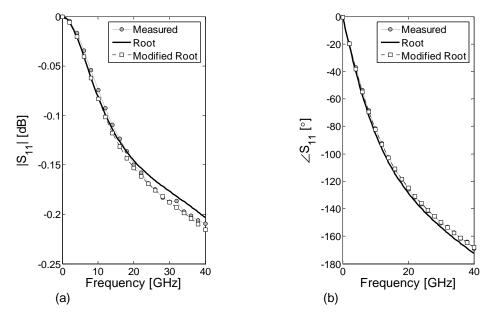

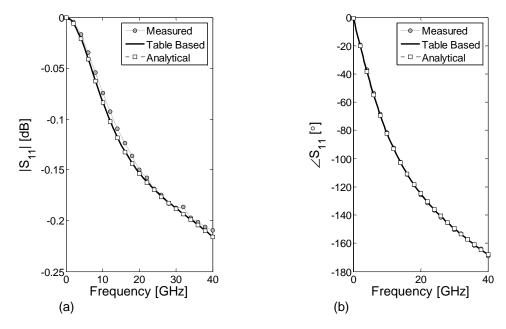

| Figure 4.18 The plots of the magnitude (a) and phase (b) of S <sub>11</sub> versus frequency with different integration starting points                                                                                                                                                                         |

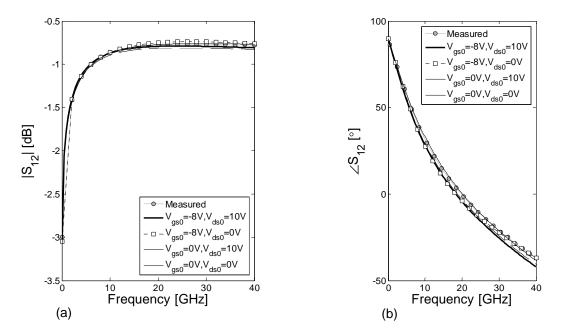

| Figure 4.19 The plots of the magnitude (a) and phase (b) of S <sub>12</sub> versus frequency with different integration starting points                                                                                                                                                                         |

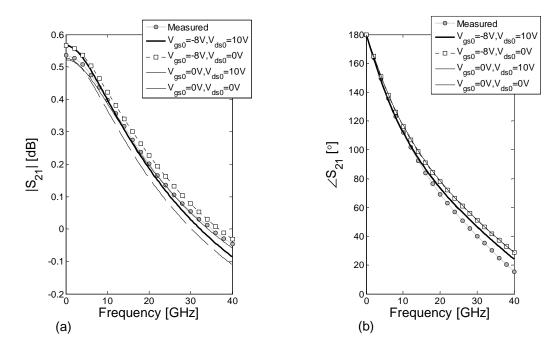

| Figure 4.20 The plots of the magnitude (a) and phase (b) of S <sub>21</sub> versus frequency with different integration starting points                                                                                                                                                                         |

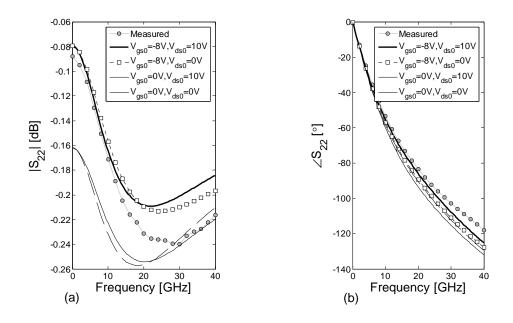

| Figure 4.21 The plots of the magnitude (a) and phase (b) of S <sub>22</sub> versus frequency with different integration starting points                                                                                                                                                                         |

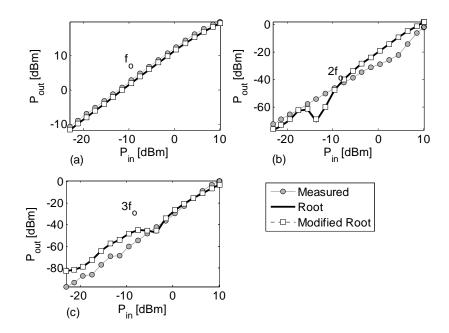

| Figure 4.22 The large-signal single-tone measurements of the (a) fundamental, (b) second harmonic and (c) third harmonic for different integration starting point. The grey circled line represents the measured data, while the solid line presents the Root model and the dashed line the modified Root model |

| Figure 4.23 The time wave forms of the gate (a) and drain (b) voltages, as well as the gate (c) and drain (d) current wave forms. The grey circled line represents the measured data, while the solid line the Root model and the dashed line the modified Root model                                           |

| Figure 4.24 The voltage versus current plots at the gate (a) and drain (b) ports. The circled line represents the measured data, while the solid line the Root model and the dashed line the modified Root model                                                                                                |

| Figure 4.25 The plots of the magnitude (a) and phase (b) of S <sub>11</sub> versus frequency. The grey circled line represents the measured data, while the solid line the Root model and the dashed line the modified Root model                                                                               |

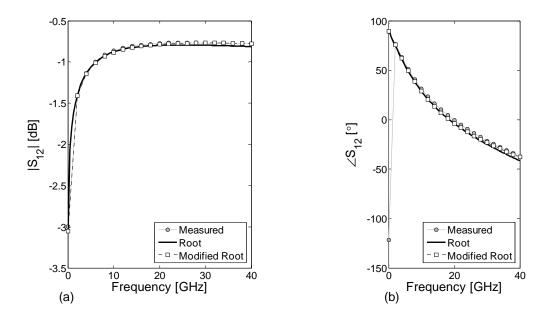

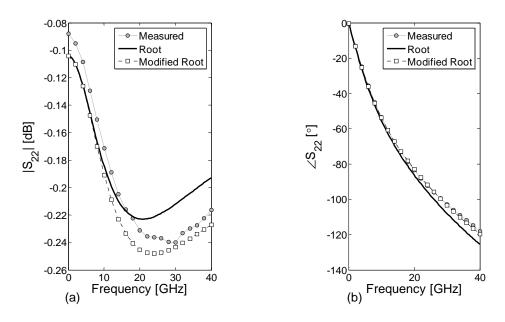

| Figure 4.26 The plots of the magnitude (a) and phase (b) of $S_{12}$ versus frequency. The grey circled line represents the measured data, while the solid line the Root model and the black dashed line the modified Root model                                                                                |

| Figure 4.27 The plots of the magnitude (a) and phase (b) of S <sub>21</sub> versus frequency. The grey circled line represents the measured data, while the solid line the Root model and the dashed line the modified Root model                                                                               |

#### Chapter 5

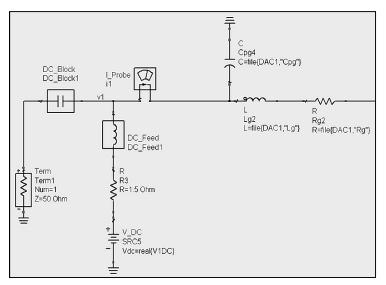

| Figure 5.2 | The biasing network used for the S-parameter is terminated in a 50 ohm load to                                                                                                                                |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| represe    | nt the terminals of the VNA. The extrinsic parameters are saved in a text file which                                                                                                                          |

| is impo    | orted using a DAC                                                                                                                                                                                             |

| nonline    | The symbolic defined device (SDD) used to implement the intrinsic parameters of the ear model. The charge sources are imported using a DAC, while the drain current is implemented using analytical functions |

| e          | The technique used to implement the nonlinear current source I <sub>dsi</sub> as an analytical n in ADS                                                                                                       |

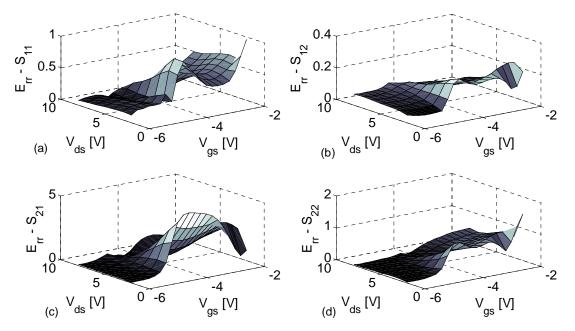

| -          | The S-parameter error made in modelling (a) $S_{11}$ (b) $S_{12}$ (c) $S_{21}$ (d) $S_{22}$ as a function gate voltage $V_{gs}$ , and drain voltages $V_{ds}$                                                 |

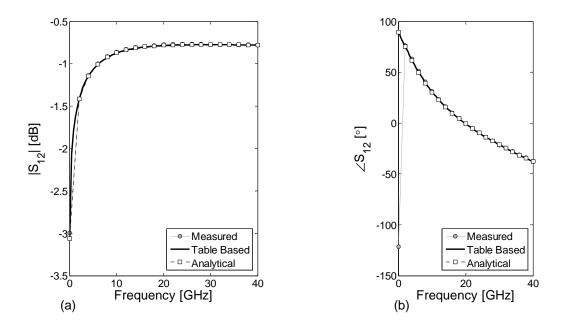

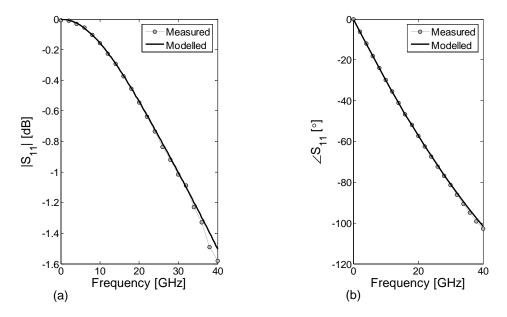

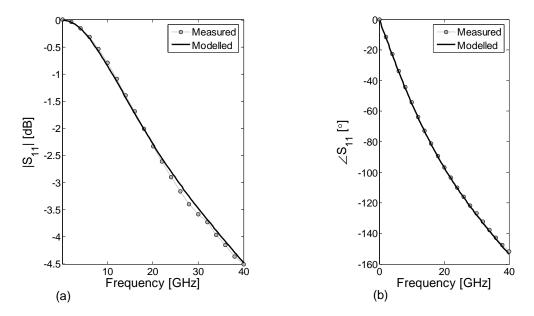

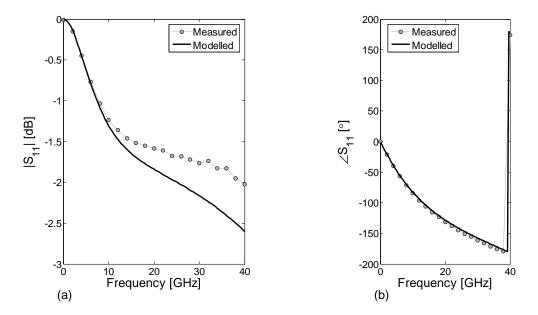

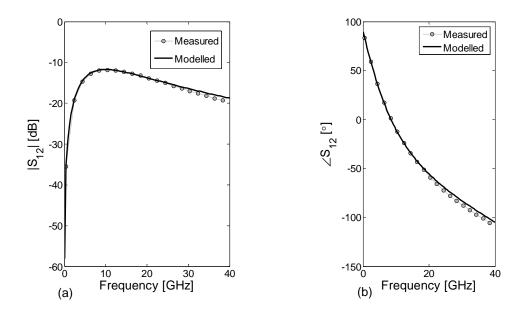

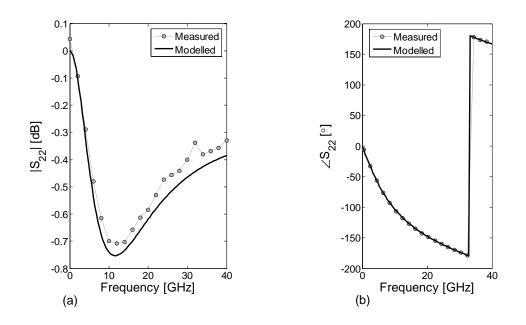

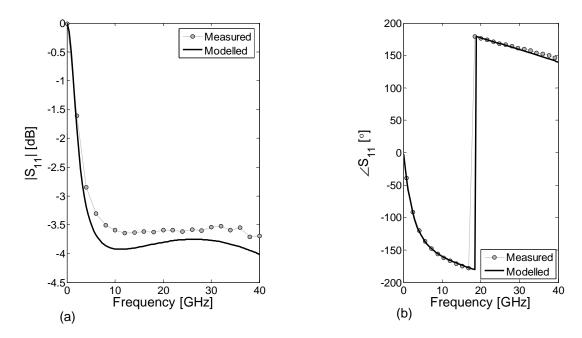

- Figure 5.9 The measured and modelled plots of the magnitude (a) and phase (b) of  $S_{22}$  versus frequency of the  $T_{02}$  device biased in a pinch-off condition ( $V_{gs} = -6V$ ,  $V_{ds} = 8V$ ). The grey circled line represents the measured data, while the solid line presents the modelled prediction. 100

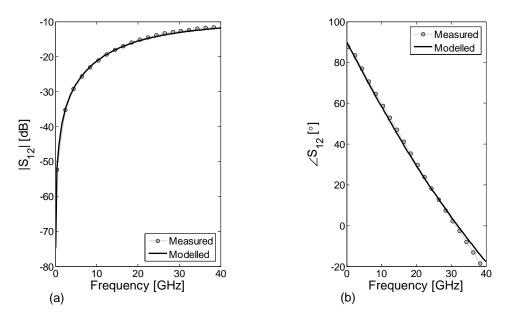

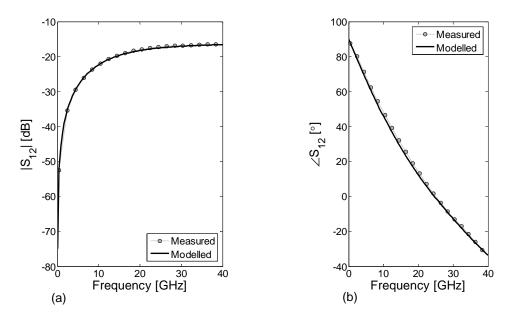

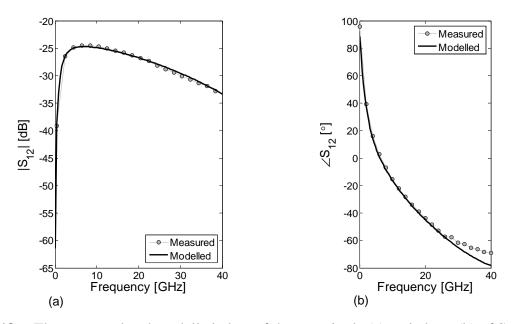

- Figure 5.11 The measured and modelled plots of the magnitude (a) and phase (b) of  $S_{12}$  versus frequency of the  $T_{02}$  device biased for class-AB operation ( $V_{gs} = -4V$ ,  $V_{ds} = 8V$ ). The grey circled line represents the measured data, while the solid line presents the modelled prediction. 101

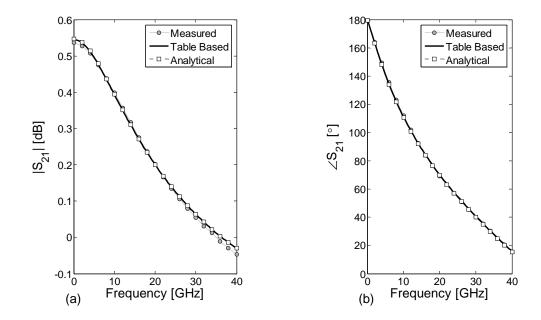

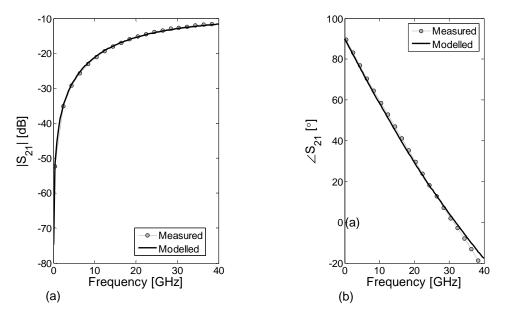

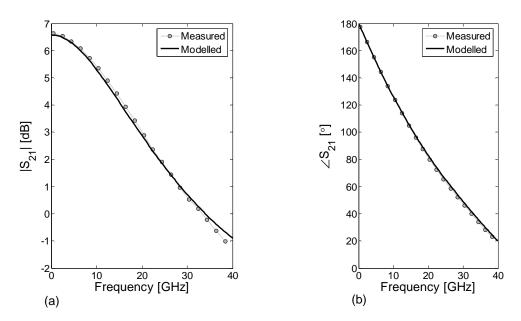

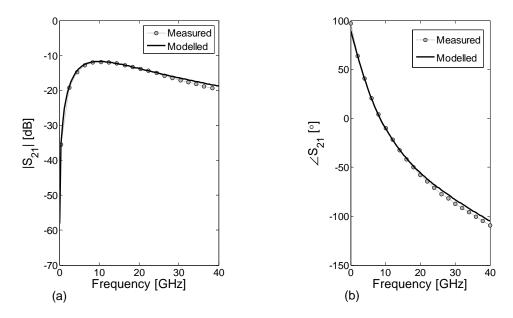

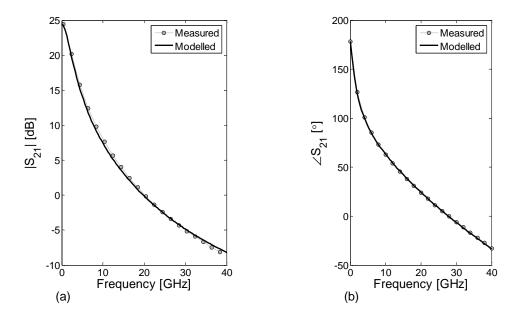

- Figure 5.12 The measured and modelled plots of the magnitude (a) and phase (b) of  $S_{21}$  versus frequency of the  $T_{02}$  device biased for class-AB operation ( $V_{gs} = -4V$ ,  $V_{ds} = 8V$ ). The grey circled line represents the measured data, while the solid line presents the modelled prediction. 101

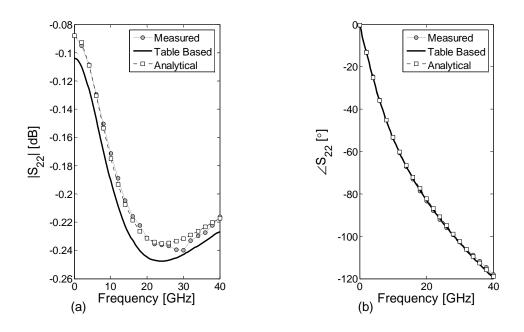

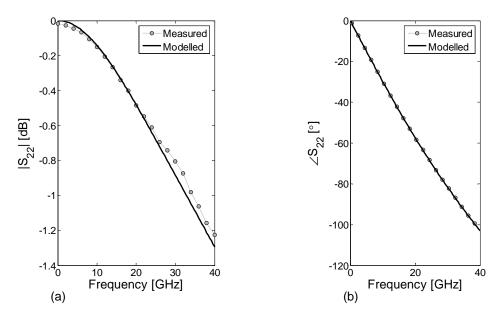

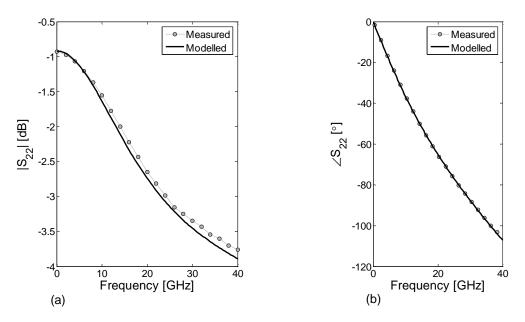

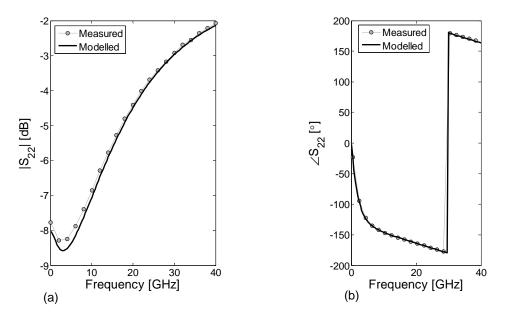

- Figure 5.13 The measured and modelled plots of the magnitude (a) and phase (b) of  $S_{22}$  versus frequency of the  $T_{02}$  device biased for class-AB operation ( $V_{gs} = -4V$ ,  $V_{ds} = 8V$ ). The grey circled line represents the measured data, while the solid line presents the modelled prediction. 102

- Figure 5.14 The measured and modelled plots of the magnitude (a) and phase (b) of  $S_{11}$  versus frequency of the  $T_{12}$  device biased in a pinch-off condition ( $V_{gs} = -8V$ ,  $V_{ds} = 8V$ ). The grey circled line represents the measured data, while the solid line presents the modelled prediction. 102

- Figure 5.15 The measured and modelled plots of the magnitude (a) and phase (b) of  $S_{12}$  versus frequency of the  $T_{12}$  device biased in a pinch-off condition ( $V_{gs} = -8V$ ,  $V_{ds} = 8V$ ). The grey circled line represents the measured data, while the solid line presents the modelled prediction. 103

- Figure 5.16 The measured and modelled plots of the magnitude (a) and phase (b) of  $S_{21}$  versus frequency of the  $T_{12}$  device biased in a pinch-off condition ( $V_{gs} = -8V$ ,  $V_{ds} = 8V$ ). The grey circled line represents the measured data, while the solid line presents the modelled prediction. 103

- Figure 5.17 The measured and modelled plots of the magnitude (a) and phase (b) of  $S_{22}$  versus frequency of the  $T_{12}$  device biased in a pinch-off condition ( $V_{gs} = -8V$ ,  $V_{ds} = 8V$ ). The grey circled line represents the measured data, while the solid line presents the modelled prediction. 104

- Figure 5.18 The measured and modelled plots of the magnitude (a) and phase (b) of  $S_{11}$  versus frequency of the  $T_{12}$  device biased for class-AB operation ( $V_{gs} = -4V$ ,  $V_{ds} = 8V$ ). The grey circled line represents the measured data, while the solid line presents the modelled prediction. 104

- Figure 5.19 The measured and modelled plots of the magnitude (a) and phase (b) of  $S_{12}$  versus frequency of the  $T_{12}$  device biased for class-AB operation ( $V_{gs} = -4V$ ,  $V_{ds} = 8V$ ). The grey circled line represents the measured data, while the solid line presents the modelled prediction. 105

- Figure 5.20 The measured and modelled plots of the magnitude (a) and phase (b) of  $S_{21}$  versus frequency of the  $T_{12}$  device biased for class-AB operation ( $V_{gs} = -4V$ ,  $V_{ds} = 8V$ ). The grey circled line represents the measured data, while the solid line presents the modelled prediction. 105

- Figure 5.21 The measured and modelled plots of the magnitude (a) and phase (b) of  $S_{22}$  versus frequency of the  $T_{12}$  device biased for class-AB operation ( $V_{gs} = -4V$ ,  $V_{ds} = 8V$ ). The grey circled line represents the measured data, while the solid line presents the modelled prediction. 106

### List of Tables

# Chapter 2

| Table 2.1 | The key advantages of GaN over competing semiconductor technologies7                           |

|-----------|------------------------------------------------------------------------------------------------|

| Table 2.2 | The different GaN HEMT topologies measured at IMEC                                             |

|           | Comparison between model parameters for the Agilent 11612B and Pulse Labs econd 5580 bias tees |

# Chapter 3

| Table 3.1 | It is ir | npor  | tant to und | erstand the | physical | mean | ing of eac | ch co | effi | cient | as it will | give  |

|-----------|----------|-------|-------------|-------------|----------|------|------------|-------|------|-------|------------|-------|

| insig     | ht into  | the   | parameter   | extraction  | process. | The  | significa  | nce   | of e | each  | coefficie  | nt is |

| sumr      | narised  | in th | is table    |             |          |      |            |       |      |       |            | 27    |

# Chapter 4

| Table 4.1 | Extracted extrinsic parameters of the on-wafer GaN HEMT $T_{03}$ device             | 57 |

|-----------|-------------------------------------------------------------------------------------|----|

| Table 4.2 | Summary of the Fager model parameters                                               | 30 |

| Table 4.3 | The values of the optimised Fager model parameters for the $T_{03}$ device topology | 32 |

# **CHAPTER 1**

## Introduction

#### **1.1 Introduction**

The main objective of this thesis is to investigate, characterise and model a new advanced microwave transistor. The technology referred to is gallium nitride (GaN) high-electron mobility transistors (HEMTs). The HEMTs measured and modelled are manufactured at the Interuniversity Microelectronics Centre (IMEC) in Leuven, Belgium. GaN semiconductor technology offers higher levels of gain at very high frequencies compared to similar devices in the market today. As this technology is relatively new, not many models have been proposed in literature and the goal of this work is to develop nonlinear models that accurately predict the linear and nonlinear behaviour of the GaN HEMTs measured.

The goal of this chapter is to give a brief introduction to the basic principles of nonlinear modelling. These principles are fundamental to fully understand how nonlinear models are derived in practice. The final section of this chapter will present the scope and layout of this thesis.

#### **1.2 Overview of Nonlinear Modelling Techniques**

Physically-based modelling, black box modelling and equivalent circuit modelling are the three main modelling approaches to describe the nonlinear behaviour of a device [12]. Each of these techniques will be discussed briefly in this section.

Physically-based modelling describes the active device in terms of the motion of charge carriers and geometrical characteristics, allowing both a physical and an electrical description of the device. The advantage of this approach is that it provides valuable insight into the operation of the semiconductor device. The disadvantage, however, is that this type of model is rather complex and requires time-consuming numerical methods to obtain solutions, thus it will not be considered in this work.

The next modelling technique is known as "Black Box Modelling". In this approach, the device is represented by a behavioural input-output model. It arises from system theory, where basic building blocks of any complexity are represented by a transfer function. The parameters of the mathematical model are fitted to a set of measured results. The newest work in this field provides very powerful models by extracting nonlinear state space equations directly from measured data. This technique requires a large amount of nonlinear vector measurements taken with the largesignal vector network analyser (LSNA). However, the accessibility of a LSNA measurement system is in most cases problematic and is a major disadvantage of this technique. The method also requires extensive fitting procedures that can be very time consuming. A trade-off between model accuracy and model simplicity has to be made, which does not make this approach suitable for this work.

The most widely used type of device model in practice is the equivalent circuit model. This model offers several key advantages over the physically-based and "Black Box" models. The first is that the small-signal equivalent model provides a link between the measured DC and S-parameters and the electronic processes occurring within the device. The elements in the equivalent circuit provide a lumped element approximation to some aspect of the physical device. A properly chosen topology, in addition to being physically meaningful, provides an excellent match to measurements over a very wide frequency range and allows for extrapolation of behaviour at frequencies beyond the capability of the available measurement setup. The main advantage of this method is that it is relatively fast and straightforward, which makes it ideal to implement in nonlinear simulation packages. The equivalent circuit parameters (ECPs) are extracted using measurements taken from the vector network analyser (VNA). Once the ECPs have been extracted, the equivalent quasi-static nonlinear model can be derived. The model can be extended to a non quasi-static model to improve the accuracy of the model predictions.

All factors considered, it is concluded that the equivalent circuit model approach will be used to model the devices in this work. In chapter four, a detailed description of the equivalent circuit model topology is presented, as well as the deduction of the nonlinear models.

#### **1.3 Introduction to Nonlinear Equivalent Circuit Models**

The main objective of an equivalent circuit is to model all the electrical characteristics of the original circuit on which it is based. When dealing with complex circuits such as transistor models, the equivalent circuit is made up of linear and nonlinear elements and must be able to

accurately predict both the linear and nonlinear behaviour of the device. In practice, the nonlinear equivalent circuit model is the most widely used nonlinear model and is fairly simple to implement in commercial computer aided design (CAD) programs.

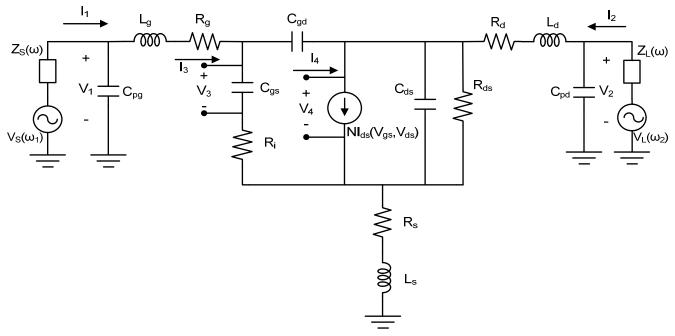

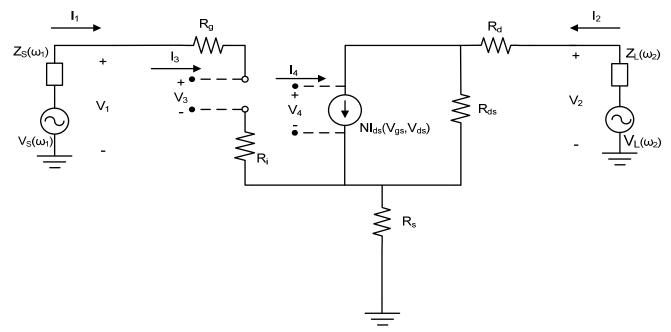

The most common method to construct these models is from measured multi-bias DC and highfrequency S-parameter data. Pulsed I-V measurements can also be used, but these measurement setups are not always accessible and will not be used in this work. The measured S-parameter data from the VNA is used to extract the linear equivalent circuit model. This model represents the small-signal response of the device. A typical small-signal model of a field effect transistor (FET) model consists of an intrinsic and an extrinsic section as shown in Figure 1.1. All the elements outside the dashed box represent the extrinsic elements. These elements are related to the packaging of the device and are bias-independent. The elements inside the box represent the intrinsic elements and are bias-dependent.

**Figure 1.1** The typical small-signal equivalent circuit for an FET.

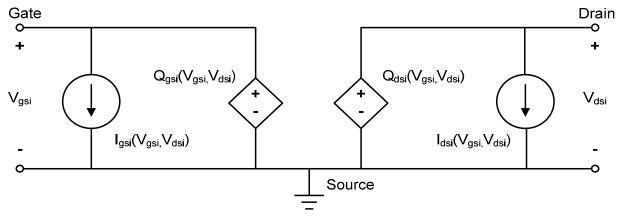

Once the equivalent circuit parameters have been extracted the next step is to construct the nonlinear current and charge functions seen in Figure 1.2. The nonlinear model is consistent with the small-signal equivalent scheme, provided that the corresponding non-linear characteristics at both ports are obtained by the path independent contour integrals. The nonlinear models transform the large amount of extracted small-signal parameters into a single set of parameters. The result is a nonlinear circuit model representation of the device that should be able to predict

the linear and nonlinear behaviour of the device. The model seen in Figure 1.2 is known as the nonlinear state-space representation and will be discussed in more detail in chapter four.

Figure 1.2 The transformed state-space nonlinear model representation.

#### 1.4 Scope and Layout of this Study

The main goal of this thesis is to develop equivalent circuit nonlinear models for an emergent active device technology, GaN HEMTs. The models should be capable of accurately predicting the linear and nonlinear behaviour of the devices. The linear characteristics include the small-signal S-parameters predictions, while the nonlinear characteristics include the harmonic and intermodulation distortion predictions. A key focus of the nonlinear models is to ensure that the model can still predict the linear small-signal S-parameters. GaN is expected to play an important role in future power amplifier applications of microwave and wireless digital telecommunications systems. GaN technology is relatively new and not many models have been presented in literature. The aim of this thesis is to develop a model that can accurately predict the linear and nonlinear behaviour of the measured devices. The following paragraphs give a brief overview of the content of this thesis.

In chapter two, an overview of GaN HEMT technology is presented, as well as the procedure followed in the device characterisation process. This chapter also discusses the various measurement instruments that were used in the characterisation and validation process of the on-wafer devices. Chapter three presents a low-frequency intermodulation distortion measurement setup used to measure the second and higher order intermodulation performance of the nonlinear drain current source,  $I_{ds}$ . The current source  $I_{ds}$  represents one of the main nonlinearities in an

equivalent circuit nonlinear model and should thus be modelled as accurately as possible. The main objective of the measurement setup is to extract a Taylor series, describing the higher order derivatives of  $I_{ds}$  directly from measurements. The Taylor series coefficients are essential for the construction of models that can accurately predict nonlinear intermodulation distortion (IMD) behaviour.

The goal of chapter four is to present a formulation and investigate the nonlinear models proposed for the GaN HEMTs. The starting point of the process is to determine the small-signal equivalent circuit model topology, followed by the detailed ECP extraction procedure. Once the ECPs are determined, the corresponding nonlinear model is constructed. The complete nonlinear model construction is discussed with a description of the nonlinear modelling procedure and formulation. The current derivative data extracted in chapter three is incorporated in the final nonlinear model. The addition of the derivative information leads to a nonlinear model that improves the S-parameter, large-signal single-tone and large-signal two-tone IMD predictions.

In chapter five, the proposed nonlinear models are verified by comparing the CAD model predictions to measurements from the VNA and LSNA. This chapter gives an overview of the error functions used to represent the difference between the measured and modelled parameters. The software tools used to implement the nonlinear models in Agilent's Advanced Design System (ADS) is described in this chapter. Finally, the nonlinear model predictions are compared to the measured S-parameters, large-signal single-tone and large-signal two-tone results. Chapter six provides an overview of the results and provides recommendations for future research.

### **CHAPTER 2**

### **Device Characterisation and Measurement Setups**

#### **2.1 Introduction**

It is very important to fully understand the device technology that is to be modelled and the measurement instruments needed in the modelling process. This chapter is dedicated to provide insight into the on-wafer gallium nitride (GaN) high-electron mobility transistors (HEMT) devices modelled, as well as the measurement setups used to characterise and verify the devices. It is vital to understand the operation and data obtained from each instrument. The measurement equipment is not only used to extract the equivalent circuit models, but also to verify the accuracy of the models. Once the parameters have been extracted, the models are implemented in a simulation package and the measured results are compared with the model predictions.

In section 2.2, an overview of the GaN HEMT technology is presented, with the explanation of the basic operation of a HEMT to provide insight into the modelling process. Before a device is measured, a selection process must be followed to ensure that the optimal devices are measured, which is discussed in section 2.3. Section 2.4 provides an overview of the various linear and nonlinear measurement instruments necessary in the nonlinear modelling process. In section 2.4.1, the vector network analyser (VNA) is discussed, from which the values of the equivalent circuit parameters (ECPs) are extracted. Section 2.4.2 discusses the large-signal network analyser (LSNA), which is used as an independent measurement to perform the nonlinear large-signal validations.

#### 2.2 GaN HEMT Technology

Over the last few years, many different technologies have been investigated in the field of power amplifiers. The latest breakthrough has come in the development of wide band-gap materials, for example, GaN. Devices based on wide band-gap materials are capable of handling higher power densities in a more efficient way than devices fabricated from other semiconductor materials. It is a result of the combination of high energy band-gap, high critical electric field, low dielectric

constant and high thermal conductivity. The main property advantages of GaN over competing semiconductor materials are demonstrated in Table 2.1 [5]. There is a wide range of applications for GaN devices, ranging from commercial applications to the medical field. GaN has been grown on many different substrates, including sapphire, Si and SiC. The most widely reported substrate is sapphire, as it has the advantage of being relatively cheap and is offered in large diameter wafers. Most importantly, it provides an excellent low-loss microwave substrate. The disadvantage of sapphire is that the thermal conductivity is very poor and will severely limit the power density and total power performance of devices fabricated on it. The devices measured in this work are based on a SiC substrate, which has promising characteristics in terms of lattice matching and thermal conductivity, and it is also an excellent microwave substrate. The disadvantages of devices on SiC are the costs related to the growth process, limited wafer size and material defects. The material defects play a critical role in the device characterisation and will be discussed in section 2.3.

| Property            | Si     | GaAs | GaN  |

|---------------------|--------|------|------|

| Suitable for high   | Medium | Low  | High |

| power applications  |        |      |      |

| Suitable for high   | Low    | High | High |

| frequencies         |        |      |      |

| HEMT structures     | No     | Yes  | Yes  |

|                     |        |      |      |

| Low cost substrates | Yes    | No   | Yes  |

|                     |        |      |      |

**Table 2.1**The key advantages of GaN over competing semiconductor technologies.

A key advantage of the HEMT devices is that it overcomes the performance limits of the conventional metal semiconductor field effect transistor (MESFET), as it exhibits more gain, a higher operating frequency and a lower noise figure. Figure 2.1 shows the basic structure of an HEMT device. It consists of a hetero-junction, composed of a narrow band-gap (GaN) material and a wide band-gap (AlGaN) material. The wide band-gap semiconductor is doped, resulting in states of lower energy [13], which leads to the electrons diffusing from the wide to the narrow band-gap semiconductor. These electrons form a thin layer which is known as a two-dimensional electron gas (2DEG). Within this region, the electrons are able to move freely because there are no other donor atoms or other items with which electrons will collide, making the mobility of the electrons in the gas very high. The output current flowing between source and drain is controlled by the modulation of the carrier density in the channel through the gate. When the gate voltage is equal to zero, a 2DEG is accumulated at the hetero-interface and the channel is open. When a positive gate voltage is applied, the output current increases. This is a result of the increase in 2DEG density and consequently the current density in the channel. However, when the gate voltage is lower than the pinch-off voltage (typically a negative voltage), the drain current approaches zero regardless of the drain bias, since the 2DEG in the channel is depleted [13].

Figure 2.1 The basic structure of an HEMT device.

### 2.3 Device Characterisation

In this section, the selection method for the characterisation of on-wafer GaN HEMT devices is detailed. As mentioned in the previous section the devices measured were fabricated on a SiC substrate, which in practice has led to difficulties regarding the growth process, wafer size and material defects. The result is that the device characteristics can differ depending on the position on the wafer. A number of different device topologies are fabricated on each wafer. The subscript in the name indicates the number of fingers and gate widths of the device. Table 2.2 gives a summary of the devices measured at IMEC. It is important to select the appropriate device on the wafer, in order to accurately characterise the desired topology.

| <b>Two-Finger Devices</b>  | Four-Finger Devices        |

|----------------------------|----------------------------|

| $T_{02}$ Devices (2×50µm)  | $T_{10}$ Devices (4×100µm) |

| $T_{03}$ Devices (2×100µm) | $T_{12}$ Devices (4×150µm) |

| $T_{06}$ Devices (2×150µm) |                            |

| $T_{07}$ Devices (2×200µm) |                            |

Table 2.2

The different GaN HEMT topologies measured at IMEC.

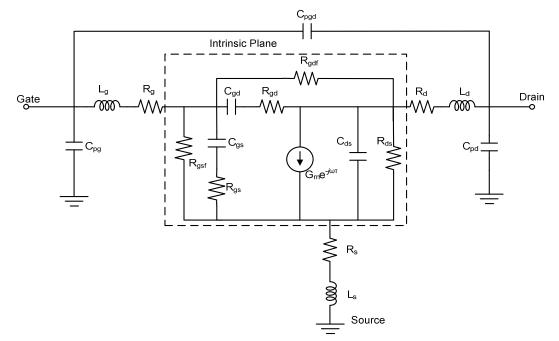

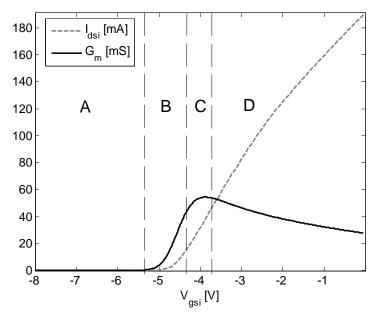

The first step in the characterisation process is to measure the drain current curves of a least five devices of the same topology. This measurement is done with a constant gate voltage and the drain voltage swept over the desired range. From these  $I_{DS}$  curves, a mean current plot is

constructed, as seen in Figure 2.2. In this figure, the T<sub>02</sub> devices are selected to demonstrate this approach. It can be seen that the curves have a relatively wide spread. With such a spread, it becomes vital to determine the optimal device to measure. The devices with the IDS curve nearest to the mean plot are selected to characterise. Selecting the devices this way ensures that an average device is selected, which resembles the best average performance of that device topology. Once the appropriate device is selected, the characterisation process can begin, which is an automated Matlab procedure used at IMEC. The automated program measures the Sparameters over a user-defined bias range and step size. Care must be taken when entering the bias range, as the device can be damaged during the process if it is put under too much strain. The gate bias range is swept from -8V to 0V in steps of 0.2V, and drain biasing from 0V to 10V in steps of 0.5V. This leads to 861 bias points in total and is enough to fully characterise the devices, with the measurement time only taking a few hours. The S-parameters are measured from 45MHz to 40GHz with 201 frequency points. Any more points could lead to extra unwanted strain on the device which can cause damage, preventing the device from being used for the modelling process. The following section will describe the different measurement setups used to characterise the nonlinear behaviour of the on-wafer GaN HEMT devices in this work.

**Figure 2.2** The different DC drain current curves for devices of the same topology.

#### 2.4 Linear and Nonlinear Measurement Setups

In this section, a brief description of the measurement setups used to characterise and verify the on-wafer GaN HEMT devices is given. It is very important to understand the instruments to ensure accurate and reliable measurements. The nonlinear models that will be simulated in a

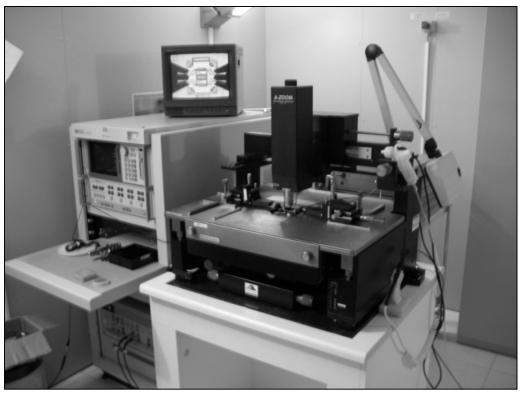

nonlinear simulation package are derived from measurements and thus it is vital that the experimental data is as accurate as possible. The first measurement setup of importance is the HP8510C VNA, which was used at IMEC to measure the S-parameters of the devices. The small-signal equivalent circuit parameters are extracted from the S-parameters. The second system is the LSNA, which was used at the Department of Electrical Engineering (ESAT) at the Catholic University Leuven, Belgium, for large-signal single-tone and two-tone verification measurements.

#### 2.4.1 Vector Network Analyser

Nonlinear models are derived from linear equivalent circuit models which are extracted from linear S-parameters and DC measurements. These linear measurements are performed using a VNA which measures both the magnitude and phase of all the complex S-parameters of a device. The VNA measures the ratio of the scattered and incident travelling voltage waves at the fundamental frequency, as demonstrated in Figure 2.3, which implies that the VNA is a linear measurement system. However, before the S-parameter can be measured a calibration process must be followed [13], [17]. The calibration ensures that the plane of the measurement is shifted to the ports of the device under test (DUT).

By measuring known precision standards, the systematic errors can be removed mathematically from the experimental setup. These systematic errors are a result of imperfections of the VNA and the test setup. If it is assumed that the errors are time invariant, then it is possible to characterise the error with a calibration process and remove the effect from the measured data [17]. The main calibration techniques which have been developed for connector and on-wafer technologies are short-open-load-through (SOLT), thru-reflect-load (TRL), load-reflect-match (LRM) and the line-reflect-reflect-match (LRRM). The SOLT and LRM are mostly used, where the SOLT calibration has been successfully used for RF characterisation up to a few GHz. However, the accuracy of the calibration decreases for frequencies higher than 20GHz, which is not sufficient for the frequency ranges required in this work. The reason is that it is very difficult to produce a high quality purely resistive load and it is difficult to have an accurate definition of the planar open circuit and the planar short circuit at such high frequencies, as the short circuit is inductive and an open circuit radiates energy [12]. Thus, the calibration technique used in this work is the LRM. This technique requires a single reflective impedance of which the model's preciseness is less stringent than for the SOLT technique and the calibration is valid up to 50GHz [13]. The advantage of using the LRM technique is that only three impedance standards are necessary. The standards are a 50 $\Omega$  load at each port, a short or open at both ports and a line standard between the two ports.

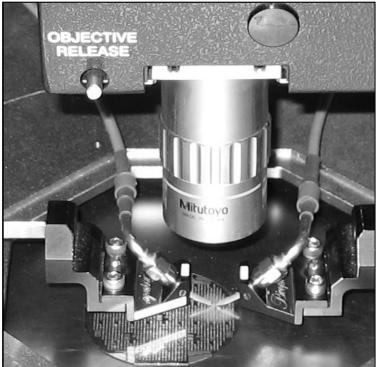

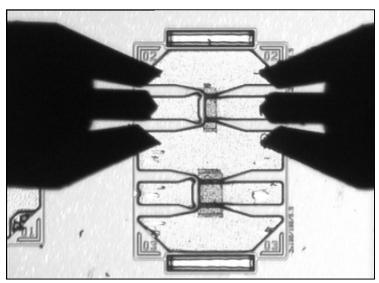

Figure 2.4 shows the HP8510C VNA used to measure the on-wafer GaN HEMT devices at IMEC. A close-up of the probe station is shown in Figure 2.5, where the probes are placed at the gate and drain terminal of the device. A microscope is used to place the probes at exact locations at ports of the device. This displays the enlarged image on a monitor as shown in Figure 2.6. Using this measurement setup, the complete small-signal RF characterisation of the devices was performed.

**Figure 2.3** The VNA measures both the magnitude and phase of all the complex S-parameters at the fundamental frequency of a device under test.

**Figure 2.4** The HP8510C VNA was used to measure the linear S-parameters of the on-wafer GaN HEMT devices at IMEC.

**Figure 2.5** The measurement probes are placed at the gate and drain terminal of the device. A microscope is used to display the image on a monitor in order to help with the placement of the probes.

**Figure 2.6** The image of the magnified  $T_{02}$  device topology is displayed on the monitor, which is used to accurately place the probes at the precise locations at the gate and drain terminals.

#### 2.4.2 Large-Signal Network Analyser

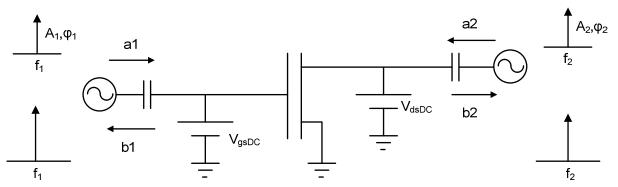

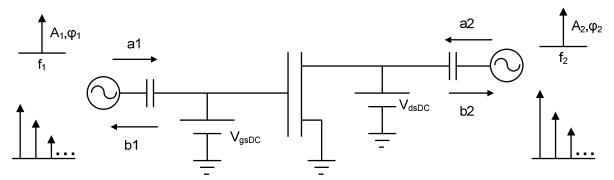

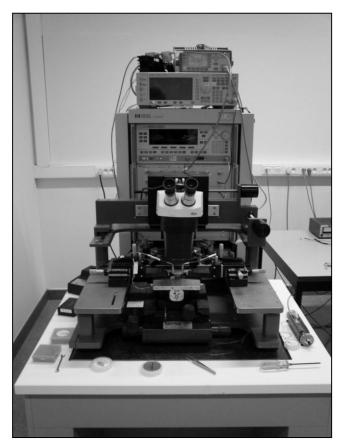

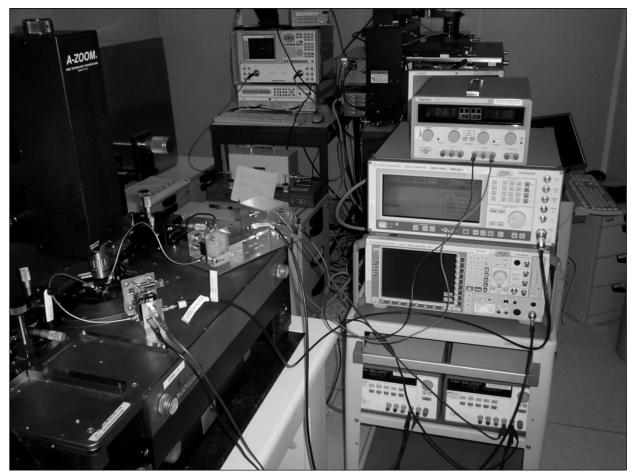

In order to verify nonlinear models and to use nonlinear measurements in the model generation process, amplitude and phase information of all the spectral components are necessary. The LSNA measures both the magnitude and phase of all harmonics of the incident and scattered travelling voltage waves at the device ports. The LSNA has two sources that can simultaneously excite both ports of the device as shown in Figure 2.7. Signals a<sub>1</sub>, a<sub>2</sub> represent the incident travelling power waves at port one and b<sub>1</sub>, b<sub>2</sub> the reflected travelling power waves at port two of the device. The LSNA sweeps the excitation power levels, but the excitation frequencies a<sub>1</sub> and a<sub>2</sub> are constant. The system also measures harmonics and intermodulation distortion (IMD) products of b<sub>1</sub> and b<sub>2</sub> waves at port one and port two respectively. Once the travelling power waves have been measured, the current and voltage wave forms can be calculated using Fourier theory. The LSNA seen in Figure 2.8 was used to measure the on-wafer GaN devices in this work and is located at the ESAT, K.U. Leuven, Belgium. It was used under the supervision of Prof. Dominique Schreurs. The LSNA setup has an RF bandwidth of 600MHz to 20GHz and the nonlinear measurements consist of single-tone and two-tone measurements over various bias conditions. The calibration process for the LSNA consists of three steps. The first is a linear calibration, which is followed by an absolute power calibration and finally a phase calibration [48].

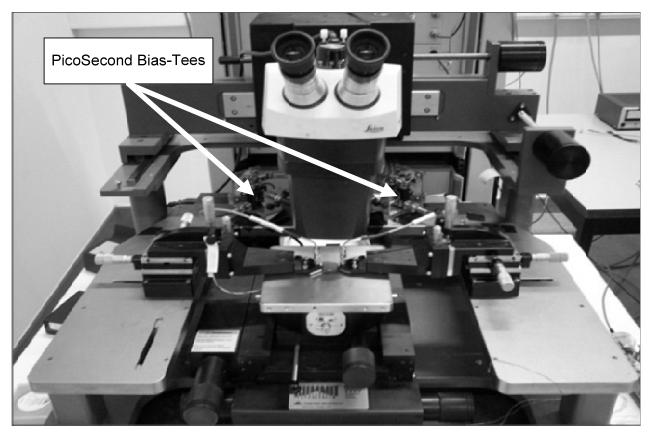

The LSNA is a nonlinear measurement instrument and thus it is possible to generate a two-tone excitation signal, which can be used to perform intermodulation distortion measurements. In earlier measurements, it was observed that memory effects appear in the lower MHz frequency range when using the LSNA. The effect can be attributed to the Agilent biasing network, which is modelled as a simple series capacitor, a parallel inductor and a series resistor. Table 2.3 summarises the model values according to datasheets for the inductor L, capacitor C and the resistance R.

|   | Agilent 11612B | Pulse Labs Picosecond 5580 |

|---|----------------|----------------------------|

| C | 800pF          | 0.22µF                     |

| L | 2μΗ            | 1.1mH                      |

| R | 1.5Ω           | 0.8Ω                       |

**Table 2.3**Comparison between model parameters for the Agilent 11612B and Pulse LabsPicosecond 5580 bias tees.

The problem originates from the time constant relating to the model values. The effect can be overcome by using the Pulse Labs Picosecond 5580 bias-tees described in chapter three. The setup is demonstrated in Figure 2.9, where the Agilent bias-tees are bypassed with the Picosecond 5580 bias-tees. The equivalent inductor, capacitor and resistor values for the

Picosecond 5580 bias-tees are also shown in Table 2.3.  $S_{21}$  for the Agilent bias tee becomes 1 only around 45MHz, while  $S_{21}$  of the Picosecond Pulse Labs bias-tees becomes 1 around 10KHz. The tone-spacing used in this work is 200KHz and by evaluating the  $S_{21}$  values of both the Agilent and Picosecond bias-tees, it is concluded that the Agilent bias-tees would be unacceptable for the two-tone experiments.

**Figure 2.7** The LSNA measures both the magnitude and phase of all the complex S-parameters at all the harmonics of a device under test.

**Figure 2.8** A photograph of the LSNA setup used at the ESAT-TELEMIC lab. The system has an RF bandwidth of 600MHz to 20GHz.

**Figure 2.9** The modified LSNA with the external Picosecond bias-tee used to perform the large-signal two tone measurements.

### **2.5 Conclusion**

In this chapter, an overview of GaN HEMT technology is given, along with the basic principles of the measurement instruments required in the modelling process. Before the characterisation can begin, a device selection process is followed to ensure that the optimal device of the desired topology is selected. It is very important to have a thorough understanding of the basic principles of the measurement instruments, which will ensure the correct interpretation of measured data. This chapter gives an overview of the VNA and LSNA. The linear S-parameters of the devices are measured using the VNA, which is used to extract the small-signal equivalent circuit parameters (ECP). From the small-signal ECP, the nonlinear models are constructed and verified using an LSNA.

#### **CHAPTER 3**

#### **Intermodulation Distortion Characterisation**

#### **3.1 Introduction**

Intermodulation distortion (IMD) predictions have become a critical part of microwave and RF amplifier design. Greater performance is required from amplifier and receiver circuits due to the development of new and more sophisticated modulation techniques. Intermodulation is unwanted in any system, as it creates spurious signals and generates minor to severe interference with operations. Thus, the ability to predict IMD allows for optimal system design and simulation. In the equivalent circuit model, the drain current source Ids is the main contributor to the nonlinear behaviour of the device [1], [7]. The I<sub>ds</sub> current derivatives are thus essential for the construction of models that can accurately predict nonlinear IMD. In this chapter, a measurement setup is investigated that is used to extract the higher order derivatives of the nonlinear drain current source  $I_{ds}(V_{gs}, V_{ds})$ . The derivatives and cross-derivatives of  $I_{ds}$  with respect to  $V_{gs}$  and  $V_{ds}$  are extracted directly from measurements. The technique was first applied in [6] to extract the coefficients of GaAs field effect transistor (FET) devices, where the cross-terms of the  $I_{ds}(V_{gs}, V_{ds})$  Taylor series expansion were successfully extracted. This technique is an extension of [9], where previously the cross-terms where neglected, also noted in [8], [10]. The goal of this chapter is to investigate if this extraction procedure can be applied to high-power gallium nitride (GaN) high-electron mobility transistors (HEMT) devices. The investigation starts by implementing the technique on a GaAs FET device measured at the University of Stellenbosch, then extending the measurement setup to measure on-wafer GaN HEMT devices at the Interuniversity Microelectronics Centre (IMEC) in Leuven, Belgium.

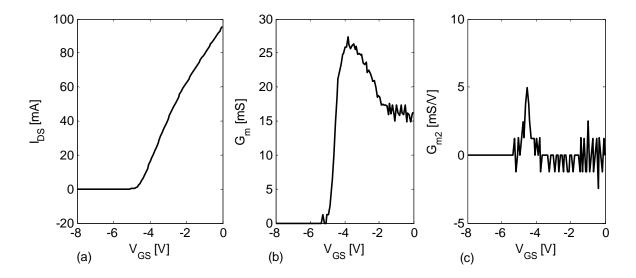

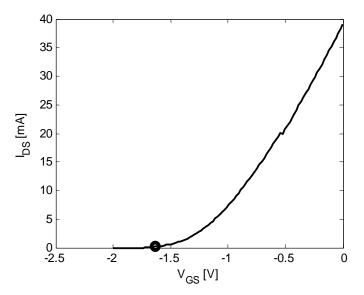

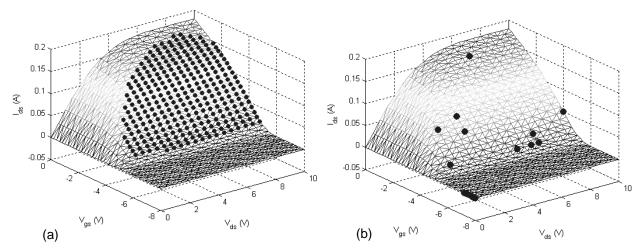

The question can be asked why a special measurement setup must be used to extract the higher order derivatives of the drain and why it cannot be obtained directly from DC measurements. One of the most important questions when evaluating  $I_{ds}(V_{gs},V_{ds})$  is if data derived from DC is still valid for AC analysis. It is generally considered that  $I_{ds}(V_{gs},V_{ds})$  can be represented as a memory-less function, which implies the quasistatic assumption. The quasistatic approximation implies that the response of each of the nonlinearities at a certain time does not depend on past time AC behaviour can be viewed as a succession of static DC excitations. Under this assumption, DC behaviour can indeed be used to predict AC performance. However, this is a theoretical assumption and is not adequate in practice [1], [2]. Derivatives cannot be extracted

from DC as a result of errors associated with successive differential operations. It is almost impossible to determine small-signal nonlinearities for Volterra analysis by differentiating the measured I/V characteristic. The repeated differentiation of the measured I/V curve introduces numerical noise, which in most cases becomes significantly large relative to the nonlinearity, as shown in Figure 3.1. The most accurate and widely used method is to extract the Taylor series coefficients from RF measurements. Thus any empirical model intended to predict very high signal-to-distortion ratios must be extracted from, or at least adjusted to, measured higher order AC data. In the same way that  $G_m$  and  $G_{ds}$  is extracted from measured linear S-parameter data, so too the higher order current derivatives must be extracted from higher order AC behaviour. The goal of this chapter is to describe the measurement techniques used to extract the nonlinear Taylor coefficients directly from measurements.

It is vital to understand the origins of distortion behaviour before undertaking the task of IMD characterisation. These principles are discussed in section 3.2. Section 3.3 gives an overview of the principles of Volterra series analysis, which is used as a basis to predict the intermodulation performance of the devices. In section 3.4, the nonlinear Taylor series model of the drain current source  $I_{ds}(V_{gs}, V_{ds})$  is presented. The full IMD characterisation procedure is discussed in section 3.5, which includes the measurement setups and extraction software used in this work. Section 3.6 documents the detailed methodology involved in the extraction process. The results and experiences gained during the study are documented in section 3.7, while section 3.8 gives the final comments of the work presented in this chapter.

**Figure 3.1** (a) The plot of measured DC drain current  $I_{DS}$  is shown, while (b) a noisy  $G_m$  is shown, which was obtained by directly differentiating  $I_{DS}$ . In (c) an extremely noise  $G_{m2}$  is plotted, which was determined by differentiating  $G_m$ .

## 3.2 Origin of Nonlinear Distortion Behaviour

Before a nonlinear model is developed and the task of IMD predictions undertaken, the fundamental principle and origin of nonlinear distortion behaviour should be fully understood. In this section, a mathematical analysis of an arbitrary nonlinearity will be used to demonstrate the origin of important nonlinear parameters. Only the basic principles are discussed in this section, but for the full mathematical analysis of the nonlinear phenomenon refer to [1], [3].

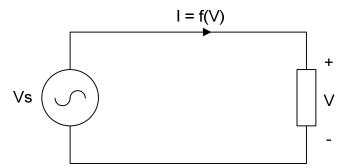

Figure 3.2 shows a general third order nonlinearity with an excitation  $V_S$  and a resulting current I. The source impedance is set to zero to simplify the mathematical analysis and thus V equals  $V_S$ . The current I can be found by substituting the source voltage  $V_S$  into a third order power series function that describes the nonlinear current expressed in equation (3.1) where a, b and c are constant, real coefficients. For the purpose of this example to simplify the mathematics,  $V_S$  is restricted to a two-tone excitation given by equation (3.2).

**Figure 3.2** A nonlinearity excited by voltage source  $V_s$  with the current a nonlinear function of the voltage V across the nonlinear device is used to demonstrate the mathematical origin of intermodulation distortion.

$$\mathbf{I} = \mathbf{a}\mathbf{V} + \mathbf{b}\mathbf{V}^2 + \mathbf{c}\mathbf{V}^3 \tag{3.1}$$

$$V_{s} = V = V_{1}\cos(\omega_{1}t) + V_{2}\cos(\omega_{2}t)$$

(3.2)

Substituting equation (3.2) into equation (3.1) results in three terms that can be grouped together to describe the order of the nonlinear current components. The total current in the nonlinear element is the sum of the currents components given by equations (3.3), (3.4) and (3.5).

$$i_a = aV_s(t) = aV_1 cos(\omega_1 t) + aV_2 cos(\omega_2 t)$$

(3.3)

$$\dot{i}_{b}(t) = bV_{s}^{2} = \frac{b}{2} \begin{cases} V_{1}^{2} + V_{2}^{2} + V_{1}^{2}\cos(2\omega_{1}t) + V_{2}^{2}\cos(2\omega_{2}t) \\ + 2V_{1}V_{2}[\cos((\omega_{1} + \omega_{2})t) + \cos((\omega_{1} - \omega_{2})t)] \end{cases}$$

(3.4)

$$i_{c}(t) = cV_{s}^{3} = \frac{c}{4} \begin{cases} V_{1}^{3}\cos(3\omega_{1}t) + V_{2}^{3}\cos(3\omega_{1}t) \\ + 3V_{1}^{2}V_{2}[\cos((2\omega_{1}+\omega_{2})t) + \cos((2\omega_{1}-\omega_{2})t)] \\ + 3V_{1}V_{2}^{2}[\cos((\omega_{1}+2\omega_{2})t) + \cos((\omega_{1}-2\omega_{2})t)] \\ + 3(V_{1}^{3} + 2V_{1}V_{2}^{2})\cos(\omega_{1}t) \\ + 3(V_{2}^{3} + 2V_{1}^{2}V_{2})\cos(\omega_{2}t) \end{cases}$$

(3.5)

The current component given by equation (3.3) is the result of the first term in equation (3.1) and is the linear or first order component. Equation (3.4) is quadratic term in equation (3.1) and is the second order component, while equation (3.5) is due to the cubic term and is the third order response. Trigonometric identities shown in equations (3.6) to (3.8) for squares and products of cosines were used to simplify equations (3.3) to (3.5).

$$\cos(\alpha) \cdot \cos(\alpha) = \frac{1}{2}\cos(\alpha - \beta) + \frac{1}{2}\cos(\alpha + \beta)$$

(3.6)

$$\cos(\alpha)^2 = \frac{1}{2} + \frac{1}{2}\cos(2\alpha)$$

(3.7)

$$\cos(\alpha)^3 = \frac{3}{4}\cos(\alpha) + \frac{1}{4}\cos(3\alpha)$$

(3.8)

In equations (3.3) to (3.5) it can be seen that several new frequency products are generated by a fairly simple nonlinearity. These equations can be used to explain a number of nonlinear effects that are common in RF devices and systems, such as harmonic generation, saturation, cross-modulation, AM-to-PM conversion and intermodulation. All these characteristics can serve as a figure of merit when defining different aspects of a system or circuits nonlinear behaviour. All these phenomena have been describe in literature [1], [3], but the most relevant to this thesis is harmonic and IMD.

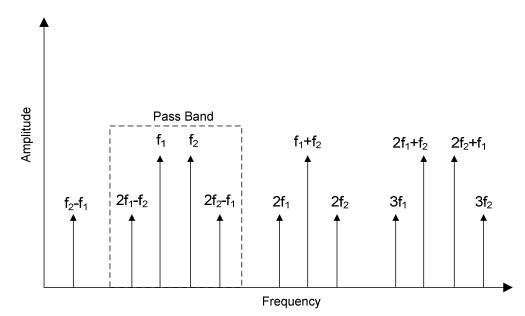

IMD is the result of two or more signals of different frequencies that are present at the input of a nonlinear device. These signals are mixed together and form additional signals at frequencies that are not at harmonic frequencies of the original input signals. The mixing frequencies are linear combinations of the terms in equations (3.3) to (3.5) and are expressed as  $\pm m\omega_1 \pm n\omega_2$ , except where m or n is equal to zero. The order of the distortion product is given by the sum of |m| + |n|. Even-order products usually occur at much higher or lower frequencies than the original signals and thus do not cause any interference problems. The products that warrant concern are the third order products that occur at  $2\omega_1-\omega_2$  and  $2\omega_2-\omega_1$  as they fall within the pass-band and are the strongest of all the odd-order products. This statement implies that these components are significantly close to the original signals. These are extremely difficult to reject with filters and are the main source of distortion in any system. Thus, it is extremely important that any nonlinear model should accurately predict third order IMD products.

**Figure 3.3** The distribution of harmonics and intermodulation products are plotted versus frequency for a two-tone excitation  $\omega_1$  and  $\omega_2$ . It can be seen that intermodulation products fall within the pass band.

#### **3.3 Principles of Volterra Series Analysis**

The standard analysis technique for distortion prediction in medium power systems has been Volterra series analysis, which can be divided into two approaches. The first is a transfer function approach where general n<sup>th</sup> order Volterra kernels are derived from first principles [1], [11]. However the method is fairly complex when applied to circuits with multiple nodes and

thus will not be considered. The second and most common technique is known as the method of nonlinear currents, which has the advantage that only the frequency components of interest need to be calculated. The following section is a summary of this approach, as demonstrated in [1], [2].

#### 3.3.1 Nonlinear Currents Method

The nonlinear currents method is an extension of the Volterra series and in this technique the current components are calculated using lower order voltage components. These current components are used to determine the voltage components of the same order, which in turn are used to calculate the next higher order current components. As mentioned, the advantage of this approach is that it is only necessary to calculate the frequency components of interest, thus it is rarely necessary to calculate the entire nonlinear transfer function.

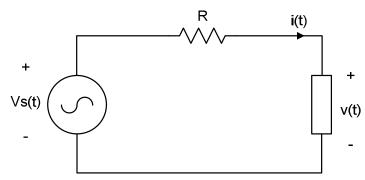

The circuit shown in Figure 3.4 is used to demonstrate the analysis procedure. The circuit consists of a voltage source, a linear resistor and a nonlinear conductance. The conductance has a voltage of v(t) across it and a current response i(t). The current/voltage relation is expressed in equation (3.9).

$$i = g_1 v + g_2 v^2 + g_3 v^3 + \dots$$

(3.9)

The Taylor series coefficients are given by  $g_n$ , while i(t) and v(t) represent the incremental current and voltage associated with the nonlinear conductance around the bias point. The voltage v(t) consists of all the mixing products. The sum of all  $n^{th}$  order mixing products is represented by  $v_n(t)$ , as shown in equation (3.10). The order of mixing products is defined by checking the subscript of the term, for example,  $v_1$  represents the first order product, while  $v_2$  the second order product and  $v_3$  the third order product. When two terms are multiplied, the order of the product is determined by adding the subscript values, for example,  $v_1v_2$  results in a third order product and  $v_2v_3$  in a fifth order product.

$$\mathbf{v} = \mathbf{v}_1 + \mathbf{v}_2 + \mathbf{v}_3 + \mathbf{v}_n + \dots \tag{3.10}$$

$$\mathbf{v} = \mathbf{v}_1 + \mathbf{v}_2 + \mathbf{v}_3 \tag{3.11}$$

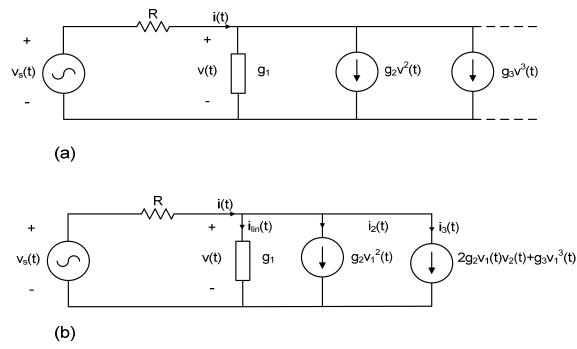

The circuit in Figure 3.4 is now transformed using the substitution theorem, which is discussed in the next section, and redrawn as shown in Figure 3.5(a). The nonlinearity is transformed to a linear conductance and several nonlinear current sources. The linear conductance represents the

linear part of equation (3.9) and the current sources represent the nonlinear terms in equation (3.9). The goal is to only predict up to the third order products (IM3) and thus the Taylor series and the mixing products are limited to the third degree. Equation (3.10) can be rewritten only to include the third degree and lower terms, as shown in equation (3.11).

**Figure 3.4** The circuit used to demonstrate the nonlinear currents method consists of a voltage source  $v_s(t)$ , a linear resistor R and a weakly defined nonlinearity with a voltage drop of v(t).

The next step is to determine the second  $v^2$  and third  $v^3$  order voltage terms in equation (3.9). The determination of the  $v^2$  term will be demonstrated as an example. Equation (3.12) shows the product of the terms in equation (3.11), while equation (3.13) expresses all the terms after the multiplication procedure. The result is a number of terms ranging in orders from second degree  $v_1^2$  to sixth degree  $v_2^3$ . The only terms of interest are the third degree and lower terms. The first two terms in equation (3.14) are third degree and lower, while the terms in the square bracket are higher than third degree and can be neglected. The result is that equation (3.14) can be simplified to equation (3.15). The same technique is used to determine the third order term  $v^3$ , which leads to equation (3.16).

$$\mathbf{v}^{2} = (\mathbf{v}_{1} + \mathbf{v}_{2} + \mathbf{v}_{3})(\mathbf{v}_{1} + \mathbf{v}_{2} + \mathbf{v}_{3})$$

(3.12)

$$\mathbf{v}^{2} = \mathbf{v}_{1}^{2} + \mathbf{v}_{1}\mathbf{v}_{2} + \mathbf{v}_{1}\mathbf{v}_{3} + \mathbf{v}_{2}\mathbf{v}_{1} + \mathbf{v}_{2}^{2} + \mathbf{v}_{2}\mathbf{v}_{3} + \mathbf{v}_{3}\mathbf{v}_{1} + \mathbf{v}_{3}\mathbf{v}_{2} + \mathbf{v}_{3}^{2}$$

(3.13)

$$\mathbf{v}^{2} = \mathbf{v}_{1}^{2} + 2\mathbf{v}_{1}\mathbf{v}_{2} + [2\mathbf{v}_{1}\mathbf{v}_{3} + 2\mathbf{v}_{2}\mathbf{v}_{3} + \mathbf{v}_{2}^{2} + \mathbf{v}_{3}^{2}]$$

(3.14)

$$\mathbf{v}^2 = \mathbf{v}_1^2 + 2\mathbf{v}_1\mathbf{v}_2 \tag{3.15}$$

$$v^3 = v_1^3$$

(3.16)

22

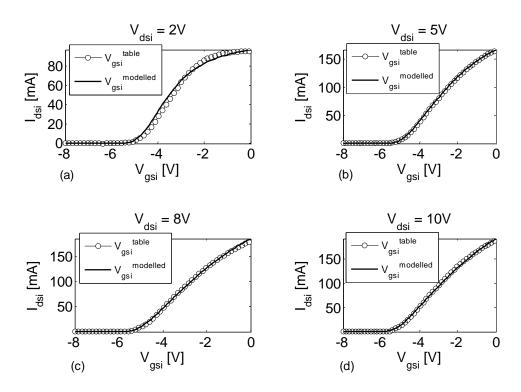

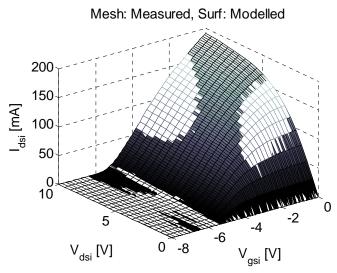

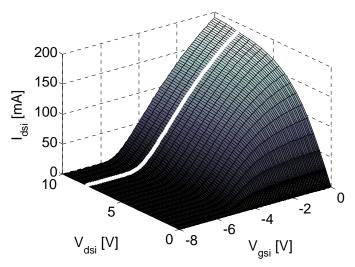

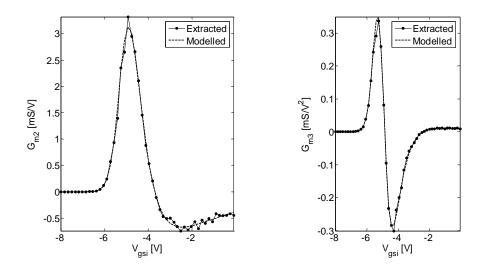

**Figure 3.5** In (a) the nonlinear resistor has been converted to a linear resistor and a set of nonlinear current sources. In (b) the current sources have been rearranged so that each represents a single order of mixing products.