# Simulation and Verification Software for Superconducting Electronic Circuits

by Johannes Arnoldus Delport

Dissertation presented for the degree of Doctor of Philosophy in Electrical and Electronic Engineering in the Faculty of Engineering at Stellenbosch

Supervisor: Prof. Coenrad Johann Fourie Electrical and Electronic Engineering Stellenbosch University

April 2019

#### Declaration

By submitting this dissertation electronically, I declare that the entirety of the work contained therein is my own, original work, that I am the sole author thereof (save to the extent explicitly otherwise stated), that reproduction and publication thereof by Stellenbosch University will not infringe any third party rights and that I have not previously in its entirety or in part submitted it for obtaining any qualification.

This dissertation includes four original papers published in peer-reviewed journals or books and zero unpublished publications. The development and writing of the papers (published and unpublished) were the principal responsibility of myself and, for each of the cases where this is not the case, a declaration is included in the dissertation indicating the nature and extent of the contributions of co-authors.

April 2019

Copyright © 2019 Stellenbosch University All rights reserved

#### Abstract

The dissertation presents simulation and verification software for both high- and low-level designs with emphasis on superconducting integrated circuits. A static timing analysis tool called SuperSTA is introduced as a method of analysing high-level superconducting designs in terms of the longest delay from any input to any output. This method of analysis provides metrics with which a design can be scrutinized and judged based on predefined criteria. A superconducting circuit simulator, JoSIM, is also introduced as a modified nodal analysis transient simulator which uses trapezoidal integration to solve a circuit netlist. A SPICE syntax circuit netlist is analysed and a matrix constructed, whereafter the Ax = b linear algebra problem is solved using the KLU algorithm. JoSIM incorporates unique features such as a modified nodal phase analysis method, parametrization through expression parsing and alphanumeric node names. JoSIM includes a built-in graphical user interface for direct result verification. This is achieved using the cross-platform graphical library FLTK as well as Python's Matplotlib library. The design of the simulator and all the incorporated components are discussed in a step-by-step manner. JoSIM is compared to existing superconducting circuit simulators and judged in terms of accuracy and ability to simulate very large scale superconducting circuit designs. Results are investigated and recommendations for future improvements and optimizations to the simulator are discussed

#### Opsomming

Die dissertasie bied simulasie- en verifikasieprogrammatuur vir beide ho- en laevlakontwerpe, met die klem op supergeleidende gentegreerde stroombane. 'n Statiese tyd-analiese program genaamd SuperSTA word bekendgestel as 'n metode om hovlak supergeleidende ontwerpe te analiseer in terme van die langste vertraging van enige intree na enige uittree. Hierdie metode van analise verskaf maatstawwe waarteen 'n ontwerp ondersoek kan word en beoordeel word op grond van voorafbepaalde kriteria. 'n Supergeleidende stroombaan simuleerder, JoSIM, word ook bekendgestel as 'n aangepaste nodus tydsgebied analiese wat trapezoidal integrasie gebruik om 'n stroombaan op te los. 'n SPICE-sintaks stroombaan intree word geanaliseer en 'n matriks gebou, waarna die Ax = b linere algebra-probleem opgelos word met behulp van die KLU-algoritme. JoSIM bevat unieke eienskappe soos 'n aangepaste nodus fase analise metode, parametrisering deur uitdrukking ontleding en alfanumeriese nodus name. JoSIM sluit 'n ingeboude grafiese gebruikerskoppelvlak in vir direkte resultaatverifikasie. Dit word behaal deur die grafiese biblioteek FLTK sowel as Python se Matplotlib-biblioteek te gebruik. Die ontwerp van die simuleerder en al die ingeslote komponente word stap-vir-stap bespreek. JoSIM word vergelyk met bestaande supergeleidende stroombaansimuleerders en beoordeel in terme van akkuraatheid en vermo om supergeleidende kringontwerpe te kan simuleer. Resultate word ondersoek en aanbevelings vir toekomstige verbeteringe en optimalisering aan die simuleerder word bespreek

#### Acknowledgements

I would like first and foremost thank my parents for all their years of support and motivation. They built the bridge on which I stand and for that I am forever grateful. Second, I would like to thank my soon to be loving wife for all the late night cups of coffee and words of support when I really needed. Third, I would like to extend my special gratitude to Dr Kyle Jackman and Mr Paul le Roux for their support and endless wisdom during times of mathematical strife and debugging nightmares. Last, I would like to thank Professor Coenrad Fourie for all his patience and wisdom when it was needed, without him all of this would not have been possible. My gratitude also extends to all of my research colleagues, past and present, who helped with testing and debugging of the software.

# Contents

| 1        | Intr | roduction 1                                                                                                                                    |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1.1  | Motivation                                                                                                                                     |

|          | 1.2  | Background on Computing and Superconductivity                                                                                                  |

|          |      | 1.2.1 Digital Devices                                                                                                                          |

|          |      | 1.2.2 Sensors and Filters 55                                                                                                                   |

|          |      | 1.2.3 Simulation in computing                                                                                                                  |

|          | 1.3  | Objectives of Dissertation                                                                                                                     |

|          |      | 1.3.1 Objectives                                                                                                                               |

|          |      | 1.3.2 Document Layout                                                                                                                          |

| <b>2</b> | Eleo | ctronic Design Automation in Superconductivity 9                                                                                               |

|          | 2.1  | Introduction                                                                                                                                   |

|          | 2.2  | Design Process                                                                                                                                 |

|          |      | 2.2.1 High Level                                                                                                                               |

|          |      | 2.2.2 Synthesis                                                                                                                                |

|          |      | 2.2.3 Analogue Simulation                                                                                                                      |

|          |      | 2.2.4 Optimization                                                                                                                             |

|          |      | 2.2.5 Layout and Fabrication                                                                                                                   |

|          |      | 2.2.6 Technology Computer Aided Design                                                                                                         |

|          | 2.3  | $Conclusion \dots \dots$                 |

| 3        | Hig  | h Level Verification 15                                                                                                                        |

|          | 3.1  | Introduction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $15$                                                                                 |

|          | 3.2  | SuperSTA                                                                                                                                       |

|          |      | 3.2.1 Design Flow                                                                                                                              |

|          |      | 3.2.2 Pre-Placed                                                                                                                               |

|          |      | 3.2.3 Post-Placed                                                                                                                              |

|          | 3.3  | $Results \ldots \ldots$ |

|          | 3.4  | Conclusion                                                                                                                                     |

| 4        | Ana  | alogue Simulation 21                                                                                                                           |

|          | 4.1  | Introduction                                                                                                                                   |

|          | 4.2  | Josephson junction                                                                                                                             |

|          | 4.3  | JSIM                                                                                                                                           |

|          | 4.4  | PSCAN                                                                                                                                          |

|          | 4.5  | WRspice                                                                                                                                        |

|          | 4.6  | Conclusion                                                                                                                                     |

| <b>5</b> | JoS        | IM - Development                       | 29         |

|----------|------------|----------------------------------------|------------|

|          | 5.1        | Introduction                           | 29         |

|          | 5.2        | Design Flow from Input to Output       | 30         |

|          |            | 5.2.1 Input                            | 30         |

|          |            | 5.2.2 Matrix Setup                     | 31         |

|          |            | 5.2.3 Solution Calculation             | 32         |

|          |            | 5.2.4 Output Handling                  | 32         |

|          | 5.3        | Components                             | 33         |

|          |            | 5.3.1 Resistor                         | 33         |

|          |            | 5.3.2 Inductor                         | 34         |

|          |            | 5.3.3 Capacitor                        | 34         |

|          |            | 5.3.4 Josephson Junction               | 35         |

|          |            | 5.3.5 Voltage and Current Sources      | 40         |

|          |            | 5.3.6 Lossless Transmission Line       | 44         |

|          |            | 5.3.7 Mutual Inductance                | 44         |

|          | 5.4        | Control Commands                       | 45<br>46   |

|          | 0.4        |                                        | 40<br>46   |

|          | F F        | 5.4.1 Parameters                       |            |

|          | 5.5        | Chicken and Egg                        | 48         |

|          | 5.6        | Phase Simulation                       | 48         |

|          |            | 5.6.1 Phase Inductor                   | 49         |

|          |            | 5.6.2 Phase Capacitor                  | 49         |

|          |            | 5.6.3 Phase Resistor                   | 50         |

|          |            | 5.6.4 Phase JJ                         | 50         |

|          |            | 5.6.5 Phase Lossless Transmission Line | 51         |

|          |            | 5.6.6 Phase Mutual Inductance          | 51         |

|          |            | 5.6.7 Phase Voltage Source             | 52         |

|          |            | 5.6.8 Phase Source                     | 52         |

|          | 5.7        | Conclusion                             | 52         |

| 0        | та         |                                        | <b>F</b> 0 |

| 6        |            | IM - Results                           | 53         |

|          | 6.1        | Introduction                           | 53         |

|          |            | IV Curve                               | 53         |

|          | 6.3        | Small Simulations                      | 54         |

|          | 6.4        | Medium to Large Scale Simulations      | 57         |

|          | 6.5        | Conclusion                             | 60         |

| _        | <b>T</b> 7 |                                        |            |

| 7        |            | y Large Scale Design Simulation        | 62         |

|          | 7.1        | Introduction                           | 62         |

|          | 7.2        | Data Structure Considerations          | 62         |

|          | 7.3        | Parallel Processing                    | 63         |

|          | 7.4        | Optimizations in the Math Engine       | 64         |

|          | 7.5        | Conclusion                             | 64         |

| 0        | a          |                                        |            |

| 8        | Con        | nclusion                               | 66         |

| Bi       | bliog      | graphy                                 | 67         |

| Aj       | ppen       | dices                                  |            |

## $\mathbf{A}$

- в

- С

- Ũ

- D

- $\mathbf{E}$

# List of Figures

| $1.1 \\ 1.2 \\ 1.3 \\ 1.4 \\ 1.5 \\ 1.6$                                                   | CMOS logic using voltage levels                                                                                                           | $2 \\ 3 \\ 4 \\ 5 \\ 6$                                                            |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 2.1<br>2.2<br>2.3<br>2.4                                                                   | Suggested standard design flow for superconducting circuit design                                                                         | 10<br>11<br>11<br>13                                                               |

| $3.1 \\ 3.2 \\ 3.3$                                                                        | Basic design flow of SuperSTA4-bit KSA simulated as DUT at HDL level4-bit KSA simulated with a clock speed higher than maximum identified | 16<br>19<br>20                                                                     |

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \end{array}$ | Basic example of a Josephson junction                                                                                                     | 22<br>22<br>23<br>23<br>24<br>25<br>26<br>27<br>27                                 |

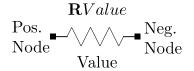

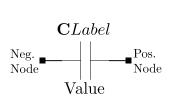

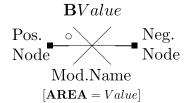

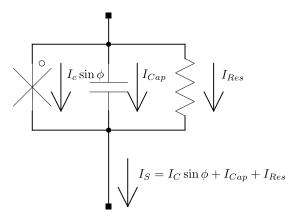

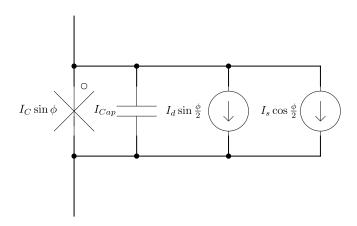

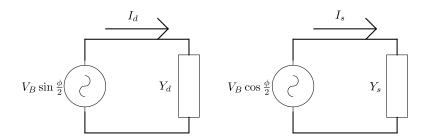

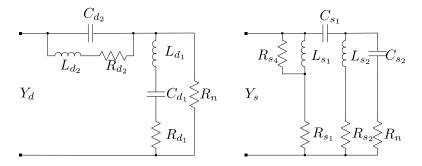

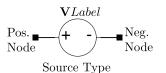

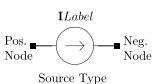

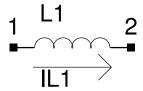

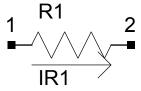

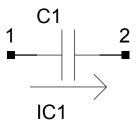

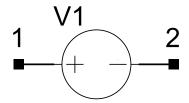

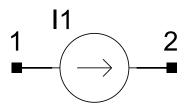

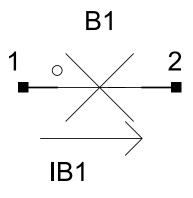

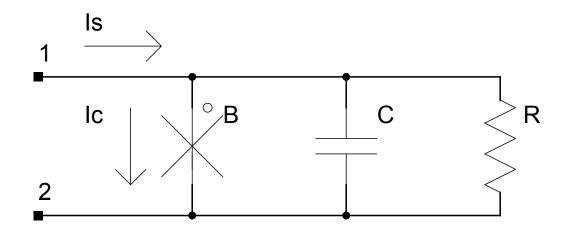

| 5.14                                                                                       | Sum and difference admittance equivalent circuits                                                                                         | $30 \\ 30 \\ 31 \\ 31 \\ 33 \\ 34 \\ 35 \\ 36 \\ 40 \\ 40 \\ 40 \\ 40 \\ 41 \\ 11$ |

| 5.15                                                                                       | Example of a PWL function depicting the relevant values                                                                                   | 41                                                                                 |

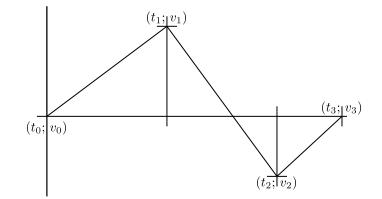

| 5.16 | Example of a pulse function depicting the relevant values                      | 42 |

|------|--------------------------------------------------------------------------------|----|

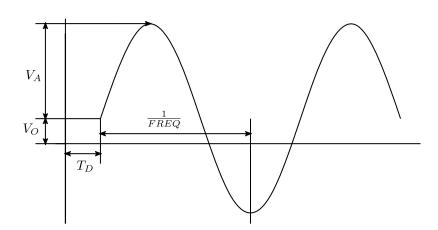

| 5.17 | Example of a sinusoidal function depicting the relevant values                 | 43 |

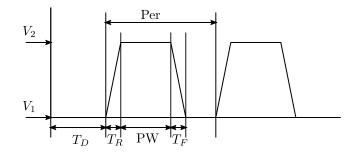

| 5.18 | Example of a custom function depicting a waveform line of [0 1 2 3 2 1 0] with |    |

|      | periodicity enabled to create a triangle wave                                  | 43 |

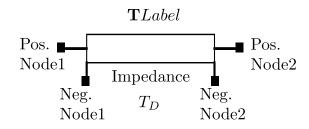

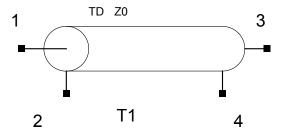

| 5.19 | A basic transmission line element                                              | 44 |

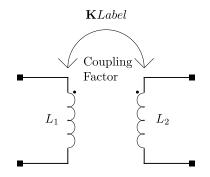

| 5.20 | A basic mutual inductance element                                              | 45 |

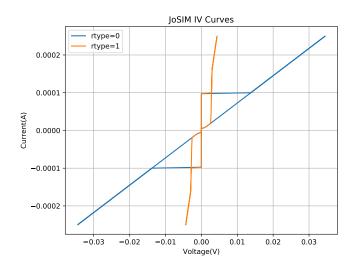

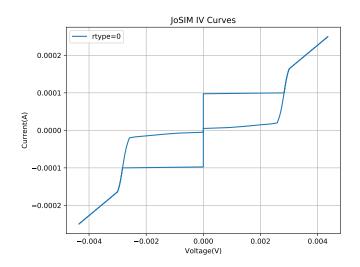

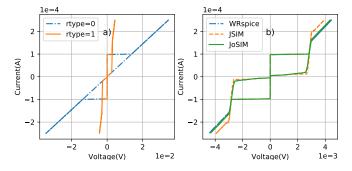

| 6.1  | JoSIM IV curves                                                                | 53 |

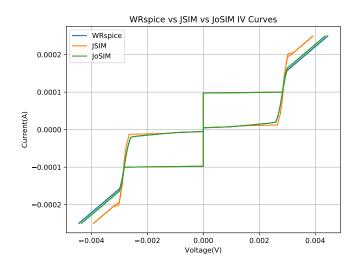

| 6.2  |                                                                                | 54 |

| 6.3  |                                                                                | 54 |

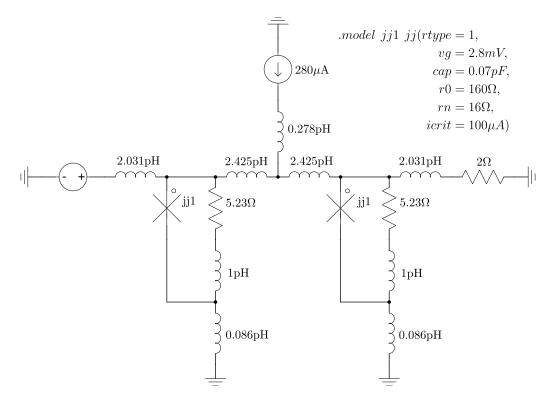

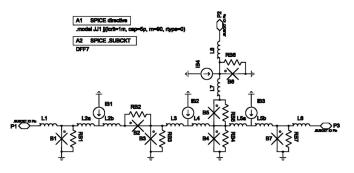

| 6.4  | Basic JTL used to test small simulations                                       | 55 |

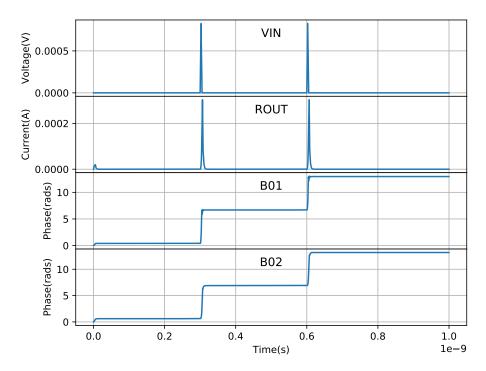

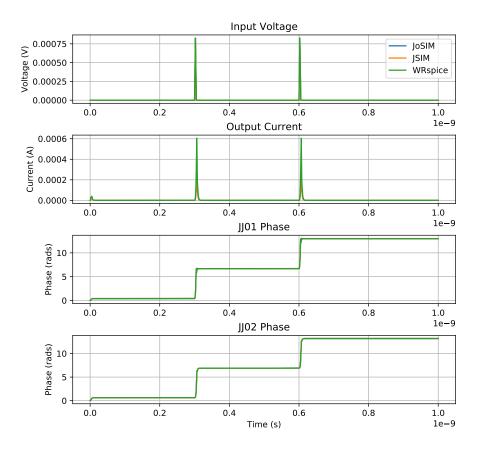

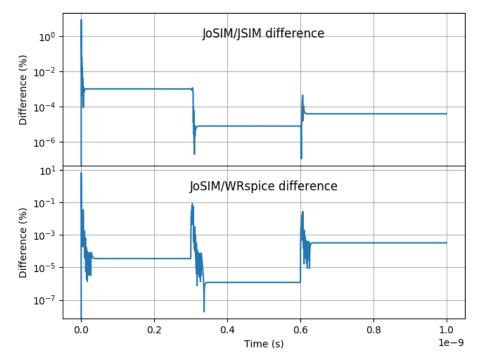

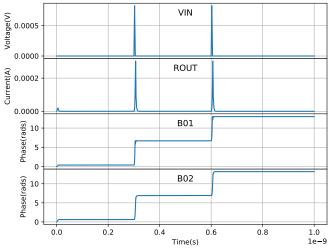

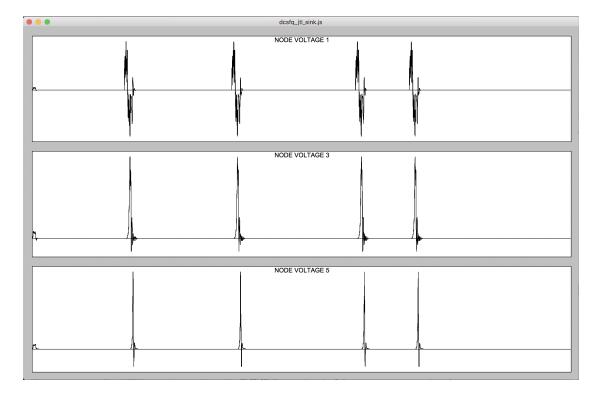

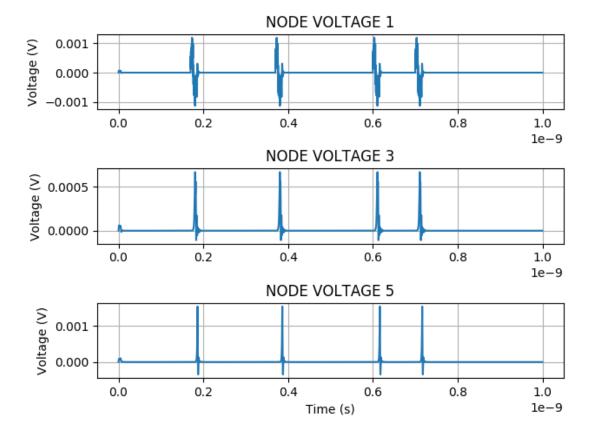

| 6.5  | Results of the JTL simulation performed with JoSIM                             | 56 |

| 6.6  | Comparison of the results for the JTL between JSIM, JoSIM and WRspice          | 56 |

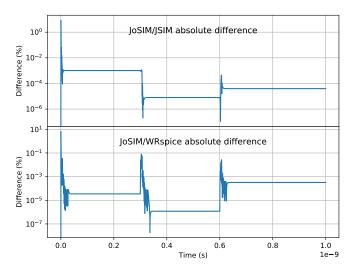

| 6.7  | Error percentage of JoSIM compared to JSIM and WRspice                         | 57 |

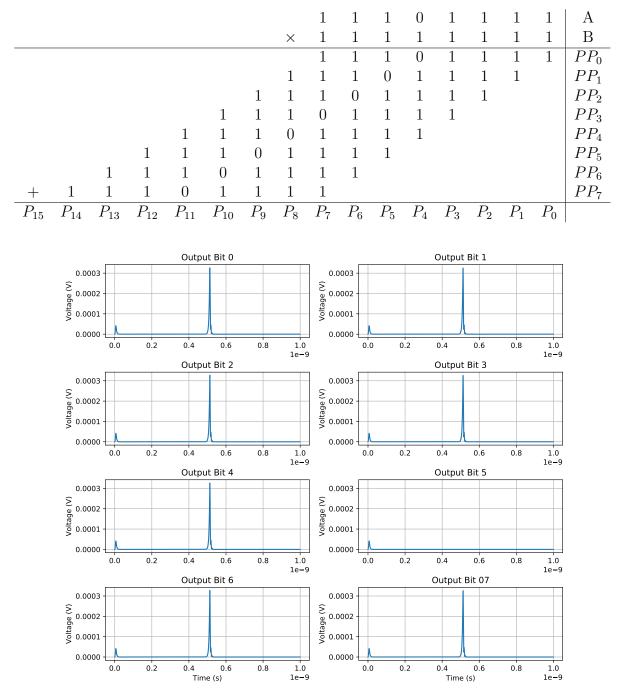

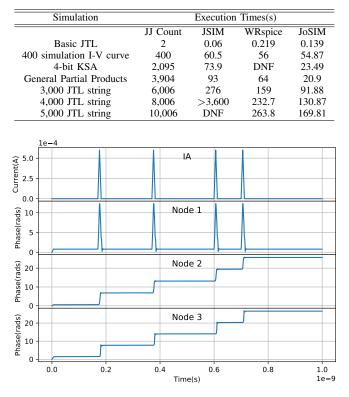

| 6.8  | Results of the 7th partial product                                             | 58 |

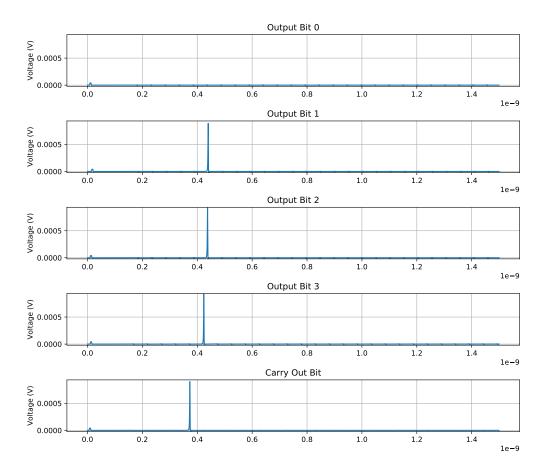

| 6.9  | Output of the 4-bit KSA simulation                                             | 59 |

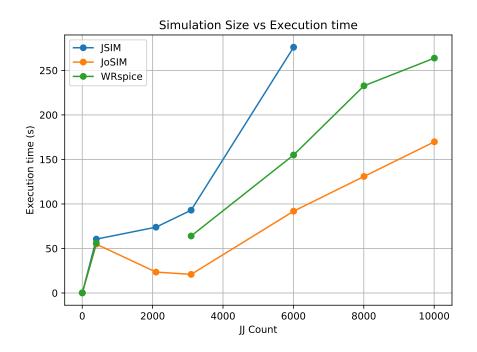

| 6.10 | Execution time vs JJ count                                                     | 61 |

# List of Tables

| 3.1          | Gate-delay timings for a RSFQ cell library | 18       |

|--------------|--------------------------------------------|----------|

|              | Shunting yard conversion to a RPN stack    |          |

| $6.2 \\ 6.3$ | General binary partial product generation  | 59<br>60 |

# Chapter 1

## Introduction

## 1.1 Motivation

With Moore's Law[1] approaching its inevitable limit, we look towards alternative technologies to replace complementary metal-oxide-semiconductors (CMOS) in the high-speed computing domain. This end is being approached from both an energy efficiency and a physical limitations point. As devices become smaller, a need to reduce the amount of components and materials used arises. When these components and materials are reduced or interchanged for others, trade-offs are made to the energy efficiency. This battle can only go on until one reaches a hard limit. We therefore aim our sights towards an entirely different technology.

One such technology is to use superconductors to produce a highly energy efficient form of computing that would far exceed the current limitations seen by CMOS[2]. The resistive property of a material is proportional to the temperature and physical area of the material. Resistance accounts for the majority of energy loss in electrical components. To therefore minimize the resistance of a material it would be crucial to reduce the temperature. When the temperature has been sufficiently reduced, the resistance becomes almost non-existent and the material enters a superconducting state[3]. Current that flows in a superconducting material can do so indefinitely as there is no resistance for it to lose energy through.

When two superconducting materials are brought very close to each other, a device called a Josephson junction (JJ) can be created wherein the current in one superconductor can be passed to another if the current exceeds a critical value[4]. We can equate this to the switching of a transistor in conventional CMOS. These JJs can be used to build logic devices, which have been shown to reach clock frequencies close to the terahertz range[5].

Unlike the well established design software found in the CMOS domain, the superconducting circuit (SC) domain lacks the necessary tools to design and fabricate complex computing designs. The development of SC simulation software is what motivates this work.

## **1.2** Background on Computing and Superconductivity

#### **1.2.1** Digital Devices

Superconducting digital devices can be created to operate using numerous technologies such as rapid single flux quanta (RSFQ), adiabatic quantum flux parametron (AQFP) and reciprocal quantum logic (RQL). Each technology is unique in its own way and vastly different to CMOS.

#### 1.2.1.1 CMOS

CMOS is a technology that was developed by Fairchild Semiconductor International, Inc. in the early 1960s. The complementary part of the name refers to the p-type and n-type metal-oxide-semiconductor field-effect-transistors (MOSFET) that almost all CMOS logic consists of. CMOS forms the basis of modern day computing.

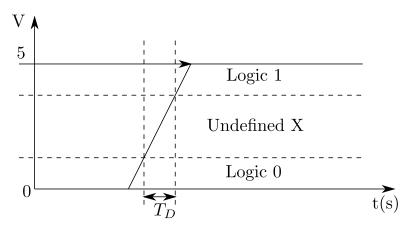

In CMOS a logical 1 is defined as a state where the voltage measured at a point to ground is within the threshold of some value, usually 5V, and the logic 0 is defined when the voltage is close or equal to 0V. Any state between these threshold values is undefined and causes undefined behaviour. The rise and fall of the voltage between levels does not occur instantly and therefore creates a delay in the system which needs to be compensated for. This concept is illustrated in Figure 1.1.

Figure 1.1: CMOS logic using voltage levels

#### 1.2.1.2 RSFQ

RSFQ is a technology that was developed by Likharev's research group at Moscow State University circa 1985[6]. RSFQ circuits are driven by single flux quantum (SFQ) voltage pulses which are defined by an integration of voltage over time where the result is exactly 1 magnetic flux quantum ( $\Phi_0$ ) or rather a fluxon (1.1). These fluxons are stored in superconducting loops consisting of inductors and JJs.

$$\int V(t)dt = \Phi_0 \equiv \frac{\hbar}{2e} \approx 2.07 \text{mV} \times \text{ps}$$

(1.1)

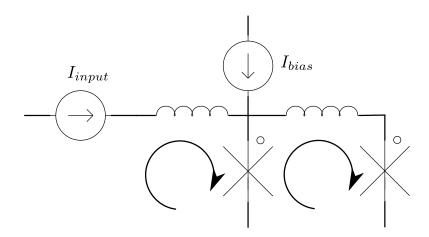

Each superconductive loop can store exactly an integer number of fluxons, and when configured with the correct amount of input and bias current, passes a fluxon on to the next superconductive loop. When a fluxon is present in a loop we call it a logic 1 and when a fluxon is absent a logic 0. Using this convention it is possible to build a pulse based family of logic gates.

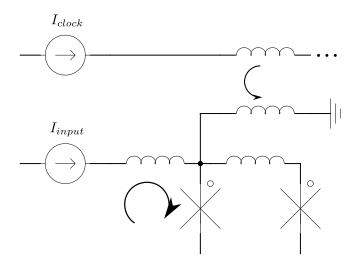

Figure 1.2: RSFQ pulse storage in superconducting loops

When an SFQ pulse arrives at the input in the circuit shown in Figure 1.2, it is stored in the initial loop until the bias current is greater than the critical current of the junction, causing a switch to occur and the pulse to be moved to the second loop.

RSFQ technology has shown the capability to be used for very-large-scale integration (VLSI) through a complete 8 bit microprocessor called CORE1. CORE1 was developed by Yokohama National University in collaboration with Nagoya University[7]. This design has been optimized quite a few times since the first release and is currently at the 4th iteration[8].

RSFQ is DC biased and therefore has static power dissipation which makes it less suitable for VLSI when compared to derivations like ERSFQ or ESFQ[9] and other technologies such as AQFP and RQL.

#### 1.2.1.3 AQFP

AQFP was developed by Professor Yoshikawa's research laboratory at Yokohama National University circa 2013[10]. Similar to RSFQ fluxons are stored in superconducting loops which consist of inductors and JJs. These circuits are AC biased which results in extremely low power dissipation.

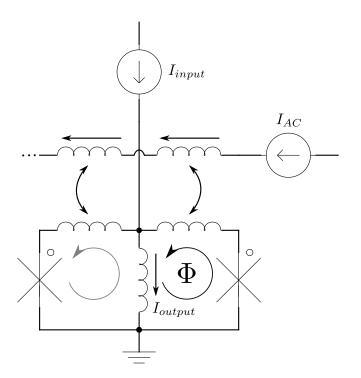

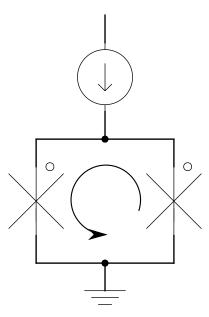

The most basic AQFP gate consists of 2 superconducting loops called a quantum flux parametron (QFP). The bias line, which consists of inductors, is mutually coupled to this QFP. When the bias is increased in the presence of a small input current, the fluxon moves between the two loops. The QFP represents a logic 0 when the fluxon is in the left loop and a 1 when it is in the right loop. We illustrate this concept in Figure 1.3.

Due to its AC nature, AQFP has almost zero power dissipation and can thus be scaled almost indefinitely for VLSI designs. This AC bias does however have the drawback of not being as fast as DC based RSFQ due to the limit of the microwave frequency generated using room-temperature electronics.

Figure 1.3: AQFP logic with a fluxon in the right loop

#### 1.2.1.4 RQL

RQL is a low power superconductor logic family developed by Northrop Grumman Systems Corp. circa 2011[11]. Like AQFP it is an AC biased logic family, however the logic is a lot more similar to RSFQ. RQL was patented by Northrop Grumman and therefore very little external research is conducted on the applications of this technology.

In RQL the clock is generated using an AC signal which also acts as the bias for the JJs through the mutually coupled inductors. Similar to RSFQ a fluxon is stored in a superconducting loop and is transferred to the next loop when the bias exceeds the junction critical current. The basic idea behind RQL is demonstrated in Figure 1.4. This technology, like AQFP, is speed-limited to the maximum speed of the microwave frequency generating circuitry and due to the AC bias retains similar low power dissipation qualities.

Figure 1.4: RQL design concept

## 1.2.2 Sensors and Filters

Superconductivity in digital electronics require very low temperatures, often close to absolute zero. At this temperature these devices become very susceptible to external interference such as external magnetic fields. This can be advantageous in some cases such as with superconducting quantum interference devices (SQUID) and superconducting quantum interference filters (SQIF).

### 1.2.2.1 SQUIDs

A SQUID is a device that consists of 2 JJs to form the superconductive loop depicted in Figure 1.5. SQUIDs are extremely sensitive to variations in current due to external magnetic fields and therefore are useful in systems where measurement accuracy is of utmost importance.

SQUIDs are mainly used in medical fields to measure neural activity as well as magnetic resonance imaging (MRI). SQUIDs can also be used in mining exploration to measure geothermal energy. These devices form the basis for some quantum computing applications[12].

Figure 1.5: A typical superconducting quantum interference device

#### 1.2.2.2 SQIFS

SQIFs are a relatively new application of the JJ where it is used in filter applications. Basic designs for SQIFs include multiple SQUID loops attached in an array with varying sizes[13]. We demonstrate a basic example of a SQIF array in Figure 1.6.

SQIFs work particularly well when used in sensitive magnetometry, due to its non-periodic voltage respone and large negative spike at zero magnetic field. The use of SQIFs in the RF domain has also been shown in recent studies[14].

Figure 1.6: An example of a superconducting quantum interference filter

### 1.2.3 Simulation in computing

Any type of computing technology requires some form of computer aided simulation software that would enable the user to verify the device operation before physically fabricating the device. Smaller designs such as simplistic filters can be mathematically verified, however in complex electronic systems this can no longer be done by hand.

The purpose of any computer aided circuit simulation software is simply to solve a set of simultaneous linear equations which can be grouped as

$$\mathbf{A}\mathbf{x} = \mathbf{b} \tag{1.2}$$

where **A** is a  $m \times n$  matrix of coefficients, **x** a vector of unknown variables and **b** a vector of known values.

In the early 1970s, a research group at the University of California Berkeley created a simulation program with integrated circuit emphasis (SPICE)[15]. What SPICE allowed them to do was solve an electronic circuit of theoretically any complexity by applying nodal analysis, essentially Kirchoff's current law (KCL), to the design creating a matrix of conductances that is used to solve the voltage at every node within the design.

Since its conception SPICE has seen many variants[16][17], with the latest being SPICE3F whereafter it became open domain and the base for all modern day commercial and non-commercial circuit simulators.

With the advancement of computing systems, new methods of simulation were also developed. These simulation methods are based on a higher level of abstraction where it is no longer necessary to see what components are physically connected in the device but rather what the behavioural function of the device would be given a specific input. This method of simulation is called high level verification and can be done using hardware description language (HDL)[18][19]. This method of circuit design spawned two programming languages, very high speed integrated circuit (VHSIC) hardware description language (VHDL)[20] and Verilog HDL[21].

HDL allows the user to describe the function of a circuit on a higher level and verify operation through logic simulation. This is a lot faster than SPICE, however, it only verifies operation and does not account for any electrical properties in the design.

## **1.3** Objectives of Dissertation

### 1.3.1 Objectives

In light of the limited availability of advanced SC simulation software for both analogue and high level verification, we propose a new SPICE type simulation engine JoSIM and a static timing analysis tool (SuperSTA) for high level timing verification.

JoSIM is specifically aimed to overcome the challenges faced when attempting to simulate designs that incorporate superconducting elements such as the JJ. SuperSTA uses results obtained from analogue simulations to apply timing verification to SC designs in both analogue form as well as high level description.

The simulation engine and all algorithms mentioned in this work are written in C++ and compiled to be executable on three major operating systems Microsoft Windows, Apple Mac OS and Linux.

We now summarise the required objectives to ensure the success of this dissertation:

- 1. Investigation of the available electronic design automation software within the superconducting circuit design domain.

- 2. Creation of high level verification tool for static timing analysis.

- 3. Creation of a SPICE simulator that is capable of interpreting superconducting elements.

- 4. Implementation of faster numerical solvers to improve simulation time and solution accuracy.

- 5. Attempt implementation of non-conventional superconducting elements such as the microscopic tunnel junction.

- 6. Investigate and derive phase based simulation techniques for more accurate superconducting simulation results.

- 7. Simulation of very large scale circuits to allow verification of microprocessor level designs within reasonable time.

#### 1.3.2 Document Layout

In Chapter 2 we discuss the state of electronic design automation (EDA) in the superconducting circuit domain and provide some insight into the steps involved when designing and creating a superconducting integrated circuit. Each step is discussed in detail with examples and what the equivalent would be within the existing CMOS EDA design flow. We take note of the large efforts made by research foundations to attempt to get the design flow for superconductivity to a level where it can compete with CMOS. We make some recommendations on fields that require investigation to help bolster the strength of EDA in superconductivity

High level verification and the effect of a higher level of abstraction is discussed in Chapter 3. We explain the need for timing analysis at this level and present the static timing analysis tool SuperSTA. The algorithms and design process for SuperSTA are discussed and results are presented. Recommendations are also made for future improvements to the tool.

In Chapter 4 we investigate the history of simulation engines for superconducting elements. Development decisions, results and features are discussed for each one and drawbacks are highlighted. Proposed improvements are mentioned and conclusions are made.

JoSIM development is discussed, design decisions are explained and supported with arguments in Chapter 5. Algorithms used for file input and output (IO) are walked through, comparing data structure methods for improved efficiency. Supported components within JoSIM are shown with their corresponding input file descriptions as well as the generalized matrix entries that collate to form the conductance matrix. Methods for solving very sparse matrices in the most efficient way are investigated and the findings implemented.

The results of various different designs, each with unique elements are displayed in Chapter 6. These results are critically analysed and compared to previous simulation engines in both speed and accuracy. We further analyse features not present in other simulators and scrutinize the accuracy of the results.

In Chapter 7, we investigate improvements to the designs implemented in JoSIM to handle massively parallel processing to reduce simulation times. Data structures used are reconsidered to reduce the complexity of the algorithms used. Optimizations to the mathematical engines used are investigated. We experiment with the idea of very large scale circuits with up to one million JJs to evaluate the efficacy of analogue simulators on microprocessor scale design.

Conclusions and recommendations as well as ideas for future research are mentioned in the final chapter.

Appendix A contains a published article "Superconducting digital circuit design with an open source and freeware tool Chain" [22] wherein we investigate the entire design flow for superconducting circuit design using only non-commercially available tools.

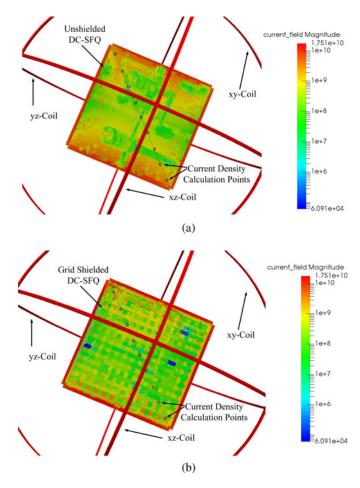

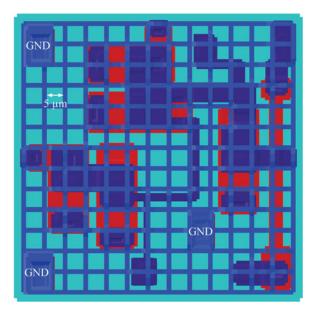

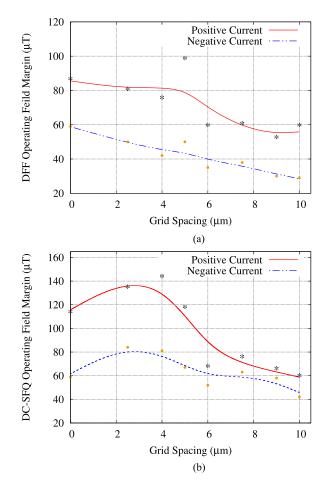

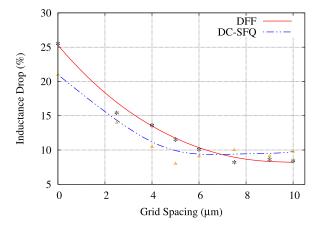

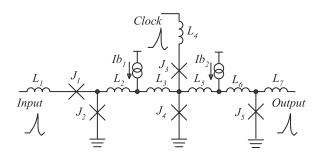

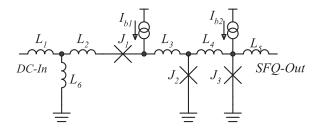

Appendix B contains a published article "Analysis of a Shielding Approach for Magnetic Field Tolerant SFQ Circuits" [23]. In this article we utilize superconducting simulation engines to investigate the effect of external magnetic fields on SFQ circuits and explore ways for improvement to make designs more tolerant to magnetic fields.

Appendix C contains a published article "A Static Timing Analysis Tool for RSFQ and ERSFQ Superconducting Digital Circuit Applications" [24], wherein we announce SuperSTA and discuss its features and capabilities as well as shortcomings.

Appendix D contains an published article "JoSIM – Superconductor SPICE Simulator" [25], wherein JoSIM is presented and evaluated against other simulation engines.

Appendix E contains the user manual for JoSIM, which guides the user through the process required to run the simulation engine while discussing the features and input file requirements.

## Chapter 2

# Electronic Design Automation in Superconductivity

## 2.1 Introduction

This chapter will discuss the process that a designer would follow when designing a superconducting circuit. This process is called a design flow and is not necessarily the exact process that always needs to be followed, but rather the one suggested by the developers of the software used in the process[22].

We discuss each step of the process as well as provide general examples of what the input/output would look like. The software used is also mentioned where possible and possibilities for future research in software that does not exist yet are mentioned. A more comprehensive roadmap of the available state of EDA in SC design can be seen in [26] and [27].

In the CMOS domain, these design flows are well-established and large EDA companies such as Cadence and Synopsis have been founded to enhance these design flows as far as possible. Efforts in the superconductivity domain have been made through large government projects[28] in the attempt to kick start EDA companies specifically for this domain.

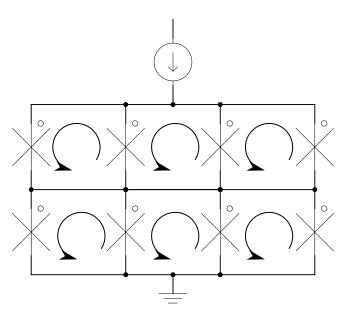

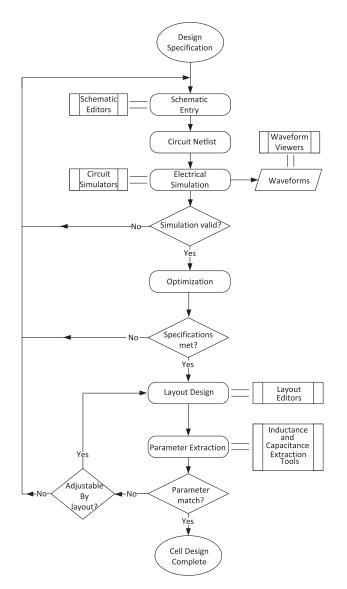

We depict a suggested standard design flow for superconducting circuit design in Figure 2.1.

## 2.2 Design Process

#### 2.2.1 High Level

A standard process to design a electronic circuit would start at a very high level of abstraction. This means that nothing is known about the physical properties of the circuit, only its function. This functionality would then be described in an HDL language of choice. An example of some behavioural description in Verilog HDL can be

```

module add(a, b, out, carry_in, carry_out)

input a, b, carry_in;

output out, carry_out;

assign carry_out = (a & b) | (a & carry_in) | (b & carry_in);

assign c = a ^ b ^ carry_in;

endmodule

```

where  $\hat{}$ , | and & are the logic operators XOR, OR and AND respectively. The example describes a single bit full adder operation in Verilog.

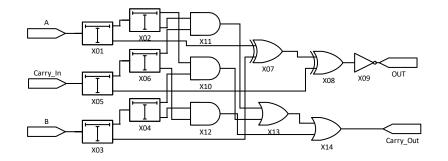

Figure 2.1: Suggested standard design flow for superconducting circuit design

Once the circuit behaviour has been described, it would be placed in an HDL testbench which will allow it to be simulated at a high level. Simulations can be done with commercial level tools or open source simulators such as Icarus Verilog[29]. Once simulated, the operation can be verified. This verification includes visual verification through interpretation of the results as well as static timing analysis to ensure there are no timing violations[24].

If the designer is satisfied with the device operation, the design can be synthesized down to an analogue netlist that can be simulated using a analogue simulation engine.

#### 2.2.2 Synthesis

Synthesis is described as a process of combining a series of components or elements to form a single entity. In EDA, synthesis is used to describe the process of transition from a high level design to lower level. There are a few variants of synthesis and the definition of the term seems to change depending on who is asked.

In SC design the two main variants of synthesis involve either generating a SPICE circuit netlist or a fully placed and routed layout from a single HDL design. Both of these processes would require the designer to specify the type of technology the design is intended for as well as provide the synthesis engine with a library of analogue logic gates that will be used to formulate the output.

There are however no known synthesis tools that support superconducting digital circuits fully due to their inherent synchronous design. There have been multiple efforts to alter existing tools or to create new ones[30][31], however none have been truly successful and thus the designer would have to create the analogue netlist either by hand or by creating a schematic in some schematic editor.

Figure 2.2: Schematic of a one bit full adder in single fanout design.

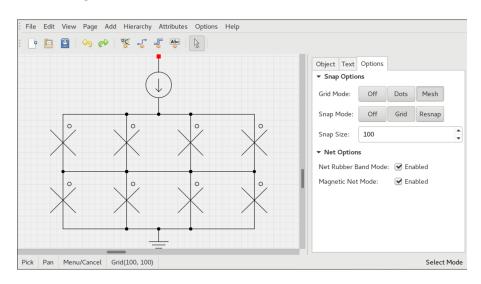

Schematic editors can be quite useful in providing visual feedback in terms of how everything is connected. Most schematic editors provide the user with the ability to convert the design into a analogue netlist which can then be used for simulation[32][33]. An example of a schematic editor can be seen in Figure 2.3.

Figure 2.3: gSchem schematic editor by gEDA

### 2.2.3 Analogue Simulation

A technology independent description of the example adder in Figure 2.2 through SPICE notation can be presented as

> .subckt ADDER 1 2 3 4 5 X01 SPLIT 1 6 7 X02 SPLIT 6 8 9 X03 SPLIT 2 10 11 X04 SPLIT 10 12 13

```

X05 SPLIT 4 14 15

X06 SPLIT 14 16 17

X07 XOR 7 11 22

X08 XOR 15 22 23

X09 NOT 23 3

X10 AND 8 12 18

X11 AND 9 16 19

X12 AND 13 17 20

X13 OR 18 19 21

X14 OR 21 20 5

. end ADDER

```

In SC design using SFQ pulse propagation, the maximum fanout that a single gate can have is one. To provide the same pulse to more than one gate a splitter cell is required, which essentially duplicates the SFQ pulse. This netlist coupled with the corresponding sub-circuits required can then once again be simulated by inserting it into a testbench with excitations at the relevant ports.

If the designer is satisfied with the results that the analogue simulation produces they can then proceed to creating a layout of the design. If however the designer is not satisfied, they then have the option to optimize the design or start from scratch. The design might produce the correct results but operation margins might make it less likely to succeed due to fabrication tolerances. Since the design operates as expected behaviourally the advised option would be to perform some form of optimization to attempt to increase operational margins and yield percentage.

#### 2.2.4 Optimization

The process of optimization includes doing a margin analysis, which varies every component within the netlist over a specified range. Multiple simulations are done while varying these components to establish the operational margins of the design. This allows the designer to identify components that might cause the design to fail once fabricated if the fabrication tolerances are not tight enough.

Optimization of these identified components can be done by manually tweaking the values of the components to try and improve stability, however this can be quite a tedious and time consuming process if the design is quite large. Optimization can also be done by implementing various methods such as genetic algorithms[34], Monte Carlo analysis[35] and others.

There are entire research fields dedicated to establishing algorithms that provide the best form of optimization. It might be worthwhile to investigate these algorithms in an attempt to create a generalised optimization software that applies the best algorithm of optimization relevant to the design under scrutiny.

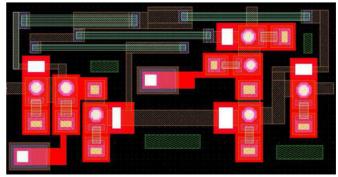

#### 2.2.5 Layout and Fabrication

Once the designer is satisfied with the results of the analogue simulation, they can then proceed with the creation of the layout. A layout is the physical description of the device that will be used for fabrication. This includes the type of materials used for each layer, the width of the material, the electrical properties and the physical location of each part of the design as it would appear on a chip.

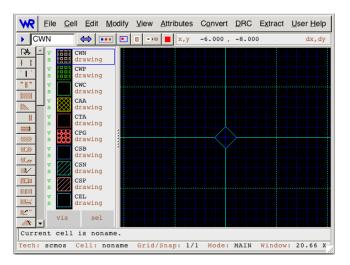

Since layouts rely strictly on the layer information, they can be done in almost any layout editor that accepts custom layers. Common layout editing software includes LayoutEditor, LASI, KLayout and Xic seen in Figure 2.4.

Figure 2.4: Xic layout editing tool

The process of laying out a design is not automated and requires that the designer have intricate knowledge on layout design. The process is very time consuming and tedious especially with large designs, though many layout editors have the ability to create sub-cells that aid the designer in the process. Software tools such as layout versus schematic (LVS) are under development to allow the user to verify the layout being created against the schematic or netlist source. LVS requires intense graph manipulating algorithms and is a very new field even in the CMOS domain.

The layout that is produced must adhere to the specific design rule checks (DRC) and electrical rule checks (ERC) of the specific technology the design was intended for. Once successful, tools such as Inductex[36] can be used to extract the impedances and repopulate the analogue netlist to ensure that the design still produces the expected results given the materials used and physical dimensions.

If the designer is completely satisfied with the results the layout level analogue simulation produces the layout can then be sent for fabrication at the very few superconducting digital circuit foundries that exist.

### 2.2.6 Technology Computer Aided Design

Technology computer aided design (TCAD) is a process whereby the fabrication process is simulated through equations that mimic the geometric extrusions[37]. This simulation method is completely seperated from the design flow and does not have an established software tool for SC design as of yet. The equations that mimic the geometry extrusions are extremely complex and require a large effort from both engineering and physics fields.

## 2.3 Conclusion

Though far from complete, the design flow for superconducting electronics is reaching a point where VLSI circuits can be designed and simulated. Operation can be verified through the verification techniques discussed. These verified designs can be fabricated and tested physically, which will possibly and most probably introduce other unforeseen parts of the design flow that have not been looked at prior to the fabrication of VLSI circuits.

Software tools that spawn from pojects like SuperTools[28] and similar will hopefully provide a good foundation to build forth from in the development of better methods for superconducting specific EDA tools. Once these tools reach a certain stability, companies may be founded from them or simply acquired by larger, well-established companies such as Cadence or Synopsis. Such is the life cycle of many innovative software technologies.

## Chapter 3

## High Level Verification

## 3.1 Introduction

High level verification is a process that attempts to establish valid design operation at a higher level of abstraction. As the number of gates in a design increase, the time required to perform an analogue simulation also increases and as a result so does the time to verify successful operation. This time grows exponentially and soon verification through analogue simulation of VLSI designs no longer become viable. To reduce the necessity of performing multiple simulations, static timing analysis attempts to gauge the maximum performance of a design by evaluating all possible paths from input to output and identifying the critical path given a set of gate-delay times.

This chapter will discuss the design and implementation of a high level verification tool SuperSTA[24]. SuperSTA is a command-line interface, static timing analysis tool for SC applications used to identify critical paths through a design, maximum frequency of operation and possible slack in the design. Two timing values are presented to the user, one being a global clock which is the maximum clock at which the design when viewed as a black box would produce an output at every clock edge. The second clock value presented is the system clock, which is the maximum clock at which the design can receive inputs at when performing wave-pipelining[38].

SuperSTA presents the user with a few additional device metrics when the user provides a target time within which the design is intended to finish. These metrics include the slack within the design as well as mean path time and path time variance.

This tool was developed under the IARPA seedling project[39] to work in conjunction with TimeEx[40] and RSFQ mapper[41]. The aim of this project was to establish the possibility of high level design tools for RSFQ and ERSFQ circuits, and is the precursor to Supertools[28].

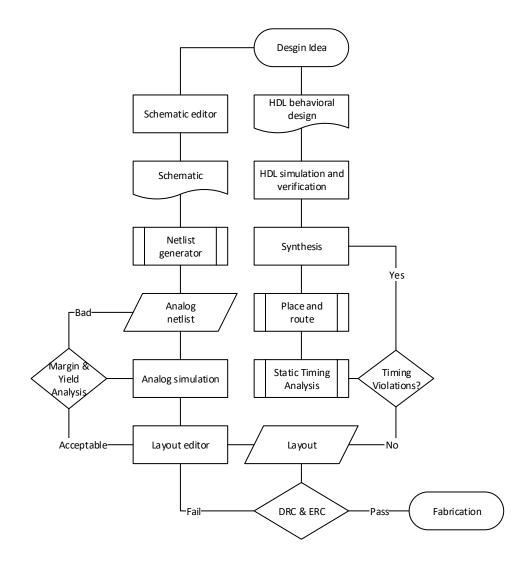

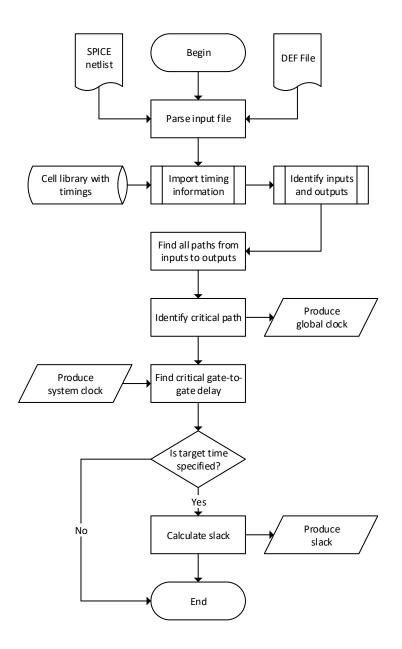

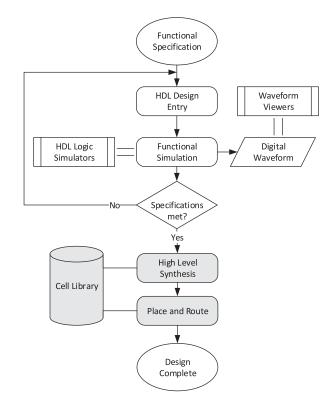

A macro view of the design flow implemented in SuperSTA is depicted in Figure 3.1.

## 3.2 SuperSTA

#### 3.2.1 Design Flow

The static timing analysis tool SuperSTA takes as input either a SPICE netlist which is produced as an intermediate step within the synthesis process discussed in Section 2.2.2 or a device exchange format (DEF)[42] file which is the end result of the place and route synthesis process. The SPICE netlist input is referred to as the pre-placed STA and is discussed in detail in Section 3.2.2 where the DEF input is called the post-placed STA and discussed in Section 3.2.3.

Figure 3.1: Basic design flow of SuperSTA

Either file type provided requires specification of the input and output nodes or locations, which, when not provided, will be determined algorithmically. SuperSTA parses each file sequentially to contruct a graph of how the design is interconnected. Once all interconnects are established, gates that are not connected at both input and output are flagged as possible IO in the case where the IO is not specified. This method of IO detection is not always accurate as there is no way of determining if the identified point is an input or output. It is therefore much more advantageous for the user to specify these points.

This constructed graph is then traversed from every possible input to every possible output using a variation of the breadth-first search (BFS) method[43]. This method traverses the graph by choosing a single point of input and output finding the most direct path between them. Due to the single fanout nature of SFQ design the use of splitters is required, which in this case causes branching to occur whenever a splitter is found whilst traversing. A note is simply made of the location of every splitter found along the path and once the path reaches an output it returns to each splitter to find a new path to an output. There are alternate methods of graph traversing such as depth-first search (DFS) [43], which explores all paths to their output first before traversing any branches. This method would essentially produce the same result, however BFS was ultimately chosen instead.

This method of finding all possible paths is however only possible if the design being analysed contains no feedback. If feedback is present, the search algorithm will loop infinitely. There are methods for circumventing this problem such as checking for repetition in the path being analysed.

Once all possible paths from intput to output have been found these paths are analysed using a provided cell library containing gate-delay times to find the path that has the longest delay. This path is called the critical path. The cell library of gate-delays is merely a folder that contains HDL descriptions of each gate with accurate timing delays as characterized using the timing extraction tool TimeEx[40]. If this cell library is not provided, generic times will be used and results will not be accurate.

This critical path can be used to identify the maximum clock frequency at which the design would produce a result in every clock cycle. This clock frequency is called the global clock and is useful in the case where the design will be used as a subcircuit in a larger design and requires a single clock input. In addition to this, each path is inspected to find the largest inter-gate delay to identify the system clock, which is the maximum clock frequency at which the design can throughput data without error. This clock is useful in cases were the design would be used through wave-pipelining[38] of the inputs.

SuperSTA is also capable of determining whether the design meets certain requirements such as operating frequency. This can be accomplished by allowing the user to specify a time within which a result is expected at the output when given an input. This timing parameter is called the target time and is used to calculate slack in the design. Slack in design philosophy is a performance metric, where positive slack indicates a good design and negative slack a design that needs reconsideration. The user is also presented with other meaningful design statistics such as the mean path time and path time variance which should also be taken into consideration when negative slack is present.

#### 3.2.2 Pre-Placed

During the process of synthesis whereby a high level design is transformed into a low level description, a SPICE-like netlist can be generated as an intermediate step. This netlist only contains information regarding the interconnection between gates as well as the types of gates used. It cannot be directly simulated and would require some form of testbench with relevant subcircuit definitions. This netlist also does not contain any wiring information, which would affect the delay within the design.

The purpose of allowing SuperSTA to evaluate this intermediate netlist is to allow the user to gauge relatively early in the design process whether the design would meet target time requirements or not. If the design does not meet the requirement in the netlist stage, then it will by no means improve through the addition of interconnect delays. Similarly, if the design just barely meets the set requirement, then it would generally not after adding interconnect delays.

The results produced for this method should not be used to accurately characterize the maximum operation speed of the design and should merely be used as an indication.

#### 3.2.3 Post-Placed

The final result of the synthesis process would generally contain information regarding the precise coordinates of placement and lengths of the interconnect wires. Additionally, due to

the use of PTLs in SFQ circuit design (discussed in Section 5.3.6), the requirement to include the delay caused by the interconnection between different layers called vias also need to be considered.

This file is called the post-placed design and is presented in a DEF file format. This file is parsed to determine the interconnection between gates as well as the delays caused by these interconnections. To calculate the interconnect delays some information is required about the material the design will be fabricated with. These values are the data transmission speed and the via delay. The user has the option to specify these values as part of the command used to execute SuperSTA. If not specified, the default values will be used.

## 3.3 Results

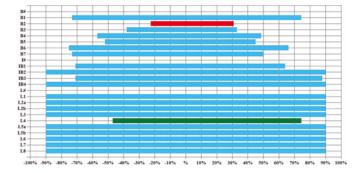

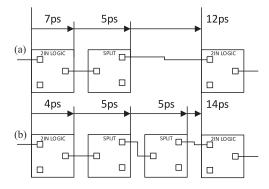

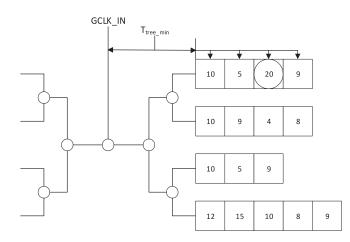

The results of static timing analysis performed on a 4-bit Kogge-Stone adder (KSA)[44] is presented. The file analysed is of the DEF type (post-placed) and the cell library of gate-delays is presented in Table 3.1.

| Gate     | Out delay         |

|----------|-------------------|

| AND      | 9.3ps             |

| DFF      | $5.5 \mathrm{ps}$ |

| JTL      | 3.2ps             |

| NDRO     | 7.0ps             |

| NOT      | 9.2ps             |

| OR       | 7.2ps             |

| PTL      | 18.5ps            |

| SPLITTER | 5.0ps             |

| XOR      | $5.7 \mathrm{ps}$ |

Table 3.1: Gate-delay timings for a RSFQ cell library

Due to the extreme file length of the 4-bit KSA def we ultimately decided not to include it in this dissertation. SuperSTA was executed using the following command

SuperSTA -t 300E-12 -ppv 0.02 -lpp 110 -d 4bitksa\_route.def

where ppv and lpp are the via delay and data transmission delay per micron. This command produces the following result

SuperSTA v2.1.1(Jan 3 2018). Copyright 2016 Johannes Delport.

This program comes with ABSOLUTELY NO WARRANTY. This is free software, and you are welcome to redistribute it under certain conditions; see the GNU GPL v3 for details.

File specified to analyse: "4bitksa\_route.def"

Total possible paths in design: 61 Critical path time: 2.92225e-10s or rather 292.225ps Global clock: 3.42202GHz

Critical path: b1\_Pad

```

Split_99_n222

xor2a_17_n17

Split_76_n199

Split_77_n200

and2_26_n26

Split_84_n207

and_{2}27_{n}27

or2_28_n28

xor2a_29_n29

DFF_67_sum2

sum2_Pad

Slack: 7.77455e-12s

Total slack: 3e-10s

Mean path time: 2.58092e-10s or rather 258.092ps

Path time variance: 4.77655e-22s^2 or rather 4.77655e-10ps^2

Path time standard deviation: 2.18553e-11s or rather 21.8553ps

Longest NET: and 2_34_n34 \rightarrow and 2_35_n35 \implies 570 micron

Largest inter-gate delay time: 50.7 ps

System clock: 19.7239GHz

```

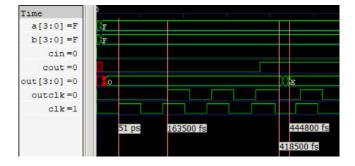

From this results we can see that the maximum clock that can be achieved internal to the design (system clock) is 19.7239GHz and note that the critical path is of depth 6 clocked gates. This means that when clocked at this frequency we expect the result to appear at the output after 6 clock cycles. When this clock is applied to the HDL test bench where the 4-bit KSA is the device under test (DUT) we observe this exact behaviour.

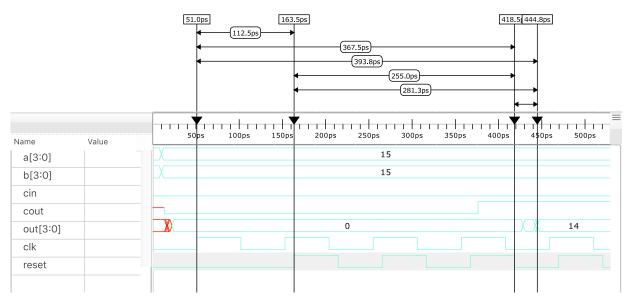

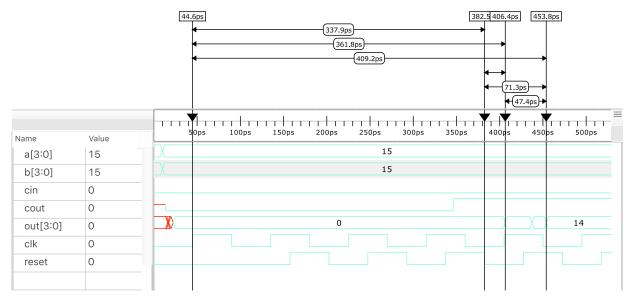

Figure 3.2: 4-bit KSA simulated as DUT at HDL level

The clock period in Figure 3.2 is determined through  $t = \frac{1}{f}$ , which in this case is 50.7ps. We adjust this to 51ps since the testbench does not accept fraction values for the clock. The time difference between the *clk* (clock input) and the *outclk* vectors is due to the delay created by the clocking circuitry. To simplify the implementation and legibility with SFQ HDL simulations we assume that every edge event is considered an SFQ pulse rather than attempting to mimic the width of the pulse. Noting this and observing the results we see that output is produced in the 6th clock cycle of the *outclk* vector.

If we alter the clock to 45ps, simply 6ps faster than the maximum speed calculated by Super-STA we observe the result appearing in the wrong clock cycle violating the timing restrictions of the design. This can be seen in Figure 3.3

Figure 3.3: 4-bit KSA simulated with a clock speed higher than maximum identified

Additionally we note that the specified target time was met and that the slack presented is positive. This design therefore meets the set requirement of the designer and can therefore be moved further down the design process.

## 3.4 Conclusion

In this chapter a static timing analysis tool SuperSTA was developed and tested. An example was run through SuperSTA and the results scrutinized. Back-annotation into an HDL description of the example confirms the results of SuperSTA as correct. Results were also shown for the example when maximum clock speed is exceeded and the consequences thereof discussed.

The use of SuperSTA can greatly speed up the design process due to the ability to backannotate results into a HDL simulation of the design. Future improvements to SuperSTA will include the analysis of a broader spectrum of design methodologies such as AQFP. We intend to continue development through inclusion of more elements that cause delay within design such as temperature, bias current effects and different clocking methods. Attempts to introduce parallel processing during the BFS stage of SuperSTA will also be investigated.

The unique contributions made through the implementation of a static timing analysis tool for superconducting circuit applications include a first of its kind tool as well as the definition of new types of delay factors involved in superconducting circuits. These contributions are further enforced through publication in an international journal[24] and is attached to this dissertation in appendix C.

## Chapter 4

## Analogue Simulation

## 4.1 Introduction

When the design moves to a lower level of abstraction, the need to perform analogue simulations arise. This requires the designer to have intrinsic knowledge of the electrical properties of the design. An analogue simulation could also be described as an electrical simulation and is used to compute electrical circuits. This is trivial for smaller circuits however as the component count increases, it quickly becomes necessary to use computer aided simulation software such as SPICE[15].

SPICE simulation in superconductivity is a rather niche field due to the complexity of the JJ element and non-linearities created by it. Most simulators rely on approximations such as the resistively and capacitive shunted junction (RCSJ) to model the tunnel current effect of the Josephson junction[4]. Regardless of being approximations, the modeled effect is suitable for simulation purpose and near enough to practical results to be acceptable in most cases. The closest approximation to the Josephson junction that models the Josephson effect most accurately was done by Werthamer in 1966[45][46]. This approximation though has not seen implementation in a general simulation engine.

The first documented case of an attempt at the Josephson effect in SPICE was by Jewett at University of California Berkeley in 1982[47]. The JJ model was added to the existing SPICE 2G5 and allowed the user to choose one of 3 types of quasiparticle resistances (Rtype). This method was however rather slow due to the numerical method used by SPICE for accurate simulation of transistor type devices. The SPICE 2G5 with the implementation of the JJ was named JSPICE.

In 1991, S. Whiteley was consulted to incorporate the JJ into the then new SPICE3 simulator which offered enhanced simulation performance and the implementation of a graphical postprocessor for result plotting[48]. Similar to the implementation of the JJ in the original SPICE, this version was named JSPICE3. JSPICE3 also included an implementation of margin analysis using pass/fail tests. JSPICE3 is the base upon which WRspice is built.

The rest of this chapter is dedicated to discussing the Josephson junction as well the capabilities and drawbacks of the available superconducting circuit simulators. This will highlight a few key areas on which improvement can be made.

## 4.2 Josephson junction

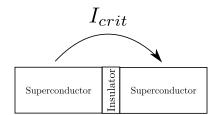

A Josephson junction is created by bringing two superconducting elements very close to each other, only separating them with a thin insulating barrier (figure 4.1). At absolute zero temperature the superconductor has no resistance and therefore a zero voltage drop. This allows DC current to persist within a superconductor forever. When the current through the JJ is

Figure 4.1: Basic example of a Josephson junction

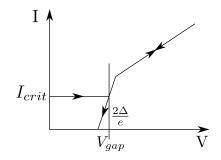

Figure 4.2: IV curve of a typical JJ

increased to some critical value, the voltage becomes non-zero and the electrons are said to tunnel across the insulator. This non-zero voltage is called the gap voltage and is presented using the equation

$$V_{gap} = \frac{2\Delta}{e} \tag{4.1}$$

where  $2\Delta$  is the binding energy of two electrons and e is the electron charge. When the current is further increased the junction approaches a linear resistance value. This resistance value is called the normal resistance and is associated with normal electron tunnelling. When the current is reduced, the curve follows the same path until it reaches the gap voltage after which it drops sharply to zero current [49]. The same occurs for negative currents the junction which creates a hysteresis curve. This phenomenon is called switching and is depicted in Figure 4.2.

## 4.3 **JSIM**

Josephson simulator (JSIM)[50], developed by Fang and Van Duzer in 1989, is a SPICE simulator dedicated to simulation of JJs and does not support any semiconductor devices. The simulator is very light weight due to the need to only support a few components. JSIM makes use of nodal analysis to compute solutions of large matrices.

JSIM, although being the most widely used superconducting circuit simulator, has received no update since the last release in 1992. It was well optimized at the time and remains so even on modern more powerful computing devices. However, many optimizations can be done to improve input methods and time to solution. The code was written with older memory architectures in mind using native C language where dynamic array sizes were hard to implement. This led to using pointers to form very long linked lists. These design choices make the alteration of the code and debugging to identify bottlenecks in large designs almost impossible.

JSIM, like JSPICE, is only capable of doing transient time domain simulations and cannot handle dc or ac simulations. What made JSIM unique to JSPICE is the implementation of the JJ requiring only the right hand side to be changed on every time step where JSPICE would change the **A** matrix after each iteration. This gives JSIM a large speed improvement compared to JSPICE.

JSIM has only 2 implemented types of quasiparticle resistance models. Rtype=0 meant

that the quasiparticle resistance was ignored and Rtype=1 approximated the resistance as a piecewise linear function. When Rtype=1 is specified the resistance used in the conductance matrix (A) for the Josephson junction would vary depending whether the junction voltage is below, in transition state or above the gap voltage.

The computing systems at the time of its creation were very limited in terms of memory and performance when compared to modern computers. This fact influences the size of simulations that JSIM can handle as it was written to be memory efficient. To further improve performance in JSIM, the time step size in the transient simulation is increased when the junction phase does not vary significantly within one time step. Similarly the time step is reduced when the phase difference becomes large and can also be reduced to less than the specified time step if the difference is greater than some threshold value.

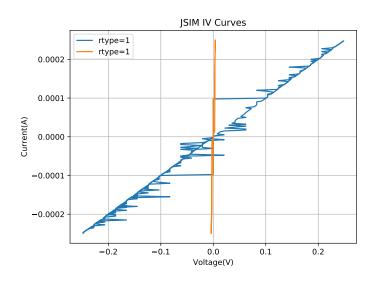

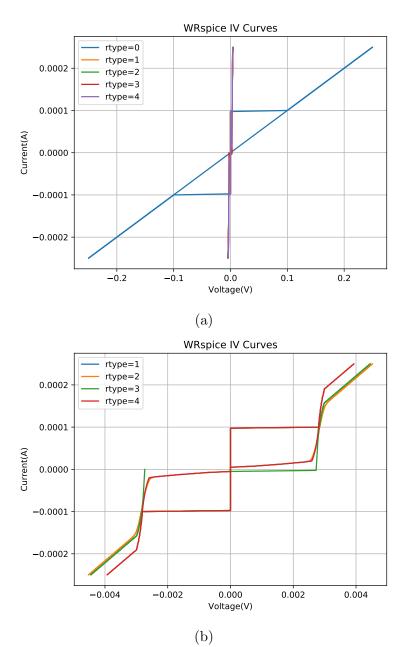

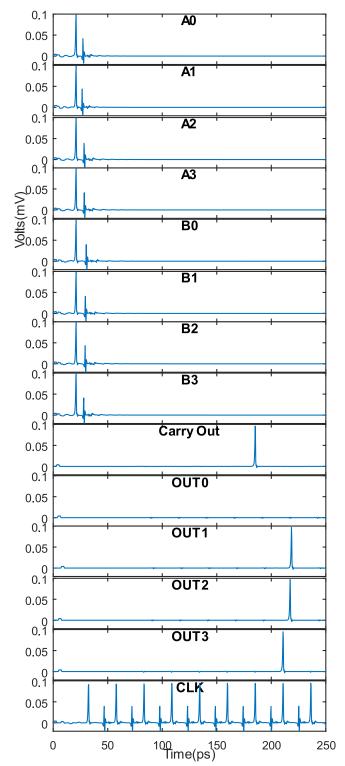

The possibility of using JSIM to simulate VLSI designs, however, becomes impractical due to it's failure in handling simulations that near 10 000 JJs. Regardless of this limitation JSIM is still regarded as one of the more popular simulators despite its age. We plot the current versus voltage (IV) curves for the JJ implementations in JSIM in Figure 4.3 and 4.4.

Figure 4.3: V curves of the RCSJ model in JSIM

Figure 4.4: IV curve of the RCSJ model in JSIM without Rtype=0

## 4.4 PSCAN

Personal superconductor circuit analyser (PSCAN) was written in 1991 by Polonsky at Moscow State University[51]. At the time only JSIM existed along with JSPICE2 and 3. All of which used the modified nodal voltage analysis approach to set up the linear equations. What PSCAN introduced was a solution that was labeled modified nodal phase analysis and made use of the relationship between the Josephson junction phase and voltage

$$v = \frac{\Phi_0}{2\pi} \frac{d\phi}{dt} \tag{4.2}$$

This method of simulation relies on satisfying London's quantization law for phase differences in a superconducting loop

$$\phi_1 + \dots + \phi_n = 0 \tag{4.3}$$

Unlike other SPICE simulators PSCAN utilizes a unique behavioural type of input language called SFQHDL[52]. This special input language made it possible for the designer to incorporate test vectors for self-verification within the input file. What this enabled was the incorporation of built-in margin optimization tools since the operation verification is done internally.

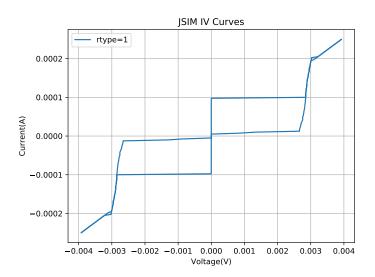

PSCAN was written in Fortran and was not available for testing publicly. PSCAN2 which was released in September 2016 by Pavel Shevchenko and builds on the development experience of the original PSCAN. PSCAN2 is written in Python and is available to the public at pscan2sim.org. Though the documentation indicate that it now accepts standard SPICE syntax, it however still requires a SFQHDL behaviour description file for which there seems to be no proper syntax guideline. We managed to get it up and running using the provided examples and used it to plot a simple JJ IV curve. This IV curve can seen in Figure 4.5.

Figure 4.5: Josephson junction IV curve created using phase based simulator PSCAN

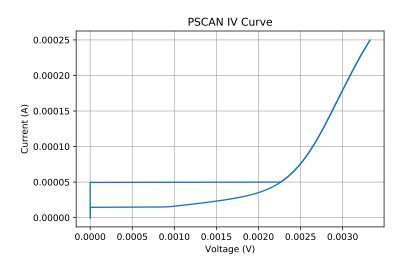

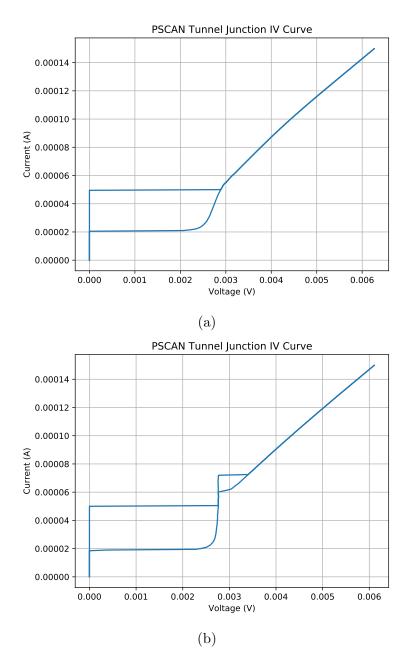

PSCAN2 includes an approximation to the microscopic tunnel junction as derived in [53] which uses a Dirichlet series approximations to model the tunnel junction behaviour. The Dirichlet series coefficients used by PSCAN2 can be set in one of the configuration files. We plot the two available tunnel junction model IV curves in Figure 4.6. One set of coefficients was provided by Prof Semenov and the other was borrowed from the tunnel junction coefficient generating tool MiTMoJCo[54].

Figure 4.6: Tunnel junction model IV curves created using PSCAN. Dirichlet coefficients used: (a) V. K. Semenov (b) MiTMoJCo

PSCAN2, unlike JSIM, includes a graphical interface window through which simulation options can be altered and results plotted. This GUI, like the rest of PSCAN2, requires the user to have in-depth knowledge of the PSCAN2 code since there is no user manual. Due to the lack of a proper syntax guideline and detrimental speed of Python, PSCAN2 is by no means a viable option to perform VLSI simulations.

## 4.5 WRspice

WRspice is a SPICE engine developed by Whiteley Research Incorporated in Sunnyvale, CA. Until October of 2017 it was a commercial SPICE engine and part of a toolset called XicTools, which included the layout package Xic. Development started as a project to rewrite JSPICE3 in C++ while maintaining full compatibility for older SPICE simulators.

WRspice unlike PSCAN and JSIM supports transistor components and was developed to

be fully graphical for ease of user interaction but still allows for command-line input. It is fully cross platform supporting Microsoft Windows, Linux and Apple MacOS.

WRspice is the most modern SPICE simulator available at present with capabilities such as network distribution, parallel processing and Monte Carlo analysis. It is well documented with an online help and manual system.

Similar to the JSPICE and JSIM the quasiparticle resistance type can be specified, however there are 5 different types unlike the 3 found in JSPICE and 2 in JSIM. WRspice supports transient analysis of any device as well as support for AC and DC (phase mode) simulations.

The integration with the layout editor Xic allows schematic editing and translation to the equivalent SPICE netlist for direct simulation. The ability for WRspice to view the simulation results directly through the graphical interface makes it the closest simulator in terms of features to what our project set out to achieve.

We compare the various implementations of JJ resistance types found in WRspice in Figure 4.7.

Figure 4.7: IV curves of the RCSJ model in WRspice. (a) With Rtype=0 (b) Without Rtype=0

# 4.6 Conclusion

In this chapter the Josephson junction as an element in analogue simulators was briefly examined. We discussed the various available circuit simulators, the features that make them unique as well as their downsides. The JJ element within each simulator was tested to form an IV curve for each type of resistance model.

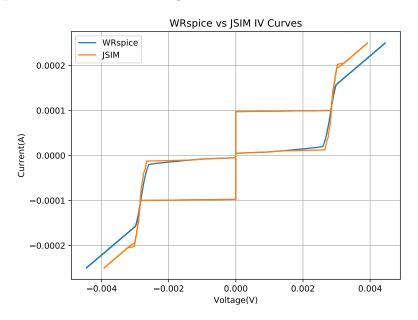

To compare these simulators to each other the testing environment needs to be set up to perform the same simulation on all of the simulators. This becomes a tedious task due to the differences in syntax between them. It was not however possible to compare PSCAN2 to JSIM or WRspice due to the lack of a proper user guide and difficulty understanding the syntax. We were however able to compare JSIM to WRspice using the exact same circuit and resistance model. This comparison can be seen in Figure 4.8.

Figure 4.8: Rtype=1 model comparison between WRspice and JSIM

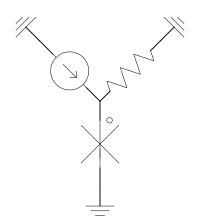

In Figure 4.8 we see that JSIM starts to let current through at a lower voltage and exits the sub-gap at a lower current level when compared to WRspice. This difference is largely due to the implementation each simulator uses to approximate the Josephson effect. This difference is further discussed in 5.3.4.2. This is achieved using the test circuit seen in Figure 4.9 and the following model for the JJ

.model jj1 jj(rtype=1, vg=2.8mV, cap=0.07pF, r0=160, rn=16, icrit=0.1mA)

Figure 4.9: Circuit used to find the IV curve of a JJ

The IV curve is drawn by ramping up the current source to  $2.5\mu$ A steadily until 50ps and then keeping it constant for the rest of the simulation. The simulation is run for 1ns and a step size of 0.1ps is used. The voltage across the JJ is then averaged for the last 500ps of the simulation and stored.

The current is increased by another  $2.5\mu$ A and the simulation is repeated. This is done until the current reaches  $250\mu$ A, which is much more than the  $100\mu$ A critical current of the JJ. The current is then ramped down back to zero incrementally and the same process is followed for the negative current.

This requires a total of 400 simulations to find an average voltage for each current value which when plotted presents the IV curve seen in Figure 4.8.

The same process is done for both WRspice and JSIM and the execution speeds of the 400 simulations are compared. In the test script we use to calculate the IV curve, the only variable is the simulator and the timing can therefore be directly compared. While using WRspice the script completed in 55.97s, where when using JSIM, it completed in 60.49s.

There are some slight differences between the piece-wise linear resistance models implemented in each simulator which could attribute to the difference in execution speed. WRspice does have the advantage of being written in C++ and using updated linear algebra methods such as KLU, but JSIM does not come in too far behind it despite its age.

This leads us to believe that a simulator written in C++ with updated linear algebra libraries that is exclusively designed for superconducting circuit simulation could be advantageous in the long run.

# Chapter 5

# **JoSIM - Development**

## 5.1 Introduction

In this chapter we will discuss the development decisions and design intricacies involved in the creation of the superconducting simulation engine JoSIM[25]. Due to JSIM and WRsice being the most common superconducting simulation engines at the start of this development process, the decision was made to utilize the same SPICE syntax used in both. This should allow simulation of existing netlists and direct comparison of results and simulation times.

JoSIM was initially developed as part of this project to help motivate the argument of this disseration. It was intended to be used to simulate VLSI designs in reasonable time by making use of advanced linear algebra libraries and modern day computing systems with parallel processing. Through the course of development, the need for JoSIM was further enhanced through the US Government sponsored IARPA project Super Tools [28], wherein the purpose of JoSIM was altered to provide simulation results of more accurate approximations of the JJ behaviour through incorporation of more intricate models. Additional requirements were set for JoSIM to be able to elegantly plot the results of a simulation to some graphical form that should be publication ready such as scalable vector graphic (SVG) format.

JoSIM is developed in standard C++ to provide compatibility across multiple platforms and is open source at JoSIM.git with the MIT license. Code is also commented as far as possible to help legibility and aid future developers of the code. Documentation in the form of a user manual is also made available and can be found in Appendix E.

Code was initially written using a MSI GE72 6QF running Microsoft Windows 10 and Microsoft Visual Studio Enterprise with a student license. Development was later shifted to a Apple Macbook Pro 13" (2017) running mac OS High Sierra and Visual Studio Code. This change was made to eliminate the need for a nearby power outlet whenever inspiration struck.

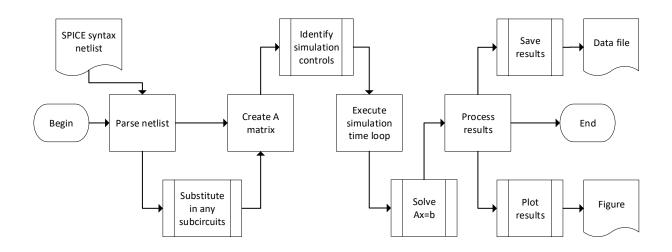

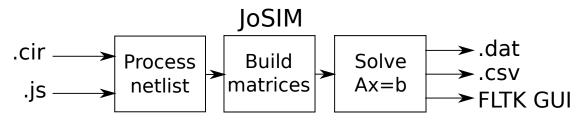

This chapter is further divided into the different sections of JoSIM as a simulation process and is depicted in the design flow shown in Figure 5.1.

Figure 5.1: Overview of the JoSIM design flow

# 5.2 Design Flow from Input to Output

#### 5.2.1 Input

As mentioned, input to JoSIM is aimed to provide as much compatibility with standard SPICE syntax and closely follows the syntax found in The SPICE Book[55]. The user would provide a netlist containing multiple lines of component definitions and interconnect information. Component definitions are further elaborated on in 5.3. These netlist files would also contain control lines that define what JoSIM has to do with the components it has read in. The types of control lines available in JoSIM are discussed in 5.4.

When a netlist is parsed, each line is read in and stored either as main design, controls or subcircuit under the corresponding subcircuit section. Once the entire file has been parsed we iterate through both the main design substituting the relevant subcircuit lines when a subcircuit definition is found. This process is recursive to included nested subcircuits. In JoSIM we allow alphanumeric node names as opposed to the standard numeric found in JSIM. This allows us to append the corresponding subcircuit label to the node names and labels of the lines being substituted. This process is illustrated in Figure 5.2 and 5.3.

. subckt RLC 1 4 R01 1 2 5 L01 2 3 10 C01 3 4 20 . ends RLC V01 0 1 PWL(0 5 10 20) R01 1 2 5 L01 2 3 10 X01 RLC 3 4 C01 4 0 20 . end

Figure 5.2: Example of a standard netlist with a subcircuit

```

V01 0 1 PWL(0 5 10 20)

R01 1 2 5

L01 2 3 10

X01 RLC 3 4

R01 | X01 3 2 | X01 5

L01 | X01 2 | X01 3 | X01 10

C01 | X01 3 | X01 4 20

C01 4 0 20

. end

```

Figure 5.3: Resulting master netlist after substitution

Once this master netlist has been generated we now iterate through each individual line, deciding what needs to be done with it base on first character of each line. These components are then transformed into their relevant MNA stamp.

#### 5.2.2 Matrix Setup

When attempting to solve a set of linear equations to find the voltage at every node as in the modified nodal analysis (MNA), we need to first decide on an integration method that would approximate the current or voltage of non-linear components. The most basic of these methods is simply the backward Euler method, which interpolates the value based on the previous value.

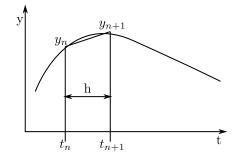

Figure 5.4: Approximating the  $y_{n+1}$  value

From Figure 5.4 we can write backward Euler differential as

$$\frac{dy}{dt_n} = \frac{y_{n+1} - y_n}{h} \tag{5.1}$$

This method is however a first order method which does not model the behaviour accurately enough and is prone to error. We therefore opt to use a second order method such as the trapezoidal integration method. The trapezoidal integration method can be defined as

$$\frac{dy}{dt_n} = \frac{2}{h} \left( y_n - y_{n-1} \right) - \frac{dy}{dt_{n-1}}$$

(5.2)