# An Autonomous, Omnidirectional, Digital, Borehole Imaging System

# UNIVERSITEIT STELLENBOSCH UNIVERSITY

Timothy G. Sindle

Study Leaders: Prof J.H. Cloete and Prof K.D. Palmer

Thesis submitted in partial fulfilment of the requirements for the degree of Masters of Engineering in the department Electrical and Electronic Engineering at the University of Stellenbosch.

| ,  |   |    |    |   |   |

|----|---|----|----|---|---|

| ec | O | ro | t1 | ^ | n |

|    |   | 14 |    | u |   |

| I, the undersigned, hereby declare that the work contained in this thesis is my own original work, except where indicated. It has not been submitted before, in its entirety or in part, for any degree or examination at any other University. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                 |

| Timothy Grant Sindle                                                                                                                                                                                                                            |

#### **Abstract**

This thesis documents the research, design, implementation and successful testing of a prototype camera probe to survey the inside of hard rock boreholes. Rock core images are intended to aid mine geologists in recording the borehole rock layers. The system consists of a wide-angle fisheye lens mounted onto a CMOS digital image sensor. The image data is read in and processed by an FPGA, then stored on a removable SD flash memory card. All of the aforementioned components are mounted inside a watertight Perspex tube. Application specific PC software is used to process the data to form strip images of the borehole wall. Using mathematical correlation, these images are stitched together into a virtual core that is a flattened representation of the rock inside the borehole. The probe contains its own power and light source which enables it to be deployed easily with no external wires needed for operation. The storage capacity, image quality, and lighting design can be improved in future design revisions.

## **Opsomming**

Die inhoud van hierdie tesis behels die navorsing, ontwerp, implementering, en suksesvolle toetsing van 'n prototipe kameraprobe wat dit moontlik maak om die binnewand van boorgate in harde rots te besigtig. Beelde van die rotskern vergemaklik die taak van myngeoloë wat die rotslae, waardeur die boorgat strek, moet opteken. Die stelsel behels 'n wyehoek bollens wat op 'n CMOS digitale sensor gemonteer is. Die data gewerf vir die vorming van die beeld word deur 'n FPGA ingelees en verwerk, waarna dit op 'n verwyderbare SD flits geheuekaart gestoor word. Die bogenoemde komponente word alles binne 'n waterdigte Perspexbuis monteer. Gebruikerspesifieke sagteware vir persoonlik rekenaars word gebruik om die data te verwerk en sodoende strookbeelde van die binnewand van die boorgat te vorm. Met gebruik van wiskundige korrelasie word hierdie beelde aan mekaar gelas om 'n virtuele kern te vorm, wat 'n voorstelling is van die rots binne die boorgat. Die probe bevat self krag en ligbronne, wat toelaat dat dit maklik bruikbaar is sonder enige eksterne bedrading. Toekomstige hersienings van die ontwerp sal verbeterde data geheue, beeldgehalte en beligting kan bewerkstellig.

#### Acknowledgements

Gratitude and thanks must be expressed to numerous people who went out of their way to make this project a success:

- To my parents Ian and Ann for their love and support over my 23 years.

- Professor J.H. Cloete for his guidance, enthusiasm and intuitive insight.

- Professor K.D. Palmer for his innovative ideas and willingness to help solve any problem.

- Professor I.M. Mason for his wealth of optical knowledge and interest in this project.

- Dr Shih-Schon Lin for his useful advice on conic mirrors and omnidirectional systems, via email correspondence.

- The Molshoop residents, Brian, Lötter, Marcel, Paul, Stefan, and Wernich for their pleasant company and inspirational ideas.

- Special thanks to Colin Sindle and Lötter Kock for helping with the proof reading of this thesis.

- Anita van der Spuy and Wessel van Brakel for the translation of the abstract.

- Wessel Croukamp, Ulrich Buttner, and Lincoln Saunders all from SED, for their help with the design and manufacturing of the mechanical parts of this project.

- Dr. J. Hargreaves for the use of his FPGA test board.

- METGLO in Brakenfell for kindly coating the conical mirror for free.

- Mr Josef Ekkerd, at DeBeers Finsch diamond mine.

- Geomole for funding during this project.

- The financial assistance of the National Research Foundation (NRF) towards this research is hereby acknowledged. Opinions expressed and conclusions arrived at, are those of the author and are not necessarily to be attributed to the National Research Foundation.

# **Abbreviations**

| ADC    | Analogue to digital converter           |  |  |

|--------|-----------------------------------------|--|--|

| BRAM   | Block random accesses memory            |  |  |

| CID    | Card identification register            |  |  |

| CLB    | Configurable logic block                |  |  |

| CMOS   | Complementary metal oxide semiconductor |  |  |

| CRC    | Cyclical redundancy check               |  |  |

| DLL    | Delay-locked loop (FPGA)                |  |  |

| DLL    | Dynamic link library (USB PC Code)      |  |  |

| DOS    | Disk operating system                   |  |  |

| DSP    | Digital signal processor                |  |  |

| FAT32  | 32-bit File allocation table            |  |  |

| FIFO   | First in first out                      |  |  |

| FPGA   | Field programmable gate array           |  |  |

| FPS    | Frames per second                       |  |  |

| $I^2C$ | Inter-integrated circuit                |  |  |

| IO     | Input output                            |  |  |

| IOB    | Input output block                      |  |  |

| JTAG   | Joint test action group                 |  |  |

| LC     | Logic cell                              |  |  |

| LUT    | Look up table                           |  |  |

| mcd    | Millicandela                            |  |  |

| MMC    | Multimedia card                         |  |  |

| PC     | Personal computer                       |  |  |

| PCB    | Printed circuit board                   |  |  |

| PGA    | Programmable gain array                 |  |  |

| PROM   | Programmable read only memory           |  |  |

| RAM    | Random access memory                    |  |  |

| RGB    | Red, green, blue                        |  |  |

| SD     | Secure digital                          |  |  |

| USB    | Universal serial bus                    |  |  |

# **Table of Contents**

| Declaration  |                                    | II   |

|--------------|------------------------------------|------|

| Abstract     |                                    | Ш    |

| Opsomming    | <b>{</b>                           | IV   |

| Acknowledg   | gements                            | V    |

| Abbreviatio  | ns                                 | VI   |

| Table of Co  | ntents                             | .VII |

| Table of Fig | ures                               | IX   |

| Table of Eq  | uations                            | XI   |

| Table of Tal | bles                               | XI   |

| An Early O   | mnidirectional Imaging System      | .XII |

| Chapter 1    | Introduction                       | 1    |

| 1.1 Ba       | ckground Study                     | 1    |

| 1.2 Ini      | tial System Specification          | 4    |

|              | sign Overview                      |      |

|              | esis Overview                      |      |

| Chapter 2    | System Level Design                |      |

| 2.1 Ex       | isting Systems and Related Patents | 6    |

| 2.1.1        | Existing Systems                   | 6    |

| 2.1.2        | Related Patents                    | 8    |

| 2.2 Sys      | stem Innovations                   | 9    |

|              | mplete System Description          |      |

| 2.3.1        | Omnidirectional Optics System      | 11   |

| 2.3.2        | Camera and Lighting                |      |

| 2.3.3        | FPGA Data Processing               |      |

| 2.3.4        | Flash Memory Storage               |      |

| Chapter 3    | Hardware Design                    |      |

|              | rdware Overview                    |      |

|              | age Sensor                         |      |

| 3.2.1        | Image Sensor Requirements          |      |

| 3.2.2        | Image Sensor Technology            |      |

| 3.2.3        | CMOS Image Sensor                  |      |

|              | ocessing Power                     |      |

| 3.3.1        | Processing Requirements            |      |

| 3.3.2        | FPGA Technology                    |      |

| 3.3.3        | Xilinx Virtex FPGA                 |      |

|              | sh Memory                          |      |

| 3.4.1        | Memory Storage Requirements        |      |

| 3.4.2        | Flash Technology                   |      |

| 3.4.3        | Secure Digital Card                |      |

|              | B Communication                    |      |

| 3.6 LE       | D Lighting Circuitry               | 29   |

| Chapter 4      | Optical Design                                       | 30 |

|----------------|------------------------------------------------------|----|

| 4.1 On         | tics Overview                                        | 30 |

| 4.1.1          | Spherical, Hyperboloidal, and Parabolodial Mirrors   |    |

| 4.1.2          | Conical Mirror                                       |    |

| 4.2 Co         | nical Mirror Optical Setup                           |    |

|                | heye Lens                                            |    |

|                | Firmware Design                                      |    |

|                |                                                      |    |

|                | mware Overview                                       |    |

|                | mera Controller                                      |    |

| 5.2.1          | Initialize Process                                   |    |

| 5.2.2          | Read Data Process                                    |    |

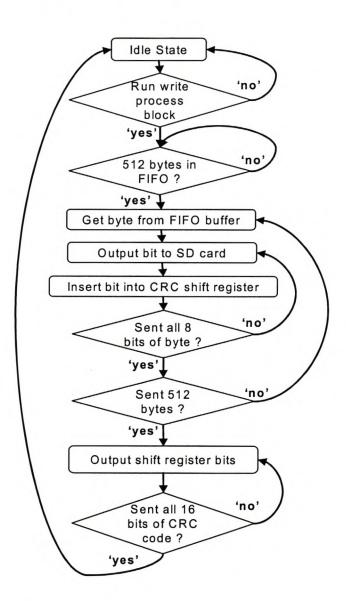

|                | Flash Controller                                     |    |

| 5.3.1          | Write Block Process                                  |    |

|                | O Memory Block                                       |    |

|                | ner and Clock Generation                             |    |

| Chapter 6      | Image Processing                                     | 58 |

| 6.1 Ba         | yer's Array to RGB, Methods and Implementation       | 58 |

|                | lar to Cartesian Conversion                          |    |

| 6.3 Co         | rrelation Based Merge and Distance Calculation       | 63 |

| Chapter 7      | Testing and Results                                  |    |

| 7.1 Pro        | ototype Packaging                                    | 65 |

|                | thting Modifications                                 |    |

|                | IOS Sensor Gain Variation Test                       |    |

|                | st Borehole Results                                  |    |

| 7.4.1          | Conical Mirror                                       |    |

| 7.4.2          | Fisheye Lens                                         |    |

|                | solution Test Chart                                  |    |

|                | ter Borehole Test                                    |    |

|                | ck Borehole Results                                  |    |

|                | ver Usage                                            |    |

|                | stem Cost                                            |    |

| Chapter 8      | Recommendations and Conclusions                      |    |

|                |                                                      |    |

|                | commendations                                        |    |

| 8.1.1<br>8.1.2 | Hardware                                             |    |

| 8.1.2          | Optics                                               |    |

| 8.1.4          | Firmware                                             |    |

| 8.1.5          | Image Processing Software                            |    |

|                | Packaging                                            |    |

| 8.2.1          | ure Developments                                     |    |

| 8.2.2          |                                                      |    |

| 8.2.3          | Wireless Downloading Linking with Orientation Sensor |    |

|                | tem Specificationtem                                 |    |

|                | nclusion                                             |    |

|                | References                                           | 92 |

# **Table of Figures**

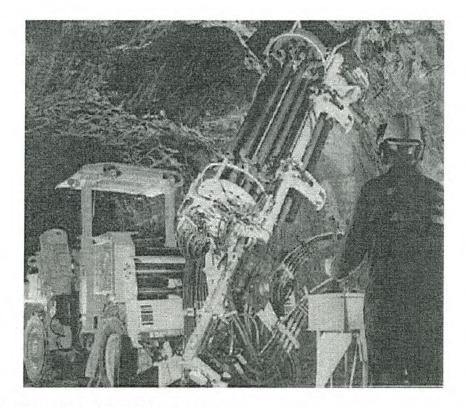

| Figure 1-1 Borehole drill rig and operator [1].                                    | 1  |

|------------------------------------------------------------------------------------|----|

| Figure 1-2 A core yard at Finsch diamond mine                                      |    |

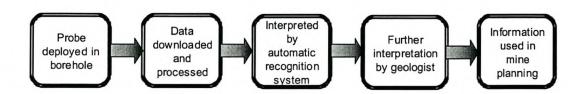

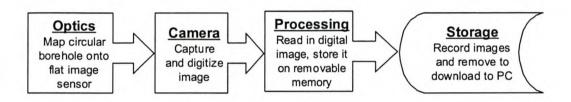

| Figure 1-3 Intended process for using this project.                                |    |

| Figure 1-4 Broad system design.                                                    | 5  |

| Figure 2-1 Raax BIPS (left) and ALT setup (right).                                 | 7  |

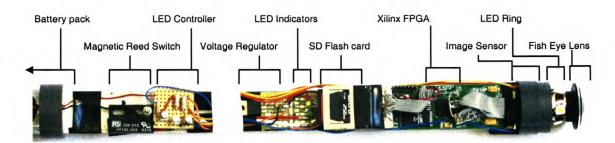

| Figure 2-2 Annotated picture of RockEye probe.                                     | 10 |

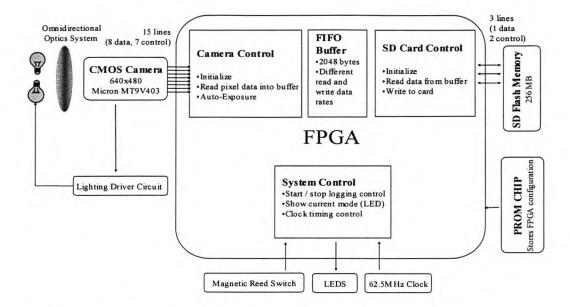

| Figure 2-3 Schematic elements of RockEye system.                                   | 11 |

| Figure 3-1 CMOS sensor showing desired annular region in grey                      |    |

| Figure 3-2 Illustration of the workings of a rolling shutter                       |    |

| Figure 3-3 A picture of a moving bus taken with a rolling shutter CMOS sensor [7]. | 15 |

| Figure 3-4 Camera board with Micron MT9V403 sensor front, back unpopulated         |    |

| Figure 3-5 Micron MT9V403 frequency response [8]                                   |    |

| Figure 3-6 Test board, FPGA and PROM highlighted.                                  |    |

| Figure 3-7 Virtex architecture [9].                                                |    |

| Figure 3-8 Two slice vertex CLB [9].                                               |    |

| Figure 3-9 SanDisk Ultra II SD flash card.                                         |    |

| Figure 3-10 Secure Digital flash card inner workings [10]                          |    |

| Figure 3-11 USB module including FTDI245BM microchip [11]                          |    |

| Figure 3-12 First picture from the camera, downloaded through USB port             |    |

| Figure 3-13 LED driver circuit.                                                    |    |

| Figure 4-1 General optics setup.                                                   |    |

| Figure 4-2 Mirror field of view, image from [14]                                   |    |

| Figure 4-3 Cone mirror setup as suggested by Lin and Bajcsy [15]                   |    |

| Figure 4-4 Gaussian simple lens setup.                                             |    |

| Figure 4-5 Test mirrors (14, 10, 5 mm) and clear mounting tube                     |    |

| Figure 4-6 Conical mirror test setup.                                              |    |

| Figure 4-7 Concentric or radial lines in focus.                                    |    |

| Figure 4-8 Images in the concentric and radial focal planes, modified from [12]    |    |

| Figure 4-9 Fisheye lens.                                                           |    |

| Figure 4-10 Fisheye lens internal optics [19]                                      |    |

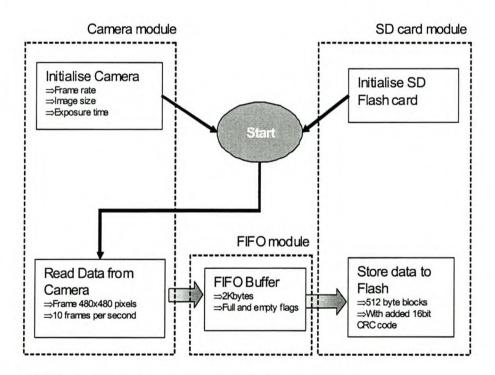

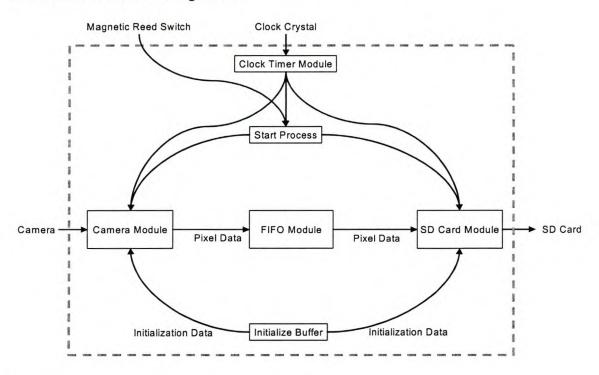

| Figure 5-1 FPGA internal process overview showing internal modules                 |    |

| Figure 5-2 Firmware dataflow.                                                      |    |

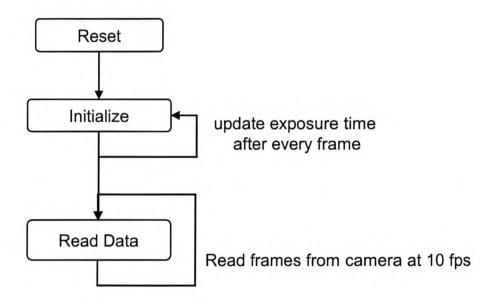

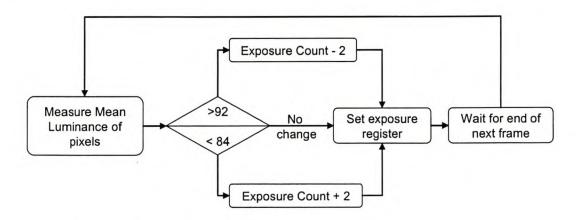

| Figure 5-3 Camera module processes.                                                |    |

| Figure 5-4 Exposure setting control loop                                           |    |

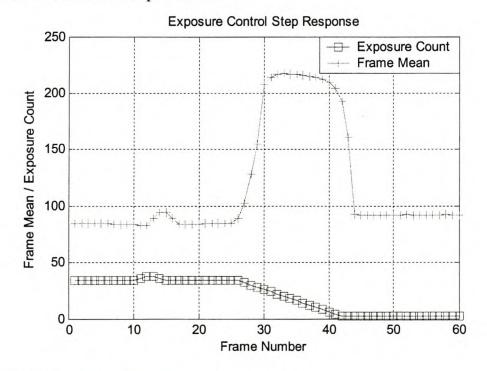

| Figure 5-5 Step response for exposure control.                                     |    |

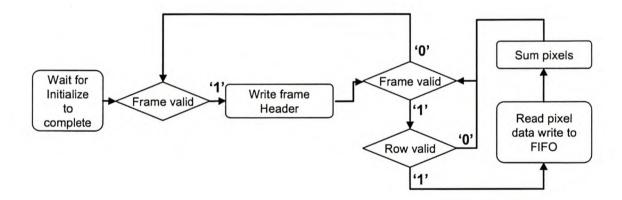

| Figure 5-6 Read data process flow                                                  |    |

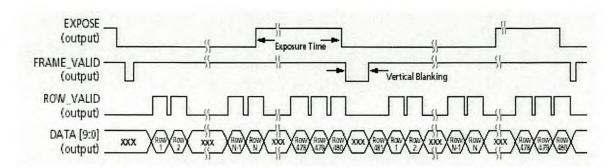

| Figure 5-7 Frame and row synchronisation waveforms [8]                             |    |

| Figure 5-8 SD card module, initialize process.                                     |    |

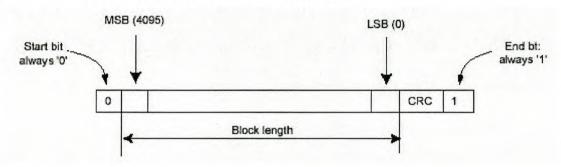

| Figure 5-9 Block data packet format [10]                                           |    |

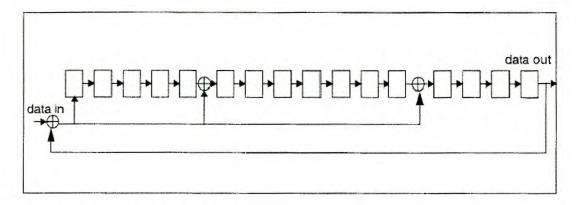

| Figure 5-10 CRC 16-bit shift register [10]                                         |    |

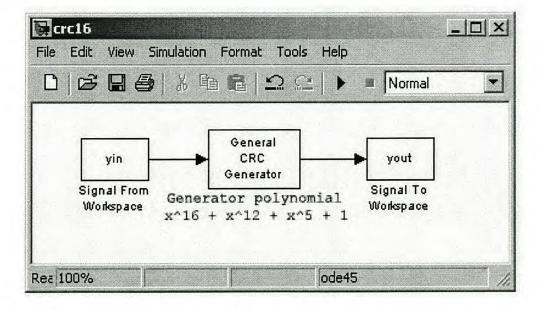

| Figure 5-11 Simulink CRC generator simulation.                                     |    |

| Figure 5-12 Write block process.                                                   |    |

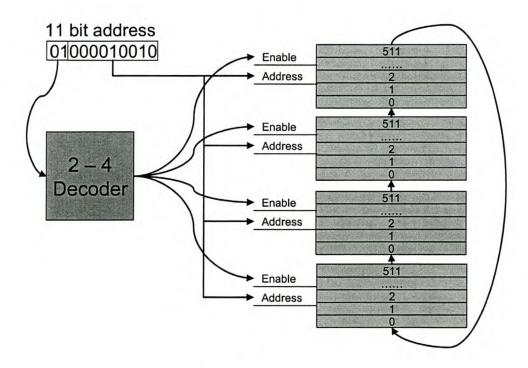

| Figure 5-13 FIFO memory buffer address decoding                                    | 55 |

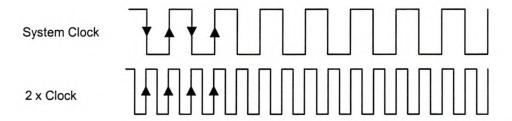

| Figure 5-14 System clock and double rate clock.                                    |    |

| Figure 5-15 Clock generation                                                       | 57 |

| Figure 6-1 Pixel colour filters, image modified from [21]                          | 58 |

| Figure 6-2 Bayer's pattern.                                                        |    |

| Figure 6-3 Interpolation implementation example                                    | 59 |

#### Stellenbosch University http://scholar.sun.ac.za

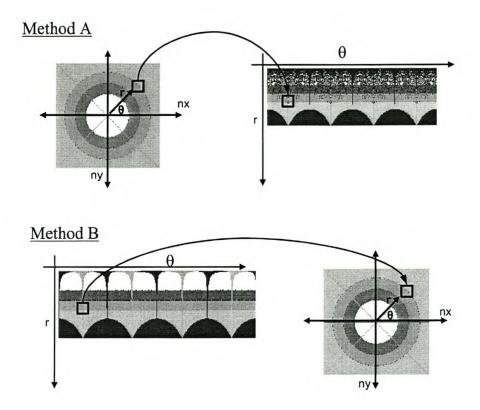

| Figure 6-4 Two methods of unwrapping the annular ring.                     | 61 |

|----------------------------------------------------------------------------|----|

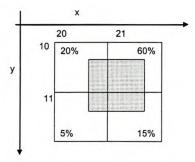

| Figure 6-5 Sub-pixel anti-aliasing.                                        | 62 |

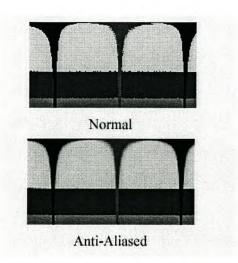

| Figure 6-6 Effect of anti-aliasing on unwrapped test image.                | 62 |

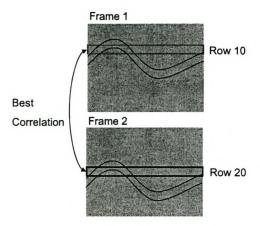

| Figure 6-7 Example of the correlation process.                             | 64 |

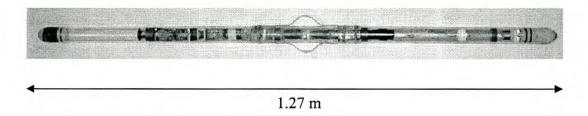

| Figure 7-1 Packaged probe                                                  |    |

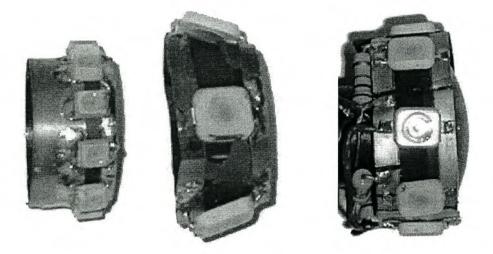

| Figure 7-2 Lighting evolutions (current setup shown on the right).         | 66 |

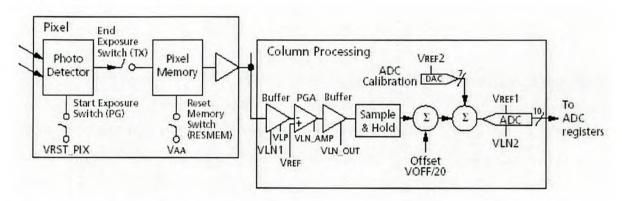

| Figure 7-3 Image sensor analogue signal path [8].                          | 67 |

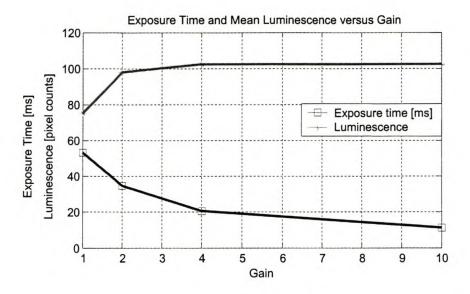

| Figure 7-4 Graph showing variation of exposure time versus gain            | 68 |

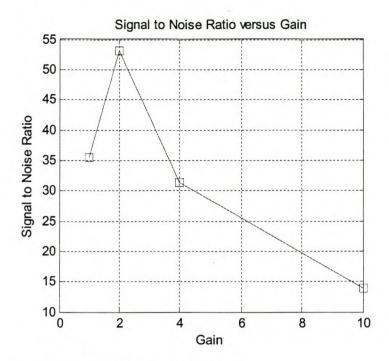

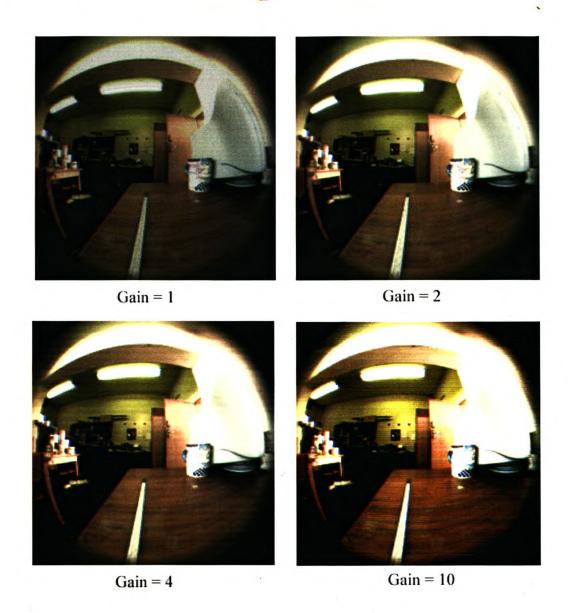

| Figure 7-5 Graph showing the change in SNR with gain.                      | 69 |

| Figure 7-6 Noise versus gain pictures.                                     | 70 |

| Figure 7-7 Conic mirror in test borehole using 8 mm lens.                  | 71 |

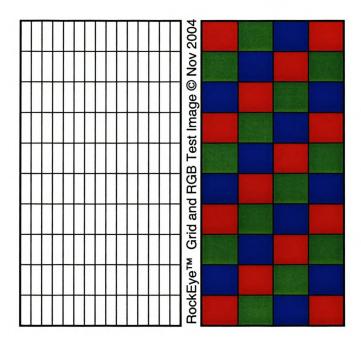

| Figure 7-8 Picture of the test borehole grid pattern using fisheye lens    | 72 |

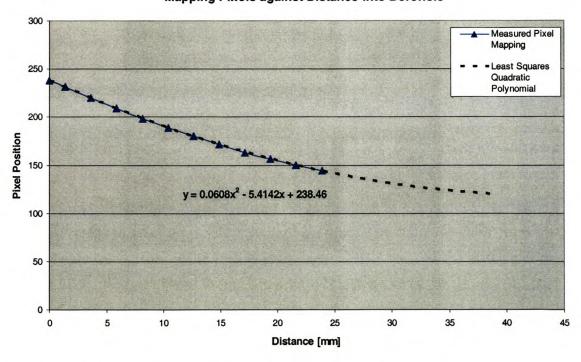

| Figure 7-9 Unwrapped test grid.                                            | 73 |

| Figure 7-10 Relationship between pixel position and borehole distance      | 73 |

| Figure 7-11 Geometrically correct unwrapped test grid.                     | 74 |

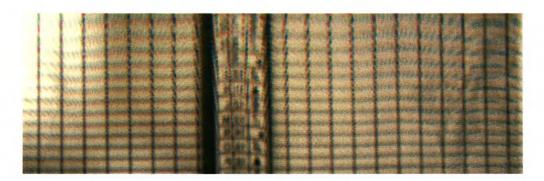

| Figure 7-12 Resolution test chart image.                                   | 74 |

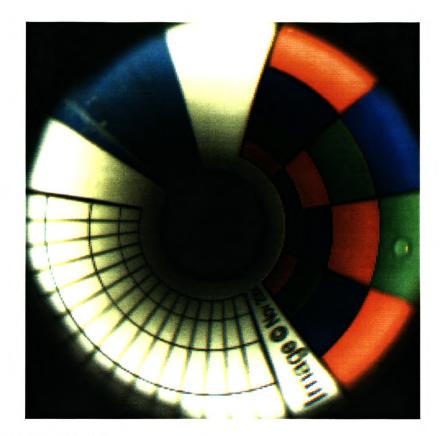

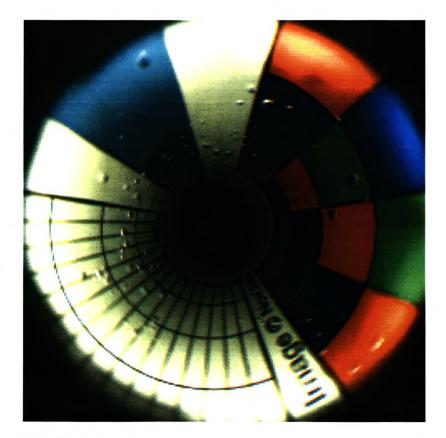

| Figure 7-13 Water borehole test image.                                     | 75 |

| Figure 7-14 Dry test borehole.                                             | 76 |

| Figure 7-15 Water filled test borehole.                                    | 76 |

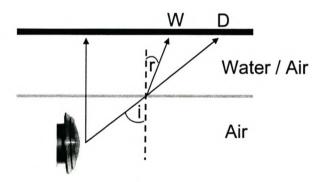

| Figure 7-16 Optics in air and water                                        | 77 |

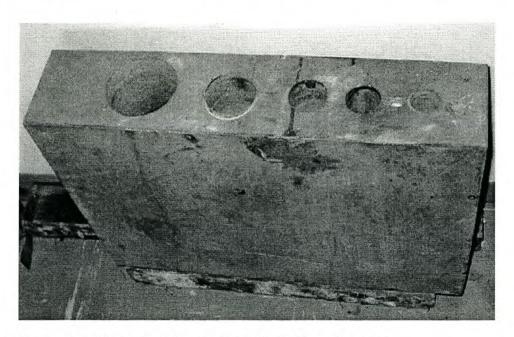

| Figure 7-17 Granite block with holes of 113, 76, 58, 50, 40 mm diameter    | 78 |

| Figure 7-18 Inside of tombstone picture.                                   | 79 |

| Figure 7-19 Unwrapped section of frame 1.                                  | 79 |

| Figure 7-20 Unwrapped section of frame 2.                                  | 79 |

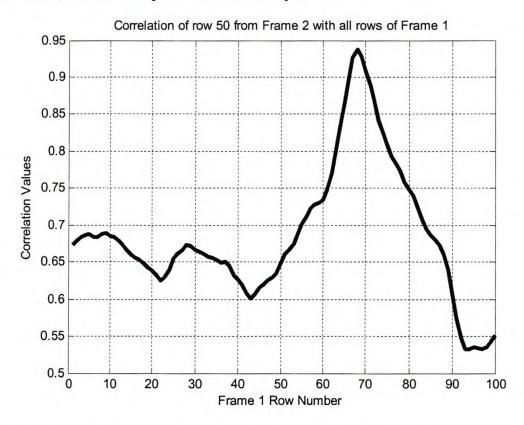

| Figure 7-21 Correlation of one row from frame 2 with all rows from frame 1 | 80 |

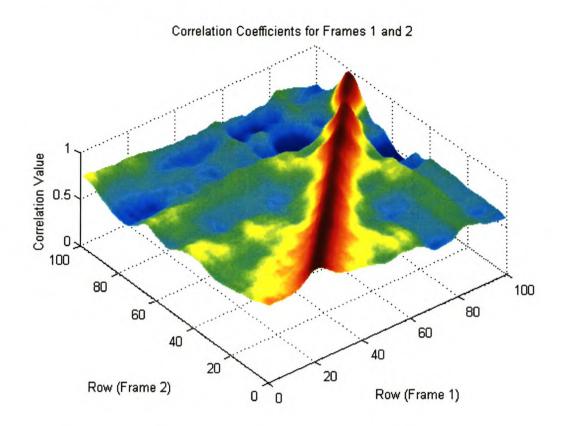

| Figure 7-22 Correlating every row in frame 1 with every row in frame 2     | 81 |

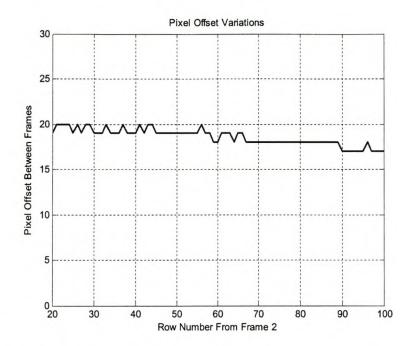

| Figure 7-23 Pixel offset between frames.                                   | 82 |

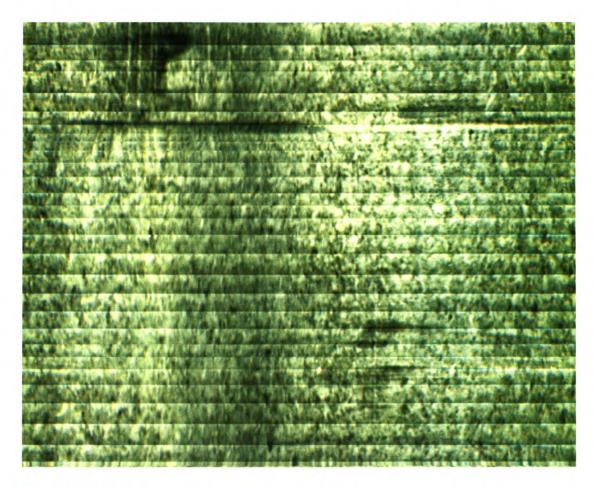

| Figure 7-24 Virtual core                                                   | 83 |

|                                                                            |    |

# **Table of Equations**

| Equation 4-1 Gaussian thin lens formula           | 35 |

|---------------------------------------------------|----|

| Equation 4-2 Focal distance formula [17]          | 40 |

| Equation 5-1 Row time formula                     |    |

| Equation 5-2 Frame time formula                   |    |

| Equation 5-3 16-bit CRC generator polynomial.     |    |

| Equation 6-1 Rectangular to polar transformation  |    |

| Equation 6-2 Polar to rectangular transformation. |    |

| Equation 6-3 Correlation formula used in MATLAB   |    |

| Equation 7-1 Signal to noise ratio formula.       |    |

| Equation 7-2 Snell's Law [23]                     |    |

# **Table of Tables**

| Table 2-1 Existing optical borehole imaging systems.     | 6  |

|----------------------------------------------------------|----|

| Table 3-1 Flash card comparisons                         |    |

| Table 3-2 Data rates of various communications protocols |    |

| Table 5-1 Camera register setup values.                  |    |

| Table 5-2 Clock frequencies for different modules.       | 57 |

| Table 7-1 Cost estimate for critical components          | 84 |

| Table 8-1 Final system specification                     |    |

# **An Early Omnidirectional Imaging System**

"Hand with reflecting Sphere", 1935 M.C. Escher

"The picture shows a spherical mirror, resting on a left hand. But as a print is the reverse of the original drawing on stone, it was my right hand that you see depicted. (Being left-handed, I needed my left hand to make the drawing.) Such a globe reflection collects almost one's whole surroundings in one disk-shaped image. The whole room, four walls, the floor, and the ceiling, everything, albeit distorted, is compressed into that one small circle. Your own head, or more exactly the point between your eyes, is the absolute center. No matter how you turn or twist yourself, you can't get out of that central point. You are immovably the focus, the unshakable core, of your world." - M. C. Escher

# **Chapter 1 Introduction**

This chapter begins with a background study that leads to the formulation of this project idea and includes the initial system specification.

# 1.1 Background Study

The mining industry is one of South Africa's most important economic activities contributing around 6.5% to the national gross domestic product. This 52 billion rand industry is kept running by numerous mines spread around the country, excavating South Africa's wealth of mineral resources. Before excavation can begin, boreholes are drilled to prospect the rock and determine the underlying strata that the mine will be entering into.

Figure 1-1 Borehole drill rig and operator [1].

Most exploration hard rock boreholes are drilled using diamond tipped drill bits that flush out a circular rock core. The often fractured core samples are collected and stacked in order for later examination by the mine geologist. However, these samples may be stacked incorrectly in the core trays, inaccurately logged against distance, or simply lost. If the cores reach the surface in good condition, the geologist may not have the time to visit the core yard and go through the laborious task of documenting it. In 2003 Anglo Platinum alone drilled 630 km of boreholes, at an average cost of R200 – R1000 per meter. This represents an approximate investment of R200 million – and this for only one of the many mining companies in SA.

The idea behind this project is to design an electronic borehole imager system that will record pictures of the entire borehole wall. The result should be an image of a virtual core, accurately logged against the distance into the borehole, which the geologist and mine planers can peruse back in their office. This will greatly increase the return on investment for the mines for every metre of borehole drilled.

Figure 1-2 A core yard at Finsch diamond mine.

There are existing borehole camera systems that are not widely used – mainly due to their high cost and complexity. They need skilled operators and a setup consisting of screens, computers, winches, optical fibres, and shaft encoders.

This project was designed to work in conjunction with a MSc. Eng. project currently being completed by Stefan van der Walt. His project aims to design an automatic rock classifier based on wavelet pattern recognition technology. It is intended for this design to produce the images that are then processed to form a virtual core. This image is then automatically interpreted as far as is possible before being passed on to the mine geologist who checks the results and uses the information for future mine planning. These steps are shown in Figure 1-3.

Figure 1-3 Intended process for using this project.

# 1.2 Initial System Specification

From the end-product described in the previous section, an initial system specification was drawn up. The aim of this project is to produce an imaging system, which is easy to deploy by unskilled miners, to capture visual pictures of the entire wall of the inside of hard rock boreholes. The specifications are:

- Capable of taking high resolution colour pictures.

- Should be able to discern features of width 0.5 mm in a 48 75 mm borehole.

- Give a full 360° side-on view of the borehole wall.

- Be able to focus on the 48 mm (and wider) diameter of the borehole wall.

- Camera frame rate should not put too many constraints on deployment speed.

- Store all images onboard on some form of memory.

- Autonomous operation (no attachment wires needed).

- Have enough battery capacity to complete a full survey<sup>1</sup>.

- Illuminate the borehole wall.

- Attempt to design for wireless (Bluetooth) download.

- Download data to a PC or handheld device at a reasonably fast rate.

- Work and fit into the physical constraints of a 48 mm diameter borehole.

- Compact design lengthwise.

- Work in air and water filled boreholes.

<sup>&</sup>lt;sup>1</sup> Borehole radar surveys typically consist of logging a 150-200 m borehole takes approximately 40min. Average deployment rate 0.1 m/sec.

## 1.3 Design Overview

Using the problem statement, the previous specifications, and many hours of research, a system was designed using the latest available technology. A prototype named the RockEye was built to test the concept. It includes optics, a camera, a processing unit, and a storage medium as shown in Figure 1-4. Post processing software was also developed to present the images in a visually useful format. The RockEye system aims to be the first borehole camera system to save all data onboard and allow complete autonomous operation. Hopefully this will revolutionise the use of borehole cameras in the mining industry.

Figure 1-4 Broad system design.

#### 1.4 Thesis Overview

The rest of this thesis details the research, design, implementation and testing of a digital borehole camera. Chapter 2 details the system as a whole - with the following chapters exploring each part of the system in detail. Hardware is discussed in Chapter 3, optics in Chapter 4, firmware in Chapter 5 and image processing in Chapter 6. Chapter 7 shows testing and results before recommendations and conclusions are made in Chapter 8. Chapters 2, 3 and 4 begin with a literature study of available technology to fulfil the specific system needs, then go on to justify the choices made and document the design.

# Chapter 2 System Level Design

This chapter initially looks at the existing commercially available borehole camera systems and related patents. The following Section 2.2, describes how this design differs from previous systems. Section 2.3 details the complete design and functioning of this unique device.

# 2.1 Existing Systems and Related Patents

## 2.1.1 Existing Systems

There are a number of available borehole imagers that form a good starting point for designing this system. Some of the main market players; the Japanese company Raax; Advanced Logic Technology (ALT) from Luxembourg and Robertson Geologging (RG) originally based in the UK. The main specifications, where available, for the probes from these companies are shown in Table 2-1.

|                               | RAAX BIPS <sup>3</sup>                                  | RG OPTV <sup>2</sup>  | ALT OBI 40 <sup>4</sup>          |

|-------------------------------|---------------------------------------------------------|-----------------------|----------------------------------|

| Diameter                      | 50 mm (42/32 option)                                    | 50 mm                 | 40 mm                            |

| Length                        | 1 m                                                     | 1.43 m                | 1.7 m                            |

| Weight                        |                                                         |                       | 7 kg                             |

| Maximum Depth                 | 500 m (50 bar)                                          | 1500 m (150 bar)      | 2000 m (200 bar)                 |

| Max Temperature               | 45°C                                                    |                       | 50°C                             |

| Logging Speed                 | 0.9 m/min                                               | 1 to 2.5 m/min        | Variable depending on resolution |

| Sensor Type                   | CCD camera                                              | CCD camera<br>768x494 | CCD camera                       |

| Sensor Azimuth<br>Resolution  | 360 or 720 pixels / 360°                                | 720 pixels / 360°     | 720 pixels / 360°                |

| Sensor Vertical<br>Resolution | 0.25 mm                                                 | 1 / 2 mm              | Up to 0.5 mm                     |

| Optics                        | Fisheye / rotating<br>Mirror / 45 degree<br>cone mirror | Hyperbolic mirror     | Polycarbonate conic prism        |

| Price                         |                                                         |                       | US \$ 25 000                     |

Table 2-1 Existing optical borehole imaging systems.

,

<sup>&</sup>lt;sup>2</sup> http://www.geologging.com

However, all of these systems are modified TV cameras housed in protective tubes attached to long cables. The cable normally supplies power and delivers the image signal to the surface where it is attached to a computer or television video recorder combination. In addition to the probe the entire system setup for these systems can comprise of: a length of fibre optic or coaxial cable including up to 7 wires; a shaft encoder to log the length of cable entered into the hole; and a specialised 486 PC including additional PC cards to complete the specific tasks and read in image data. Together, these elements form a complex and costly setup. The Raax and ALT setups are shown in Figure 2-1.

Figure 2-1 Raax BIPS<sup>3</sup> (left) and ALT<sup>4</sup> setup (right).

<sup>3</sup> http://www.raax.co.jp

<sup>4</sup> http://www.alt.lu

#### 2.1.2 Related Patents

There are a number of patents relating to the field of borehole imaging. Schlumberger seem to have filed the first one in 1986, which consists of a hemispherical mirror being imaged by photodiodes housed in a vacuum chamber to stop them being influenced by the heat in the boreholes [2]. However, since then, RAAX seem to be the most prolific patent filers. Initially in 1992 they patented a modified conic mirror and associated imaging probe [3]. The modified conic mirror had the tip cut off and replaced by a plane 45° mirror used for high resolution detailed borehole inspection. Since then they have patented various minor advancement on this theme. Additionally, in 1996 they patented a 3D borehole imaging system [4]. It is based on a conic mirror and two Fresnel prisms. The system generates two images, one for each eye, allowing the borehole to be viewed in 3D.

Jeffrey Beckstead of Interscience based in New York, patented another modification on the conic mirror in 1998 – this time with a transparent centre, so in addition to being able view sideways it can view forward images as well [5].

In 2002 Brad Meltzer from the US company DHV International patented a method of lighting for borehole cameras [6]. Their design has a light shining on an ellipsoidal mirror. At the focus point of the elliptical mirror a fibre optics bundle takes the light and shines it out radially. They claim the increased efficiency allows the probe to contain its own battery pack and thus reduce the size of the wires attached to the probe – allowing it to go into narrower boreholes.

This patent search showed that borehole camera advancements are actively being filed. Additionally it seems conical mirrors are regularly used for borehole inspection. There may be more patents published that were not found as performing a full patent search is an arduous and expensive task.

# 2.2 System Innovations

The RockEye aims to be the first completely autonomous borehole imaging system with all data stored on board, as well as having its own power and light source. After deployment and once out of the mine, the captured images can be downloaded using a standard PC. This design takes advantage of the very latest trends in semiconductor camera and memory technology – the camera chip used was released in November 2003 and the flash memory card has been on the market for less than a year. The hardware of the system was designed to be simple, with all the processing completed by one FPGA. There are no moving parts, which increases the reliability of the probe. While other systems log the distance into the borehole by measuring the number of rotations of the winch deploying it, this system aims to calculate distance using post processing correlation based software working on the calibrated images taken in the borehole.

These advances in technology enable this device, consisting of only a probe, to compete with existing entire systems. Hopefully, with the increase in simplicity of this system, coupled with its ease of use, the mines will adopt borehole cameras for every day service.

## 2.3 Complete System Description

The prototype probe shown in Figure 2-2 has been designed with a maximum width of 38 mm to fit inside a 40 mm Perspex tube. Rightmost in Figure 2-2 is a fisheye lens to capture a view of the entire circumference of the borehole in one camera shot. Next, the borehole wall is lit using a ring of eight ultra bright LEDs. Behind the LEDs is the camera sensor and associated support circuitry, mounted facing forward. The digital output from the camera is captured and processed by the FPGA before being written to the removable flash disk memory storage. There are three LEDs to show the current probe mode. A voltage regulator ensures a steady 5V is supplied to the electronics. The LED controller handles the high current drawn by the lighting diodes. A magnetic switch enables the probe's mode to be changed while the device is sealed in a watertight package. Finally, the battery pack supplies power to the entire device enabling it to run without any wires.

Figure 2-2 Annotated picture of RockEye probe.

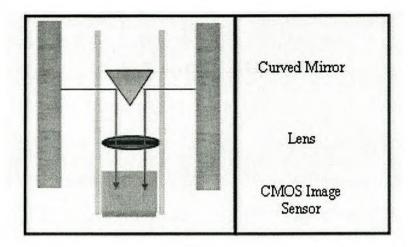

Figure 2-3 Schematic elements of RockEye system.

The various element of this design are shown schematically in Figure 2-3. They are discussed in more detail in the following subsections.

#### 2.3.1 Omnidirectional Optics System

Although the prototype contains a fisheye lens, lens-mirror combinations were also investigated, specifically the conical mirror. The fisheye lens has a field of view of 180° enabling it to see forward as well as to the side, effectively mapping the circumference of the borehole onto the flat plane of the image sensor. The optics of this project are discussed in detail in Chapter 4.

#### 2.3.2 Camera and Lighting

The full colour 640 by 480 pixel image sensor is capable of running at up to 200 frames per second (fps) but for this application it need only run at 10 fps. It has an internal digital shutter that eliminates the need for an external mechanical shutter. Inside the camera, the analogue values read from the light sensitive pixels are transformed into digital values by an internal 10-bit analogue to digital converter (ADC). The most significant 8 bits are read into the FPGA along with digital control lines indicating when the row and frames are valid. There is also a two wire serial interface to the camera to set internal registers such as the exposure time. The camera

and the control thereof is described in more detail in the hardware and firmware chapters.

The borehole wall is lit using eight Osram Golden Dragon LEDs. These LEDs are extremely bright over a wide viewing range. However, they use a lot of power and generate heat. To cut down on their power use, the lights are only turned on when the camera is taking a picture. There is a digital output from the camera that goes high whenever it is exposing a picture. This expose line is connected through a transistor driver circuit to the LEDs. These circuits are explained in Section 3.6.

#### 2.3.3 FPGA Data Processing

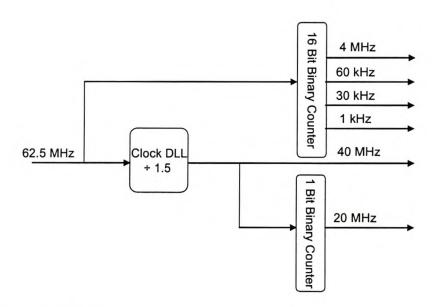

Upon power up, the FPGA configures itself from an external programmable read only memory chip (PROM). The FPGA then initializes the camera and memory card, setting internal registers and ensuring that they are both in the correct modes to start recording picture information when the magnetic switch is activated. The FPGA is clocked using a 62.5MHz external crystal oscillator – all the internal clock rates are generated from this frequency. Three external LEDs show the current mode of the probe and if there are any faults. They were also used extensively during development for debugging purposes. From the CMOS sensor, the image data is read into an internal buffer on the FPGA and then read out and stored on the flash memory card. The firmware is described in more detail in Chapter 5 and the FPGA itself within the hardware chapter in Section 3.3.2.

#### 2.3.4 Flash Memory Storage

A Secure Digital (SD) flash card is used to store the images. Flash memory is a nonvolatile memory storage type, so when the power is switched off, the data remains. This flash disk has a capacity of 256MB allowing storage of 1070 images. It is controlled by a command line, a clock line, and a data line. Once the images have been recorded on the card, it can be removed from its holder and downloaded on any PC with an SD card reader and some specialized software. The methods used to write to the card are outlined in Section 5.3 and the card itself is described in Section 3.4.

# **Chapter 3 Hardware Design**

This chapter examines each of the hardware elements in detail. Firstly, examining the available technology, and then justifying the choices made for this design.

#### 3.1 Hardware Overview

The hardware in this system is split into four functional groups: data capture, data processing, data storage and data download. Each of these functional groups is examined in the rest of this chapter under the sub-sections: image sensor, processing power, flash storage, and USB communications. Although USB communications have not been built into the current prototype, they were tested successfully during development and it is envisaged that a final system may include USB download capabilities.

## 3.2 Image Sensor

#### 3.2.1 Image Sensor Requirements

For this application the image sensor has the following requirements:

#### Resolution

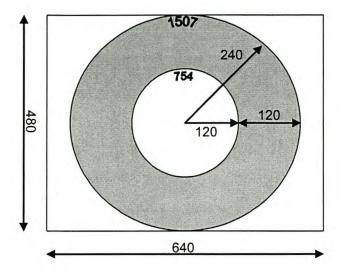

The image sensor's resolution is determined by the desired azimuth resolution on the borehole wall. The vertical resolution is set by the optics. One of the initial specifications was that the system should be able to discern features that are 0.5 mm in width in a 48 mm diameter (150.7 mm circumference) borehole. To meet this criterion, the image sensor should have an azimuth resolution of approximately 0.2 mm per pixel. A 640x480 pixel standard size will achieve this as it has a maximum ring circumference of roughly 1507 pixels (480  $\times \pi$ ), resulting in a resolution of 0.1mm per pixel for the outer ring. The minimum diameter in number of pixels to achieve a

0.2 mm resolution is 240, where the circumference is 754. Thus, we can have an annular ring that is up to 120 pixels wide.

Figure 3-1 CMOS sensor showing desired annular region in grey.

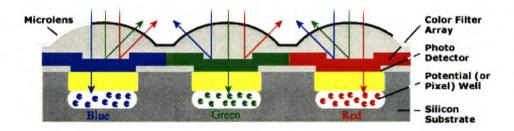

#### Colour

The final graphic representation of the core should look like it does if one was viewing it with one's own eyes. For this, we need a full colour picture with at least 8 bits per colour – forming a 24-bit red, green and blue (RGB) image.

#### Frame Rate

Suppose, the probe is deployed at 100 mm per second and each picture scans a region of approximately 24 mm (120 pixels times 0.2 mm per pixel). Thus the minimum frame rate is 5 fps. Eventually the individual frame images should be stitched together and some overlap must be allowed so the eventual frame rate will be higher than 5 fps.

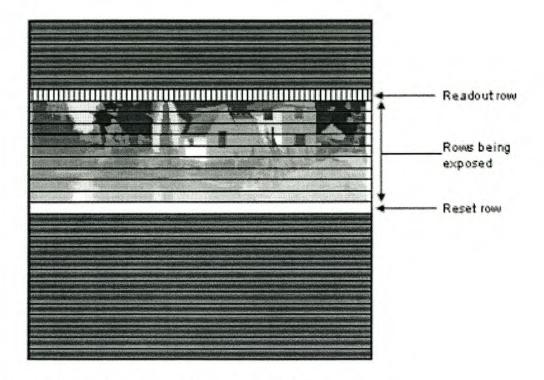

#### **Electronic Shutter**

Most image sensors employ a form of rolling shutter where a narrow band of the sensor is exposed sequentially. The width of the band is determined by the exposure settings. This process is shown in Figure 3-2. In this system, the probe is moving while taking pictures of the nearby borehole wall. A rolling shutter will result in a distorted image similar to the picture of a bus in Figure 3-3. Another option is to include a mechanical shutter, but this adds unwanted moving parts to the design and

size issues may be a problem. In this system an internal electronic full frame shutter is desired.

Figure 3-2 Illustration of the workings of a rolling shutter.

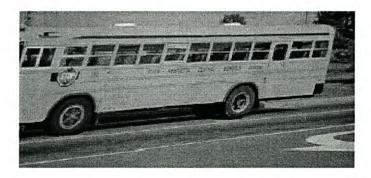

Figure 3-3 A picture of a moving bus taken with a rolling shutter CMOS sensor [7].

## **Light Sensitivity**

Again, as the probe is moving while taking pictures, the exposure time has to be kept to a minimum to combat blurring. A combination of a sensitive camera and a bright light will have to be used.

#### 3.2.2 Image Sensor Technology

With the recent boom in the digital camera market there are numerous image-sensing microchips available. Two competing technologies in this arena are Complementary Metal Oxide Semiconductor (CMOS) sensors and Charge Coupled Devices (CCD). The most significant differences between the two relate to how electrons are transferred from the sensor and the fact that CMOS can incorporate more processing functions on the chip. Initially, both CMOS and CCDs were invented as solid-state memory storage devices and neither had anything to do with digital photography.

In the 1960s various scientists discovered that CMOS could be made photosensitive. Around the same time, developments in the Bell Labs found CCDs to have impressive charge transfer capabilities that would make them ideal for image sensing. The first commercially available CCD image sensor was produced in 1973.

CCDs are specialized chips, used only for image capture manufactured by only a handful of very specialized fabrication facilities such as those owned by Sony, Philips, Kodak, Matsushita, Fuji, and Sharp. CMOS however, used in many more kinds of devices, including the vast majority of consumer electronic devices, are produced using standard processes in high volume facilities. Economics of mass production are such that CMOS image sensors are considerably less expensive to manufacture.

Other factors add to CMOS image sensors cost effectiveness. They can include image processing and analogue-to-digital converters (ADC) on-chip. This makes CMOS sensors significantly less expensive to build and buy, as well as physically smaller. CMOS image sensors also require less energy than CCDs so they need less battery capacity. They are a digital camera one chip solution and normally require only additional decoupling capacitors.

In recent years, CMOS imagers have improved in picture quality significantly and now come close to rivalling CCDs. However, in systems for which image quality is the most important factor, a CCD is still superior. It has greater sensitivity to light, better dynamic range and less noise.

For this project, a CMOS imager was chosen for the above reasons and the fact that although important, absolute image quality is not the highest design priority. The image quality is likely to be limited by external factors, such as unclear water or dirt in the harsh mine environment, rather than image sensor technology itself.

#### 3.2.3 CMOS Image Sensor

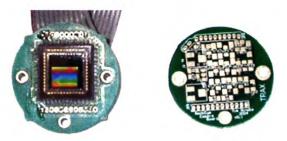

Most of the ready built camera modules are physically too large to fit inside the Perspex pipe. It is thus necessary to build up an image sensor from the basic building blocks including the CMOS chip and all associated circuitry on a custom built PCB. This also allows us to choose the best suited image sensor for this application.

There are a vast array of CMOS image sensors on the market at the moment. The main industry players are Kodak, OmniVision, Mitsubishi, ST-Microelectronics, and Micron. The full frame electronic shutter constraint is the most limiting factor as most sensors have the more common rolling shutter described in Figure 3-2. Kodak and Micron have sensors with these capabilities. However, the Kodak sensor's freeze frame only works when in single picture mode, which will not work for this application. The Micron MT9V403 image sensor, Figure 3-4, was released in November 2003. It has an array of 659x494 pixels and incorporates TrueSNAP<sup>TM</sup> full freeze frame shutter technology. The chip is capable of running at speeds of up to 200fps which is faster than will ever be required in this application. There is an onboard 10-bit ADC connected to the 10 line parallel digital output pins.

Micron is one of the leading CMOS chip manufactures worldwide. Historically they concentrated on manufacturing memory chips for PCs. Recently in 2001, they bought out Photobit, the CMOS image sensor manufacturers. Photobit were originally a spin-off company selling the image sensing technology developed by the NASA Jet Propulsion Laboratories.

The MT9V403 sensor also incorporates a two wire serial interface used to set various internal registers. These control different aspects of the sensor including exposure time, image window size, pixel gain factors, etc. Each pixel measures 9.9 by 9.9  $\mu m$

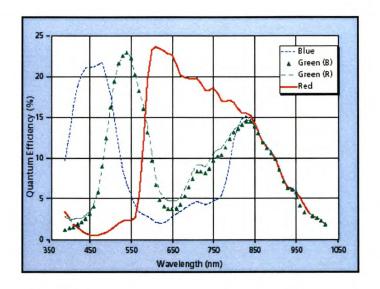

which is fairly large in comparison to most sensors on the market. The large size increases the light sensitivity and decreases the noise present. From the frequency response shown in Figure 3-5 it is clear that the sensor is sensitive to near infrared light. Either an infrared filter must be used or the lighting must not emit infrared light.

External circuitry needed to run this sensor is limited to an array of decoupling capacitors and two potentiometers for setting external voltages. A PCB was designed, then manufactured by TRAX<sup>5</sup> and populated by ELPROM<sup>6</sup>.

Figure 3-4 Camera board with Micron MT9V403 sensor front, back unpopulated.

Figure 3-5 Micron MT9V403 frequency response [8].

<sup>&</sup>lt;sup>5</sup> http://www.trax.co.za/

<sup>6</sup> http://www.elprom.co.za/

# 3.3 Processing Power

#### 3.3.1 Processing Requirements

There are many different options available to solve the processing needs for this system. The quest is to find the solution that will perform all the desired functions with a fair amount of configurability, without compromising the complexity or price of the end product.

For the high speed and accurate timing needed to get data from the CMOS imager to the flash memory, an FPGA is the optimal solution.

A DSP is the best option for the onboard image processing tasks including image scaling and unwrapping of the annular ring. However, this processing would be better done on a PC with a fast CPU and plenty of RAM rather than on an embedded processor. External data processing would mean extraneous data has to be stored in the onboard memory and a larger capacity for data storage will be needed.

The dedicated camera processors made by Texas Instruments and others are specialised and not highly configurable, although they do contain some nice features like built in JPEG encoders and USB connectivity.

The initialization procedures for the camera and flash card are easiest to perform on a microprocessor. However one can also implement simple processors on an FPGA like the Pico-Blaze 8-bit processor offered free by Xilinx.

The most common solution to the camera processing requirements is a combination of an FPGA and a small microprocessor. The FPGA is used to shift the vast amounts of data around within the strict timing constraints and the processor is used to initialize the various components as well as communicate with the outside world. However, in this design, the bold choice was made to go with just a single FPGA. At the cost of extra time and difficulty during programming, the benefits of a single chip design will pay off if this design goes into small scale production.

#### 3.3.2 FPGA Technology

There are a multitude of FPGAs on the market today. The two main chip manufactures, Xilinx and Altera dominate the market, with some competition now coming from Actel. FPGAs within the various ranges are characterized by:

- Number of system gates

- Number of IO pins

- Amount of internal RAM

- Package size

Development of the VHDL code began before the chip was chosen leading to the conclusion that one of the smaller entry level chips would suffice for this design. There was not much difference between the devices offered by Xilinx and Altera, however the embedded block memory feature of the Xilinx Virtex series finally swung the decision in their favour – even the smallest Virtex FPGA has 4 KB of internal block ram.

The major benefit of this choice is that programming for the prototype could start immediately using an FPGA test board designed by J Hargreaves<sup>7</sup>. It incorporates the smallest Xilinx in the Virtex range, the XCV50. A few board modifications were needed to access the FPGA IO pins. The test board incorporates some other ICs, however, the only ones used in the prototype were: the FPGA and associated PROM chip (highlighted in Figure 3-6): a 62.5 MHz clock, and the 3.3 V and 2.5 V power supplies.

Figure 3-6 Test board, FPGA and PROM highlighted.

<sup>&</sup>lt;sup>7</sup> Dr J Hargreaves works for Geomole and the University of Sydney.

#### 3.3.3 Xilinx Virtex FPGA

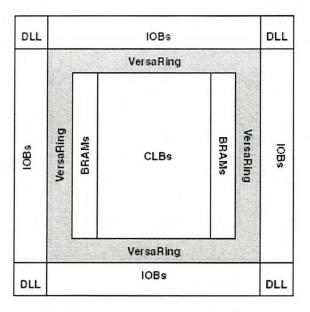

Xilinx Virtex devices feature a flexible architecture that consists of an array of configurable logic blocks (CLB) surrounded by programmable input/output blocks (IOB), all interconnected by versatile routing resources shown in Figure 3-7. Virtex FPGAs are volatile RAM-based, and are customized by loading configuration data into internal memory cells. When the power is cycled the configuration is lost. For this design a Programmable ROM (PROM) chip is connected to the FPGA so that whenever the power is switched on, the FPGA automatically configures itself from the PROM. The PROM is loaded with setup data through a JTAG port from a PC using the Xilinx software and download cable.

Figure 3-7 Virtex architecture [9].

The Xilinx XCV50 has 57,960 logic gates and is packaged in the CS144 (12x12 mm) package allowing it to have a maximum of 94 IO pins. It contains four delay-locked loops (DLL) that are used to eliminate clock-distribution delays and provide phase shifted versions of the source clock, or divide the clock by 1.5, 2, 2.5, 3, 4, 5, 8, or 16.

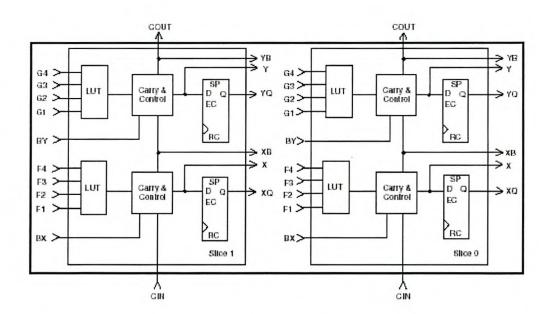

The basic building block of the Virtex CLB is the logic cell (LC). A LC includes a 4-input look up table (LUT) function generator, carry logic, and a storage element. Each Virtex CLB contains four LCs organized in two similar slices, as shown in Figure 3-8. These simple building blocks are routed together to form complex logic capable of executing the desired processing tasks.

Figure 3-8 Two slice vertex CLB [9].

# 3.4 Flash Memory

#### 3.4.1 Memory Storage Requirements

The recent developments in the field of mass storage flash solutions is the main enabling technology that allows this autonomous device to be built, permitting the RockEye to break away from the conventional TV camera on a wire devices.

Previously, the forms of non-volatile memory included EEPROM, DataFlash™, and magnetic storage media. These old technologies are too bulky, too slow, or do not have enough storage capacity for this application. Flash memory is so called because entire sections of the microchip can be erased at once, or flashed. Most high end flash memory is based on NAND gate technology.

The storage capacity for this system can be accessed from an area perspective. For a 150 m borehole of 48 mm diameter (150.7 mm circumference) the borehole picture area is 22.619 m<sup>2</sup>. A resolution of 0.2 mm per pixel in both directions, gives 25 million pixels per square metre. This works out to 565 million pixels, with 8 bits per pixel a total storage capacity of 565 MB of data is needed.

These calculations are for a perfect system, however currently there is no means for the probe to accurately measure the distance into the hole. Thus the frame rate and size of the picture will have to be accurately matched to the deployment speed with an additional overlap. The overlap must be able to cover for the variations in speed to ensure that no image information is lost. The average percentage overlap is directly proportional to the increase in data. Additionally, all parts of the image are not taken at the same resolution as shown in Figure 3-1, resulting in an added increase in data. However, flash technology is developing at a rapid rate and there are currently up to 1 GB flash cards on the market.

Another constraint on the storage medium is the burst and sustained write speeds. Burst write speed is defined as the maximum speed at which data can be written to the flash device. The sustained rate is the average write rate, taking into account the time between write operations when the microchip is busy. To calculate the maximum data rate needed for this application – assume 10 fps and that the entire image square image (480x480 pixels) is stored for each frame. Each frame then contains 230400 bytes of data resulting in a required maximum data rate of 2.3 MB/s.

#### 3.4.2 Flash Technology

Two different approaches can be taken when deciding on which flash technology to use. One option is to use the basic flash microchip. These are simply bulk storage devices with no additional internal circuitry. However, flash memory is not completely reliable, two different types of errors present themselves, bad blocks from manufacturing faults and erroneous bits appearing during operation. Initial bad blocks have to be scanned for and mapped out by the firmware before any writing operations can take place. The error bits that appear from time to time can be corrected by developing error correcting codes. Developing this firmware would be time consuming and it is currently the subject of an MSc thesis<sup>8</sup> here at Stellenbosch University.

The other option is to use one of the pre-packaged flash cards as used in digital cameras and hand held PCs. Most of these cards include sophisticated controllers that handle the transfer of data to the flash memory, as well as powerful error correcting codes. For example the SD card has a data reliability rating of less than one non-recoverable error in 10<sup>14</sup> bits read. This means that there should be less than one bit error for every 12 500 gigabytes of data read. Table 3-1 documents the specifications of some of the more popular flash cards on the market at the moment.

<sup>&</sup>lt;sup>8</sup> Ian Horsburgh, "The Analysis of NAND Flash Memory for a Mass Memory Unit on a Micro-Satellite", Electronic System Laboratory.

|                             | SD       | MMC      | Compact   | Smart   | Memory            |

|-----------------------------|----------|----------|-----------|---------|-------------------|

| D D .:                      | 11.5     |          | Flash     | Media   | Stick             |

| Power Ratings               |          |          |           | 10.0    | The second second |

| Sleep                       | 150 μΑ   | 150 μΑ   | 200 μΑ    | 20 μΑ   | 1.5 mA            |

| Read                        | 40 mA    | 35 mA    | 35 mA     | 10 mA   | 65 mA             |

| Write                       | 45 mA    | 45 mA    | 35 mA     | 10 mA   | 100 mA            |

| Typical speeds <sup>9</sup> |          |          |           |         |                   |

| Burst [MB/s]                | 10       | 2.5      | 16        | 8       | 10                |

| Read [MB/s]                 | 3 - 10   | 1.4      | 3.3 - 5.9 | 3.5     | 10                |

| Write[MB/s]                 | 0.8 - 9  | 1.2      | 1.5 - 4.8 | 3.5     | 1.875             |

| Physical size               |          |          |           |         |                   |

| Length [mm]                 | 32       | 32       | 36.4      | 45      | 50                |

| Width [mm]                  | 24       | 24       | 42.8      | 37      | 21.5              |

| Thickness [mm]              | 2.1      | 1.4      | 3.30      | 0.76    | 2.8               |

| Capacity [MB]               | 16 -1000 | 32 - 128 | 64 - 4000 | 8 - 128 | 128 - 2000        |

| Temp Rating [°C]            | -25 – 85 | -25 - 85 | 0-60      | 0 – 55  | -25 - 85          |

Table 3-1 Flash card comparisons.

The borehole probe size constraint excludes use of the Compact Flash and Smart Media cards. It is notoriously difficult to get hold of the technical data regarding operating the Sony memory stick and for this reason it was excluded. The two cards left, the Multimedia card (MMC) and its successor, the Secure Digital (SD) card are physically almost the same size and compatible in some devices. However the MMC is not produced in large capacities (greater than 128 MB) and has slow read and write speeds. SD cards contain newer technology and are being aggressively developed as well as adopted in many new products including a range of Nokia phones. There is also an Ultra II range of SanDisk SD cards that have a guaranteed sustained read and write speed of above 9 MB/s. For the prototype RockEye a 256 MB SanDisk Ultra II SD card was used.

Figure 3-9 SanDisk Ultra II SD flash card.

<sup>&</sup>lt;sup>9</sup> The write and read speed vary considerably from one brand of card to another. Speeds also vary considerably between different capacity cards from the same manufacturers. Speeds based on results from <a href="http://www.digit-life.com/articles2/flashcard-test/flashcard-test-p2.html">http://www.digit-life.com/articles2/flashcard-test/flashcard-test-p2.html</a>

#### 3.4.3 Secure Digital Card

The SD Card specifications were originally defined by Matsushita Electric Company, Toshiba Corporation and SanDisk Corporation. Currently, the specifications are controlled by the Secure Digital Association (SDA)<sup>10</sup>. The SanDisk SD Card [10] was designed to be compatible with the SD Card Physical and Protocol Specification as set out by the SDA.

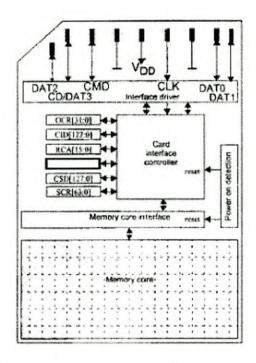

Figure 3-10 Secure Digital flash card inner workings [10].

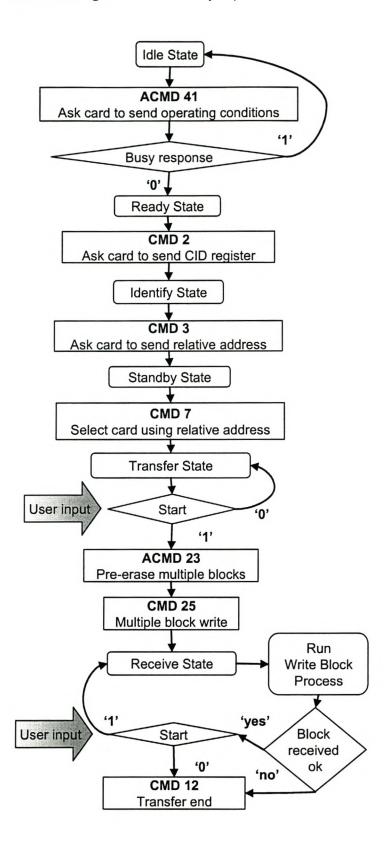

The SD card has nine external lines: four data lines, a clock line, a command line, a power line and two grounds. The card can be used in either one or four data wire mode. With one wire the maximum data rate is 3.125 MB/s and with four it is 12.5 MB/s, however, this is the burst speed whereas this system is still limited by the overall sustained transfer rate of the card. Figure 3-10 shows a representation of the internals of an SD card. The flash memory core is controlled through the memory core interface by the card interface controller. The smallest amount of data that can be read or written is 512 bytes. There are also various registers and card addresses that can be read. A complex initialization procedure must be followed, which is described in more detail in Chapter 5.

<sup>10</sup> http://www.sdcard.org

#### 3.5 USB Communication

From the initial specifications the Bluetooth protocol for wireless downloads was investigated. Currently, there is a good implementation for serial RS232 to Bluetooth connectivity using Bluewave technology. However, this would be a laboriously slow process as the current serial download speed is 57 600 bits per second. Approximate download times for two different sized files are shown in Table 3-2 for different communication protocols. Firewire, also known as IEEE 1394, is not included as it is very similar to USB 2.0 in speed.

| Protocol              | Speed   | Speed  | 90 MB file    | 512 MB file   |

|-----------------------|---------|--------|---------------|---------------|

|                       | [kB/s]  | [kB/s] | download time | download time |

|                       |         |        | [h:m:s]       | [h:m:s]       |

| RS-232                | 57.6    | 7.2    | 3:30:00       | 19:45:00      |

| Bluetooth             | 723     | 90.125 | 0:16:00       | 1:34:00       |

| USB1.1                | 1500    | 187.5  | 0:08:00       | 0:47:00       |

| USB1.1- Full Speed    | 12 000  | 1500   | 0:01:00       | 0:06:00       |

| USB 2.0 <sup>11</sup> | 480 000 | 60 000 | 0:00:02       | 0:00:09       |

Table 3-2 Data rates of various communications protocols.

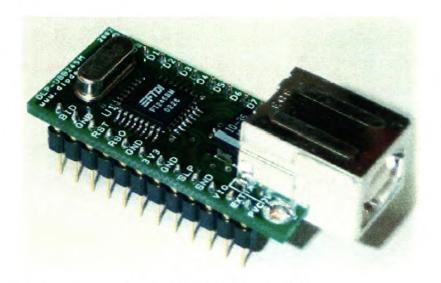

From Table 3-2 it is clear that for a reasonable download time the minimum acceptable protocol is USB 1.1. There is a very useful chip made by FTDI, the FT245BM. This IC accepts 8-bits data and handles all USB communications with a host PC, in a first in first out (FIFO) manner. It includes a 384 byte transmit buffer and a 128 byte receive buffer which ensures maximum data transfer rate. There are free dynamic link libraries (Dlls), provided by the manufacturer to aid in Windows<sup>TM</sup> USB direct communications development. Data can be transferred at up to 1 MB/s using these USB Dlls. This chip is also available as part of a ready built module, as shown in Figure 3-11, including the necessary external circuitry and USB connector – very handy for development work.

27

<sup>&</sup>lt;sup>11</sup> Assuming the flash memory could be read at this speed, which is not possible.

Figure 3-11 USB module including FTDI245BM microchip [11].

The USB chip is fairly easy to operate. Data is placed on the 8 parallel input lines and the write line (WR) is clocked from high to low. The transmit allow (TXE#) line should also be monitored to check when the internal buffer is full. On the PC side an application is written using Borland C++ Builder to communicate through the FTDI Dlls with the USB port. The received data is then saved directly to file. Before the SD card was up and running, this USB module was used extensively and the first pictures from the camera were downloaded through it. This was an important step in the development of the entire system as it proved the camera and FPGA were working correctly before the memory card was added.

Figure 3-12 First picture from the camera, downloaded through USB port.

## 3.6 LED Lighting Circuitry

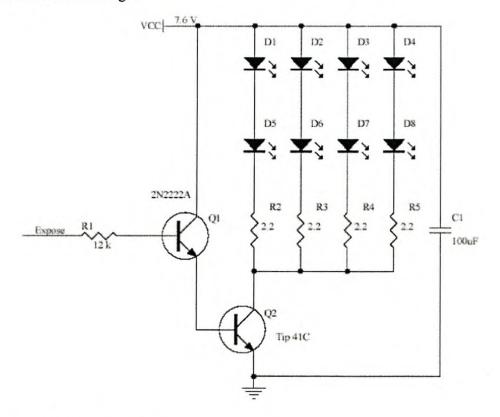

The Golden Dragon™ LEDs made by OSRAM draw 350mA each and have a forward voltage of 3.2 - 3.6 V. Their spectral emission does not extend past the visual range so no infrared filters are necessary for the camera. They are capable of emitting 10,000 mcd with a viewing angle of 120°. During operation they need to dissipate one watt of power which is only possible if special considerations and materials are taken into account when designing and manufacturing their mountings. To save power and eliminate the need for this costly thermal management, the LEDs are only turned on when the camera is in the expose mode. The digital expose pin output from the MT9V403 image sensor goes high whenever the sensor is taking a picture. This pin can only drive 0.2 mA and is thus connected through a modified Darlington pair transistor circuit to drive the high power LEDs directly from the 7.6 V battery pack. The LEDs cannot be connected directly in parallel as their forward voltages differ and are therefore connected as four sets of two LEDs in series each with a resistor. Figure 3-13 shows this circuit. A high power TIP41C transistor is used to switch on the LEDs handling a peak current of 1.4 A. A large capacitor is added in parallel to handle the current surges.

Figure 3-13 LED driver circuit.

## **Chapter 4 Optical Design**

This chapter presents the design and implementation of the optics part of the RockEye system. The goals for the optics are first described, followed by an in-depth study. Two different optical solutions, the conic mirror and the fisheye lens, are presented.

## 4.1 Optics Overview

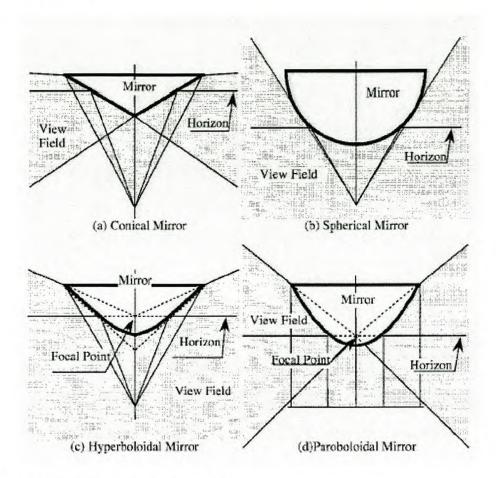

The objective for the optics in this system is to map an image of the circular borehole onto the flat CMOS sensor. There are various ways to acquire an omnidirectional (360°) view using a single camera as presented in patents, available literature, and existing systems, including:

- Hyperbolic mirrors

- Paraboloidal mirrors

- Spherical mirrors

- Conical mirrors

- Fisheye lenses

With the exception of the fisheye lens, which will be dealt with later, the above omnidirectional sensors consist of a combination of lenses and mirrors. These are known as catadioptric systems. Dioptrics is the science of lens refracting elements, and catoptrics the science of mirror reflecting surfaces [12]. The combination of refracting and reflecting elements is therefore referred to as catadioptrics.

The most common catadioptric setup includes a convex mirror placed in front of a lens and aligned with the centre of the lens system on the optical axis. The mirror collects light from 360 degrees around the device, reflecting it through the lens system, which focuses it to provide a sharp picture on the CMOS sensor. The generalised setup is shown in Figure 4-1. Instead of using mirrors, prisms could also have been used, where the shape of the mirror is cut from a suitable transparent medium, based on the total internal reflection criteria. A prism system has to be well designed to stop chromatic aberrations causing the various colours of the spectrum to

be refracted at slightly different angles. Before describing each of the omnidirectional mirror setups in more detail, some constraints are introduced.

Figure 4-1 General optics setup.

One of the constraints often cited in omnidirectional literature is the single view point constraint. Under the single viewpoint constraint, every pixel in the sensed image measures the irradiance of the light passing through the viewpoint in one particular direction. A single viewpoint is desirable as it is a requirement for the generation of geometrically correct perspective images as well as panoramic ones from the images captured by the catadioptric cameras. However, although it is optically beneficial, it is not an absolute necessity for this system to have a single viewpoint in order to produce useful images.

The other constraints are of a more practical nature – the optics for this system should be small to fit inside the borehole. The mirror must be physically easy to manufacture or commercially available – custom optics are often prohibitively expensive, with long lead times for manufacture. It is more preferable to be able to use off the shelf components.

Figure 4-2 Mirror field of view, image from [14].

## 4.1.1 Spherical, Hyperboloidal, and Parabolodial Mirrors

These three mirrors shown in Figure 4-2b, c and d are fairly similar in nature. They all have a large angular field of view – which is not necessary for this application as the camera is only viewing a thin band of the rock wall. The spherical mirror has the largest field of view and has good central resolution but poor peripheral resolution. According to Baker and Nayar [13], the spherical mirror satisfies the single viewpoint constraint only when the effective pinhole is placed at the base of the sphere – in which case the observer will only be able to see itself as the point of the sphere is flat. Hyperbolodial and parabolodial mirrors do conform to the single viewpoint constraint and have better peripheral resolution due to the narrower field of view.

#### 4.1.2 Conical Mirror

The cone mirror or conic section can be though of as an angled plane mirror rotated about the optical axis. The cone mirror is the only system that can get a perfect image vertically when you use a perfect lens system as it is a plane mirror in the vertical direction. All other curved mirrors introduce defocus blurs in the vertical direction as they are curved longitudinally [13]. So even with a perfect lens system you can not get a perfect vertical image in those mirrors. In the concentric direction, all omnimirrors are curved with the same horizontal cross-section shape – circles.

Baker and Nayar [13] as well as Yagi [14] suggest that the conical mirror has a single view point, but as it is located at the tip of the cone it is a degenerative case and not of any practical value. However, Lin and Bajcsy [15], argue that if true geometric Gaussian optics are used in place of the simplified pin-hole optics, used by Baker and Nayar, there are two effective pinholes in the system – one at the tip of the cone, the other a distance f away. Where f is the front focal length of the thin lens used. Lin and Bajcsy built a successful prototype system to prove their theory.

The conical mirror configuration also gives a linear compression of the image towards the centre of the cone – this should make the unwrapping algorithm easier. Conical mirrors are also commercially available off the shelf from Edmund Scientific<sup>12</sup>. They stock a range of micro lenses with 10, 5, and 3 mm diameters costing about US \$175 each.

Due to the positive reviews in Lin and Bajcsy's article and their commercial availability, initial test went ahead with the conic mirror setup. However, as described in Section 4.2, problems were encountered and a fisheye lens was also investigated, described in Section 4.3.

<sup>12</sup> http://www.edmundoptics.com

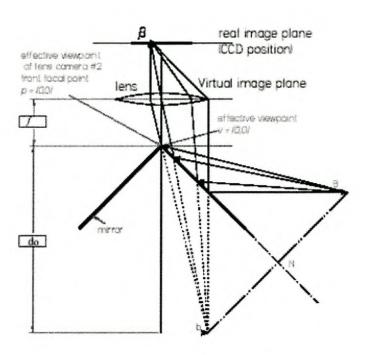

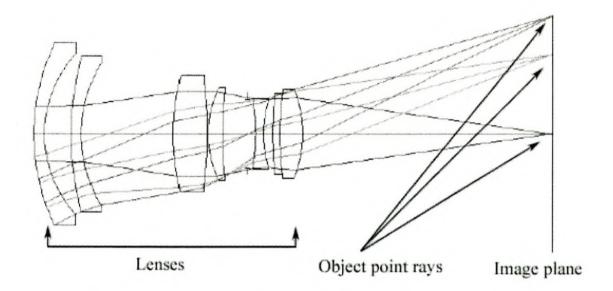

### 4.2 Conical Mirror Optical Setup

The setup for an omnidirectional imaging system using a conical mirror as suggested by Lin and Bajcsy is shown in Figure 4-3. The setup consists of a mirror, a thin lens and an image sensor. The point of the conical mirror is placed a distance f away from the lens at the front focal point. Point B is the imaged point on the borehole wall; b is the virtual point as seen when looking at the mirror from the top;  $\beta$  is the corresponding point on the image plane, sensed on the CMOS imager. Various rays are traced between B and  $\beta$  to give some insight as to what is happening with the optics.

Figure 4-3 Cone mirror setup as suggested by Lin and Bajcsy [15].

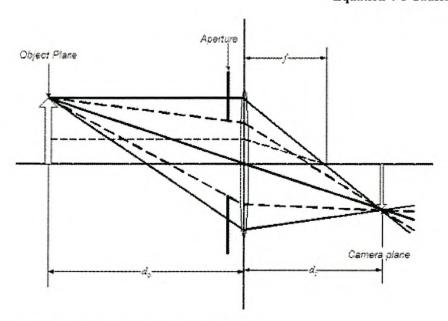

The system can then be focussed according to Gaussian optic lens laws, ignoring the lens and just calculating the total path length. Where  $d_0$  is the total ray distance to the object being imaged;  $d_i$ , the distance from the virtual image plane to the image sensor; and f the lens's focal length.

Gaussian optics was developed for paraxial<sup>13</sup> rays. It states that all rays that come from the same object point in the world and enter the focused optical system, converge at the same point. Using this, any two rays can be traced from a world point to find its image point. Normally the two most easily traced rays are used.

- The ray that passes through the front focal point is refracted by the lens and then proceeds parallel to the optical axis.

- The ray that passes through the centre of the lens is not affected and carries on travelling in its original direction.

This is illustrated in Figure 4-4. Equation 4-1, the standard thin lens formula, can be derived from similar triangles. The magnification (m) can also be worked out from the relationship between  $d_i$  and  $d_o$ .

$$\frac{1}{d_o} + \frac{1}{d_i} = \frac{1}{f}$$

$$m = \frac{d_i}{d_o}$$

Equation 4-1 Gaussian thin lens formula.

Figure 4-4 Gaussian simple lens setup<sup>14</sup>.

<sup>&</sup>lt;sup>13</sup> Rays that arrive at the lens at shallow angles with respect to the optical axis, i.e. almost parallel to the axis.

<sup>&</sup>lt;sup>14</sup> Image from <a href="http://www.high-techdigital.com/integration/optics\_t\_2.htm">http://www.high-techdigital.com/integration/optics\_t\_2.htm</a>

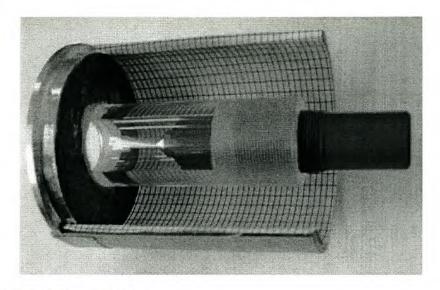

Armed with the theoretical knowledge of the accepted setup of an omnidirectional catadioptric sensor, a test setup was built. Three conical 45° mirrors were sourced. Two, a 10 mm and a 5mm, come from Edmund Scientific in the U.S and one, a 14 mm, from MIT (Measurement Instrumentation Technology) in Johannesburg. The 14 mm glass cone was not coated originally and it was kindly coated with reflective aluminium by METGLO in Brakenfell. The mirrors were then mounted into the threaded PVC holders shown in Figure 4-5.

Figure 4-5 Test mirrors (14, 10, 5 mm) and clear mounting tube.

These PVC holders screw into a clear Perspex tube into which the camera is mounted on the opposite side. A section of 66 mm PVC pipe was cut and used as a test borehole, shown in Figure 4-6. Different printed test patterns were placed inside, in Figure 4-6 it contains a grid pattern. A circular aluminium disk was machined to hold the Perspex pipe in the centre of the test borehole.

Figure 4-6 Conical mirror test setup.

A standard PCB mount lens holder with a micro-lens was mounted onto the camera board and connected to the Perspex tube. It was soon found that the standard micro lenses are more complicated than they seem. Further investigation by Robin Starke [16], revealed that these seemingly simple lenses actually consist of three to four internal lens elements and are remarkably complex for such standard, inexpensive lenses. They also have different front and back focus planes that are not well defined – which makes focussing by any means other than educated trial an error impractical.

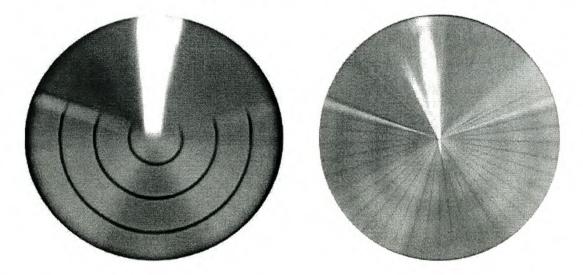

Figure 4-7 Concentric or radial lines in focus<sup>15</sup>.

<sup>&</sup>lt;sup>15</sup> These photos were taken using a Nikon Coolpix digital camera.

The photos in Figure 4-7 are taken using the test setup shown in Figure 4-6, photographing the mirror in the test setup viewing the grid pattern. Due to the time consuming processes involved in taking pictures, and the difficulty in changing the focus of the RockEye camera while connected in the test setup, a standard digital camera was used to take the above pictures. By varying the focus settings it is possible to either get the concentric ring (left-hand picture) or the radial lines (right-hand pictures) in focus. This unexpected result was confusing at first but was clarified by looking through Hecht's chapter on aberrations [12]. Figure 4-7 exhibiting the effects of the astigmatism aberrations, introduced by the conical mirror.

Astigmatism in classic optics is a defect in the surface of a lens or mirror where the focus of a light beam varies depending on how far off centre the light beam hits the lens or mirror. For example, light hitting the centre of an astigmatic lens might focus at 20 cm while light hitting the outside of the lens would focus at 20.5 cm. The actual focus of the lens would then vary from 20 to 20.5 cm, with no perfect focus. However, in this case the astigmatism is caused by the curvature of the conical mirror.

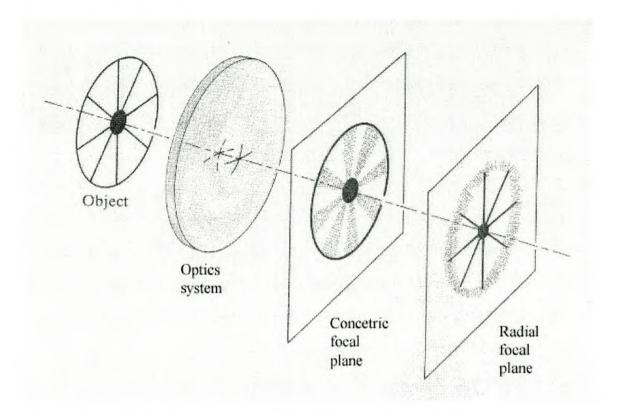

If a plane of light aligned with the optical axis hits the conical mirror, it encounters a plane mirror and is reflected accordingly. However, if a plane of light perpendicular to the optical axis hits the cone it encounters a mirror circular in shape – this causes the light to diverge more than it would when hitting a plane. The end result of this phenomenon is that the concentric focal length differs from the radial one. In omnidirectional literature this effect is commonly referred to as defocus blur and is common to all catadioptric sensors. This effect seen in the test images of Figure 4-7 is demonstrated in Figure 4-8 from Hecht [12].

Figure 4-8 Images in the concentric and radial focal planes, modified from [12].