# The Design of a High-Performance, Floating-Point Embedded System for Speech Recognition and Audio Research Purposes

William Duckitt

Thesis presented in partial fulfilment of the requirements for the degree Master of Science in Electronic Engineering at the University of Stellenbosch

> Supervisor: Dr TR Niesler Co-supervisor: Mr W Smit

> > December 2007

i

### Declaration

I, the undersigned, hereby declare that the work contained in this thesis is my own original work and that I have not previously in its entirety or in part submitted it at any university for a degree.

Signature:..... Date:.....

Copyright © 2007 Stellenbosch University All rights reserved

### Abstract

This thesis describes the design of a high performance, floating-point, standalone embedded system that is appropriate for speech and audio processing purposes.

The system successfully employs the Analog Devices TigerSHARC TS201 600MHz floating point digital signal processor as a CPU, and includes 512MB RAM, a Compact Flash storage card interface as non-volatile memory, a multi-channel audio input and output system with two programmable microphone preamplifiers offering up to 65dB gain, a USB interface, a LCD display and a push-button user interface.

An Altera Cyclone II FPGA is used to interface the CPU with the various peripheral components. The FIFO buffers within the FPGA allow bulk DMA transfers of audio data for minimal processor delays. Similar approaches are taken for communication with the USB interface, the Compact Flash storage card and the LCD display.

A logic analyzer interface allows system debugging via the FPGA. This interface can also in future be used to interface to additional components. The power distribution required a total of 11 different supplies to be provided with a total consumption of 16.8W. A 6 layer PCB incorporating 4 signal layers, a power plane and ground plane was designed for the final prototype.

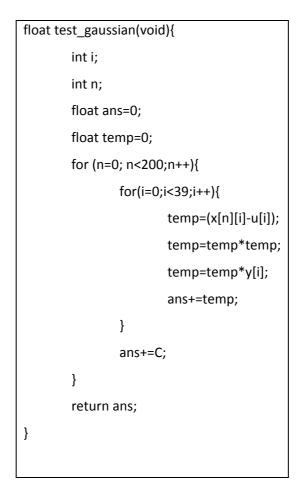

All system components were verified to be operating correctly by means of appropriate testing software, and the computational performance was measured by repeated calculation of a multi-dimensional Gaussian log-probability and found to be comparable with an Intel 1.8GHz Core2Duo processor.

The design can therefore be considered a success, and the prototype is ready for development of suitable speech or audio processing software.

### Opsomming

Die tesis beskryf die ontwerp van 'n hoë werk verrigting, wisselpunt stelsel wat geskik is vir spraak-en klank toepassings.

Die stelsel maak gebruik van 'n Analog Devices TigerSHARC TS201 600MHz wisselpunt digitale seinverwerker as sentrale verwerker met 512MB RAM. Dit gebruik 'n Compact Flash geheuekaart as lees-alleen-geheue en het 'n multi-kanaal klank inset/uitset poorte met twee programmeerbare mikrofoon voor-versterkers wat tot 65dB aanwins lewer. Dit het ook 'n USB koppelvlak, 'n LCD skerm en 'n gebruikerskoppelvlak.

'n Altera Cyclone II FPGA word gebruik om met die CPU en verskeie ander komponente te kommunikeer. Die FIFO buffers binne die FPGA laat DMA blokoordrag van klank data toe met minimale verwerkervertragings. Die kommunikasie word op 'n soortgelyke manier word gedoen met die USB koppelvlak, die Compact Flash kaart en die LCD skerm.

Die logiese analiseerderkoppelvlak laat stelselontfouting toe via die FPGA. Die koppelvlak kan ook in die toekoms gebruik word om met bykomende komponente te kommunikeer. Die kragstelsel het 'n totaal van 11 verskillende toevoere benodig, met 'n totale verbruik van 16.8W. Die finale prototipe gebruik 'n 6 vlak gedrukte etsbaanboard met 4 sein lae, een krag laag en 'n grond laag.

Alle stelselkomponente is geverifieer om korrek te funksioneer met gepaste toets sagteware, en die berekeningswerksverrigting is gemeet deur herhaalde berekening van 'n multidimensionele Gauss logwaarskynlikheid. Dit is gevind om vergelykbaar te wees met 'n Intel 1.8GHz Core2Duo verwerker.

Die ontwerp is daarom 'n sukses en die prototipe is reg vir ontwikkeling van gepaste spraak en klank verwerkingssagteware.

## Acknowledgements

To my supervisor, Dr Thomas Niesler, for your tremendous support and guidance, and for providing all the necessary equipment to successfully implement this design.

To Willem Smit, for all your advice in the field of embedded design.

To my parents and my brother, for their enduring support throughout my studies.

## Contents

| Declaration                                | ii  |

|--------------------------------------------|-----|

| Abstract                                   | iv  |

| Opsomming                                  | v   |

| Acknowledgements                           | vi  |

| List of Figures                            | xii |

| List of Tables                             | xiv |

| Abbreviations                              | xv  |

| 1 Introduction                             | 1   |

| 1.1 System Requirements                    | 2   |

| 2 Processor Selection                      |     |

| 2.1 Comparison of processors               |     |

| 2.1.1 Analog Devices TigerSHARC TS201      |     |

| 2.1.2 Analog Devices SHARC 21368 Processor |     |

| 2.1.3 Texas Instruments TMS320C6727        |     |

| 2.1.4 Microchip dsPIC30F6014               |     |

| 2.1.5 Freescale MPC7457:                   |     |

| 2.1.6 Renesas SH7751:                      |     |

| 2.2 Conclusion                             | -   |

|                                            |     |

|                                            |     |

| 4 The Central Processing Unit              |     |

| 4.1 TigerSHARC Computational Blocks        |     |

| 4.2 TigerSHARC internal memory             |     |

| 4.3 External Port                          |     |

| 4.3.1 Pipelined protocol                   | 20  |

| 4.3.2                                                                                                            | Slow device protocol                                                                                                                                                                                     | 21                                                       |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 4.3.3                                                                                                            | DMA Controller                                                                                                                                                                                           | 23                                                       |

| 4.3.4                                                                                                            | Interrupt controller                                                                                                                                                                                     | 23                                                       |

| 4.3.5                                                                                                            | EPROM/FLASH Interface                                                                                                                                                                                    | 23                                                       |

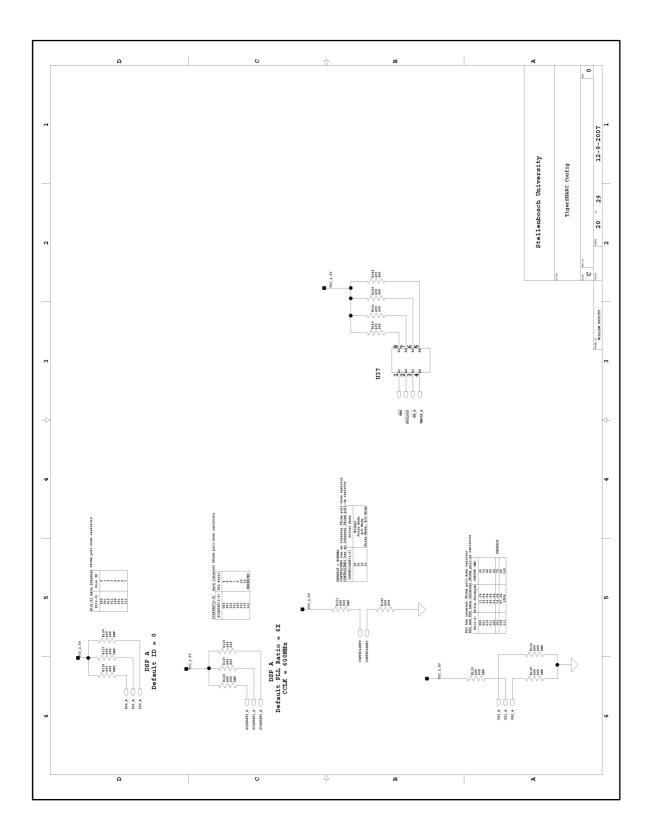

| 4.4 Tig                                                                                                          | erSHARC Configuration                                                                                                                                                                                    | 24                                                       |

| 4.4.1                                                                                                            | TigerSHARC Clock Domains                                                                                                                                                                                 | 24                                                       |

| 4.4.2                                                                                                            | Reference Voltage Filtering                                                                                                                                                                              | 25                                                       |

| 4.4.3                                                                                                            | Processor Identification                                                                                                                                                                                 | 25                                                       |

| 4.4.4                                                                                                            | IO Driver Impedance Control                                                                                                                                                                              | 25                                                       |

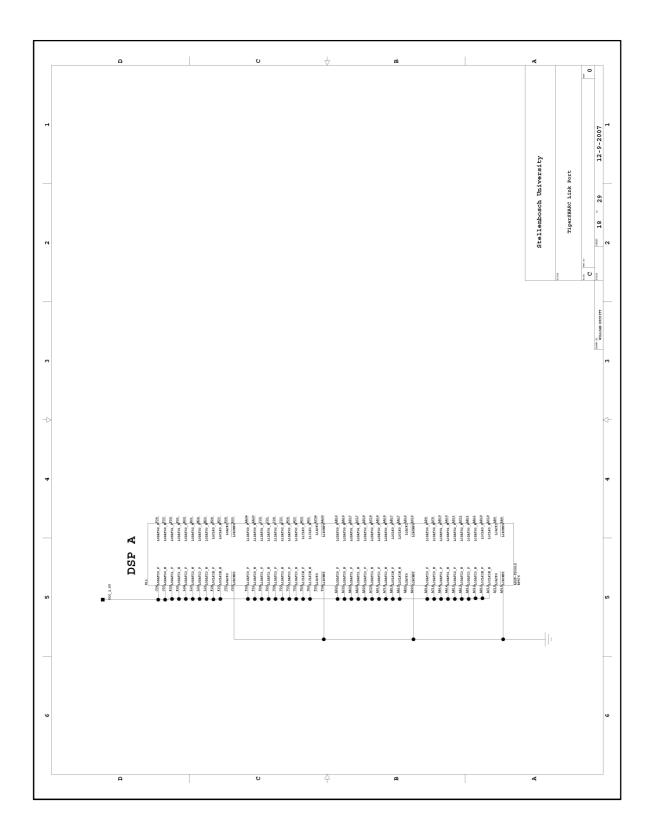

| 4.4.5                                                                                                            | Link Port Termination                                                                                                                                                                                    | 26                                                       |

| 4.4.6                                                                                                            | Configurable pins                                                                                                                                                                                        | 26                                                       |

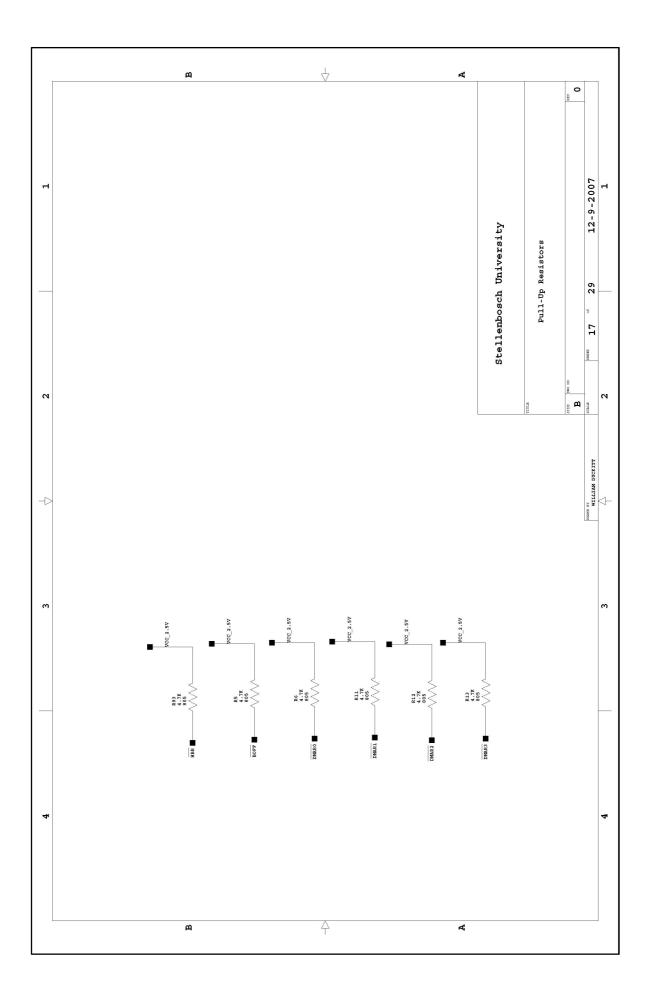

| 4.4.7                                                                                                            | Miscellaneous pull-up resistors                                                                                                                                                                          | 26                                                       |

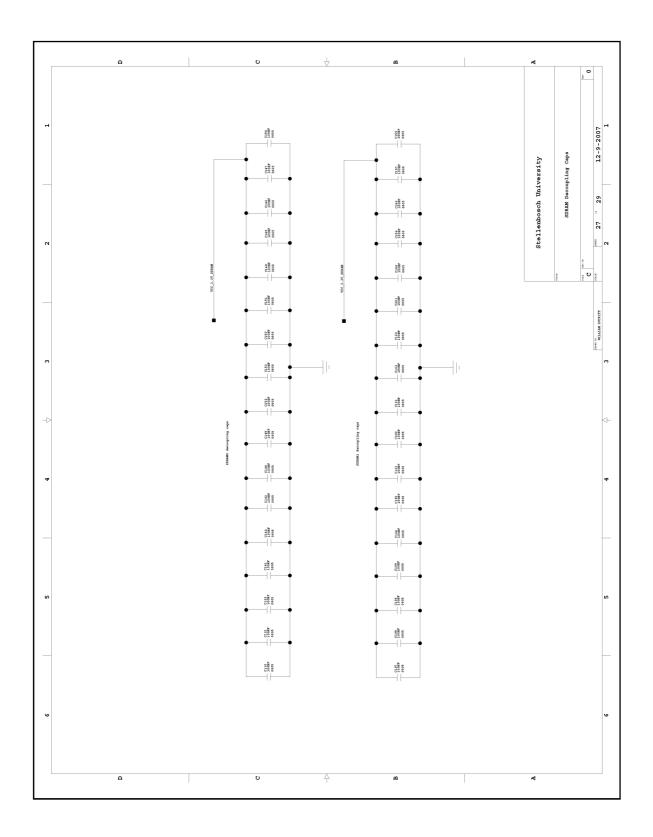

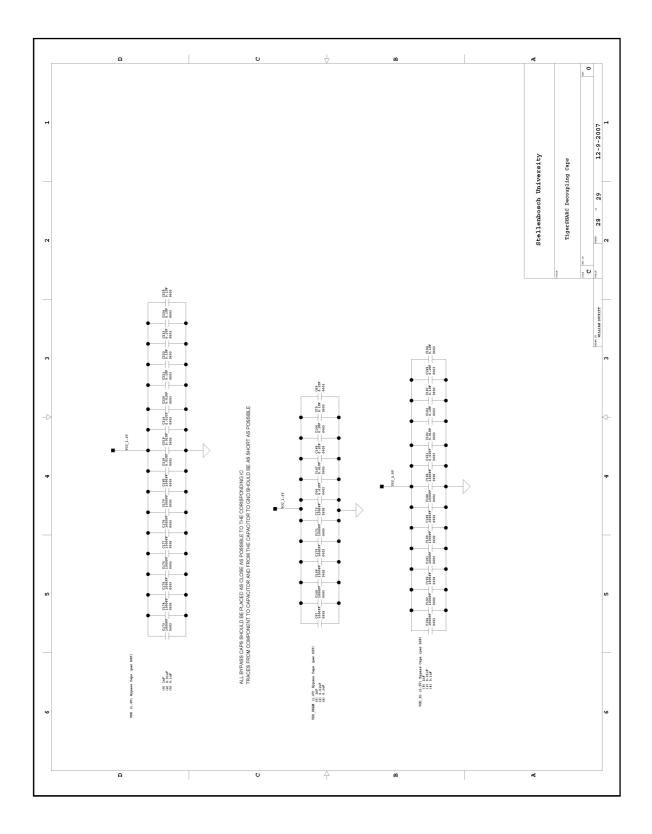

| 4.4.8                                                                                                            | Power Supply Pins and Decoupling.                                                                                                                                                                        | 27                                                       |

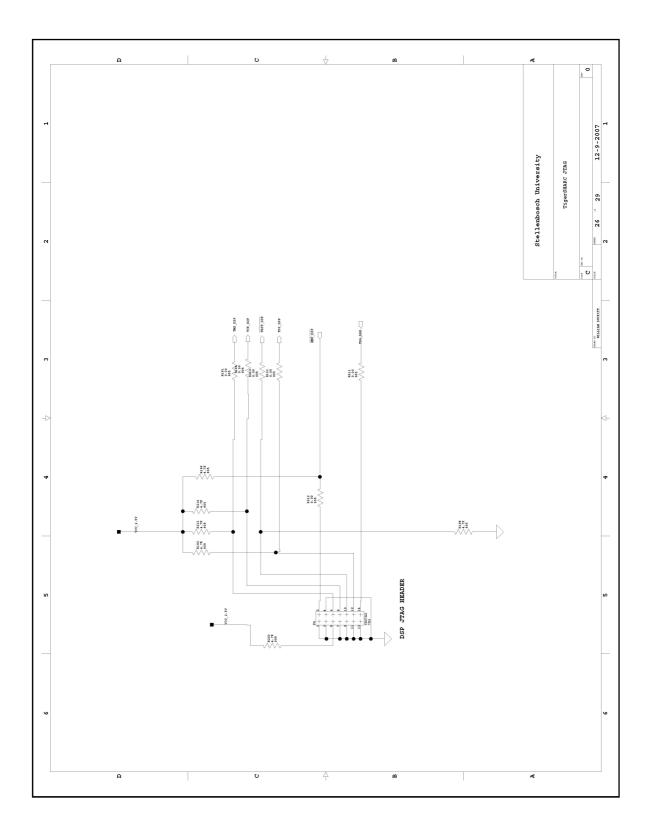

| 4.4.9                                                                                                            | TigerSHARC JTAG Interface                                                                                                                                                                                | 27                                                       |

| 4.5 The                                                                                                          | ermal Relief                                                                                                                                                                                             | 28                                                       |

|                                                                                                                  |                                                                                                                                                                                                          |                                                          |

| 4.6 Sur                                                                                                          | mmary and Conclusion                                                                                                                                                                                     |                                                          |

|                                                                                                                  | nmary and Conclusion                                                                                                                                                                                     |                                                          |

| 5 FPGA Sy                                                                                                        |                                                                                                                                                                                                          | 31                                                       |

| 5 FPGA Sy<br>5.1 Alt                                                                                             | /stem                                                                                                                                                                                                    | 31                                                       |

| 5 FPGA Sy<br>5.1 Alt<br>5.2 Tig                                                                                  | era Cyclone II FPGA                                                                                                                                                                                      | 31<br>31<br>31                                           |

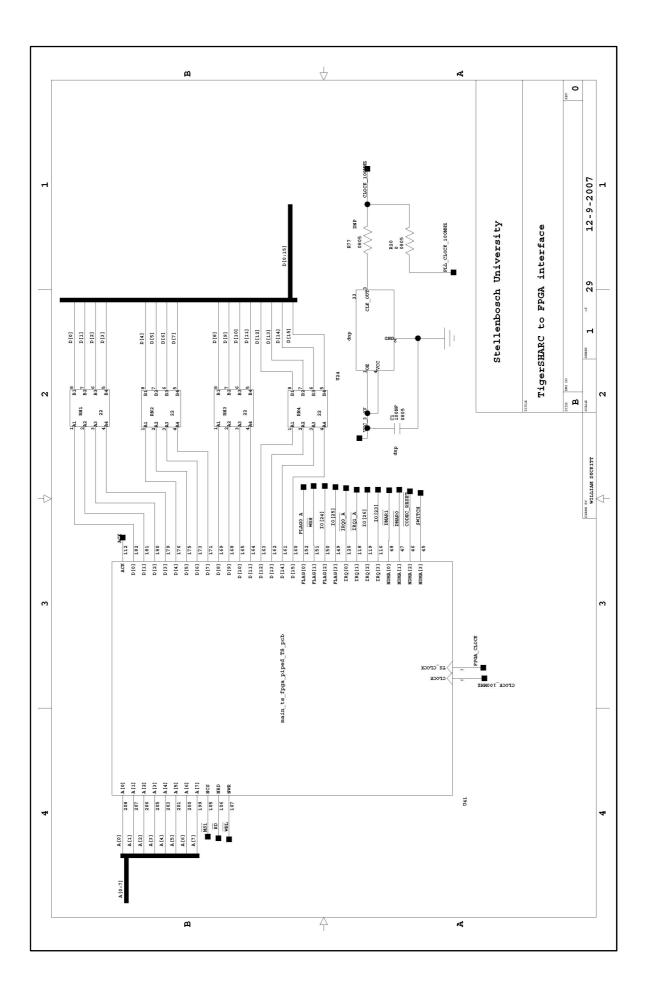

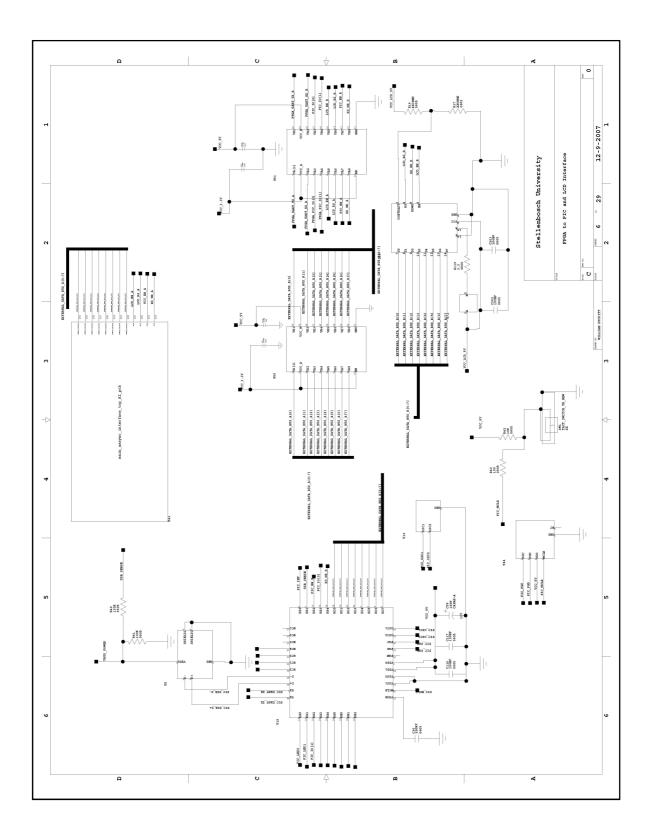

| 5 FPGA Sy<br>5.1 Alt<br>5.2 Tig<br>5.3 FPC                                                                       | era Cyclone II FPGA<br>erSHARC to FPGA interface                                                                                                                                                         | 31<br>31<br>31<br>31                                     |

| 5 FPGA Sy<br>5.1 Alt<br>5.2 Tig<br>5.3 FPC<br>5.4 FPC                                                            | era Cyclone II FPGA<br>erSHARC to FPGA interface<br>GA Internal module design                                                                                                                            | 31<br>31<br>31<br>36<br>39                               |

| 5 FPGA Sy<br>5.1 Altr<br>5.2 Tig<br>5.3 FPC<br>5.4 FPC<br>5.5 FPC                                                | era Cyclone II FPGA<br>erSHARC to FPGA interface<br>GA Internal module design<br>GA Control Register                                                                                                     | 31<br>31<br>31<br>36<br>39<br>39                         |

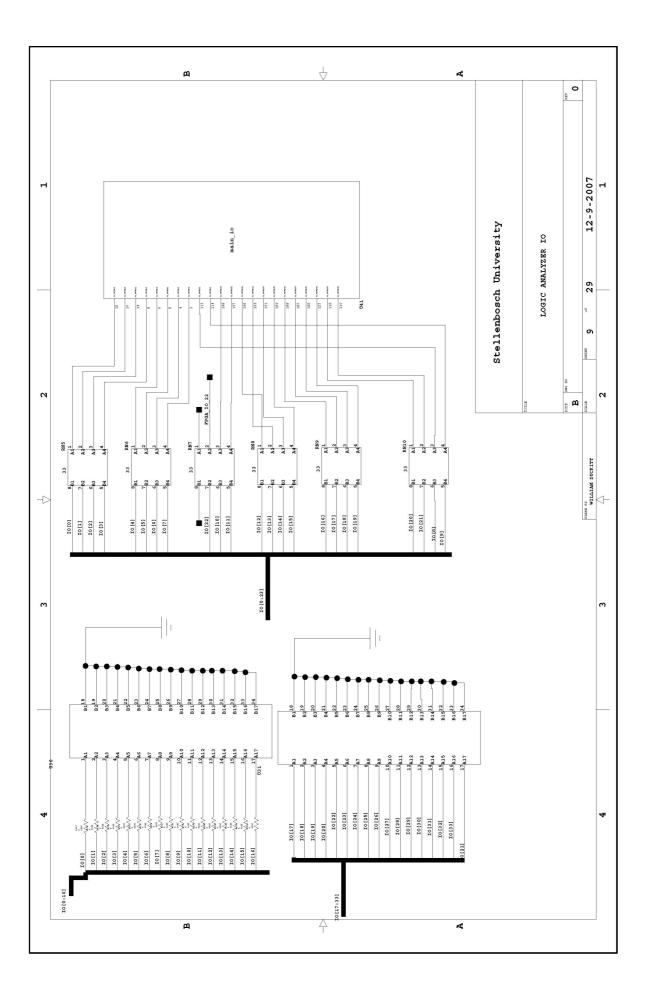

| 5 FPGA Sy<br>5.1 Alt<br>5.2 Tig<br>5.3 FPC<br>5.4 FPC<br>5.5 FPC<br>5.6 FPC                                      | rstem<br>era Cyclone II FPGA<br>erSHARC to FPGA interface<br>GA Internal module design<br>GA Control Register                                                                                            | 31<br>31<br>36<br>36<br>39<br>39<br>                     |

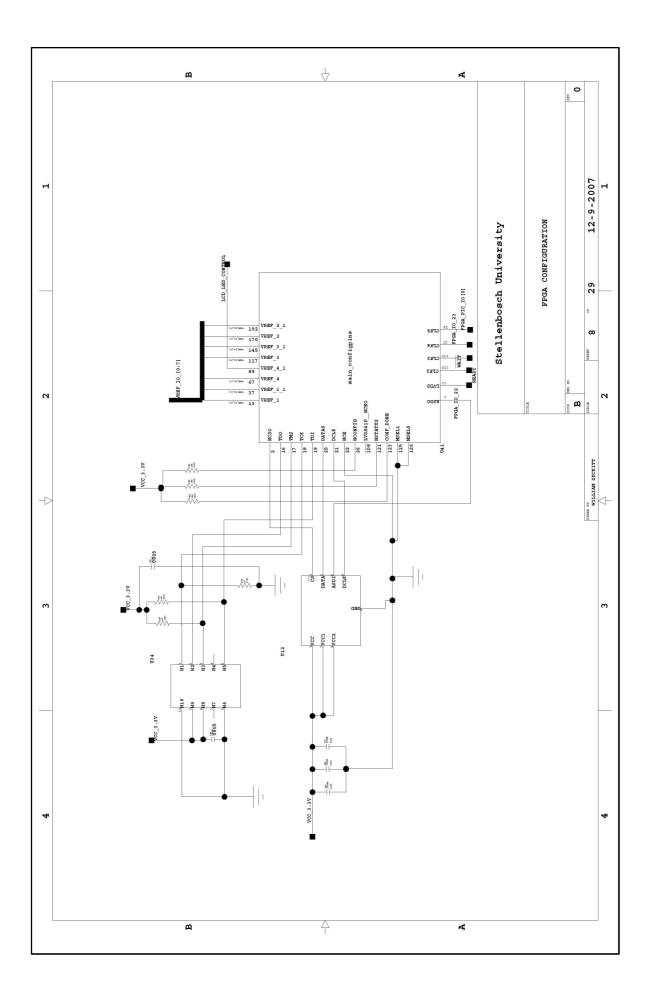

| 5 FPGA Sy<br>5.1 Alt<br>5.2 Tig<br>5.3 FPC<br>5.4 FPC<br>5.5 FPC<br>5.6 FPC<br>5.7 FPC                           | era Cyclone II FPGA<br>erSHARC to FPGA interface<br>GA Internal module design<br>GA Control Register<br>GA Logic Analyzer Interface<br>GA configuration                                                  | 31<br>31<br>31<br>36<br>39<br>39<br>40<br>41             |

| 5 FPGA Sy<br>5.1 Alta<br>5.2 Tig<br>5.3 FPC<br>5.4 FPC<br>5.5 FPC<br>5.6 FPC<br>5.7 FPC<br>5.8 Sur               | rstem<br>era Cyclone II FPGA<br>erSHARC to FPGA interface<br>GA Internal module design<br>GA Control Register<br>GA Control Register Interface<br>GA Logic Analyzer Interface<br>GA Power Requirements   | 31<br>31<br>36<br>36<br>39<br>39<br>40<br>41             |

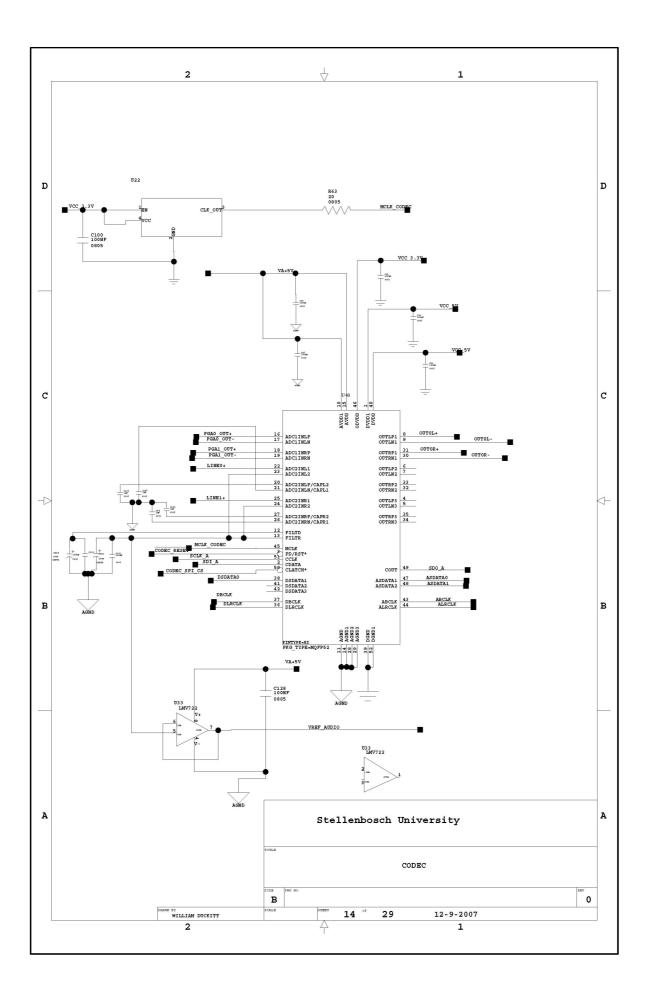

| 5 FPGA Sy<br>5.1 Altr<br>5.2 Tig<br>5.3 FPC<br>5.4 FPC<br>5.5 FPC<br>5.6 FPC<br>5.7 FPC<br>5.8 Sur<br>6 Audio Sy | era Cyclone II FPGA<br>erSHARC to FPGA interface<br>GA Internal module design<br>GA Control Register<br>GA Logic Analyzer Interface<br>GA configuration<br>GA Power Requirements<br>mmary and Conclusion | 31<br>31<br>31<br>36<br>39<br>39<br>40<br>41<br>41<br>42 |

|    | 6    | .2.1     | I2S interface                                 | 6              |

|----|------|----------|-----------------------------------------------|----------------|

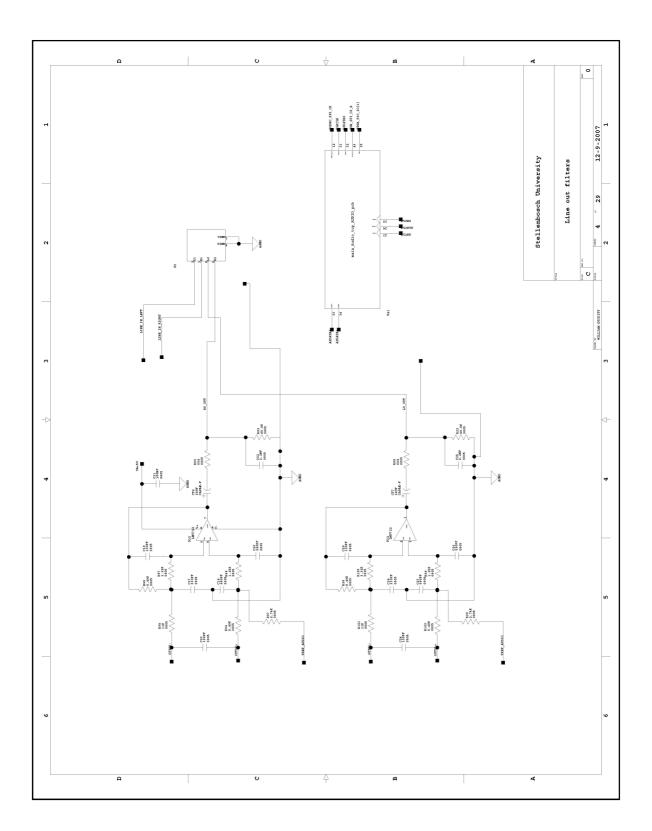

|    | 6    | .2.2     | Line out4                                     | 6              |

|    | 6    | .2.3     | Codec reference voltage4                      | 8              |

|    | 6    | .2.4     | Codec Power supply4                           | 8              |

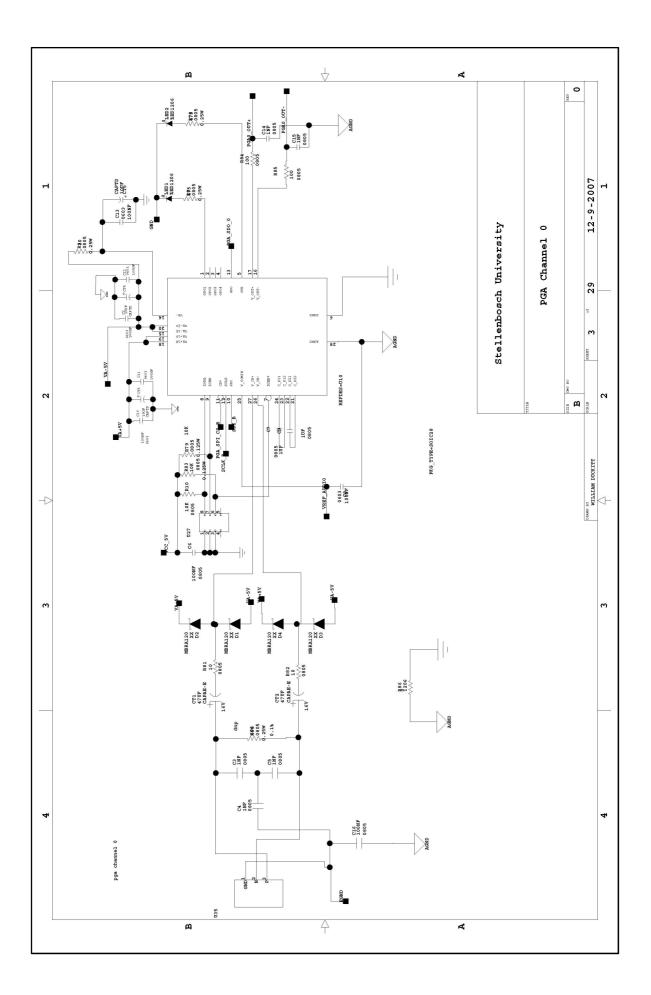

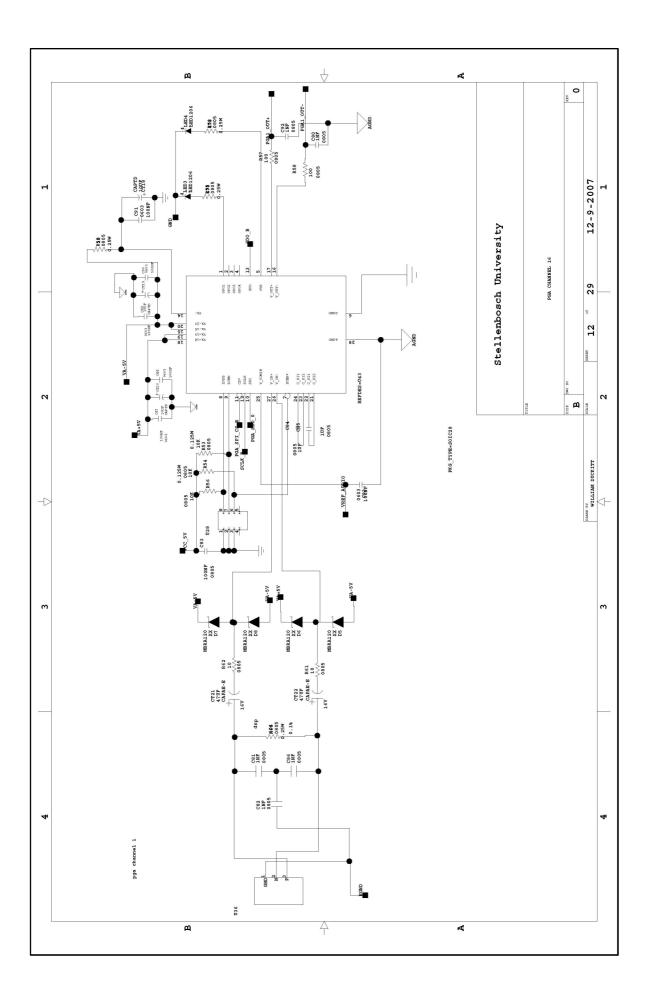

|    | 6.3  | Mic      | rophone Channels4                             | 9              |

|    | 6    | .3.1     | PGA SPI Interface5                            | 50             |

|    | 6.4  | FPG      | A Audio Module5                               | 52             |

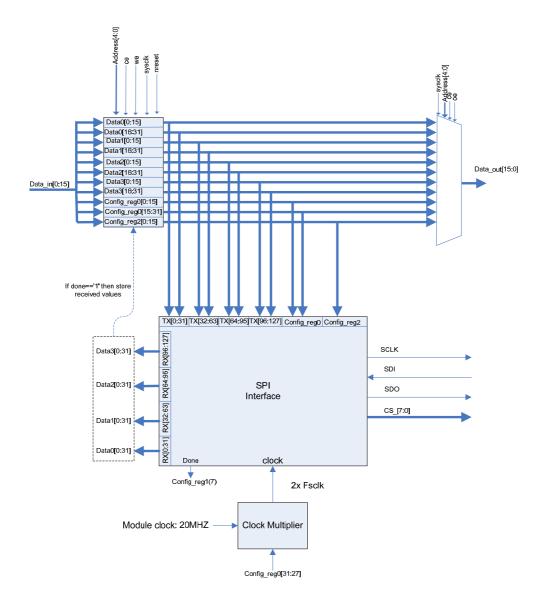

|    | 6.5  | Seri     | al Peripheral Interface5                      | 57             |

|    | 6.6  | The      | FPGA SPI module5                              | 8              |

|    | 6.7  | Sum      | nmary and Conclusion6                         | 52             |

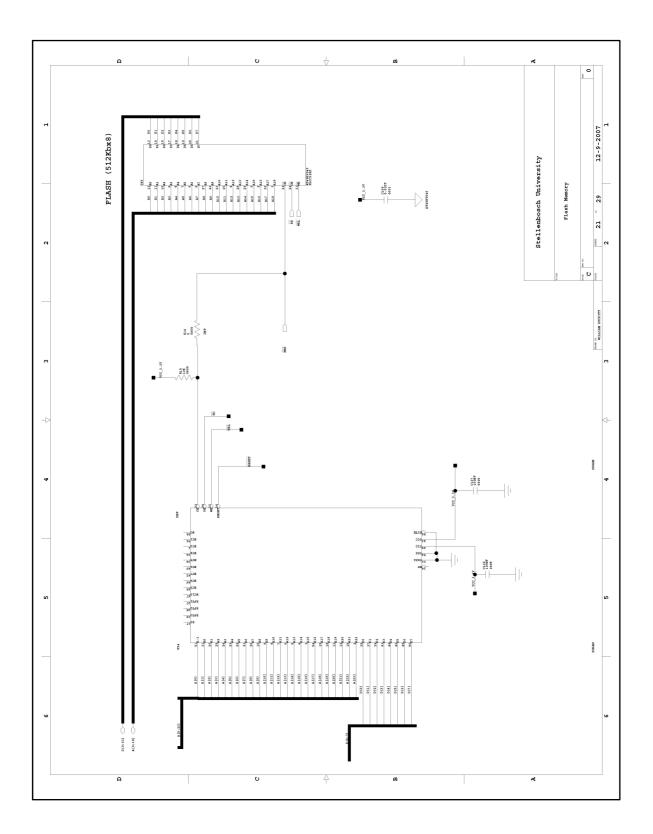

| 7  | St   | torage S | System                                        | 53             |

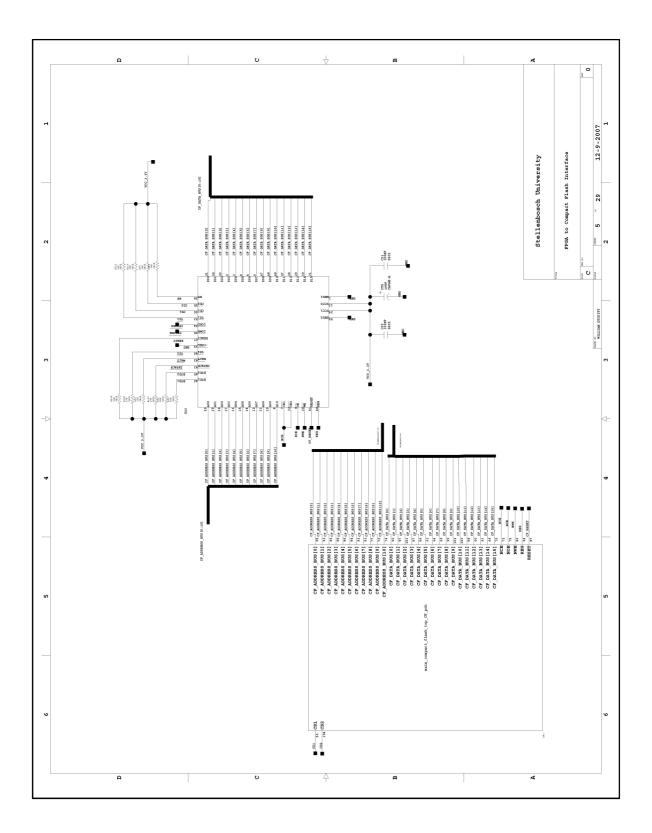

|    | 7.1  | Con      | npact Flash Storage Medium6                   | ;3             |

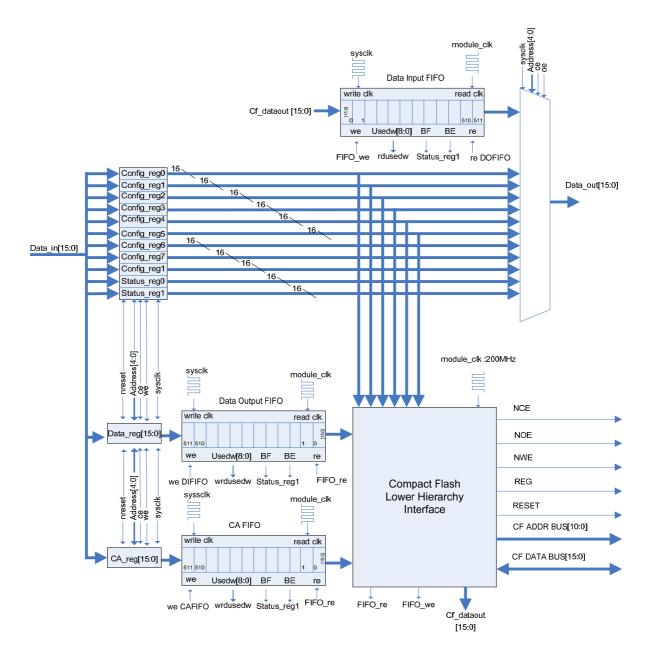

|    | 7.2  | FPG      | A Compact Flash Module6                       | 6              |

|    | 7.3  | Sum      | nmary and Conclusion7                         | ′5             |

| 8  | L    | CD and   | USB System                                    | '6             |

|    | 8.1  | FPG      | A Asynchronous Interface Module7              | '6             |

|    | 8.2  | Mic      | rochip PIC18F45508                            | 34             |

|    | 8.3  | LCD      | Screen                                        | 37             |

|    | 8.4  | Sum      | nmary and Conclusion8                         | 37             |

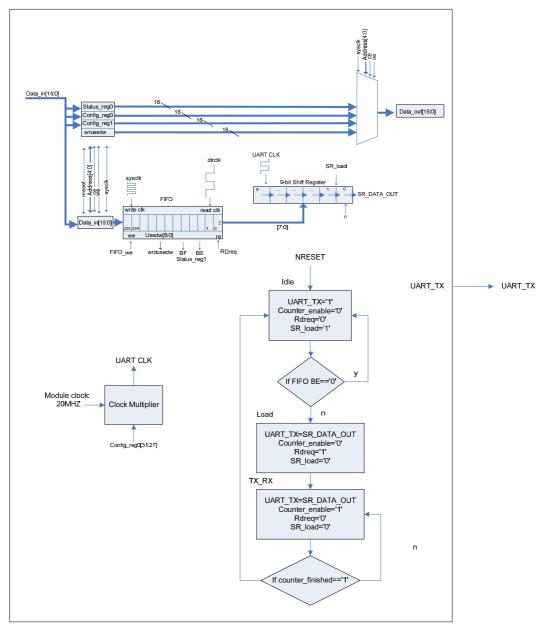

| 9  | U    | ART Int  | erface System8                                | 8              |

|    | 9.1  | FPG      | A UART module8                                | 8              |

|    | 9.2  | RS2      | 32 Line Driver9                               | 1              |

|    | 9.3  | Sum      | nmary and Conclusion9                         | 1              |

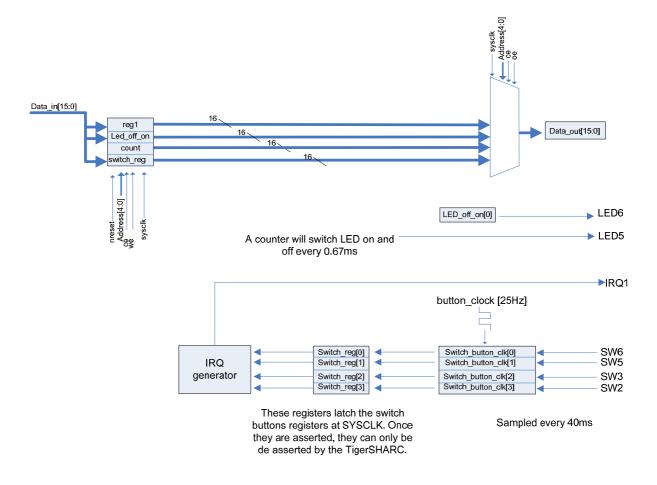

| 1( | )    | FPGA     | Test Registers, LEDs and Push-Buttons system9 | 12             |

|    | 10.1 | . FPG    | A Test Registers and Buttons Interface9       | 12             |

|    | 10.2 | 2 Sum    | nmary and Conclusion9                         | <del>)</del> 5 |

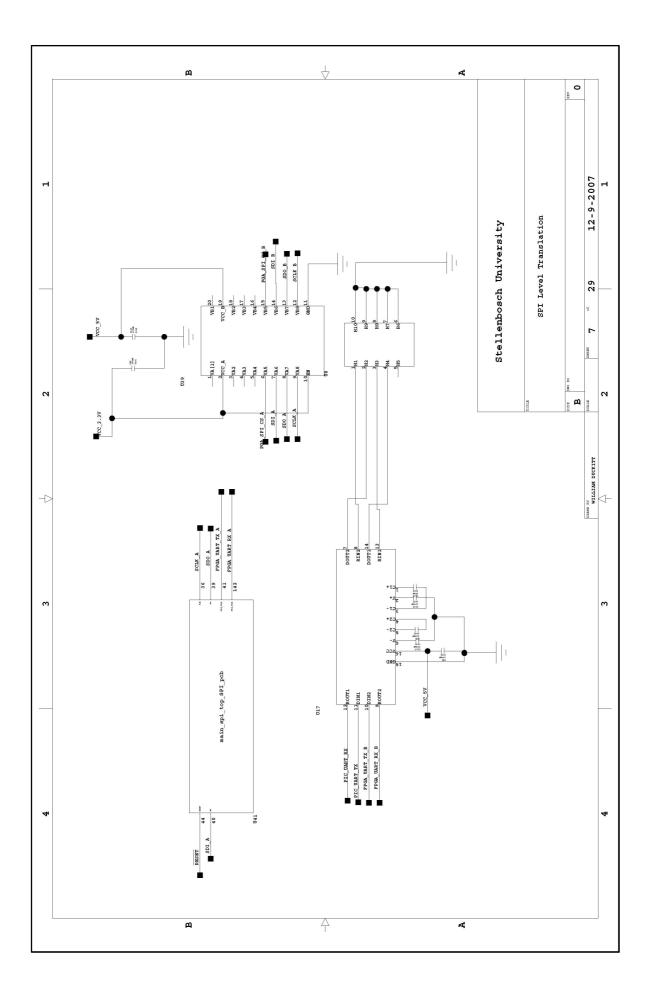

| 1  | l    | Logic L  | evel Translation9                             | 16             |

|    | 11.1 | . Max    | im MAX3002EUP9                                | 96             |

| 11.2 | Summary and Conclusion                    | 96  |

|------|-------------------------------------------|-----|

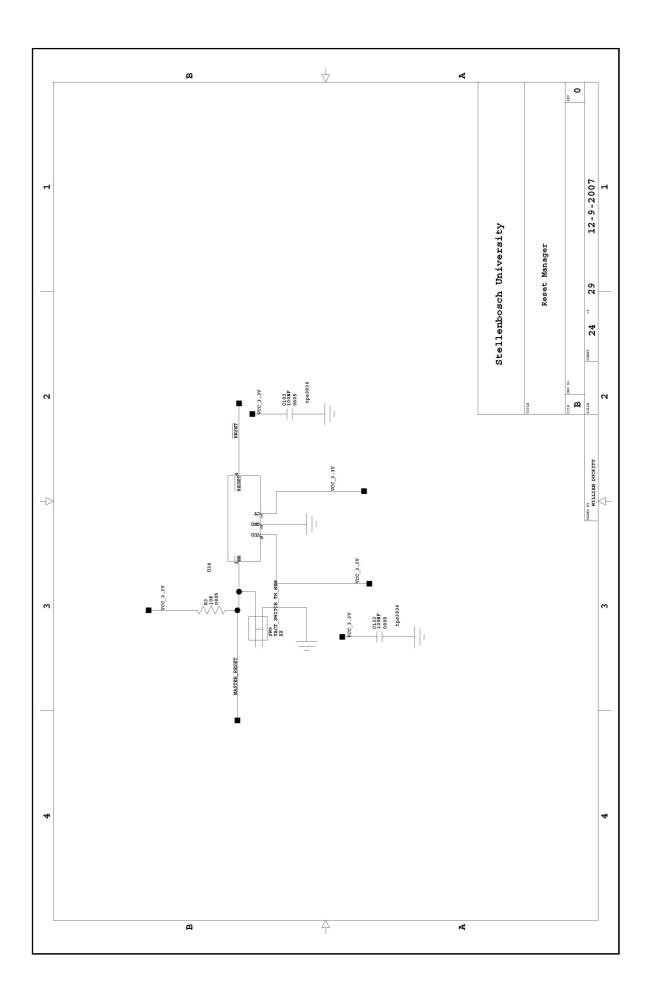

| 12   | System Reset                              | 97  |

| 12.1 | Texas Instruments TPS3836 Reset Manager   | 97  |

| 12.2 | Summary and Conclusion                    | 97  |

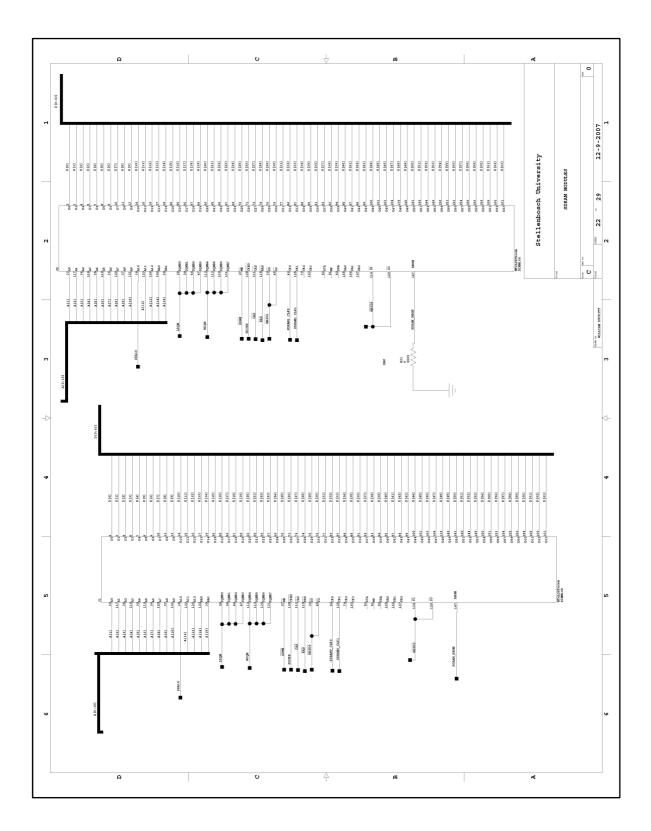

| 13   | SDRAM System                              | 98  |

| 13.1 | SDRAM Controller and Memory Modules       | 98  |

| 13.2 | SDRAM Controller Configuration Register   | 101 |

| 13.3 | Summary and Conclusion                    |     |

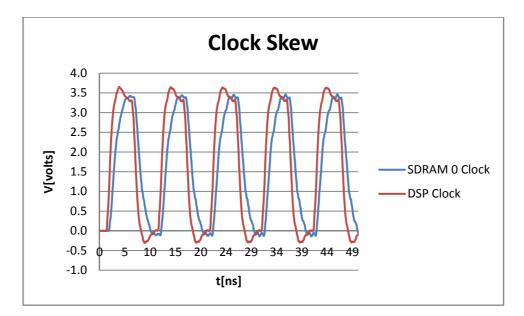

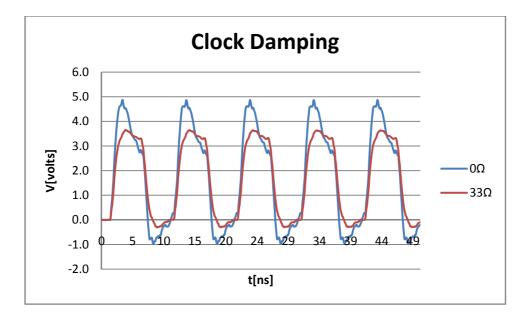

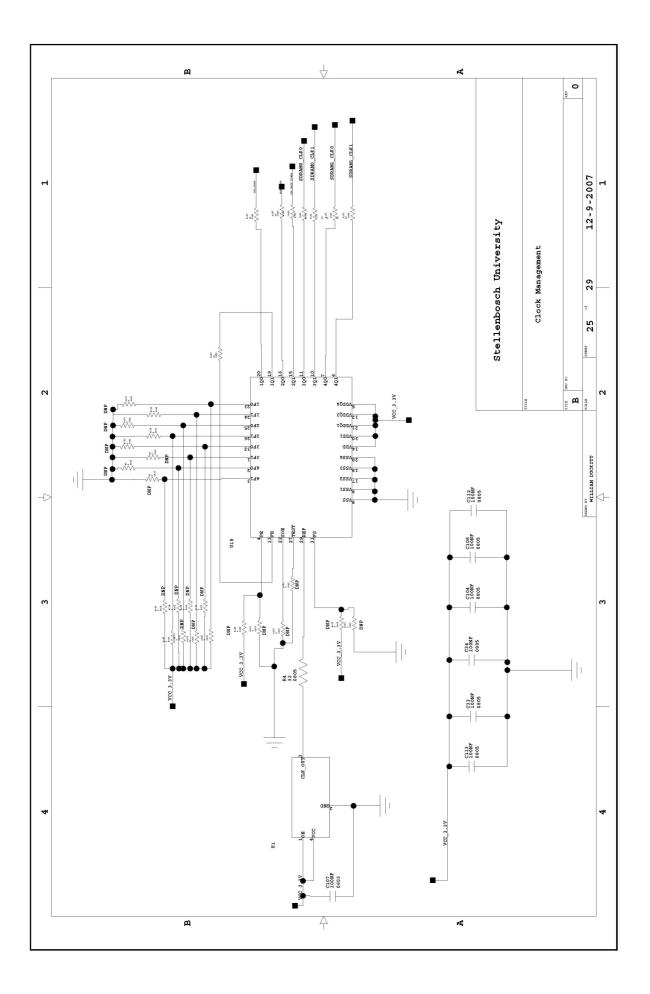

| 14   | Clock Distribution and Signal Integrity   |     |

| 14.1 | Clock Distribution                        |     |

| 14.2 | Signal Integrity                          |     |

| 14.3 | Summary and Conclusion                    | 112 |

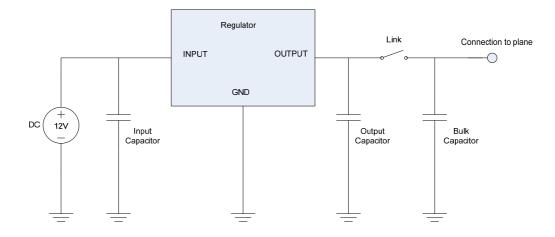

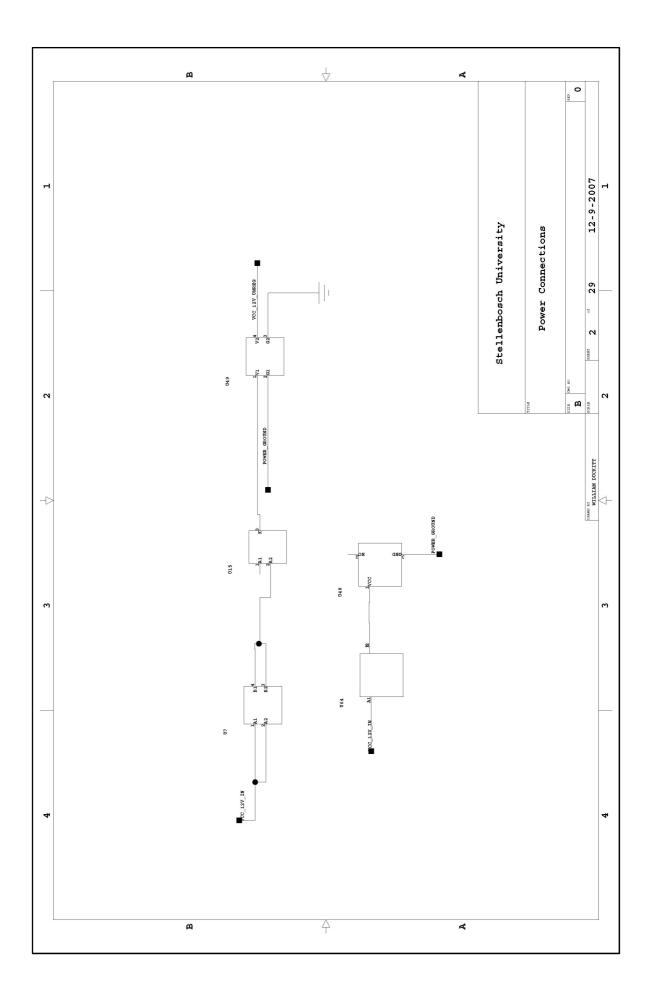

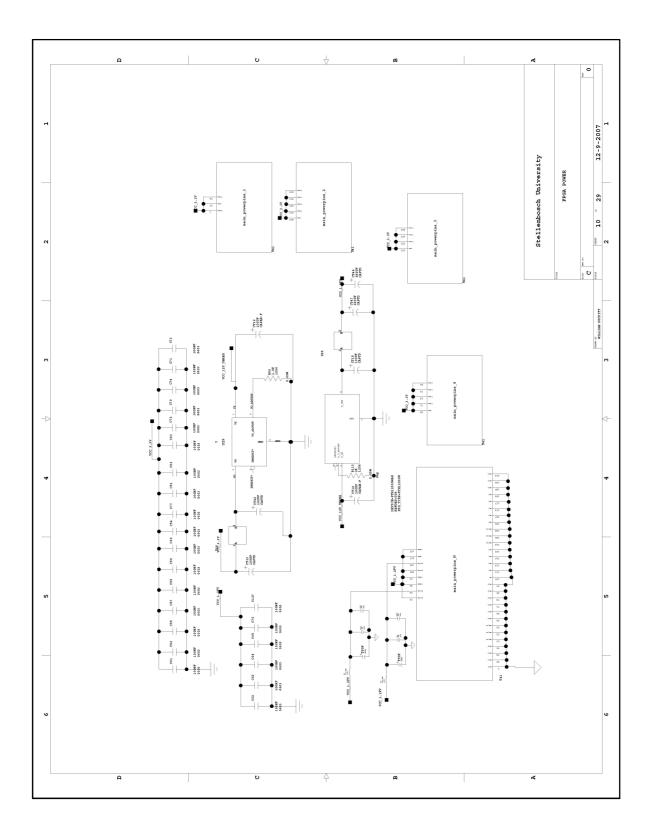

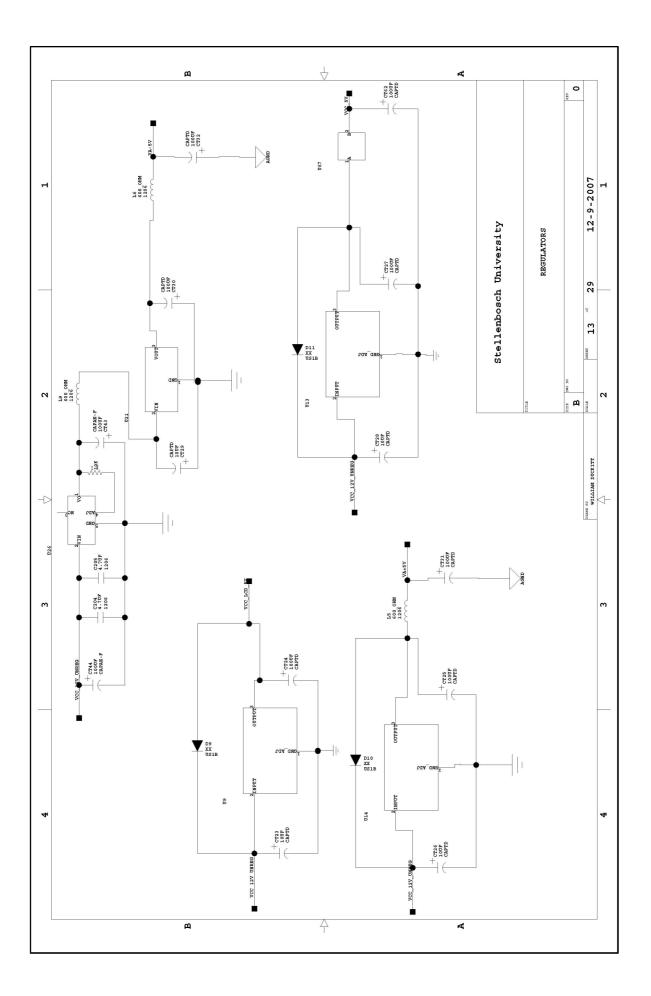

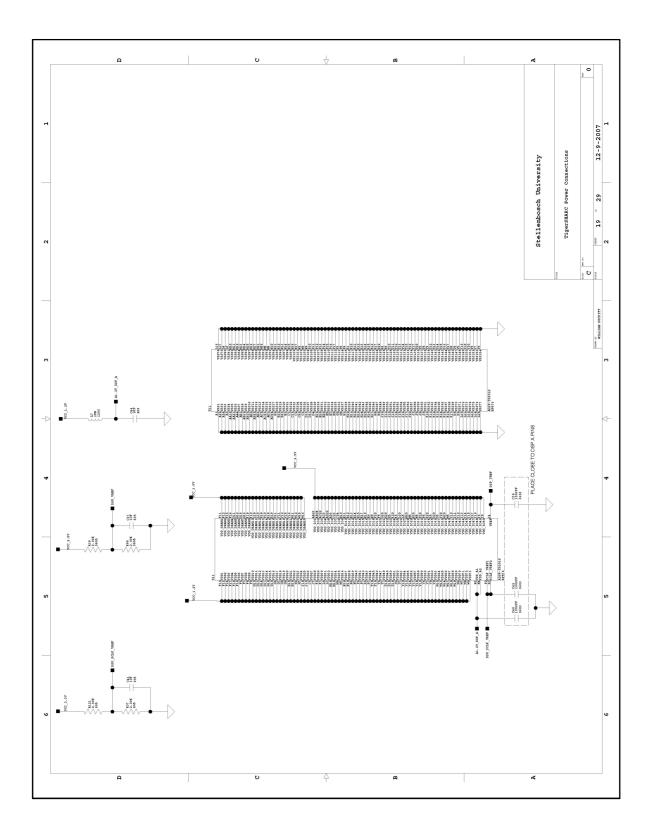

| 15   | Power Supply                              | 113 |

| 15.1 | Power Distribution Network                | 113 |

| 15.2 | Power Supply Protection and Filtering     | 124 |

| 15.3 | Power Supply Sequencing                   | 126 |

| 15.4 | Summary and Conclusion                    | 127 |

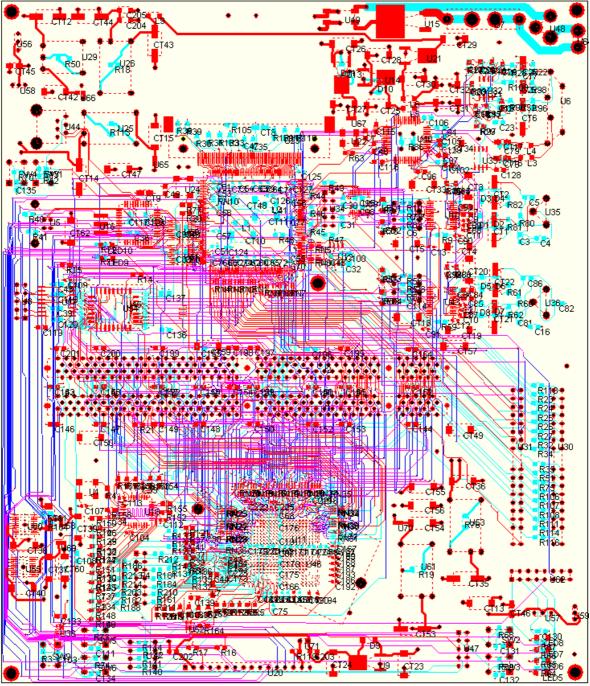

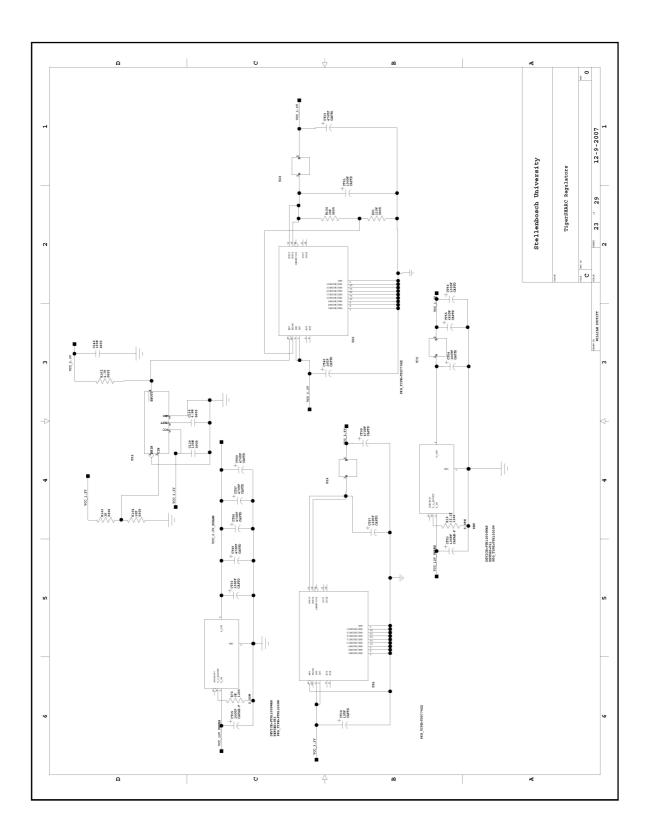

| 16   | Schematic Capture and PCB layout          | 128 |

| 16.1 | Schematic Capture                         | 128 |

| 16.2 | PCB Layout                                | 128 |

| 16.3 | Summary and Conclusion                    | 135 |

| 17   | Software                                  | 136 |

| 17.1 | Communication with the FPGA               | 136 |

| 17.2 | FPGA SPI module                           | 137 |

| 17.3 | Audio Driver                              | 139 |

| 17.4 | PIC18F4550 and LCD Asynchronous Interface | 140 |

| 17.5 | Push-Buttons                              | 141 |

| 17.6 | Compact Flash Interface and File System   | 142 |

| 17.7  | 7 TigerSHARC and SDRAM Initialization | 145 |

|-------|---------------------------------------|-----|

| 17.8  | 8 USB Keyboard and Mouse              | 147 |

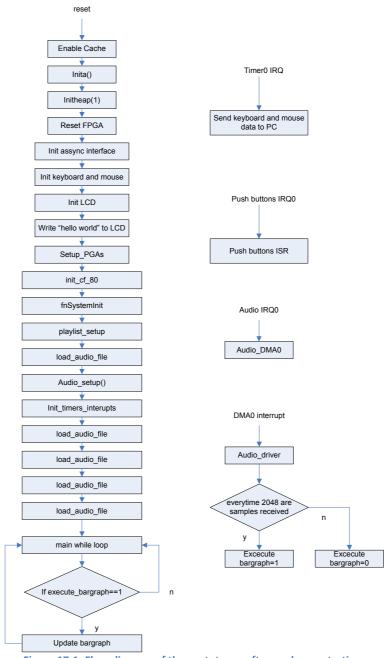

| 17.9  | 9 Prototype Demonstration Software    | 151 |

| 17.1  | 10 Summary and Conclusion             | 153 |

| 18    | Processor Performance                 | 154 |

| 18.1  | 1 Summary and Conclusion              | 156 |

| 19    | Conclusion                            | 157 |

| 20    | References                            | 158 |

| Apper | ndix A                                | 160 |

|       | Schematics                            | 160 |

| Apper | ndix B                                |     |

|       | PCB Layout                            |     |

| Apper | ndix C                                | 201 |

|       | Bill of Materials                     | 201 |

| Apper | ndix D                                | 206 |

|       | Extracts from Datasheets              |     |

# **List of Figures**

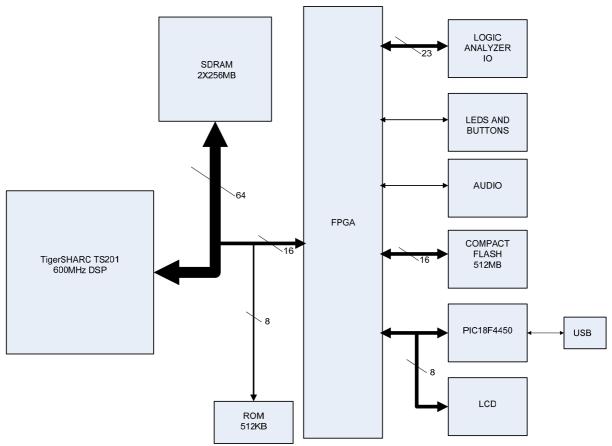

| Figure 3-1: High level block diagram of the system.                                          | 12 |

|----------------------------------------------------------------------------------------------|----|

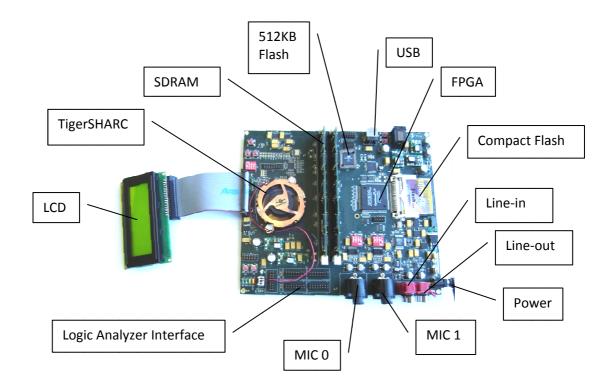

| Figure 3-2: A photograph of the final prototype illustrating the different system components | 13 |

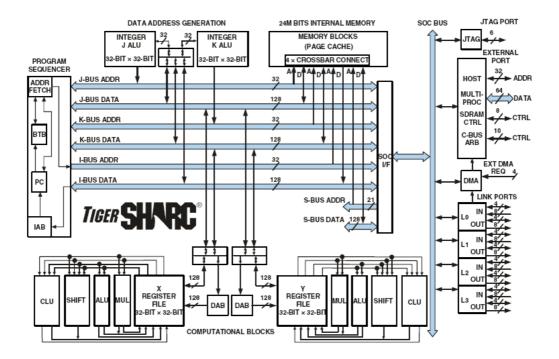

| Figure 4-1: Functional Block Diagram of the TigerSHARC (reproduced from datasheet (3)).      | 15 |

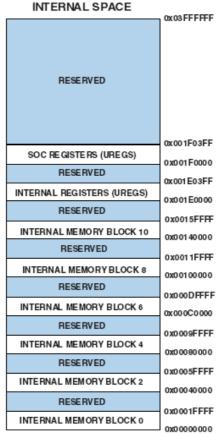

| Figure 4-2: TigerSHARC internal memory space, showing blocks M0 to M10 (reproduced fro       | m  |

| datasheet (3))                                                                               | 16 |

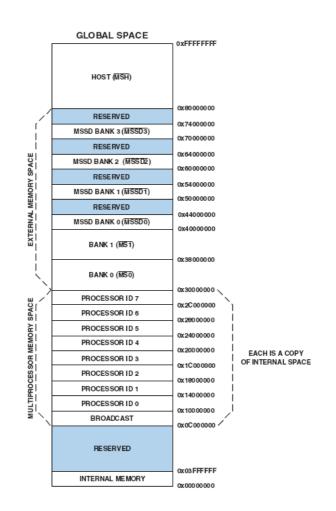

| Figure 4-3: TigerSHARC unified memory map (reproduced from datasheet (3))                    | 18 |

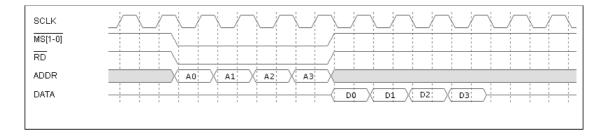

| Figure 4-4: Pipelined protocol: read cycle, with a read latency of 4                         | 20 |

| Figure 4-5: Pipelined protocol: write cycle, with a write latency of 1                       | 21 |

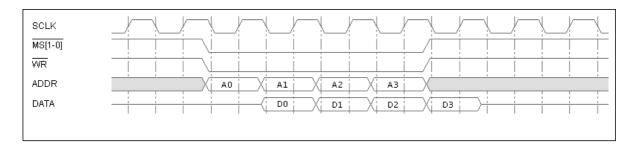

| Figure 4-6: Slow device protocol: read cycle                                                 | 21 |

| Figure 4-7: Slow device protocol: write cycle                                                | 21 |

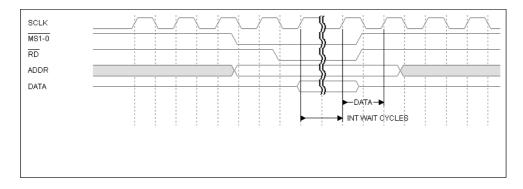

| Figure 4-8: Slow device protocol: read cycle with external wait cycles                       | 22 |

| Figure 4-9: Slow device protocol: write cycle with external wait cycles                      | 22 |

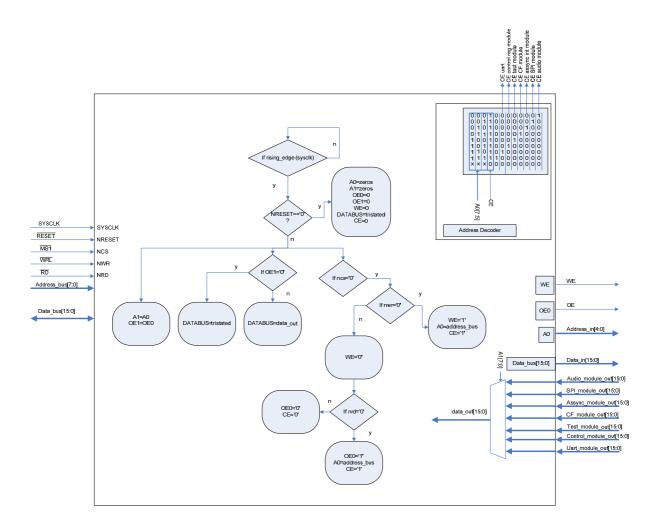

| Figure 5-1: A Bock diagram of the TigerSHARC to FPGA interface                               | 32 |

| Figure 5-2: The TigerSHARC to FPGA pipelined protocol interface module                       | 34 |

| Figure 5-3: The general design of the top level entities of the FPGA modules                 | 36 |

| Figure 5-4: Read and write access to internal FPGA registers.                                | 37 |

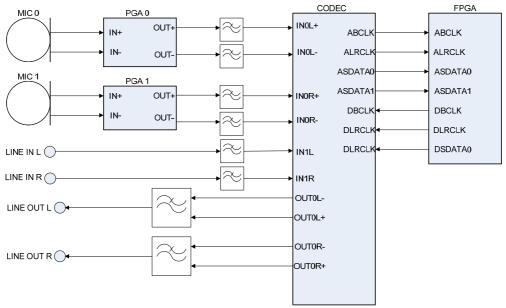

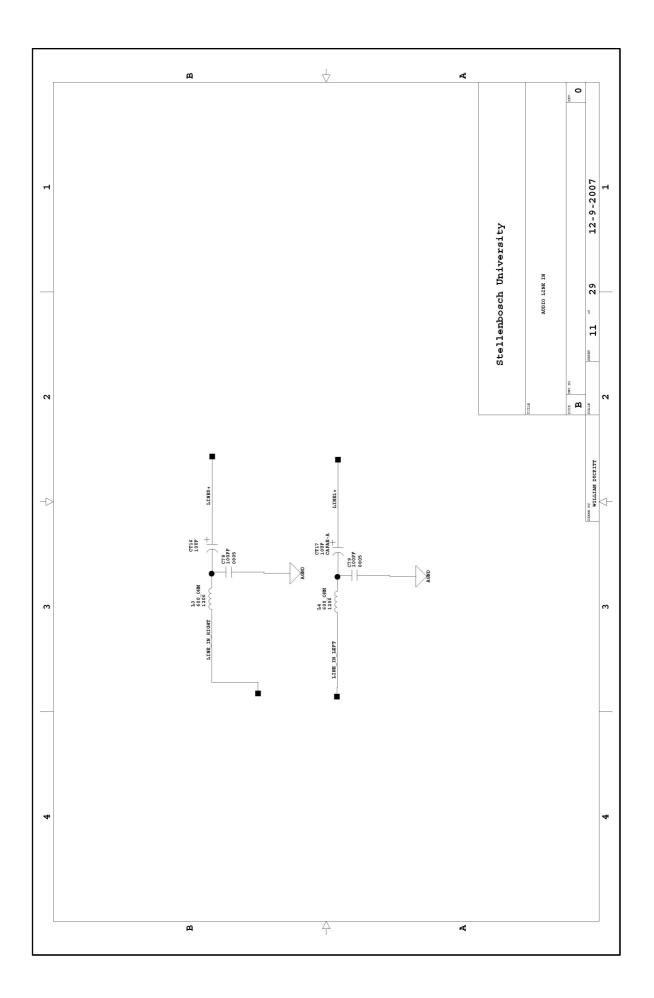

| Figure 6-1: A high level block diagram of the audio system                                   | 12 |

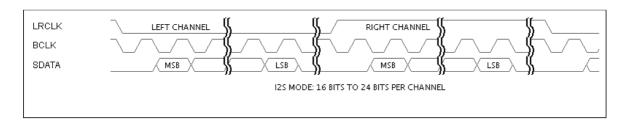

| Figure 6-2: The I2S protocol                                                                 | 16 |

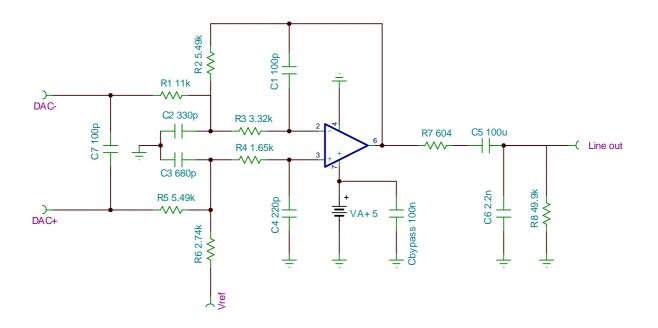

| Figure 6-3: 3rd order single opamp low pass filter circuit.                                  | 17 |

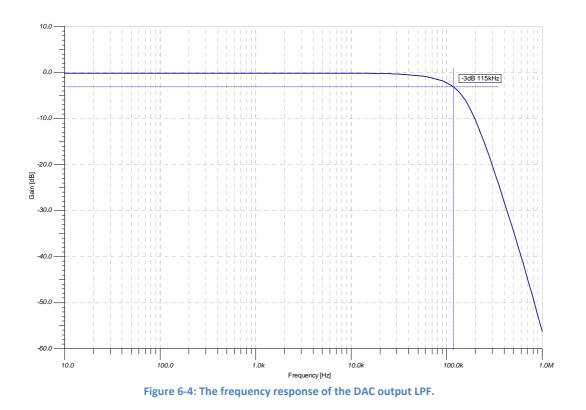

| Figure 6-4: The frequency response of the DAC output LPF                                     | 17 |

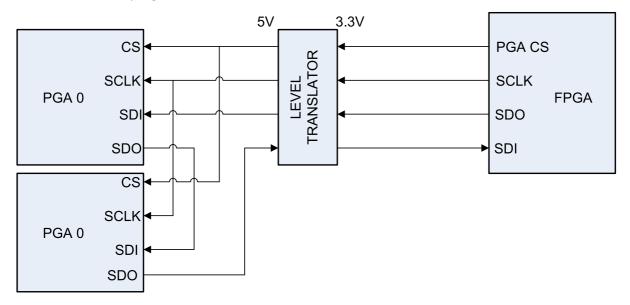

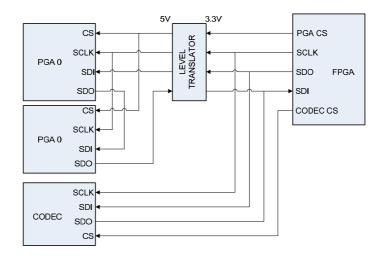

| Figure 6-5: Daisy chain arrangement of the PGAs.                                             | 51 |

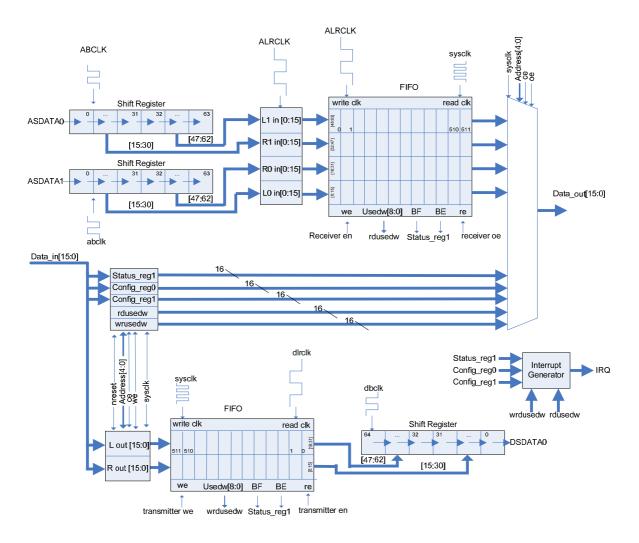

| Figure 6-6: The FPGA audio module                                                            | 52 |

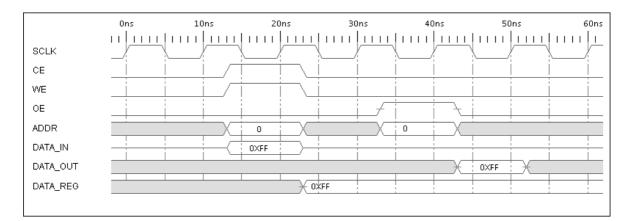

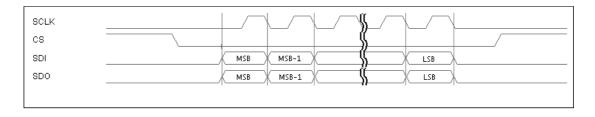

| Figure 6-7: A timing diagram of the SPI protocol                                             | 57 |

| Figure 6-8: A high level block diagram of the SPI system.                                    | 57 |

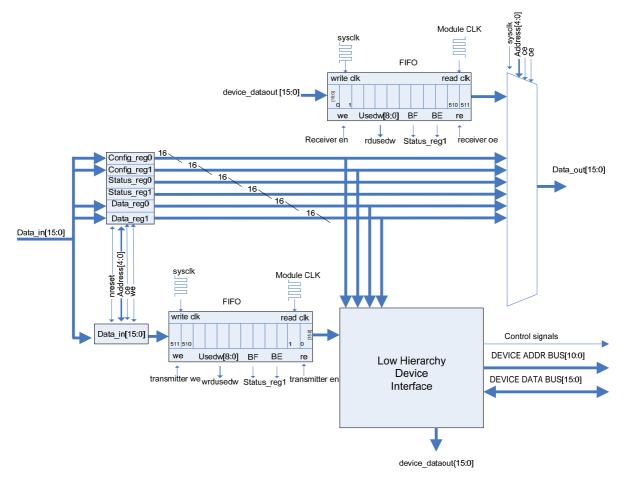

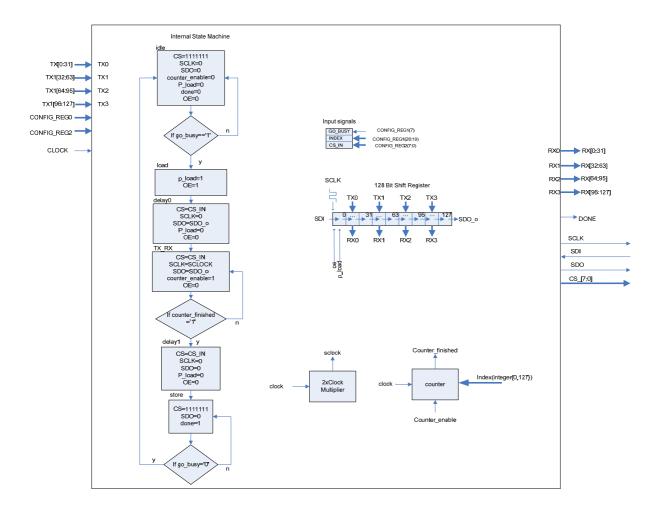

| Figure 6-9: A high level block diagram of the SPI top level VHDL module                      | 59 |

| Figure 6-10: A high level block diagram of the lower hierarchy SPI interface module          | 50 |

| Figure 7-1: Compact Flash top level entity.                                                  | 57 |

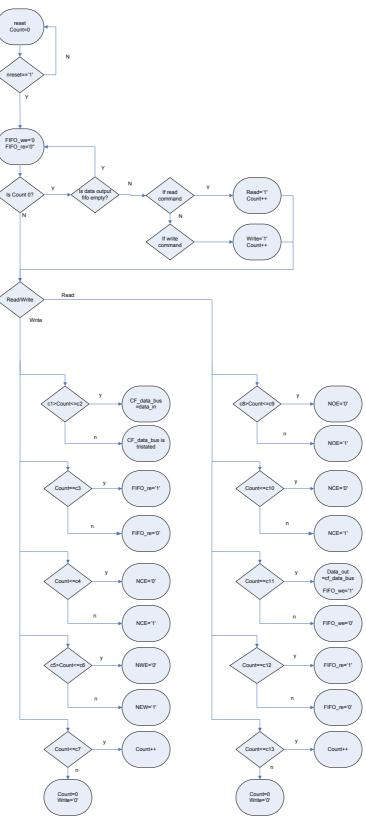

| Figure 7-2: Compact Flash interface flow diagram.                                            | 73 |

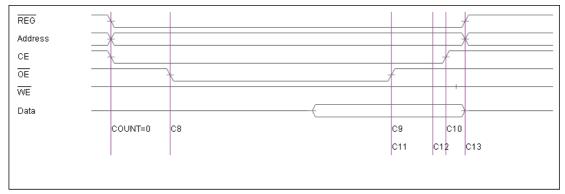

| Figure 7-3: Compact Flash read cycle                                                         | 74 |

| Figure 7-4: Compact Flash write cycle.                                                       | 74 |

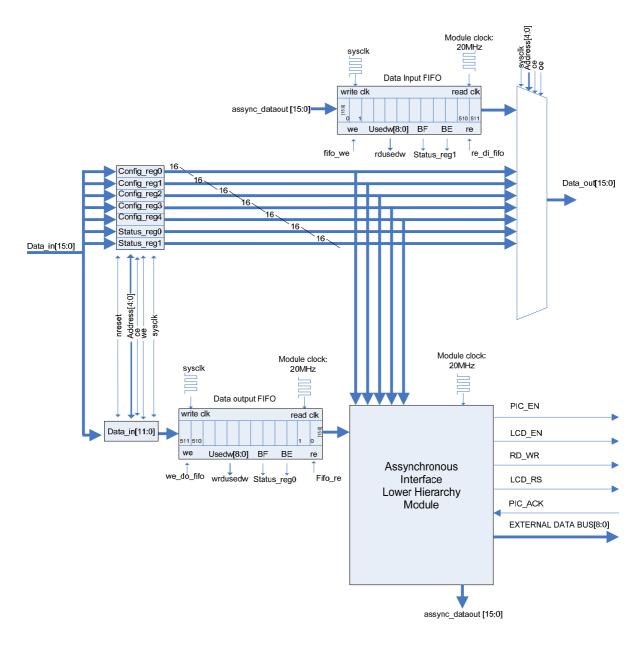

| Figure 8-1: A block diagram of the asynchronous interface top level entity.                  | 77 |

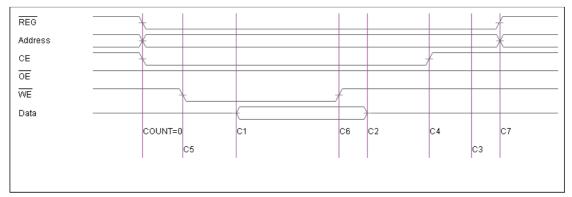

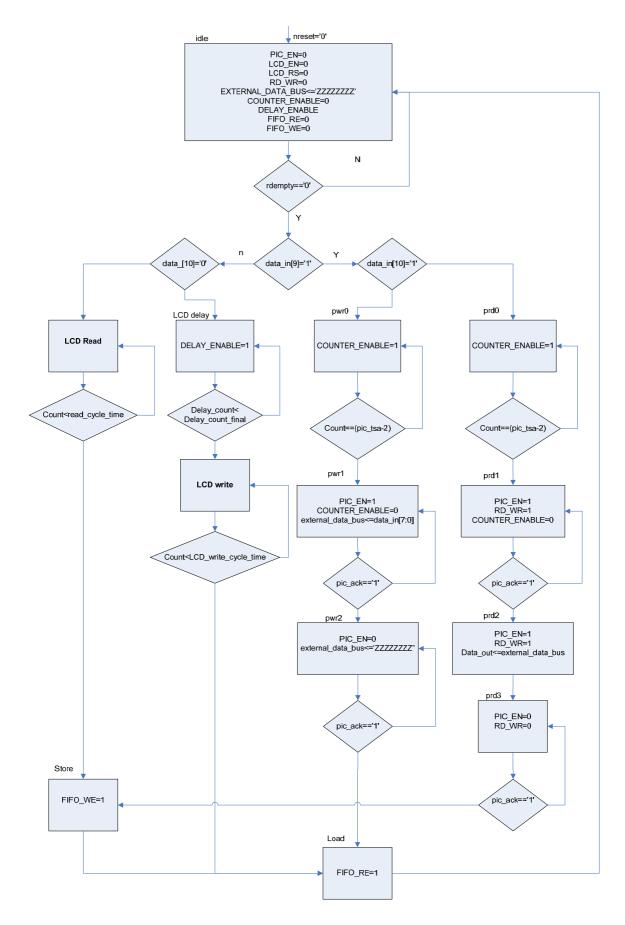

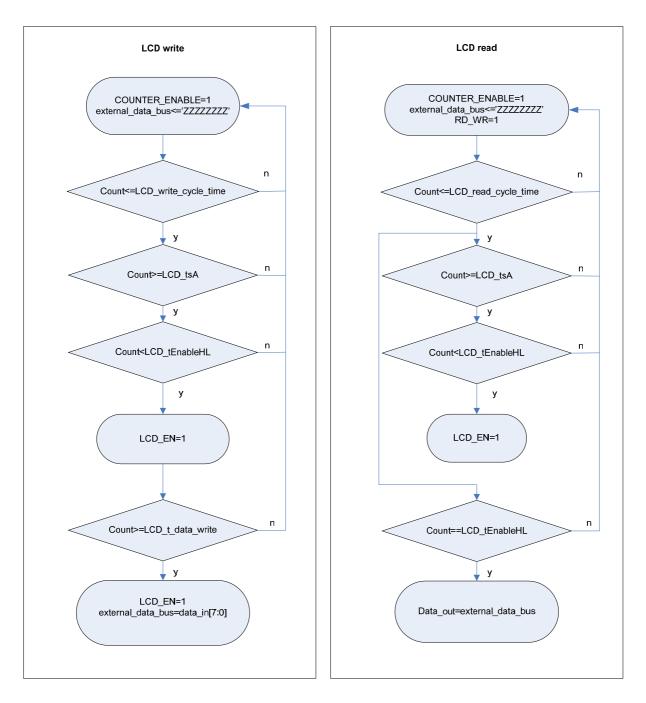

| Figure 8-2: Asynchronous interface state machine.                                      | 78  |

|----------------------------------------------------------------------------------------|-----|

| Figure 8-3: Asynchronous interface LCD write and LCD read state.                       | 79  |

| Figure 9-1: The FPGA UART module.                                                      | 89  |

| Figure 10-1: The test registers and buttons Interface top level entity.                | 92  |

| Figure 14-1: Clock skew (600ps) of DSP clock (leading) and SDRAM clocks (lagging)      | 105 |

| Figure 14-2: Clock damping with and without a series source resistor.                  | 106 |

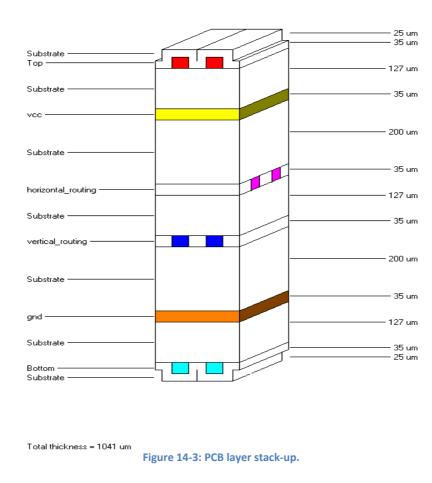

| Figure 14-3: PCB layer stack-up.                                                       | 108 |

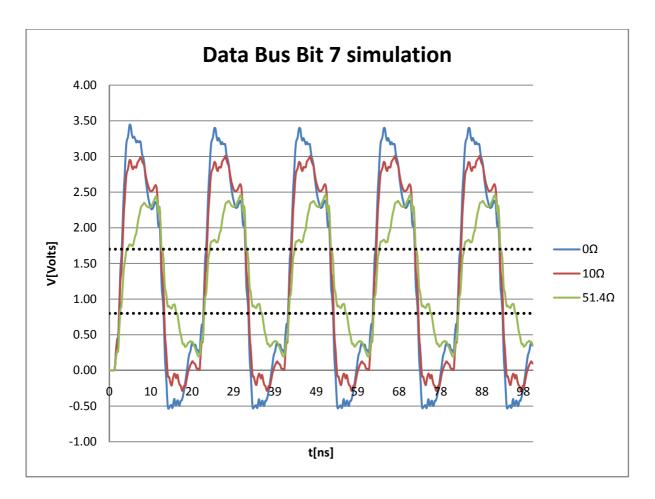

| Figure 14-4: Simulation of bit 7 of the data bus for three choices of series resistors | 110 |

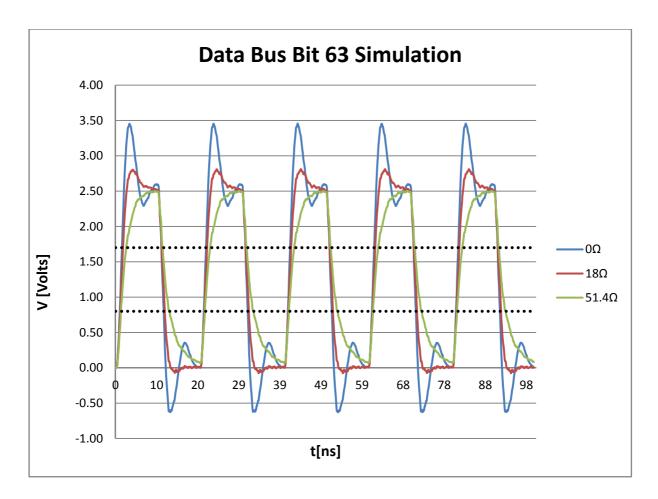

| Figure 14-5: Simulation of Data bus bit 63.                                            | 111 |

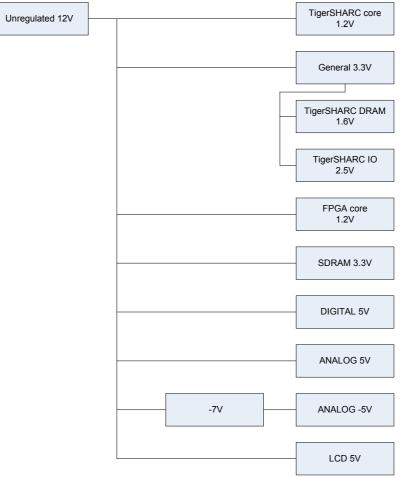

| Figure 15-1: Power distribution network                                                | 114 |

| Figure 15-2: Regulator connection scheme.                                              | 115 |

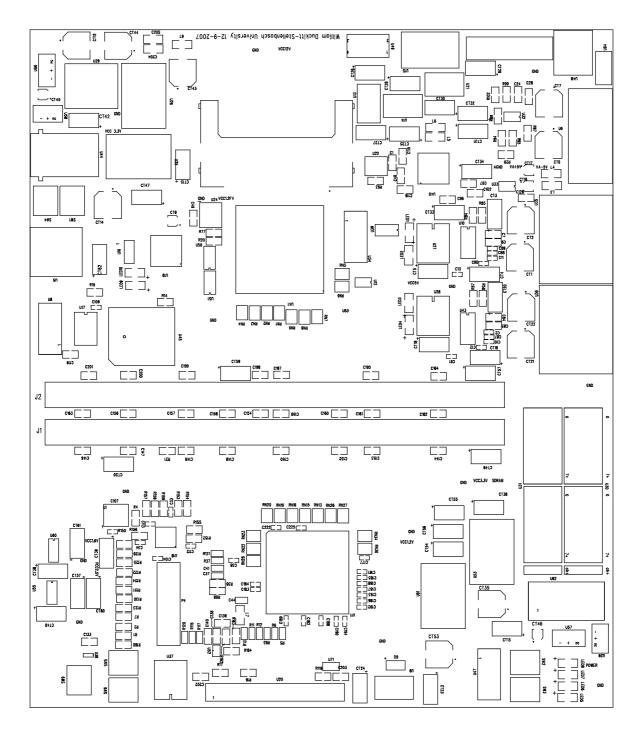

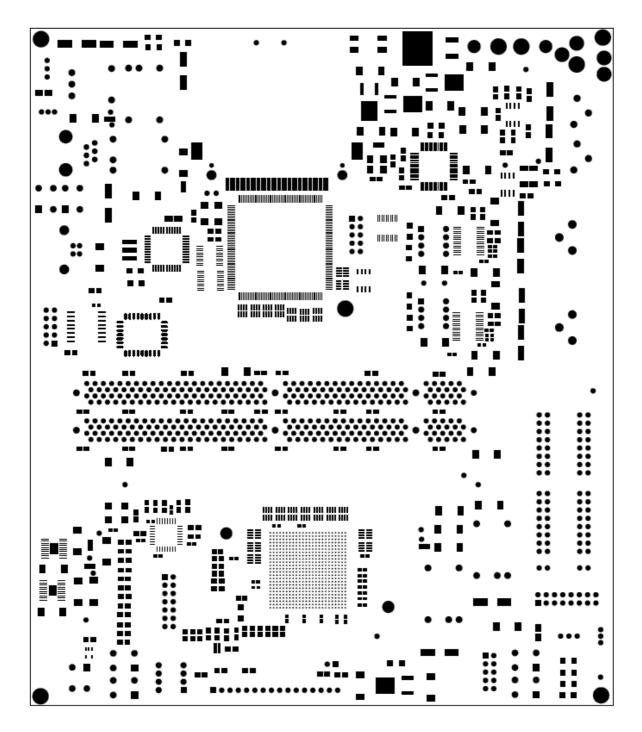

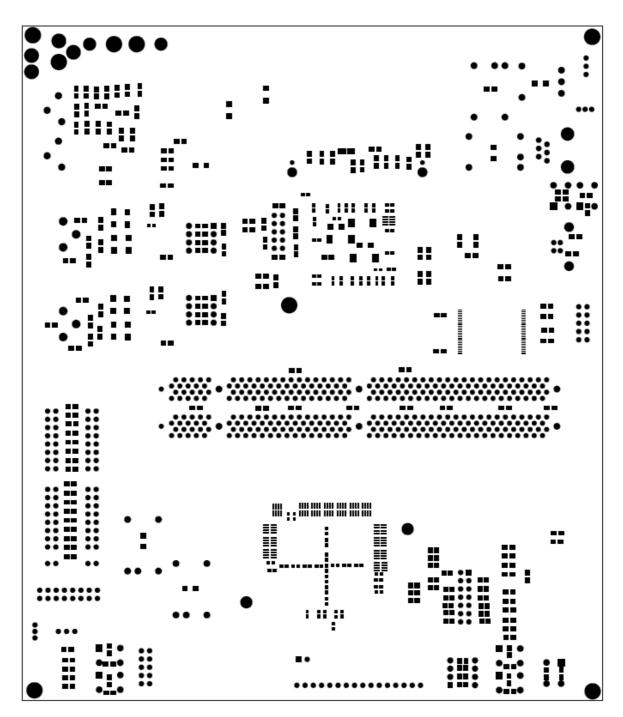

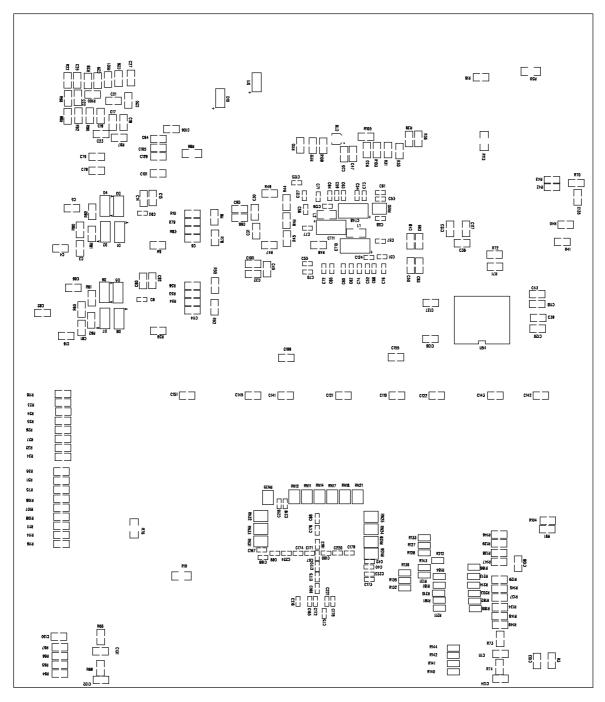

| Figure 16-1: The PCB component arrangements                                            | 130 |

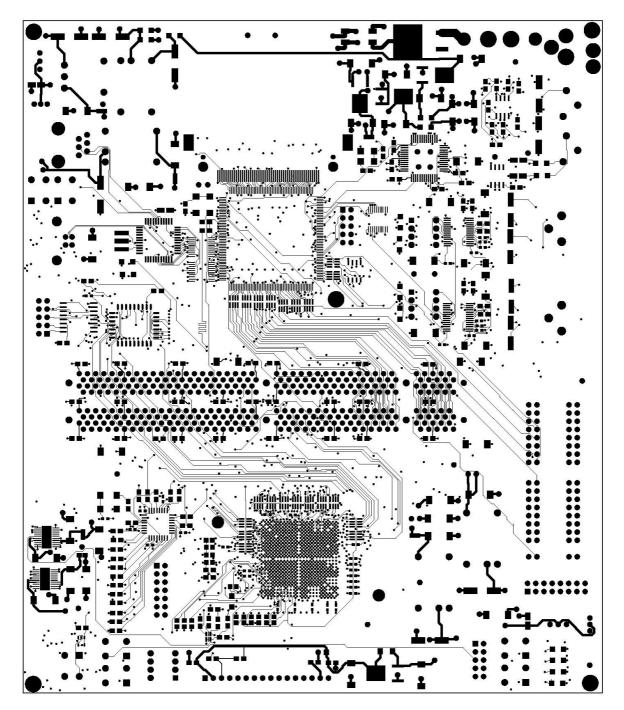

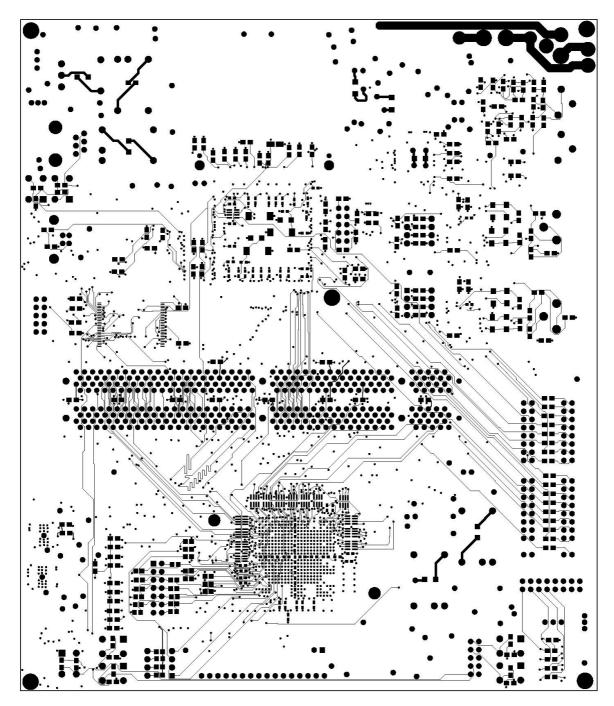

| Figure 16-2: The four signal layers superimposed to illustrate the overall PCB design  | 132 |

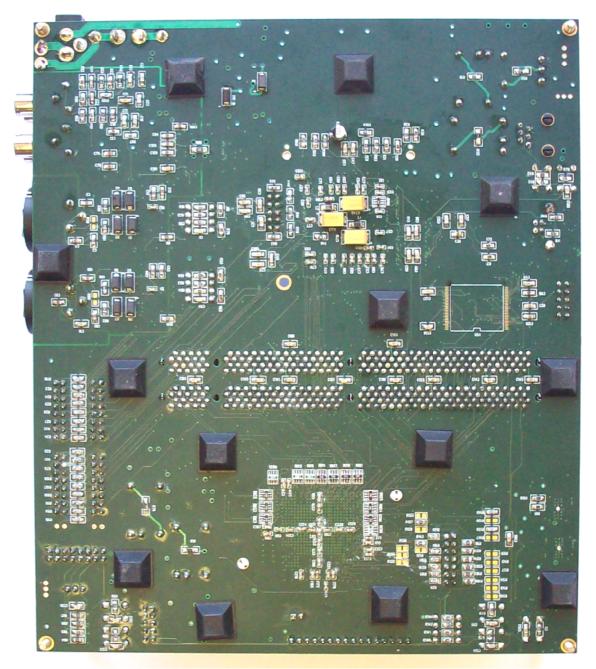

| Figure 16-3: The final prototype                                                       | 133 |

| Figure 16-4: The bottom view of the final prototype.                                   | 134 |

| Figure 17-1: Flow diagram of the prototype software demonstration                      | 151 |

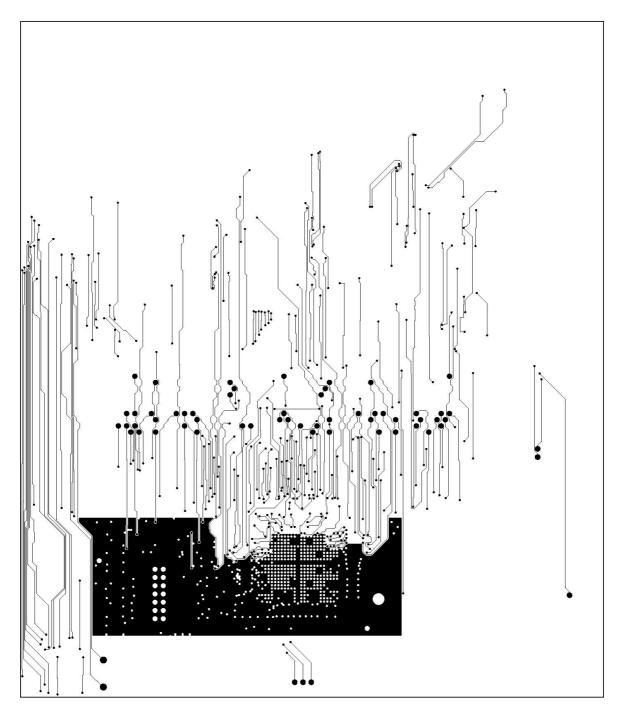

| Figure B-1: Top layer silk screen.                                                     | 191 |

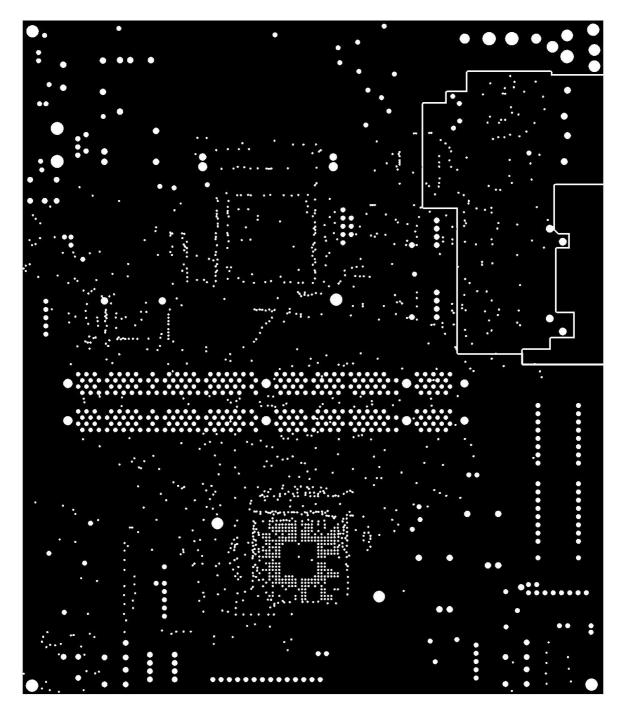

| Figure B-2: Solder mask top                                                            | 192 |

| Figure B-3: Top layer routing                                                          | 193 |

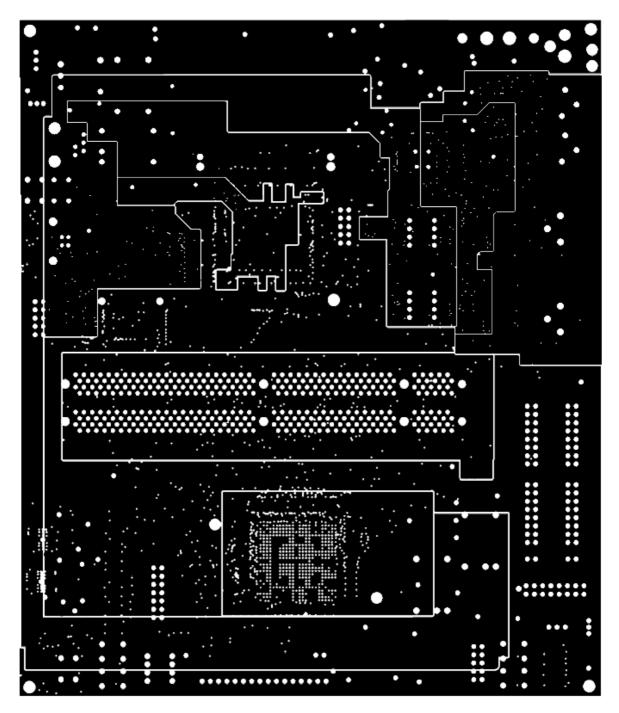

| Figure B-4:Power layer                                                                 | 194 |

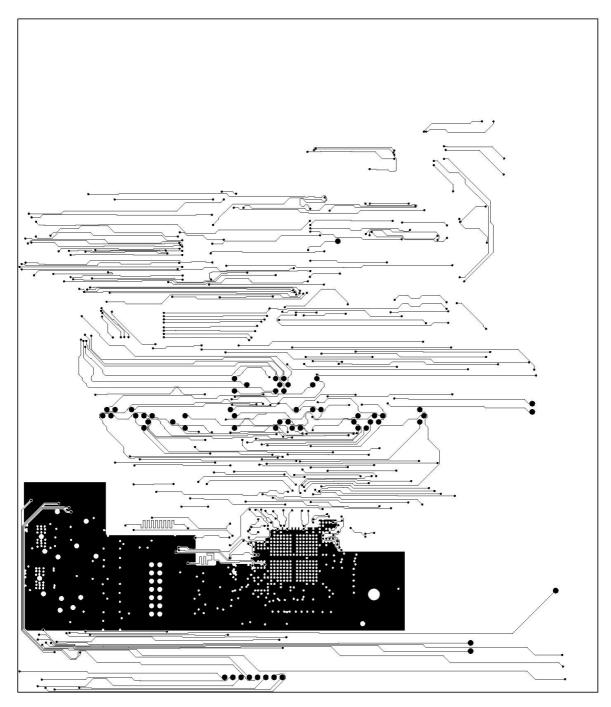

| Figure B-5: Horizontal routing layer                                                   | 195 |

| Figure B-6: Vertical routing layer.                                                    | 196 |

| Figure B-7: Ground layer                                                               | 197 |

| Figure B-8: Bottom routing layer (mirrored).                                           | 198 |

| Figure B-9: Bottom solder mask (mirrored)                                              | 199 |

| Figure B-10: Bottom silk screen (mirrored).                                            |     |

## **List of Tables**

| Table 2-1: Comparison of processors.                                                   | 5   |

|----------------------------------------------------------------------------------------|-----|

| Table 2-2: Comparison of processor evaluation boards.                                  | 6   |

| Table 4-1: Chip select address decoding                                                | 19  |

| Table 4-2: Configurable pins connected to switch U37.                                  | 26  |

| Table 5-1: FPGA Control Registers                                                      |     |

| Table 6-1: Codec's 16-bit SPI word format                                              | 45  |

| Table 6-2: PGA Configurable pins connected to switch U28                               | 50  |

| Table 6-3: PGA2500 16-bit SPI word format                                              | 51  |

| Table 6-4: Audio module memory addressable registers.                                  | 54  |

| Table 6-5: SPI module memory addressable registers                                     | 60  |

| Table 7-1 Compact Flash module memory addressable registers                            | 68  |

| Table 7-2: The Compact Flash count values used for 80ns read and write cycles.         | 74  |

| Table 8-1: Asynchronous interface memory addressable registers                         | 80  |

| Table 9-1: UART memory addressable registers                                           |     |

| Table 10-1: Test registers and push-button interface memory addressable registers.     | 93  |

| Table: 13-1 SDRAM controller and SDRAM module capabilities.                            | 99  |

| Table 14-1: System timing budget                                                       | 106 |

| Table 15-1: Power requirement of various elements of the final prototype               | 125 |

| Table 17-1: HID Mouse Report Descriptor                                                | 147 |

| Table 17-2: HID Keyboard Descriptor.                                                   | 147 |

| Table 17-3: The commands that are decoded by the PIC18F4550 assync_interface() funtion | 149 |

| Table 18-1: Benchmark of the processors                                                | 155 |

## Abbreviations

| ACK    | Acknowledge                               |

|--------|-------------------------------------------|

| ADC    | Analog-to-Digital Converters              |

| ALU    | Arrhythmic Logic Unit                     |

| AS     | Active Serial                             |

| ASM    | Algorithmic State Machine                 |

| BCLK   | Bit Clock                                 |

| BGA    | Ball Grid Array                           |

| CAFIFO | Command Address FIFO                      |

| CAS    | Column Address Strobe                     |

| CE     | Chip Enable                               |

| CF     | Compact Flash                             |

| CLU    | Communications Logic Unit                 |

| CMOS   | Complementary Metal Oxide Semiconductor   |

| CPU    | Central Processing Unit                   |

| DAC    | Digital-to-Analog Converters              |

| DC     | Direct Current                            |

| DIFIFO | Data Input FIFO                           |

| DIMM   | Dual Inline Memory Module                 |

| DMA    | Direct Memory Access                      |

| DRAM   | Dynamic Random Access Memory              |

| DSP    | Digital Signal Processor                  |

| EMIF   | External Memory Interface                 |

| FIFO   | First In First Out Buffer                 |

| FPGA   | Field Programmable Gate Array             |

| GB     | Giga-Byte                                 |

| GFLOPS | Giga-Floating Point Operations Per Second |

| GPO    | General Purpose Output                    |

| 12C    | Inter-Integrated Component Communication  |

| IFIFO  | Input First In First Out Buffer           |

| 10     | Input Output                              |

| IRQ    | Interrupt Request                         |

| JTAG   | Joint Test Access Group                   |

| KB     | Kilobyte                                  |

| LCD    | Liquid Crystal Display                    |

| LDF    | Linker Descriptive File                   |

| LED    | Light Emitting Diode                      |

| LRCLK  | Left-Right Channel Clock                  |

| LSB    | Least Significant Bit                     |

| MB     | Mega-Byte                                 |

| MHz    | Mega Hertz                                |

| MIPS   | Million Instructions Per Second           |

| MMU0   | Memory Management Unit                    |

| MS0    | Memory Space 0                                  |

|--------|-------------------------------------------------|

| MS1    | Memory Space 1                                  |

| MSB    | Most Significant Bit                            |

| MSSD0  | Memory Space SDRAM 0                            |

| MSSD1  | Memory Space SDRAM 1                            |

| MSSD2  | Memory Space SDRAM 2                            |

| MSSD3  | Memory Space SDRAM 3                            |

| nF     | Nano-Farad                                      |

| ns     | Nano-Seconds                                    |

| OE     | Output Enable                                   |

| OFIFO  | Output First In First Out Buffer                |

| OVR    | Over Voltage Register                           |

| РСВ    | Printed Circuit Board                           |

| PGA    | Programmable Gain Amplifier                     |

| PLD    | Programmable Logic Device                       |

| PLL    | Phase Locked Loop                               |

| PRC    | Pre-charge                                      |

| PS     | Passive Serial                                  |

| PWM    | Pulse Width Modulation                          |

| RAM    | Ram Access Memory                               |

| RAS    | Row Address Strobe                              |

| SCLK   | System Clock                                    |

| SDATA  | Serial Audio Data                               |

| SDI    | Serial Data In                                  |

| SDO    | Serial Data Out                                 |

| SDRAM  | Synchronous Dynamic Random Access Memory        |

| SIMD   | Single Instruction Multiple Data                |

| SPDIF  | Sony/ Phillips Digital Interface                |

| SPI    | Serial Peripheral Interface                     |

| SPORTS | Serial Ports                                    |

| SRAM   | Static Random Access Memory                     |

| SRC    | Sample Rate Converter                           |

| UART   | Universal Asynchronous Receiver and Transmitter |

| USB    | Universal Serial Bus                            |

| V      | Volts                                           |

| VLIW   | Very large instruction word                     |

| W      | Watt                                            |

| WE     | Write Enable                                    |

### 1 Introduction

Modern speech recognition systems employ a number of fundamental techniques and mathematical models, such as diagonal covariance Gaussian mixture models and hidden Markov models. The use of these techniques is highly processor intensive and is most suited to systems that can perform floating point computations.

Implementations of speech recognition systems range from state-of-the-art research systems, to word processing applications that have embedded speech recognition (such as Microsoft Office), to applications that can recognize isolated words on a cellular phone. Research systems typically process the speech off-line, whilst word processing and cellular phones attempt to process the speech in real time. For real time systems, performance accuracy is dependent on the processing power of the system. Cellular phones typically employ processors that can only perform fixed-point calculations, requiring the floating point computations to be emulated or approximated. This leads to system performance and/or accuracy penalties. A further factor that degrades the performance of such systems is the relatively small amount of available RAM and secondary memory. This limits the complexity of the speech models which the system can store, as well as the sophistication of the recognition process it can perform.

Very little hardware that is specifically optimized for speech recognition applications, and that is accessible for research use, has been described in literature. The *In Silico Vox* project (1) is an attempt to implement speech recognition algorithms directly as hardware, by using a large FPGA. This system is limited in terms of its vocabulary size and the sophistication of its acoustic models, as it is currently only capable of recognizing up to 1000 words at a rate that is 2.2 times slower than real time. A speech recognition library has also been made available by Microchip specifically for the dsPIC30F 16-bit fixed-point family of microprocessors (2). This system is also very limited as the library only supports 100 specific words with American English pronunciation.

The aim of this project is to develop a portable high-performance microprocessor based hardware platform that can be used to completely abstract the speech recognition process from a personal computer. Hence, the system should be able to emulate the PC's peripherals, such as the mouse and keyboard, which control the input to the computer. The system, however, should not be limited to this application. We envision that a successful portable system could be employed as general voice-activated device, which can for example be used to activate household appliances for disabled persons, or in a car for hands free operation.

Finally, the system should have similar capabilities in terms of processing power and memory to a personal computer. This will allow speech recognition systems to be developed on a PC, and then easily transferred to the portable device. With these guidelines in mind, the system requirements are set out in the following section.

#### **1.1 System Requirements**

The aim of this project is to develop a stand-alone embedded system upon which state of the art processor intensive speech processing algorithms can be performed. The system would then be able to control peripheral devices through voice commands. The system requirements for the design are as follows:

- 1. The system must utilize a floating point central processing unit (CPU). The CPU must be able to perform 32-bit floating point calculations.

- 2. The system must support a minimum of 512 MB RAM.

- 3. The system must support a minimum of 512 MB non-volatile secondary storage memory.

- 4. The design must include a stereo audio analog to digital converter (ADC) and a stereo audio digital to analog converter (DAC).

- 5. The design must include microphone pre- amplification.

- 6. The design must include a universal serial bus (USB) peripheral interface with a personal computer. The design must be capable of implementing the HID keyboard and HID mouse subset of the USB2.0 HID specification.

- 7. The design must include a liquid crystal display (LCD).

It is clear from the above specification that the most important system component is the CPU itself. The choice of the CPU directly influences the processing power, amount of RAM, secondary storage and the number of peripheral devices that can be included in the design.

Therefore it is necessary to choose the CPU first and the following chapter discusses the process by which this was done.

## **2 Processor Selection**

This chapter discusses the selection process of the processor that is utilized in our design. A number of currently available high-performance processors were considered and compared, before a final choice was made.

### 2.1 Comparison of processors

Several processors were considered for this design. An in depth comparison of these processors was performed, which is summarized in Table 2-1. The different categories used to evaluate the processors are listed in the first column and the capabilities of each processor are listed in the remaining column. An explanation for the notes and abbreviations appear at the end of the table, as do the descriptions of each of the processors themselves.

| Processor                         | Analog Devices<br>SHARC 21368 | Analog Devices<br>TigerSHARC TS201 | Texas Instruments<br>TMS320C6727 | Microchip<br>dsPIC30F6014 | Freescale<br>MPC7457 | Renesas SH7751 |

|-----------------------------------|-------------------------------|------------------------------------|----------------------------------|---------------------------|----------------------|----------------|

| Clock Speed (MHz)                 | 400                           | 600                                | 300                              | 40                        | 1200                 | 240            |

| # Processing Elements             | 2                             | 2                                  | 2                                | 1                         | 1                    | 1              |

| GFLOPS                            | 2.4                           | 3.6                                | 1.8                              | No                        | unknown              | 1.7            |

| MIPS                              | 400-800 <sup>*1</sup>         | 3600 <sup>*2</sup>                 | 2400                             | 30                        | 2900                 | 430            |

| Internal Register Size            | 32-bit                        | 32-bit                             | 32-bit                           | 16-bit                    | 32-bit               | 32-bit         |

| Instruction Word Length           | 48-bit                        | 128-bit                            | 256 bit                          | 24 bit                    | 32-bit               | 16-bit         |

| Address Bus Size                  | 24 bit                        | 32-bit                             | 32-bit                           | No                        | 32-bit               | 26 bit         |

| Data bus Size                     | 32-bit                        | 64-bit                             | 32-bit                           | No                        | 64-bit               | 32-bit         |

| 32-bit Floating Point             | Yes                           | Yes                                | Yes                              | No                        | Yes                  | Yes            |

| 40-bit Floating Point             | Yes                           | Yes                                | Yes                              | No                        | No                   | No             |

| 64-bit Floating Point             | No                            | No                                 | Yes                              | No                        | Yes                  | Yes            |

| 16-bit Fixed Point                | Yes                           | Yes                                | Yes                              | Yes                       | Yes                  | Yes            |

| Cache                             | 32x48bit<br>instruct          | 6 x<br>128Kbit                     | 32KB                             | No                        | 32KB(L1)             | 24KB           |

| EMIF Transfer Rate                | 532MB/s                       | 1GB/s                              | 400MB/s                          | No                        | 640MB/s              | 640MB/s        |

| External SDRAM<br>Supported       | 384MB                         | 1024MB                             | 256MB                            | None                      | *3                   | 128MB          |

| SDRAM Speed                       | 133MHz                        | 125MHz                             | 100MHz                           | None                      | Unknown              | Unknown        |

| Onboard SRAM                      | 256KB                         | None                               | 256kB                            | 8KB                       | None                 | None           |

| Onboard DRAM                      | None                          | 3072KB                             | None                             | None                      | None                 | None           |

| Onboard ROM                       | 768KB                         | None                               | 384KB                            | 192KB                     | None                 | None           |

| Flash supported                   | 242MB                         | 16MB                               | 256MB <sup>*4</sup>              | None                      | None                 | None           |

| Slow Device Protocol              | No                            | 2 <sup>*5</sup>                    | No                               | No                        | No                   | No             |

| DMA channels                      | 32                            | 14                                 | 16                               | None                      | None                 | 4              |

| SPI Bus                           | 2                             | None                               | 2                                | 2                         | None                 | None           |

| SPORTS                            | 8                             | None                               | 16                               | None                      | None                 | None           |

| SRC                               | Yes                           | No                                 | No                               | No                        | No                   | No             |

| SPDIF                             | Yes                           | No                                 | No                               | No                        | No                   | No             |

| JTAG                              | Yes                           | Yes                                | Yes                              | No                        | Yes                  | Yes            |

| Link ports                        | None                          | 4                                  | None                             | None                      | None                 | None           |

| I2C Bus                           | None                          | None                               | 2                                | 1                         | None                 | None           |

| EEPROM                            | None                          | None                               | None                             | 4KB                       | None                 | None           |

| PCI                               | No                            | No                                 | No                               | No                        | No                   | Yes            |

| PCMCIA                            | No                            | No                                 | No                               | No                        | No                   | Yes            |

| Serial Communication<br>Interface | No                            | No                                 | No                               | No                        | No                   | Yes            |

| Smart Card                        | No                            | No                                 | No                               | No                        | No                   | Yes            |

|           | Package                                                   | 256 BGA                             | 576 BGA         | 256 BGA           | 80-<br>lead | 483 CBGA       | 256 BGA      |

|-----------|-----------------------------------------------------------|-------------------------------------|-----------------|-------------------|-------------|----------------|--------------|

|           |                                                           | 200 20,1                            | 570 501         | 200 201           | TQFP        |                | 200 20,0     |

|           | Price                                                     | R665                                | R1365           | R146              | R48         | R194           | Unknown      |

| * see not | tes for explanation                                       |                                     | •               | •                 |             |                |              |

| 1.        | The processor can therefore perform 800.                  |                                     |                 |                   | -           |                |              |

| 2.        | The processor can MIPS are 3600.                          | perform 6 32-bit                    | : instructions  | per cycle in S    | SIMD mod    | e. Therefore t | he maximum   |

| 3.        | The processor does via MPX or 60X bus                     |                                     | RAM controlle   | er directly. It o | can interfa | ce with a SDR/ | AM controlle |

| 4.        | The TMS320C6727<br>memory. However,<br>purpose input/outp | only has enoug<br>, this can be exp |                 |                   |             |                |              |

| 5.        | The TigerSHARC als<br>devices such as second              | so supports a slo                   | -               |                   |             |                | e with slowe |

| Abbrevia  | tions:                                                    |                                     |                 |                   |             |                |              |

| GFLOPS:   | Giga-floating po                                          | pint operations pe                  | er second.      |                   |             |                |              |

| MIPS:     | Million instruct                                          | ions per second.                    |                 |                   |             |                |              |

| EMIF:     | External memo                                             | ry interface.                       |                 |                   |             |                |              |

| SPI:      | Serial periphera                                          | al interface. Used                  | for interfacing | g to periphera    | l devices.  |                |              |

| SPORTS:   | Serial ports. Use                                         | ed for interfacing                  | to ADCs and D   | DACs.             |             |                |              |

| SRC:      | Sample rate con                                           | nverter.                            |                 |                   |             |                |              |

| SPDIF:    | Sony/ Phillips d                                          | igital interface. A                 | digital audio i | nterface.         |             |                |              |

| JTAG:     | Joint test acces                                          | s group IEEE 1149                   | 9.1 boundary-s  | can standard      |             |                |              |

| 12C:      | Inter-integrated                                          | d component com                     | munication      |                   |             |                |              |

Table 2-1: Comparison of processors.

Table 2-2 compares the development boards that were available from the various processors. The categories used to evaluate the development boards are listed in the first column and the specifications of each board in the following columns. No evaluation board was available for the Microchip dsPIC30F6014. Freescale and Renesas do not manufacture their own development boards. Therefore development boards from Sandpoint X3 and Codescape were analyzed.

| Evaluation kits | Analog Devices<br>SHARC | Analog Devices<br>TigerSHARC | Texas<br>Instruments | Sandpoint X3<br>(Freescale) | Codescape<br>(Renesas) |

|-----------------|-------------------------|------------------------------|----------------------|-----------------------------|------------------------|

| Processor       | 21369                   | TS201                        | TMS320C6713          | MPC7455                     | SH7751                 |

| Clock speed     | 400MHz                  | 600MHz                       | 225MHz               | 800MHz                      | 240MHz                 |

| SDRAM           | 4MB                     | 32MB                         | 8MB                  | 128MB                       | Unknown                |

| Flash memory    | 1MB                     | 512KB                        | 512KB                | None                        | Unknown                |

| Price           | R3296                   | R6659                        | R2630                | R25972                      | R18044                 |

Table 2-2: Comparison of processor evaluation boards.

The following paragraphs describe each CPU listed in Table 2-1 in more detail.

#### 2.1.1 Analog Devices TigerSHARC TS201

The TigerSHARC TS201 uses a static superscalar architecture. It has dual computational units, which each contain an arrhythmic logic unit (ALU), a multiplier, a register file and a communications logic unit (CLU). It also contains dual integer-ALUs which are separate to the computational units. The processor uses a 128-bit very large instruction word (VLIW) which enables it to execute between 1 and 4 32-bit instructions per cycle. The CPU can be configured to operate in single instruction multiple data mode (SIMD). In this mode the CPU can execute up to 6 32-bit instructions per cycle allowing a maximum of 6 32-bit floating point calculations per cycle or 24 16-bit fixed point calculations per cycle. It has 4 128-bit internal data busses that connect the processing elements to the 6 4-Mbit internal DRAM memory banks providing an internal bandwidth of 33GB/s.

The processor has a 64-bit external data and a 32-bit external address bus. The 32-bit address bus allows the CPU to address a 4G 32-bit word space. The onboard SDRAM controller can support a total of 1024MB of SDRAM over 4 SDRAM modules. The 64-bit external data bus can operate a maximum throughput of 1GB/s.

The external data bus also supports peripheral protocols such as the pipelined and slow device protocols which can address 512MB over two banks. This could be used to interface with secondary storage memory.

The CPU contains no support for serial peripheral devices such as analog-to-digital converters (ADC's). Therefore a field programmable gate array (FPGA) would be necessary to interface the CPU to an ADC and a digital-to-analog converter (DAC). The same FPGA could used to interface with a liquid crystal display (LCD) and to an USB controller.

The development board includes an ADC, a DAC, 32 MB SDRAM and 4-Mbit flash memory. It provides accessible connections to the external data bus, external address bus and control signals. A peripheral prototype board that connects through the external connections could therefore be designed, thereby simplifying the development of the final board that would also contain the CPU, and SDRAM modules.

#### 2.1.2 Analog Devices SHARC 21368 Processor

This processor is based on a super Harvard architecture. It contains two computational processing elements that operate as a SIMD engine. The processor can either operate as a single processing unit or in SIMD mode where each processing element executes the same instruction but on different data. Each processing element contains a set of parallel computation units such as an ALU, multiplier, shifter and a register file.

The super Harvard architecture allows two operands to be fetched from the data memory, two operands from the program memory, and a 48-bit instruction to be fetched from cache in a single cycle.

Transfers between the internal memory and the core can be sustained at 6.4GB/s when operating at a clock frequency of 400MHz.

7

The processor contains 2-Mbits internal static RAM and 6-Mbits internal ROM. It supports 4 external memory devices which can be either SDRAM or asynchronous memory. A maximum of either 16 MB asynchronous memory or 128MB SDRAM can be connected on each of the 4 banks. If configured to use one bank in asynchronous mode, which would be necessary in this design, then the processor would be able to support a maximum of 384MB SDRAM.

The SHARC is designed specifically for audio applications. This is emphasized by the variety of IO interfaces it supports, such as serial ports, I2C, SPIs and UARTs.

These IO interfaces provide a simple means to interface with ADCs and DACs. However glue logic would still be required to interface with a LCD, secondary storage and USB.

#### 2.1.3 Texas Instruments TMS320C6727

This CPU uses a 256-bit very large instruction word (VLIW). This allows it to execute between one and eight 32-bit instructions per cycle (six of which can be floating point instructions). The CPU supports double precision floating point, where as the TigerSHARC and SHARC do not, however a 64-bit floating point operation can take up to 4 cycles to complete.

The CPU has two data paths that connect to 2 processing units. Each unit has four functional units, namely a data-addressing unit, a multiplier and units responsible for arithmetic, logic and branch functions. Each processing unit contains 32 general purpose registers.

The CPU has 32 KB program cache, 256KB on-chip RAM and 384KB on-chip ROM. The memory controller supports single cycle data accesses between the CPU to ROM and RAM. It can perform up to three of the following parallel accesses to internal RAM and ROM:

- 2 64-bit accesses from the CPU.

- 1 256 bit program fetch from the core and program cache.

- 1 32-bit data access from the peripheral system.

The external memory interface has a 32-bit data bus and supports a maximum of 256MB of SDRAM. It also directly supports 16KB of flash memory, which can be extended to 256MB through the use of general purpose IO pins.

Like the SHARC, the TMS320C6727 is designed specifically for audio applications. This is emphasized by the variety of serial peripheral interfaces it contains. However, external interface circuitry would be necessary to interface with a USB controller and a LCD.

The development board supplied by Texas Instruments contains the TMS320C6713 CPU and not the higher performance TMS320C6727 CPU. This board has only 8MB onboard RAM and 18KB of L1 cache. It does however incorporate 64KB of L2 cache. These limitations may cause bottle necks if the size of program is too large to fit in the internal memory.

#### 2.1.4 Microchip dsPIC30F6014

This CPU is a 16-bit processor and uses a 24-bit instruction word length. The core is capable of performing one data memory read, one working register read, one data memory write and one program memory read per instruction cycle. The digital signal processor (DSP) engine features a high speed fixed point 17-bit X 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The CPU has no support for hardware floating point operations. It also has no support for external memory such as SDRAM or Flash memory.

#### 2.1.5 Freescale MPC7457:

The MPC7457 implements the 32-bit Power PC and uses a superscalar architecture. As many 4 instructions can be fetched from the cache simultaneously and as many as 12 instructions can be in the instruction queue. Most instructions have a single cycle execution time.

The CPU contains 11 independent execution units, consisting of 3 register files, a branch processing unit, 4 integer units, a floating point unit, 4 vector units and a load/store unit. It contains 32 KB of L1 cache, 512 KB of L2 cache and supports up to 4MB of external SRAM as L3 cache. It is capable of performing 32-bit and 64-bit floating point operations.

The processor also supports the MPX and 60X bus protocols, which allow the MPC7457 to interface with memory controllers and host bridges. Its memory management unit can address a 36bit physical address and a 52bit virtual address. The MPX and 60X bus protocol support a sustained throughput of 640MB/s via a 64-bit data bus.

The MPC7457 would therefore require a host controller that interfaces to SDRAM, it would also require external logic such as an FPGA or PLD to interface with ADC's, a USB, an LCD display and external flash memory.

#### 2.1.6 Renesas SH7751:

Like the SHARC, the SH7751 uses a super Harvard architecture. This super scalar architecture allows the simultaneous execution of 2 instructions, reaching a maximum throughput of 2 instructions per cycle. It has a 32-bit internal data bus and it has a 16-bit instruction length.

It uses a memory management unit (MMU) to create a 32-bit virtual memory address space. Part of the address space corresponds to external memory, which is addressed by 29 address lines. This allows a total of 448MB of external memory such as SRAM, DRAM and ROM, PCMCIA and MPX to be directly attached in 7 separate areas, each with a maximum size of 64MB. An eighth area is used as reserved space (therefore the total memory that can be addressed including this reserved space is 512MB). The MMU uses address translation to convert from the virtual memory address to the physical memory address. The 7 areas can be configured to support different memory types in different ways. One is able to configure a maximum of 128MB SDRAM and a maximum of 448MB SRAM.

The CPU can execute the floating point multiply and accumulate, floating point add, floating point subtraction and floating point multiply instructions with 3 cycle latency for single precision and a 8 cycle latency for double precision. These instructions also have a pipeline delay of 1 cycle for single precision and a pipeline delay of 6 cycles for double precision.

The CPU supports a serial communication interface which would provide a simple means to interface with ADC's, USB and to LCD displays. It however would require external logic such as a PLD to interface with secondary storage memory.

#### 2.2 Conclusion

For all of the CPU choices considered it would be necessary to use external communication logic to interface with most of the required peripheral components. The support for peripheral components is therefore not a major determining factor for the choice of an appropriate processor.

To simplify the design and prototype process, it is necessary to select a CPU for which a development board is available that includes reasonable amounts of RAM and also external connections that can be used to interface with a peripheral board. This would allow the debugging of the peripheral components to be performed, before a final prototype including the processor and system memory is developed.

The development boards available for the Renesas and Freescale CPU's are both very expensive when compared to those supplied by the other manufacturer and therefore they were not considered for this design.

No development board was available for the higher performance Texas Instruments CPU. This processor does not meet the system requirements with respect to the amount of RAM that can be supported and is therefore not considered for this design.

The Microchip dsPIC30F6014 does not meet any of the system requirements and is therefore not considered for this design.

The Analog Devices SHARC does not meet the system requirements with respect to the amount of RAM supported and is therefore not considered for the design.

The only processor that does meet the RAM system requirements is the Analog Devices TigerSHARC. The TigerSHARC development board contains 32MB of RAM, and the external interface of the development board can be used to interface with peripheral devices by means of suitable interconnection logic. The Analog Devices TigerSHARC TS201 600MHz DSP is therefore chosen for the design that is described in this thesis, and the following chapters describe the design and implementation of this system in detail.

## **3 System Design Overview**

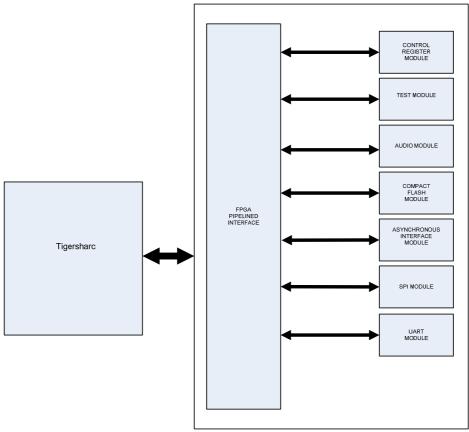

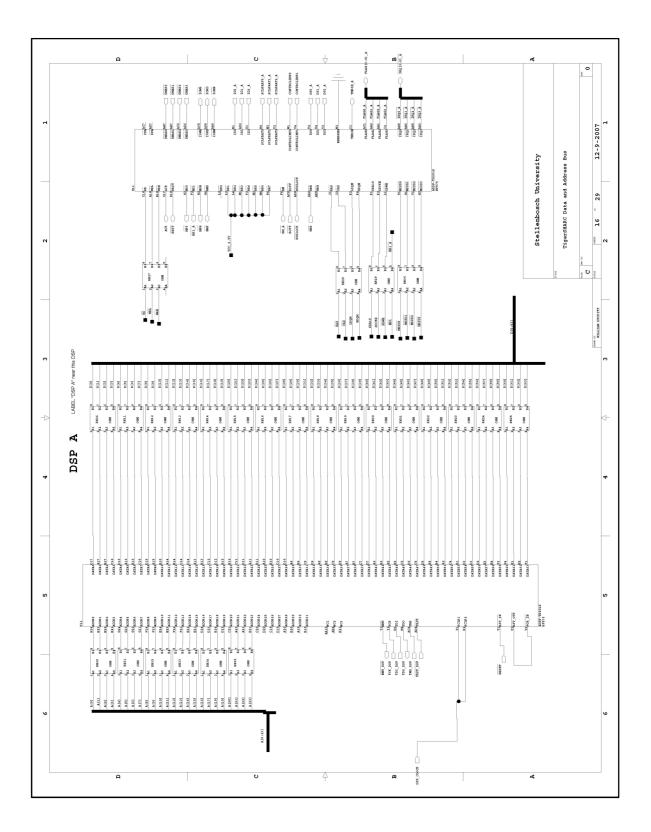

Our system utilizes the Analog Devices TigerSHARC 600MHz digital signal processor as the central processing unit. The TigerSHARC makes use of its external data bus, which operates at 100MHz, to interface to 512MB SDRAM, an FPGA and 512KB ROM.

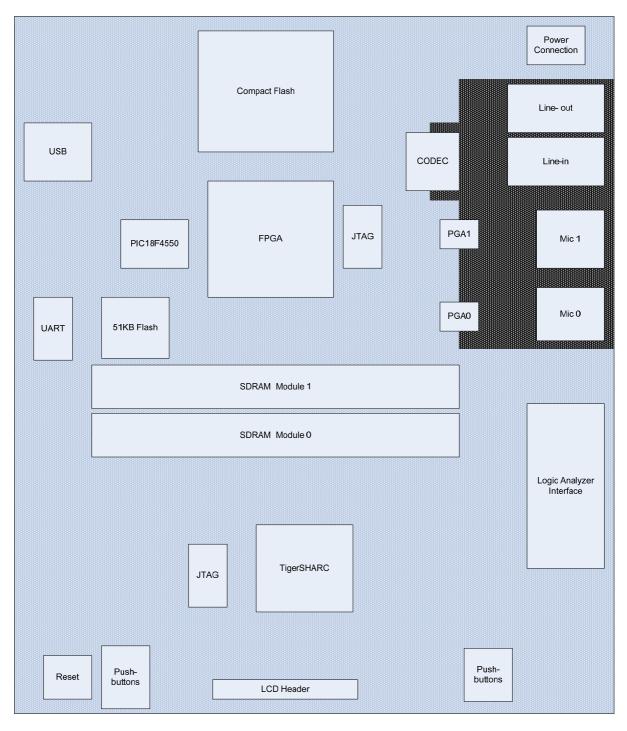

The FPGA is in turn used to interface with all the peripheral components, such as an LCD display, a Compact Flash card, a multi-channel audio input and output system, a USB interface, a logic analyzer, a UART and a push-button and LED interface. A high level block diagram of our design is illustrated in Figure 3-1.

Figure 3-1: High level block diagram of the system.

Figure 3-2: A photograph of the final prototype illustrating the different system components.

The system was designed in two phases. The initial phase involved interfacing the Analog Devices TigerSHARC TS201 development board to a peripheral board.

The design of this peripheral board involved implementing parts of the system specification, such as the secondary storage, audio, LCD, and USB. The final stage involved incorporating the peripheral board into a design which also included the TigerSHARC processor and RAM. A photograph of the final prototype is illustrated in Figure 3-2.

In designing this system, consideration needed to be taken for the clock distribution, signal integrity, system reset and the system power distribution, all of which are not illustrated in the block diagram.

This thesis documents the complete system design in detail. In order to improve the documents readability, the flow of the hardware design is broken down into the following chapters:

- Chapter 4 discusses the TigerSHARC processor.

- Chapter 5 discusses the FPGA system.

- Chapter 6 discusses the audio system.

- Chapter 7 discusses the storage system.

- Chapter 8 discusses the USB and LCD system.

- Chapter 9 discusses the UART system.

- Chapter 10 discusses the push buttons and LEDs system.

- Chapter 11 discusses the logic level translation system between various components

- Chapter 12 discusses the system reset.

- Chapter 13 discusses the SDRAM.

- Chapter 14 discusses the clock distribution and signal integrity.

- Chapter 15 discusses the power supply system

- Chapter 16 discusses the schematic capture and PCB layout.

Finally, the software that was written to demonstrate the correct working of this system is discussed in Chapter 17 and the performance of the processor is evaluated in Chapter 18.

## **4 The Central Processing Unit**

This chapter discusses the implementation of the Analog Devices TigerSHARC TS201 600MHz digital signal processor (DSP) as the central processing unit in our design.

Figure 4-1: Functional Block Diagram of the TigerSHARC (reproduced from datasheet (3)).

Figure 4-1 illustrates a functional block diagram of the DSP. The following sections explain the parts of the DSP which are applicable to this design.

#### 4.1 TigerSHARC Computational Blocks

The TigerSHARC is a static superscalar CPU. It has dual computational units, which each contain an ALU, a multiplier, a register file and a communications logic unit. It also contains dual integer-ALUs. It has a 128-bit very large instruction word (VLIW) which enables it to execute between 1 and 4 32-bit instructions per cycle. The CPU can be configured to operate in single

instruction multiple data mode (SIMD) where both computational units perform the same instructions but on different data. In this mode the CPU can execute up to 6 32-bit instructions per clock cycle allowing a maximum of 6 32-bit floating point calculations per cycle or 24 16-bit fixed point calculations per cycle.

#### 4.2 TigerSHARC internal memory

The ADSP-TS201S processor internal memory consists of 24M bits of on-chip DRAM, divided into six blocks of 4M bits that are addressable as 128K × 32-bit words. Each block—M0, M2, M4, M6, M8, and M10—can store program instructions, data, or both, so applications can configure memory to suit specific needs. Placing program instructions and data in different memory blocks, however, enables the DSP to access data while performing an instruction fetch. Each memory segment contains a 128K bit cache to enable single cycle access to internal DRAM. The internal memory space is illustrated in Figure 4-2.

Figure 4-2: TigerSHARC internal memory space, showing blocks M0 to M10 (reproduced from datasheet (3)).

The linker descriptive file (LDF) is used to tell the compiler in which sections of memory the program code and data must be placed. Although, memory can be allocated dynamically at runtime through the use of multiple heaps, it is necessary to reserve memory for the heap in the LDF and to statically declare in which portions of memory the code and data must be placed. For example, it is possible to place multiple heaps in the internal memory or in the external memory. For more information on how to program the LDF and the compiler please refer to the Linker manual and C/C++ compiler manual (4).

#### 4.3 External Port

The TigerSHARC TS201 processor's external port provides an interface with off-chip memory and peripherals. The 4G 32-bit word space is included in the DSP's unified memory map, which is illustrated in Figure 4-3.

Figure 4-3: TigerSHARC unified memory map (reproduced from datasheet (3)).

The external system bus provides a single 64-bit data bus and a single 32-bit address bus. The external data bus can be configured for 32-bit and 64-bit, little endian operations. Our system is configured to operate with a 64-bit data bus. The lower 32-bits of the external data bus are connected to even memory addresses and the upper 32-bits are connected to the odd addresses. The addressing of the external memory devices and memory mapped peripherals is facilitated by the on-chip decoding of high order address lines to generate memory bank select signals. The TigerSHARC can be configured to operate in a multiprocessor environment. Figure 4-3 illustrates how it is possible to address each of the processor's internal memory space within the unified memory map. Since our design implements 1 processor, however, the multiprocessor memory space is not used. Similarly the host memory space provides an interface with a host processor. However, since no host processor is implemented in this design, the host processor memory space is also not used.

The external port supports pipelined, slow and SDRAM protocols.

The TigerSHARC TS201 processor has two memory spaces, named MS0 and MS1, which can be used to interface with peripheral devices using the pipelined or slow device protocol. The processor also has four memory spaces which can be used to interface with SDRAM devices, named MSSD0 bank 0, MSSD1 bank 1, MSSD2 bank 2, MSSD3 bank 3.

Each memory space is 64M 32-bit words in size. Consequently the chip selects signals for these address spaces are  $\overline{\text{MS0}}$ ,  $\overline{\text{MS1}}$ ,  $\overline{\text{MSSD0}}$ ,  $\overline{\text{MSSD1}}$ ,  $\overline{\text{MSSD2}}$  and  $\overline{\text{MSSD3}}$  respectively, and Table 4-1 illustrates address decoding of these chip select signals. Address bus bits 26-0 are used to address each of the 64M x 32-bit words in each memory space.

| Address Bus Bits 31-27 | Chip Select Signals |

|------------------------|---------------------|

| 00110                  | MSO                 |

| 00111                  | MS1                 |

| 01000                  | MSSD0               |

| 01010                  | MSSD1               |

| 01100                  | MSSD2               |

| 01110                  | MSSD3               |

Table 4-1: Chip select address decoding.

Depending on the configuration of the drive strength of the TigerSHARC (discussed in section 4.4.4), the control signals, address bus and data bus can take up to 4ns to become valid after the rising edge of the system clock cycle (SCLK) in which they were asserted. The signals are also held for a minimum of 1ns and disabled within 2ns after the following rising edge. Therefore all timing diagrams discussed in the following sections illustrate the address, data bus and control signals cycles with a slight delay after the rising edge of the clock.

The following section discusses the pipelined and slow devices protocols that can be used in memory space MS0 and MS1. The SDRAM controller and interface are discussed in chapter 13.

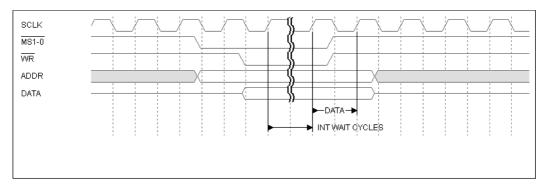

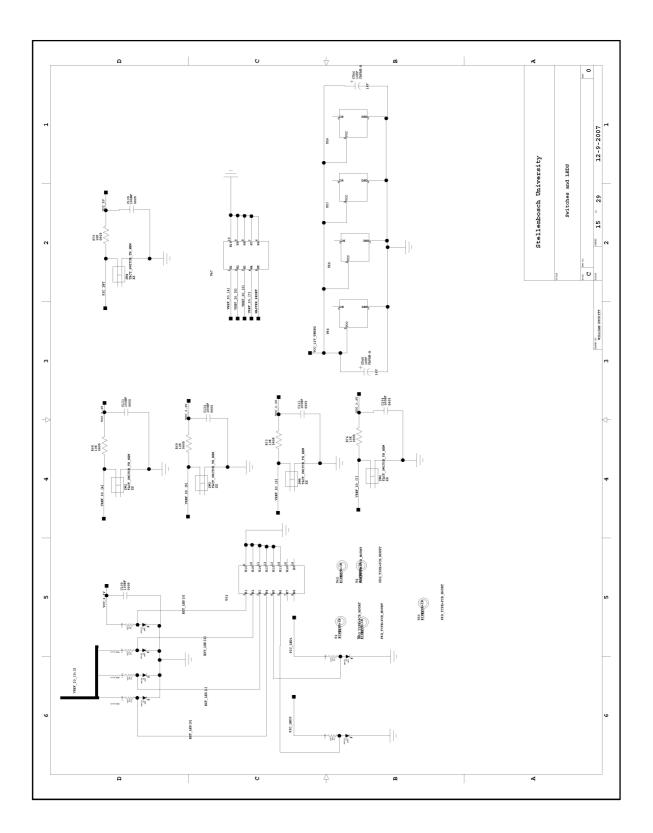

## 4.3.1 Pipelined protocol

The pipelined protocol is the faster of the two communication protocols that can be used in memory space MS0 and MS1. It allows for the pipelining of transactions with a throughput of one datum per cycle and a transaction latency that can be programmed to be between one and four cycles. The address and control signals of a transaction are issued in the address cycle and the data is transferred a few cycles later. The TigerSHARC processor can issue an address of a new transaction every cycle and does not need to wait for the completion of the data cycle of the first transaction before beginning the address cycle of the new transaction. Figure 4-4 illustrates the pipeline protocol read cycle with a read latency of 4, for four sequential read cycles. Figure 4-5 illustrates the pipeline protocol write cycle with a write latency of 1, for four sequential write cycles.

Figure 4-4: Pipelined protocol: read cycle, with a read latency of 4.

Figure 4-5: Pipelined protocol: write cycle, with a write latency of 1.

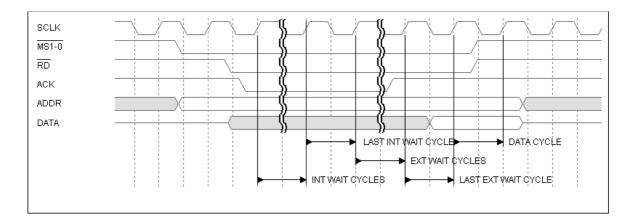

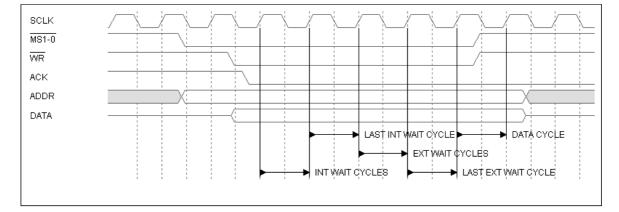

## 4.3.2 Slow device protocol

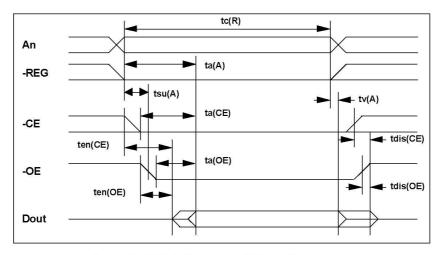

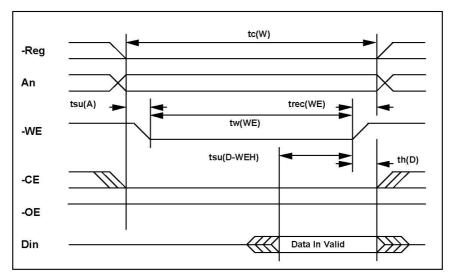

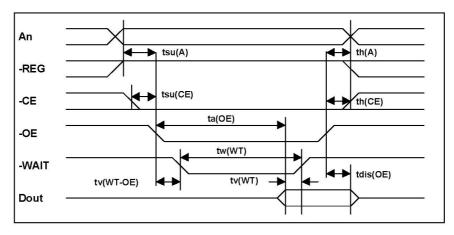

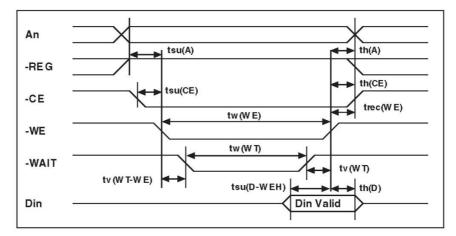

The TigerSHARC also supports a slow device protocol in memory spaces MSO and MS1. The protocol allows the TigerSHARC to interface with non critical devices, and supports the insertion of wait cycles. A maximum of three internal wait cycles can be inserted, while external wait cycles can be inserted through the use of the acknowledge (ACK) signal. The slow device protocol read and write cycles are illustrated in Figure 4-6 and Figure 4-7 respectively. Figure 4-8 and Figure 4-9 illustrate the read and write cycles with external wait cycles.

Figure 4-6: Slow device protocol: read cycle.

Figure 4-7: Slow device protocol: write cycle.

Figure 4-6 and Figure 4-7 illustrate that the chip selects signals  $\overline{MS0}$  and  $\overline{MS1}$  are asserted in the first clock cycle. In the next cycle the read or write control signal is asserted, after which the programmed internal wait cycles are inserted. After the completion of the wait cycles, the host or the device will sample the data bus in the data cycle.

Figure 4-8: Slow device protocol: read cycle with external wait cycles.

Figure 4-9: Slow device protocol: write cycle with external wait cycles.

Figure 4-8 and Figure 4-9 illustrate that the chip selects signals  $\overline{MS0}$  and  $\overline{MS1}$  are asserted in the first clock cycle. In the next cycle, the read or write control signal is asserted, after which the programmed internal wait cycles are inserted. The slave device must assert the ACK signal before the completion of the internal wait cycles. If the device asserts the ACK signal before the start of the last internal wait cycle, then the TigerSHARC will insert extra wait cycles until the slave device deasserts the ACK signal. The TigerSHARC will then insert one more internal wait cycle. After which the host or the device will sample the data bus in the data cycle.

#### 4.3.3 DMA Controller

The TigerSHARC has an on-board DMA controller that provides 14 zero overhead DMA channels that can function without processor intervention. The controller operates independently of the core, enabling DMA transfers to execute whilst the DSP's core continues to execute program instructions. The DMA controller is capable of performing both one dimensional and two dimensional memory transfers. It can perform internal to internal, internal to external and external to internal memory transfers as well as DMA chaining, whereby the DMA controller can be configured to initialize another DMA transfer.

The DMA channels 0 to 3 perform transfers between external memory and internal memory. This design employs DMA channel 0 to perform memory transfers for the audio driver. DMA channel 3 is used to perform block transfers between the FPGA and internal memory and vice versa. The other DMA channels are not currently used and remain for future expansion.

#### 4.3.4 Interrupt controller