# GPU Acceleration of Matrix-based Methods in Computational Electromagnetics

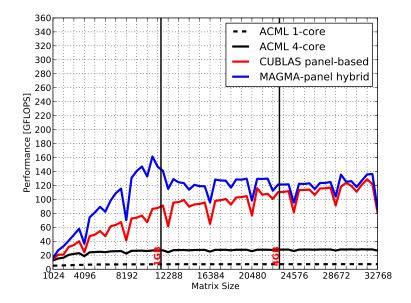

by

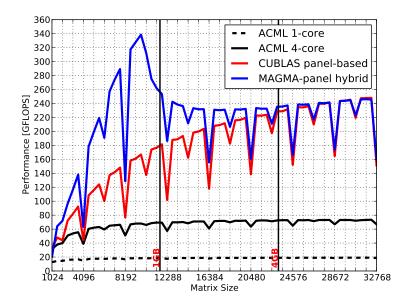

#### Evan Lezar

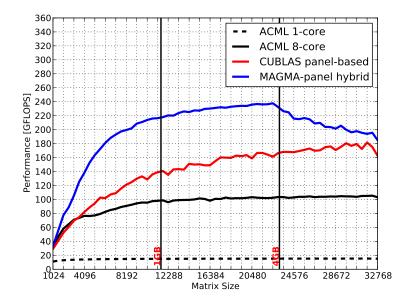

Dissertation approved for the degree of Doctor of Philosophy in Engineering at Stellenbosch University

Department of Electrical and Electronic Engineering, Stellenbosch University, Private Bag X1, 7602 Matieland, South Africa.

Promoter: Prof. D.B. Davidson

Department of Electrical and Electronic Engineering

Stellenbosch University

### **Declaration**

By submitting this dissertation electronically, I declare that the entirety of the work contained therein is my own, original work, that I am the sole author thereof (save to the extent explicitly otherwise stated), that reproduction and publication thereof by Stellenbosch University will not infringe any third party rights and that I have not previously in its entirety or in part submitted it for obtaining any qualification.

| Signat | ure: E. Lezar     |

|--------|-------------------|

| Date:  | February 23, 2011 |

Copyright  $\bigodot$  2011 Stellenbosch University All rights reserved.

### **Abstract**

This work considers the acceleration of matrix-based computational electromagnetic (CEM) techniques using graphics processing units (GPUs). These massively parallel processors have gained much support since late 2006, with software tools such as CUDA and OpenCL greatly simplifying the process of harnessing the computational power of these devices. As with any advances in computation, the use of these devices enables the modelling of more complex problems, which in turn should give rise to better solutions to a number of global challenges faced at present.

For the purpose of this dissertation, CUDA is used in an investigation of the acceleration of two methods in CEM that are used to tackle a variety of problems. The first of these is the Method of Moments (MOM) which is typically used to model radiation and scattering problems, with the latter begin considered here. For the CUDA acceleration of the MOM presented here, the assembly and subsequent solution of the matrix equation associated with the method are considered. This is done for both single and double precision floating point matrices.

For the solution of the matrix equation, general dense linear algebra techniques are used, which allow for the use of a vast expanse of existing knowledge on the subject. This also means that implementations developed here along with the results presented are immediately applicable to the same wide array of applications where these methods are employed.

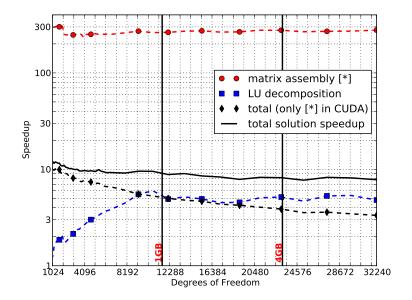

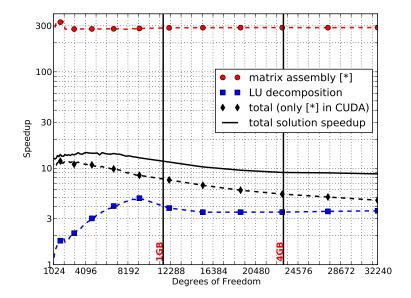

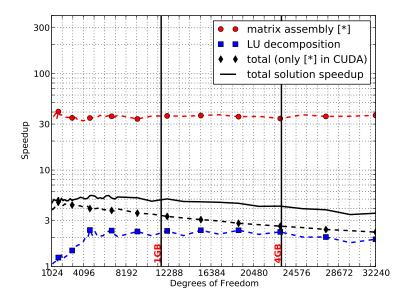

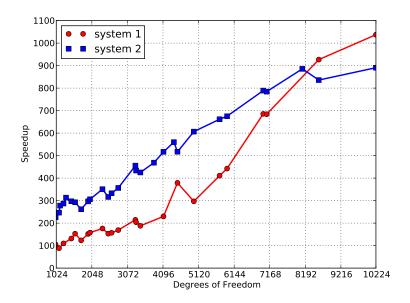

Both the assembly and solution of the matrix equation implementations presented result in significant speedups over multi-core CPU implementations, with speedups of up to  $300 \times$  and  $10 \times$ , respectively, being measured. The implementations presented also overcome one of the major limitations in the use of GPUs as accelerators – that of limited memory capacity – with problems up to 16 times larger than would normally be possible being solved.

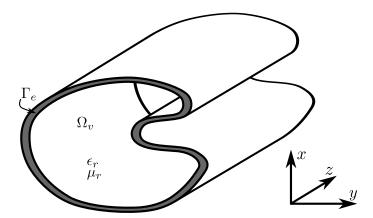

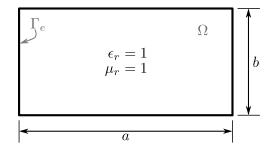

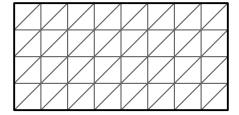

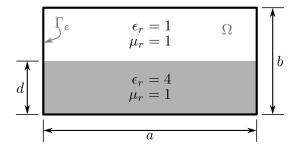

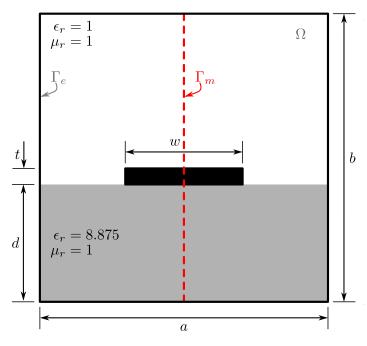

The second matrix-based technique considered is the Finite Element Method (FEM), which allows for the accurate modelling of complex geometric structures including non-uniform dielectric and magnetic properties of materials, and is particularly well suited to handling bounded structures such as waveguide. In this work the CUDA acceleration of the cutoff and dispersion analysis of three waveguide configurations is presented. The modelling of these problems using an open-source software package, FEniCS, is also discussed.

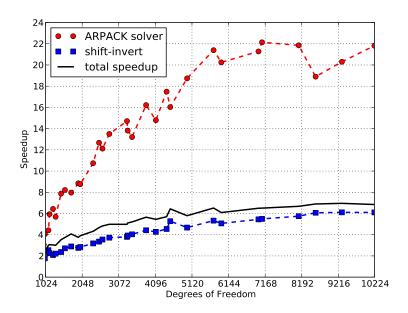

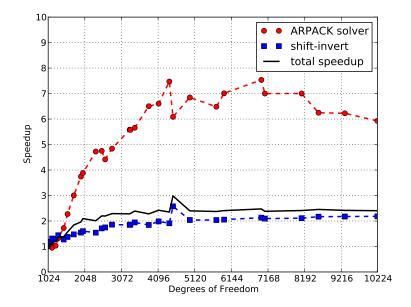

Once again, the problem can be approached from a linear algebra perspective, with the formulation in this case resulting in a generalised eigenvalue (GEV) problem. For the problems considered, a total solution speedup of up to  $7\times$  is measured for the solution of the generalised eigenvalue problem, with up to  $22\times$  being attained for the solution of the standard eigenvalue problem that forms part of the GEV problem.

# **Opsomming**

In hierdie werkstuk word die versnelling van matriksmetodes in numeriese elektromagnetika (NEM) deur die gebruik van grafiese verwerkingseenhede (GVEe) oorweeg. Die gebruik van hierdie verwerkingseenhede is aansienlik vergemaklik in 2006 deur sagteware pakette soos CUDA en OpenCL. Hierdie toestelle, soos ander verbeterings in verwerkings vermoë, maak dit moontlik om meer komplekse probleme op te los. Hierdie stel wetenskaplikes weer in staat om globale uitdagins beter aan te pak.

In hierdie proefskrif word CUDA gebruik om ondersoek in te stel na die versnelling van twee metodes in NEM, naamlik die Moment Metode (MOM) en die Eindige Element Metode (EEM). Die MOM word tipies gebruik om stralings- en weerkaatsingsprobleme op te los. Hier word slegs na die weerkaatsingsprobleme gekyk. CUDA word gebruik om die opstel van die MOM matriks en ook die daaropvolgende oplossing van die matriksvergelyking wat met die metode gepaard gaan te bespoedig.

Algemene digte lineêre algebra tegnieke word benut om die matriksvergelykings op te los. Dit stel die magdom bestaande kennis in die vagebied beskikbaar vir die oplossing, en gee ook aanleiding daartoe dat enige implementasies wat ontwikkel word en resultate wat verkry word ook betrekking het tot 'n wye verskeidenheid probleme wat dié lineêre algebra metodes gebruik.

Die Eindige Element Metode word op sy beurd gebruik om komplekse geometrieë as ook nieuniforme materiaaleienskappe te modelleer. Die EEM is ook baie geskik om begrensde strukture soos golfgeleiers te hanteer. Hier word CUDA gebruik of om die afsny- en dispersieanalise van drie golfleierkonfigurasies te versnel. Die implementasie van hierdie probleme word gedoen deur 'n versameling oopbronkode wat bekend staan as FEniCS, wat ook hierin bespreek word.

# Acknowledgements

I would like to thank the following people, who all played some role in making this research possible:

**Ingrid** for everything that she has done for me, especially in the last few months when pressure was at its highest.

**Prof. D.B. Davidson** for the guidance through the years.

**Renier Marchand** for his proofreading, useful comments, and ensuring that this manuscript was handed in on time.

Mary Lancaster for her proofreading and caramel brownies.

My family for there continued support.

My in-laws for providing me with board and lodging while in Stellenbosch.

Danie Ludick for useful discussions and code samples.

Braam and Delita Otto, Paul van der Merwe, and Josh Swart for their continued friendship and the odd cup of coffee or tea.

André Young for his countless lifts to and from the airport and insightful discussions.

**Prof. Albert Groenwold** for his willingness to listen and excitement about the results that really kept me motivated.

Ulrich Jakobus for his discussions on the MOM and LU decomposition implementations.

Willem Burger for his help in debugging many of the implementations.

**Heine de Jager** for his assistance in the administration of the new GPU-enabled node at the university's HPC facility.

Kevin Colville and Sebastian Wyngaard for interesting discussions on HPC in general.

The NRF, CHPC, and EMSS-SA (Pty) Ltd for providing financial support for this research in the form of bursaries, contract employment, or funding for hardware used for testing.

The CEMAGG group for the great group lunches.

The occupants of E212 for putting up with my tea and coffee habits.

The residents of Farside for providing a little life outside the office.

and to anyone that I have forgotten. Thank you too.

# Contents

| D                         | eclar | ation                                                               | ]          |

|---------------------------|-------|---------------------------------------------------------------------|------------|

| $\mathbf{A}$              | bstra | net                                                                 | i          |

| $\mathbf{O}_{\mathbf{j}}$ | psom  | nming                                                               | iii        |

| A                         | ckno  | wledgements                                                         | iv         |

| C                         | onter | nts                                                                 | v          |

| N                         | omer  | nclature                                                            | /iii       |

| 1                         | Intr  | roduction                                                           | 1          |

|                           | 1.1   | Research objectives                                                 | 2          |

|                           | 1.2   | Contributions                                                       | 3          |

|                           | 1.3   | Chapter summary                                                     | 4          |

| 2                         | Ger   | neral purpose GPU computing                                         | 6          |

|                           | 2.1   | An overview of parallel computing                                   | 6          |

|                           | 2.2   | History of GPU computing                                            | 8          |

|                           |       | 2.2.1 History of NVIDIA CUDA                                        | 9          |

|                           |       | 2.2.2 History of the ATI Stream SDK                                 | 10         |

|                           | 2.3   | NVIDIA CUDA                                                         | 11         |

|                           |       | 2.3.1 Programming model                                             | 11         |

|                           |       | 2.3.2 Hardware implementation                                       | 17         |

|                           |       | 2.3.3 Mapping software to hardware                                  | 20         |

|                           |       | 2.3.4 Software ecosystem                                            | 21         |

|                           | 2.4   | ATI Stream SDK                                                      | 23         |

|                           |       | 2.4.1 Hardware                                                      | 23         |

|                           |       | 2.4.2 Software                                                      | 25         |

|                           | 2.5   | OpenCL                                                              | 26         |

|                           |       | 2.5.1 Platform model                                                | 26         |

|                           |       | 2.5.2 Execution model                                               | 27         |

|                           |       | 2.5.3 Memory model                                                  | 28         |

|                           | 2.6   | Outlook for GPGPU computing                                         | 28         |

|                           | 2.7   |                                                                     | 29         |

| 3                         | GP    | U-accelerated dense NLA                                             | <b>3</b> 0 |

|                           | 3.1   | Dense numerical linear algebra                                      | 31         |

|                           |       |                                                                     | 34         |

|                           | 3.2   | A note on CUDA-based dense numerical linear algebra implementations | 36         |

CONTENTS

|          | 3.3          | Overcoming GPU memory limitations for dense LU decomposition | 37        |

|----------|--------------|--------------------------------------------------------------|-----------|

|          |              | 3.3.1 Left-looking LU decomposition                          | 39        |

|          |              | 3.3.2 Adapting for GPU acceleration                          | 40        |

|          |              | 3.3.3 The MAGMA-panel-based hybrid                           | 42        |

|          |              | 3.3.4 Implementation analysis                                | 44        |

|          | 3.4          | Benchmarking                                                 | 45        |

|          | 0.1          | 3.4.1 The test platforms                                     | 46        |

|          |              | 3.4.2 Results                                                | 46        |

|          | 3.5          | Conclusion                                                   | 56        |

|          | 5.5          | Conclusion                                                   | 50        |

| 4        | MO           | M scattering analysis                                        | <b>58</b> |

|          | 4.1          | Related work                                                 | 59        |

|          | 4.2          | Problem overview                                             | 60        |

|          |              | 4.2.1 Monostatic scattering                                  | 61        |

|          |              | 4.2.2 The Method of Moments                                  | 62        |

|          | 4.3          | The implementation of an accelerated MOM solution process    | 66        |

|          |              | 4.3.1 The development process                                | 67        |

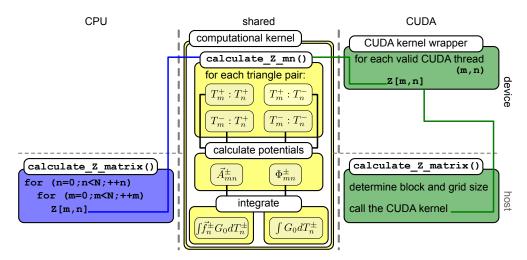

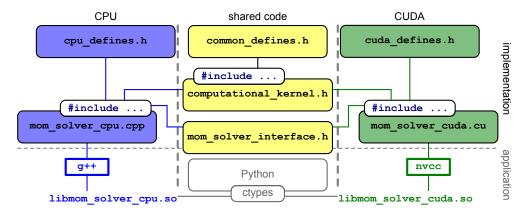

|          |              | 4.3.2 The matrix assembly computational process              | 68        |

|          |              | 4.3.3 CPU and CUDA co-development                            | 68        |

|          |              | 4.3.4 Parallel CPU implementation                            | 73        |

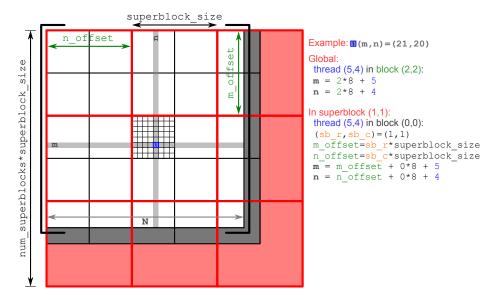

|          |              | 4.3.5 Parallel CUDA implementation                           | 74        |

|          |              | 4.3.6 Implementation of the other phases                     | 80        |

|          | 4.4          | Verification results                                         | 81        |

|          | 4.5          | Performance results                                          | 85        |

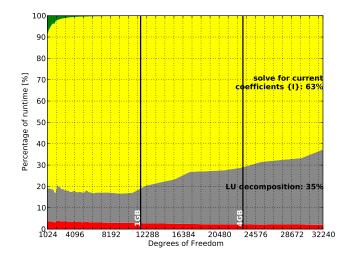

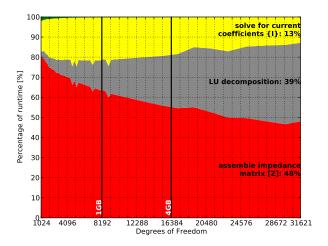

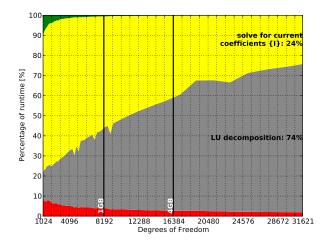

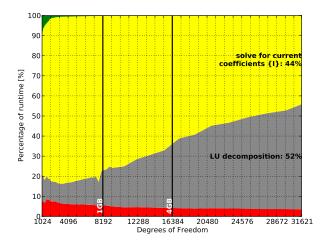

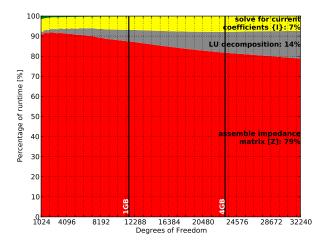

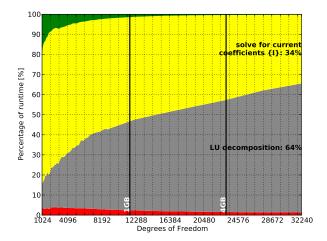

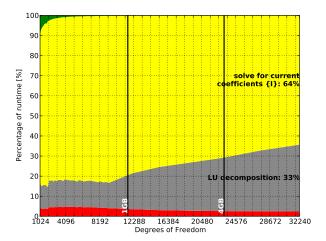

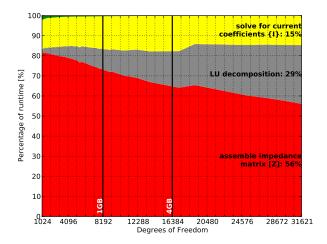

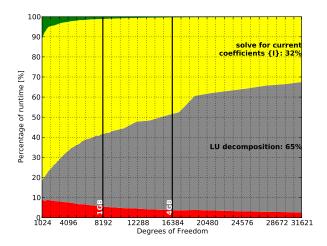

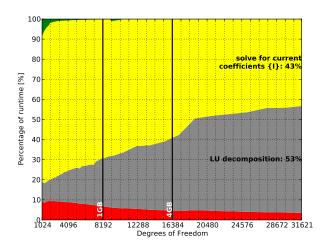

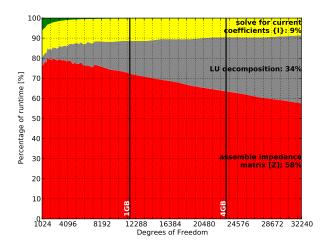

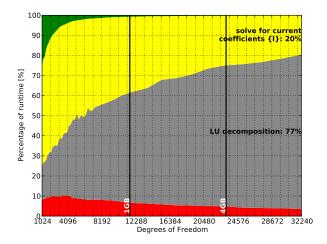

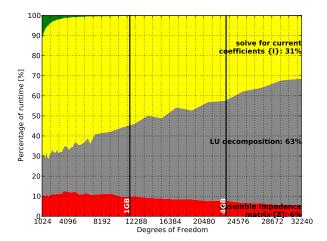

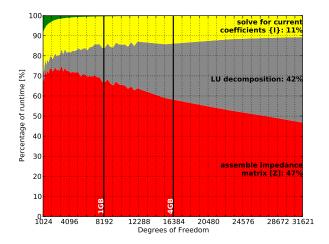

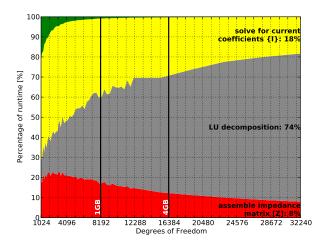

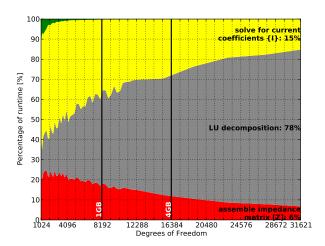

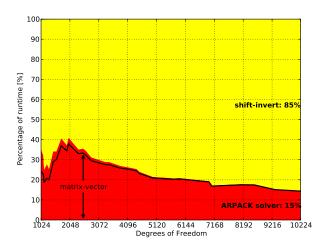

|          | 1.0          | 4.5.1 Runtime contributions                                  | 85        |

|          |              | 4.5.2 Speedups                                               | 87        |

|          |              | 4.5.3 Discussion of results                                  | 93        |

|          | 4.6          | Conclusion                                                   | 95<br>95  |

|          | 4.0          | Conclusion                                                   | 90        |

| <b>5</b> | FEN          | M waveguide analysis                                         | 97        |

|          | 5.1          | Related work                                                 | 98        |

|          | 5.2          | FEM formulation for cutoff and dispersion analysis           | 98        |

|          |              | 5.2.1 Cutoff analysis                                        | 100       |

|          |              |                                                              | 101       |

|          |              |                                                              | 102       |

|          | 5.3          | •                                                            | 104       |

|          |              | •                                                            | 104       |

|          |              |                                                              | 113       |

|          | 5.4          | •                                                            | 117       |

|          | 5.5          |                                                              | 123       |

|          | 0.0          |                                                              | 123       |

|          |              |                                                              | 125       |

|          |              |                                                              | 126       |

|          | 5.6          |                                                              | 128       |

|          | 0.0          | Conclusion                                                   | 140       |

| 6        | Con          | nclusion and future work                                     | 130       |

| -        | 6.1          |                                                              | 131       |

|          | 6.2          |                                                              | 131       |

|          | ~ · <b>-</b> |                                                              |           |

| Lis      | st of        | References                                                   | 133       |

| CONTENTS                           | vii |

|------------------------------------|-----|

| Additional MOM performance results | 144 |

| Additional FEM performance results | 154 |

### Nomenclature

#### Notation

$\|\cdot\|$  the Frobenius norm

[X] a matrix

$(X)_{ij}$  the entry at row i and column j of the matrix [X]

$\{x\}$  a column vector

$(x)_i$  the  $i^{\text{th}}$  element in the vector  $\{x\}$

$\vec{x}$  a spatial vector

$\hat{x}$  a spatial vector with unit norm

#### Constants

$c_0 \approx 299792458 \text{ m} \cdot \text{s}^{-1} \text{ (the speed of light in vacuum)}$

$\pi \approx 3.14159265$

#### **Symbols**

$\vec{E}$  electric field

$ec{E}_{inc}$  incident electric field  $ec{E}_s$  scattered electric field

$\epsilon_r$  relative permittivity of a medium

$f, f_c, f_o$  frequency, cutoff frequency, operating frequency

$\vec{f}_n$  the RWG basis function associated with edge the  $n^{\rm th}$  edge

$G_0$  the scalar free-space Green's function

$\gamma = \alpha + j\beta$  propagation constant

$\Gamma_e$  a boundary that is an electric wall  $\Gamma_m$  a boundary that is a magnetic wall

$\vec{J}$  surface current density

$k, k_c, k_o$  wavenumber, cutoff wavenumber, operating wavenumber

$\vec{k}$  propagation vector

$L_i$  the  $i^{\text{th}}$  scalar Lagrange finite element basis function

$\mu_r$  relative permeability of a medium

$\vec{N}_i$  the  $i^{\text{th}}$  curl-conforming Nédélec finite element vector basis function of the first

kind

$\nabla$  the gradient operator  $\nabla \times$  the curl operator

$\nabla_t$  the transverse gradient operator

NOMENCLATURE ix

| $ abla_t 	imes$                  | the transverse curl operator                                                                              |

|----------------------------------|-----------------------------------------------------------------------------------------------------------|

| $\omega,  \omega_c,  \omega_o$   | angular frequency, angular cutoff frequency, angular operating frequency                                  |

| $\Omega$                         | the domain defined by a waveguide cross-section                                                           |

| $\Omega_v$                       | the domain defined by the interior of a waveguide                                                         |

| $ec{r}$                          | the position vector                                                                                       |

| $r,	heta,\phi$                   | coordinates in the spherical coordinate system                                                            |

| $\hat{r},\hat{	heta},\hat{\phi}$ | the unit coordinate vectors in the spherical coordinate system                                            |

| $\sigma$                         | the real valued shift used to transform a generalised eigenvalue problem to a standard eigenvalue problem |

| $\sigma_{RCS}$                   | the radar cross-section                                                                                   |

| $TE_{mn}$                        | a transverse electric waveguide mode                                                                      |

| $TM_{mn}$                        | a transverse magnetic waveguide mode                                                                      |

| x, y, z                          | coordinates in the Cartesian coordinate system                                                            |

| $\hat{x},\hat{y},\hat{z}$        | the unit coordinate vectors in the Cartesian coordinate system                                            |

|                                  |                                                                                                           |

#### Abbreviations and acronyms

ALU arithmetic and logic unit

API application programming interface

BVP boundary-value problem

CEM computational electromagnetics

CPU central processing unit

DP double precision

EFIE electric field integral equation FDTD finite-difference time-domain

FEM finite element method

FP floating point

FLOP floating point operation FLOPs floating point operations

FLOPS floating point operations per second

MFLOPS  $10^6$  FLOPS GFLOPS  $10^9$  FLOPS TFLOPS  $10^{12}$  FLOPS PFLOPS  $10^{15}$  FLOPS

GB gigabyte (1024 MB) GB/s gigabyte per second

GEV generalised eigenvalue problem

GPU graphics processing unit GPUs graphics processing units GPGPU general purpose GPU

ISA instruction set architecture MB megabyte  $(1024 \cdot 1024 \text{ bytes})$

MB/s megabyte per second

NOMENCLATURE x

MIMD multiple-instruction-multiple-data

MOM method of moments

NLA numerical linear algebra

OOC out-of-core

PEC perfect electrical conductor

RCS radar cross-section

RWG Rao-Wilton-Glission

SDK software development kit

SEV standard eigenvalue problem

SIMD single-instruction-multiple-data

SMP symmetric multiprocessor/multiprocessing

SP single precision

SPMD single-program-multiple-data

TE transverse electric

TM transverse magnetic

#### **NVIDIA-specific abbreviations**

CUDA Compute Unified Device Architecture

GPC graphics processing cluster

SFU special function unit

SIMT single-instruction-multiple-threads

SM symmetric multiprocessor

SP stream processor

TP thread processor

TPC thread/texture processing cluster

#### **AMD-specific abbreviations**

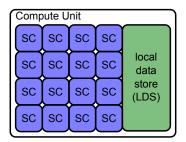

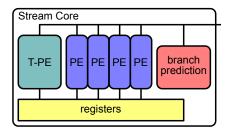

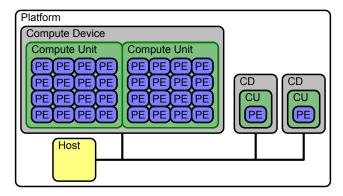

CD compute device CU compute unit

PE processing element

SC stream core

T-PE thick PE

### Chapter 1

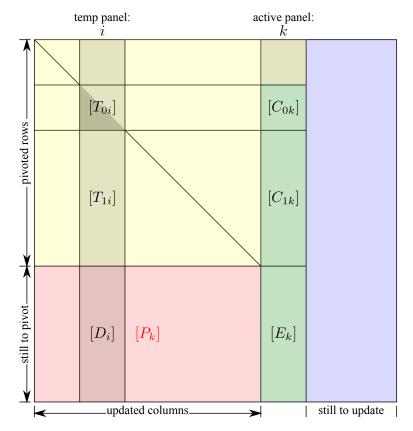

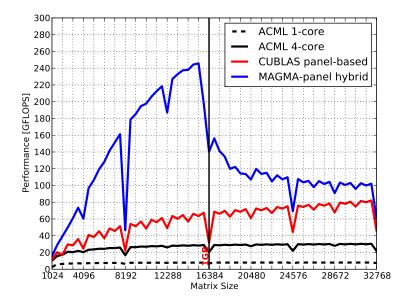

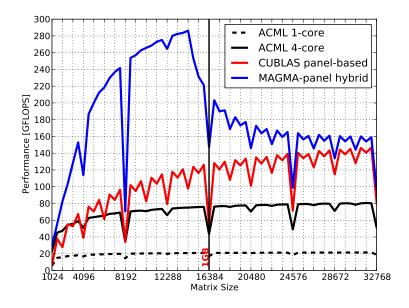

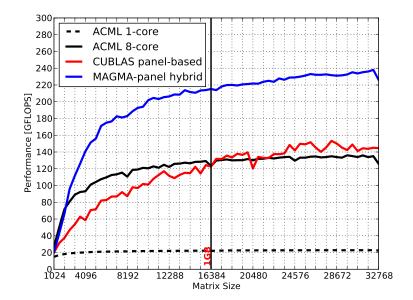

### Introduction

In the field of computational electromagnetics (CEM), like most scientific or engineering disciplines, there is a constant drive for the solution and understanding of more complex problems. Unfortunately, the solution of these problems comes at an increased cost in terms of computational as well as storage requirements.

Although the computational power at our immediate disposal has increased dramatically with time, much of that improved performance has been due to frequency scaling which was halted just after the start of this century due to power requirements [1]. In its stead, computer system and architecture designers have made ever increasing use of parallelism to keep the growth in performance alive. The power of this parallelism is evident in the performance of the fastest – according to the Top500 list [2] – supercomputers in the world, where the performance has increased by four orders of magnitude over the past 17 years.

It is clear then at this point that the future, and in fact the present, are both highly parallel. One of the consequences of the shift to increasing the number of cores or processors in a computer system, instead of simply scaling the frequency at which they operate, is that software that is not designed to run in parallel no longer gets any faster for nothing – hence the phrase "The Free Lunch is Over", that is the title of [1]. It is then imperative that existing implementations and techniques be revisited and their feasibility for parallel execution considered.

One of the fields where the move towards massive parallelism is most evident is in the field of general purpose GPU (GPGPU) computing. Although this discipline has been around in some form or another since the late 1970s, the release of more powerful hardware as well as a number of high-level languages over the past 10 years has really seen the field move from strength to strength. One of the most notable additions, and the one used in this dissertation, is the CUDA software and hardware architecture released by NVIDIA in November of 2006 [3]. A quick glance at the CUDA Zone [4] gives an indication of the vast array of applications that now make use of this acceleration technology.

Although a number of competing architectures exist, CUDA was one of the first to provide a software environment that was straightforward enough for anybody with a reasonable amount of general programming knowledge to grasp. Furthermore, a number of accelerated versions of common routines in linear algebra and signal processing were made available early on and resulted in out-of-the-box speedups for many applications. It is this software advantage, coupled with incremental increases in hardware capabilities, that has been the main driving force in the high adoption rate of CUDA and lead to the point where three of the top five fastest computers in the world – including the number one – now make use of these accelerators.

In this dissertation two well known matrix-based techniques in the field of computational electromagnetics are considered, namely the Method of Moments (MOM) for scattering problems and the Finite Element Method (FEM) for waveguide cutoff and dispersion analysis. More specifically, the parallelisation and resultant acceleration of these methods using CUDA-capable

GPUs is investigated. The fact that both methods are matrix-based allows for the adaptation and reuse of many of the advancements from GPU-based linear algebra to achieve speedups in some of the phases of the respective solution processes. This also means that improvements made here can be directly applied to a wide range of other applications – as long as the same class of linear algebra routines are used.

For the finite element problems considered, the part of the solution that can be expressed in terms of linear algebra contributes most significantly to the total computational cost. This is not always so for the MOM, and as such, the other phases of the solution process are also considered for acceleration. In this case, there are no libraries available the allow for the rapid development of an accelerated implementation, and instead an implementation must be developed from scratch. This does however allow for a better understanding of the parallel implementation.

It should be noted that although GPUs are an attractive option at present, largely due to the fact that their prices are kept low by the computer gaming industry, in their current implementation they still represent a relatively young technology – especially in the field of general purpose computing. Although there is evidence to the contrary [5, 6], it may be that these architectures will fade away to give rise to something else. Even if this is the case, there is a good chance that whatever replaces them will be even more parallel and any knowledge and experience gained in the porting of existing applications or the development of new code for GPU execution will prove invaluable.

#### 1.1 Research objectives

Apart from the overarching aim of investigating the use of GPU-based acceleration in the field of computational electromagnetics, this research sets out to address a number of other points of interest. It should be noted that only a small sub-set of computational electromagnetic problems are considered, namely the Method of Moments (MOM) as applied to scattering analysis and the Finite Element Method (FEM) for the analysis of bounded waveguide structures.

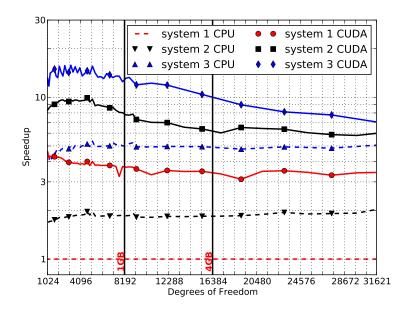

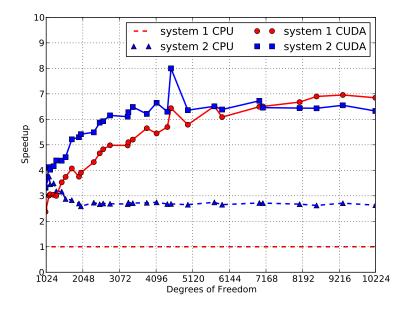

For any GPU-based implementation, a positive result would be a speedup of more than  $1 \times$  relative to a CPU implementation of a given method. Although this is the case here, it is not the only factor considered. A number of comparative benchmarks across multiple platforms allow for the investigation of the relative performance of GPU and CPU implementations on a single platform, as well as to the relative strengths of the different machines with and without GPU acceleration.

This benchmarking strategy allows for two issues to be addressed. The first of these is whether a GPU-accelerated implementation can enable high-end compute node performance on more standard systems. Secondly, the viability of GPUs as an upgrade path for existing systems is considered, allowing for an increase in the useful – and performance-competitive – lifespan of older systems at the fraction of the cost of a full replacements.

One of the factors limiting the usefulness of GPUs in general purpose computing is the amount of memory available on such devices. The implementations presented here attempt – wherever possible – to overcome this limitation. At this point it should be noted that this research is limited to investigating the performance of single systems each with a single GPU in use. Since the distributed use-case is not considered here, an implementation that aims to overcome the memory limitations of a GPU is considered to be successful if it is able to deal with problem sizes comparable to those that can be accommodated in the primary memory installed in the system.

A second factor impeding the widespread adoption of GPUs as accelerators is the (perceived) steepness of the learning curve associated with their programming. Although this may have been true in the past, where GPUs were bent to the will of a programmer using a number of graphics programming tricks, the development of compute-specific languages such as CUDA and OpenCL

has greatly improved the ease with which these devices can be programmed. The development of a number of high-level libraries that are widely used has also lowered the barrier to entry and increased the adoption rate.

The work presented here aims to address this second hurdle in a number of ways. Firstly, existing, freely available libraries are used. This route offers the most plug-and-play approach to first-time developers or people wishing to experiment with various implementations. An attempt is also made to keep much of the discussion and implementations as general as possible so as to ensure that the results are of interest to a wide range of applications.

An important aspect that is also considered in the work is that of CPU and GPU codevelopment. This stems from the realisation that no – or at least very few – GPU-based implementations exist alone. Generally they are either ported from an existing CPU implementation, or a CPU implementation is also required for compatibility reasons. The time and effort involved in developing and maintaining two versions of the same code can be prohibitive, especially in a commercial setting or any application where requirements and features change often.

#### 1.2 Contributions

This work represents a number of contributions that result from the consideration of the research objectives discussed in Section 1.1. When considered in its entirety, an investigation into the use of GPU-acceleration in computational electromagnetic matrix-based methods is presented. Apart from addressing the overarching aim of this dissertation, this can be considered a useful contribution in it own right, as it summarises the work presented in a number of sources dealing with the GPU acceleration of a single CEM method. That is, either the Finite Element Method or the Method of Moments.

The GPU acceleration of the CEM methods considered uses a set of typical problems from each method as the starting point for the implementation as well as the results presented. This use of simple problems and a tutorial-like approach to many of the implementation discussions means that this research should be useful to anyone wishing to develop their own GPU-enabled versions of existing methods.

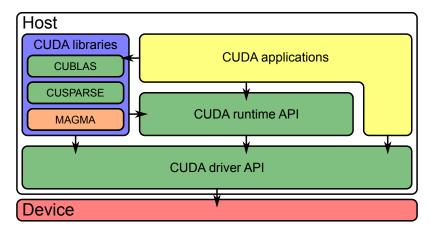

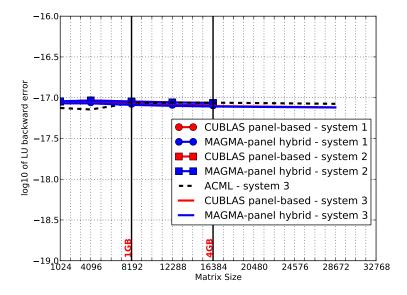

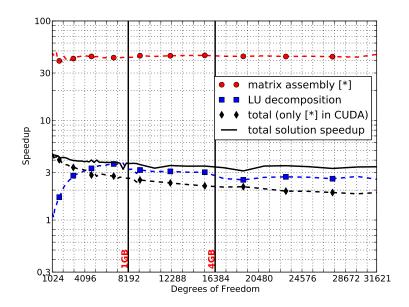

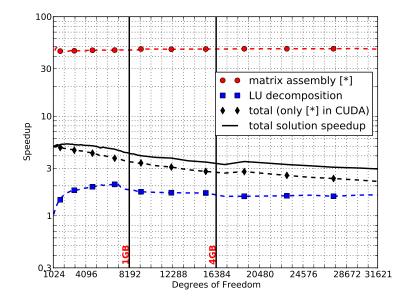

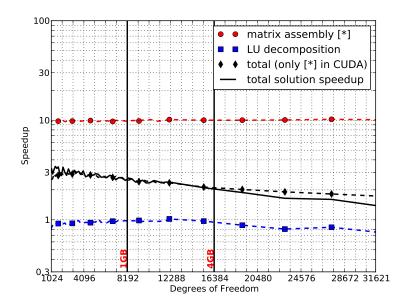

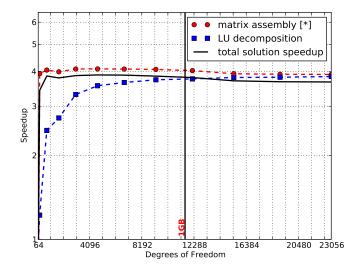

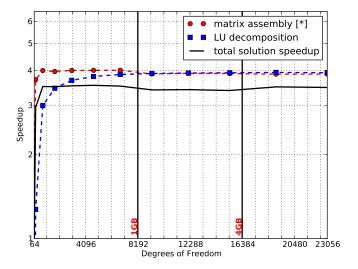

Since both the MOM and the FEM are matrix-based, they allow for the use of existing accelerated linear algebra routines such as CUBLAS [7] and MAGMA [8]. In the case of the LU decomposition, the MAGMA implementation is extended to allow for the solutions of problems that are larger than can be accommodated by the memory installed on the GPU. This is in keeping with one of the aims of this research with the accelerated GPU implementation able to outperform a multi-core platform-optimised CPU implementation even in cases where the amount of memory required is 16 times greater than the amount available to the GPU. This memory-resilient LU decomposition is also used as part of the Method of Moments solution process. The research into the LU decomposition led to a publication in *Electronics Letters* [9].

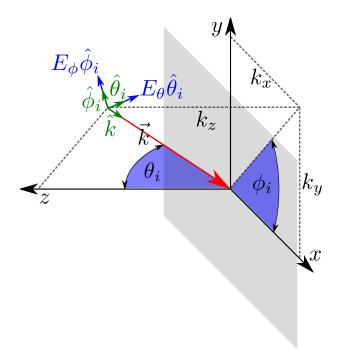

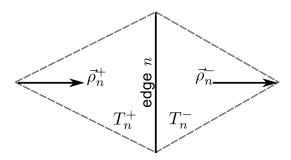

In the case of the Method of Moments, a seminal work in the field – the 1982 paper by Rao, Wilton, and Glisson [10] – is considered as a starting point for the discussion of the GPU acceleration of the MOM solution process. When compared to existing GPU-based MOM implementations, the work presented here is novel in a number of ways. These include the implementation of the entire solution process in both native double precision – as supported by the latest generation of GPUs – as well as the direct application to the formulation and problems presented in [10] resulting in the publication of [11] and [12]. The MOM process presented here is also implemented in such a way so as to overcome the restrictions on the problem size due to limited GPU memory.

For the Finite Element Method, the GPU acceleration of another set of canonical problems is considered. That of cutoff and dispersion analysis of waveguide structures [13]. The acceleration

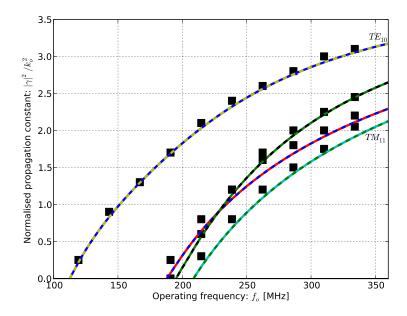

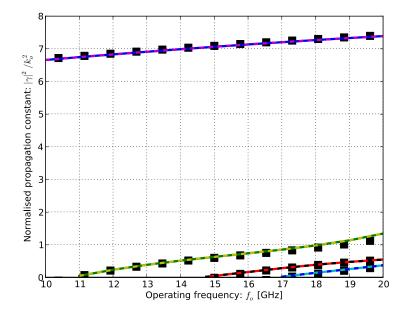

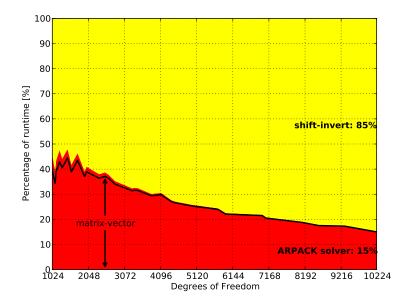

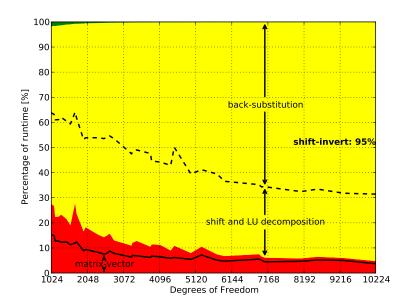

of these problems is approached from a linear algebra perspective, and focuses on the solution of the eigenvalue problems that results as part of the FEM solution process. The GPU-accelerated (using both CUBLAS and MAGMA) ARPACK [14] implementation that results is to the author's knowledge the first to deal with generalised eigenvalue problems, and more specifically those that results from the FEM analysis of waveguide structures. The work presented is a continuation of that published in [15], and although only relatively small dense matrix problems are considered, the findings lay excellent groundwork for continued research.

Another contribution of both the MOM and the FEM implementations is in addressing the research objective of CPU and CUDA co-development. In these implementations CPU- and GPU-accelerated implementations are developed in parallel, with a methodology followed in each case that allows for the sharing of much of the code – especially in the case of the MOM implementation – between the two versions. This sharing of code greatly simplifies the addition of new features and the unavoidable debugging that will be required to implement them correctly.

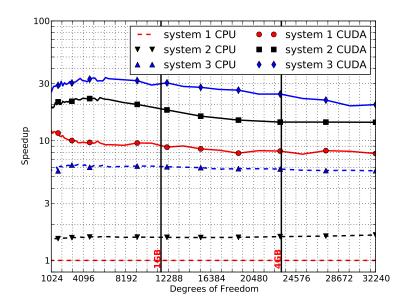

A final general contribution is a set of comparative benchmarks over three (two in the case of the FEM results) different systems with different CPU and GPU capabilities. Of these systems, one is significantly older than the other two with a CPU performance that is lower by at least a factor two. The results presented show that not only does the addition of a GPU to the older system improve its achievable performance, but that the improved performance is such that the old machine is able to compete with the (unaccelerated) newer systems for most of the problems considered. The exception here is that the most expensive of the new systems still offers better performance for double precision computation, although it should be added that the cost of the new system is about 25 times higher than the GPU used to upgrade the slower system. One of the major contributions of these comparative performance results is that they allow for better informed upgrade or replacement decisions, which can result not only in a monetary saving, but also in the reduction of waste.

Although not mentioned in Section 1.1, one of the objectives for the FEM component of this research is the identification of a suitable open-source software environment to be used for finite element modelling in CEM. The software chosen, FEniCS, offers a set of powerful tools such as the ability to describe the finite element formulations in a very high-level language. The FEM implementations presented here use FEniCS and represent its first application to electromagnetic waveguide problems. The examples considered here are also to be included as part of the set of demos available at [16], thus contributing directly to the open-source community.

### 1.3 Chapter summary

The main body of work is divided into six chapters, with this chapter constituting the fist and providing a general overview of the dissertation. A number of points are addressed including a general motivation, as well as discussing the research aims and contributions of the work.

Chapter 2 provides an introduction to general purpose GPU computing and provides a history of the field, as well as a comparison of two current technologies, namely CUDA and OpenCL, of which the former is used for the implementations in this dissertation. The chapter serves to introduce much of the CUDA-specific terminology used in the rest of the dissertation, and provides a few simple examples to explain the workings of the architecture.

In Chapter 3 the application of CUDA to acceleration of dense numerical linear algebra (NLA) is considered. This includes a quick discussion on NLA in general including the BLAS and LAPACK libraries. As far as the CUDA aspects are concerned, libraries such as CULA Tools, MAGMA, and CUBLAS are discussed with the latter two subsequently used in the implementation that follows. The implementation sees the mapping of traditional out-of-core LU decomposition techniques to the CUDA device-host relationship and result in two versions of the LAPACK-compatible LU decomposition. These are not only faster than multi-core CPU imple-

mentations, but are in addition, not limited by the amount of memory available on the GPUs used. The chapter also introduces the benchmark systems used for the performance comparisons in this dissertation, with performance results for the LU decomposition implementations given.

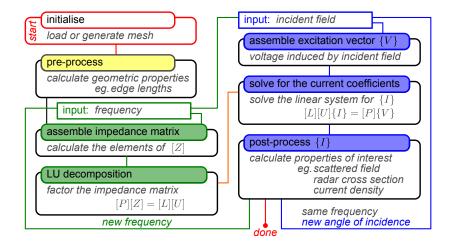

The LU decomposition presented in Chapter 3 is used as part of the Method of Moments solution process which is discussed in Chapter 4. Here, the formulation from [10] is adapted for execution on CUDA GPUs, with a parallel CPU implementation also developed. This allows for the introduction of the CPU and GPU co-development methods, where much of the code is shared between the two implementations. This section also sees a large number of comparative benchmarks obtained for the sample problem considered. Results indicate that the implementation is resilient in terms of the limited amount of memory available on the CUDA devices used.

Chapter 5 continues the discussion of CUDA-accelerated matrix-based methods in CEM with an investigation of the acceleration of the finite element analysis of waveguide structure. Here, both cutoff and dispersion problems are considered. The CUDA acceleration is achieved by using the dense NLA routines supplied by CUBLAS and MAGMA to construct a generalised eigenvalue problem solver that is based on ARPACK. A set of comparative benchmarking results is also presented. In addition to the accelerated eigensolver, the chapter introduces the FEniCS software that is used for the implementation of the finite element formulations discussed. General conclusions and recommendations for future work are presented in Chapter 6, followed by two appendices, Appendix 6.2 and Appendix 6.2, which provide additional results not included as part of the MOM and FEM chapters (Chapter 4 and Chapter 5), respectively.

### Chapter 2

# General purpose GPU computing

General purpose GPU (GPGPU) computing is the use of graphics processing units to perform computations for which they were not initially designed. Although this practice has been around for some time, its adoption in a wide variety of fields including scientific computing, computational finance, and engineering has of late seen a remarkable increase. Much of this is a result of the very attractive performance promises made by such devices, as well as the improvement in the increasing ease with which they can be employed to perform arbitrary computational tasks.

This chapter aims to present an overview of GPGPU computing so as to provide a background for its application to computational electromagnetic problems in later chapters. Discussion starts with a general overview of parallel computation in Section 2.1, which is followed by the history of general purpose GPU computing in Section 2.2.

Sections 2.3 through 2.5 address CUDA by NVIDIA, the ATI Stream SDK from AMD, and OpenCL. Special attention is given to NVIDIA CUDA with much of the discussion going into great detail, as this is the language of choice for the implementations and results presented in Chapter 3, Chapter 4, and Chapter 5. Many of the concepts illustrated can, however, be applied to other technologies with one-to-one correspondences existing in many cases. The chapter is concluded with a brief discussion on possible future developments in the field of GPU computing.

### 2.1 An overview of parallel computing

In this section, a brief overview of parallel computing in general is presented. This serves to provide a basis on which the subsequent sections on GPGPU computing build. Furthermore, much of the terminology that is used in this chapter and the remainder of the dissertation is introduced.

When parallel computing is mentioned, one typically envisions rooms filled with a large number of connected computers with computational capabilities far outstripping a regular desktop or notebook computer. Twice a year a list is released where the performance of the top 500 of these supercomputers is showcased [2] and there is often much competition for the coveted top position. The performance – measured in floating-point operations per second (FLOPS) – of the machines on the list has increased exponentially since its inception in June of 1993, with the current (November 2010) number 1 system achieving a performance of 2.57 PFLOPS (thousand trillion floating-point operations per second). This is up from 59.7 GFLOPS (billion floating-point operations per second) in June of 1993 and represents an improvement of more than 43000 times over less than 20 years.

Most of the systems in the current Top500 list are built as clusters of thousands of compute nodes and thus follow the distributed computing model [17]. In this model each of the nodes has its own local memory and software running on the system must rely on a message passing protocol such as MPI [18] to ensure that each of the nodes has the data it requires. In such

systems each of the compute nodes is typically a fully-fledged multi-core system with a small number (10–20) of cores. Since each of these cores has access to the memory local to the node, message passing is not required for communication on a single node [17]. In this case, the shared memory parallel model or symmetric multiprocessor (SMP) model can be used, with tools such as OpenMP [19] available to realise such implementations.

It should be noted that although supercomputers such as those on the Top500 list have been making use of multiple processors to achieve performance for some time now, it represents a relatively recent development in the main-stream computing sector. The first consumer-level multi-core processors appeared in the early 2000s as a direct results of the increasing power requirements associated with ramping up the frequency as which the processors operate (which had been one of the main sources of the performance improvements up to that point) [1]. The multi-core processor is now ubiquitous in everyday computing and most desktop machines can be seen as an implementation of the shared memory parallel model. These multi-core nodes or hosts are examples of multiple-instruction-multiple-data (MIMD) machines, that allows for multiple separate instructions to operate on different data in parallel [20].

Just as there are different models for the description of parallel computers, whether they be the distributed or massively parallel processor systems of the Top500 list or a standard desktop computer, there are a number of models that define the way in which parallelisation can be achieved. These are bit-level, instruction-level, task, and data parallelism [17]. The first two of these are generally closely tied to hardware and are only discussed briefly before addressing task and data parallelism. Bit-level parallelism is leveraged to increase the performance of a processor by increasing the word size (the number of bits that can be operated on at a time) of the processor. This is evident in the increase from 8 bits in early x86 computers to 64 bits in the current x86-64 architecture. Instruction-level parallelism relies on the fact that any program executing on a computer consists of a stream of instructions and that many of the instructions can be reordered and executed in parallel without changing the results of the program.

In contrast to bit-level and instruction-level parallelism, task and data parallelism are more closely related to the algorithm or application being implemented [17] and not the underlying hardware architecture. It should, however, be noted that there do exists architectures (including the GPUs discussed later in this chapter) that are specifically designed for data-parallel execution. An application or algorithm exhibits task parallelism (also called function parallelism) when entirely different calculations are to be performed on the same or different data [17] and these tasks can be performed in parallel. A contrived example of this is an application that needs to compute the sum and the products of lists of numbers. Regardless of whether the numbers are from different or the same lists, these operations (the sum and the product) are independent and can be performed concurrently.

Data parallelism involves performing the same (or similar) operations or functions on individual elements of a large data structure [17]. This type of parallelism is often achieved by examining loops present in an implementation and executing independent portions in parallel. An example would be the addition of the corresponding elements in two arrays, where it is clear that each of the new data elements to be computed are independent and the operations can thus be performed in parallel. Note that the data parallel model as discussed in [17] is a generalisation of the single-instruction-multiple-data (SIMD) model that forms part of Flynn's taxonomy [20], and later evolved into the single-program-multiple-data (SPMD) approach. An alternative is the MIMD approach – which can be compared to task parallelism in some cases – already mentioned with reference to general shared-memory and multi-core machines.

Applications usually exhibit both task and data parallelism and often have a number of different levels at which these parallelisations can be implemented [17]. That is to say that a particular algorithm could be implemented as a set of parallel tasks performed per data element (task parallelism within data parallelism) or as a set of separate tasks which are each data parallel

(data parallelism within task parallelism). It should be noted that, although task parallelism is often relatively easy to implement using message passing or a multi-threaded implementation, the amount of parallelism available is usually modest and does not increase much with the size of the problem being considered [17]. Data parallelism on the other hand does grow with the size of the data set and allows for the utilisation of massively parallel processors such as GPUs.

Although this section aims to provide a relatively complete overview of the parallel computing landscape, the scope of the field makes this impossible. An additional source of information is [21], which provides a number of insights including the matching of algorithms to a specific architecture. A field that has not been mentioned at all in this section is that of grid computing. This is addressed with specific reference to computational electromagnetic problems in [22].

### 2.2 History of GPU computing

Any history of GPGPU computing should at least mention the Ikonas system of 1978 [23]. This system was developed as a programmable raster display system for cockpit instrumentation and was quite large by today's standards. Although other such systems have been developed [24, 25], the rest of the history addresses the use of consumer-level hardware such as the GPUs originally introduced by NVIDIA in 1999 [26].

Due to the inherently parallel nature of graphics rendering – the processing of geometric, texture and lighting data to generate a scene for display on a computer monitor by calculating the required properties of each pixel [27] – and the ever increasing capabilities of GPUs, the scientific community started investigating their use in general purpose computation shortly after their introduction. Initial attempts were based on utilising the rendering pipeline of the GPU directly using OpenGL, which was originally intended for writing 2D and 3D graphics applications. Although this approach did result in some impressive speedups for the time, the process was quite complex and this hindered large scale adoption.

As the hardware developed and became more programmable (predominantly for applying effects in computer visualisations and games), a number of higher level languages were also developed that greatly simplified the programming process. These include shader languages, such as Cg (2002), GLSL (2002), and HLSL (2002), whose primary goal was not general GPU computation, but the description of more complex scenes for use in computer generated imagery.

Later, a number of academic languages were developed that the were specifically targeted to GPGPU applications. These languages typically considered the GPU as a stream processor performing some operation (or kernel) on a stream of input data to produce the desired output data stream. In many cases the same operation is performed on each element of the input stream. This process of applying the same operation to a number of data elements (usually in parallel) is referred to as the single-instruction-multiple-data (SIMD) model, as opposed to the multiple-instruction-multiple-data (MIMD) model typically followed by conventional CPUs. Two such languages that deserve some mention are BrookGPU (2003) and Sh (2003) which have each since been developed into commercial offerings. The Sh language and API was released as PeakStream, soon after which it was purchased by Google with no public development now taking place. BrookGPU became RapidMind and is now owned by Intel. This seemingly forms the core of Ct (C for Throughput Computing), intended as a data-parallel programming language to leverage the power of multi-core processors.

The end of 2006 saw the birth of what can be considered modern general purpose GPU computing, with both NVIDIA and AMD releasing products that offered previously unheard of programmability and promises of computational power [3, 28]. The history of what would become the ATI Stream SDK from AMD and the Compute Unified Device Architecture (CUDA) from NVIDIA is presented briefly, after which CUDA is considered in some detail in Section 2.3. A comparative overview of the ATI Stream SDK is presented in Section 2.4.

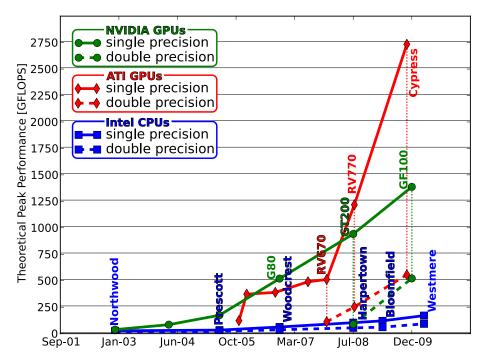

A comparative performance timeline for the two technologies is given in Figure 2.1, with data taken from [29] and [30]. As can be seen from the figure, the performance promised by the devices is one of the primary reasons that there has been so much interest in utilising these technologies for general purpose computation. It should be pointed out that there are a number of caveats that should be considered when comparing theoretical peak performance figures such as these. A comparative study of GPU vs CPU performance is provided in [31], and lists a number of these.

One of the indications of the coming of age of general purpose GPU computing was the inclusion of systems using this technology in the twice yearly Top500 list discussed in Section 2.1 [2]. The Tsubame cluster from Tokyo Institute of Technology improved its position to 29<sup>th</sup> in the November 2008 list with the inclusion of 170 Tesla S1070 units from NVIDIA. The November 2009 list saw the inclusion in the fifth position of the Tianhe-1 system from National Super Computer Centre in China which used AMD/ATI GPUs to accelerate computation. Where the Tsubame system used Tesla units designed for the high-performance computing segment, the Tianhe-1 used two Radeon 4870 (high-end consumer) devices in each node [2].

The high point in terms of GPU computing and the Top500 list came with the announcement of the November 2010 results which has 10 of the systems using NVIDIA GPUs for acceleration with AMD/ATI devices being used by two systems [2]. The systems using NVIDIA GPUs include three of the top five systems. The Tianhe-1A system at the National Supercomputing Center in Tianjin, China occupies the first place, with the Nebulae system, also from China, in third (down from second in June 2010). The final GPU-enabled system in the top five is the Tsubame 2.0 from the Tokyo Institute of Technology in fifth position.

#### 2.2.1 History of NVIDIA CUDA

Although a number of NVIDIA GPUs had been used for the purpose of GPGPU computation with some success up until that point [32, 33], the real birth of NVIDIA's GPGPU computing

**Figure 2.1:** Figure showing the performance timelines of NVIDIA GPUs, ATI (AMD) GPUs, and Intel CPUs over the past seven years. Theoretical peak performance curves are shown for both single precision (solid curves) and double precision (dashed curves) and are adapted from [29] and [30].

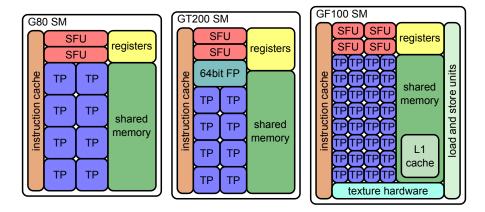

effort came at the end of 2006 with the release of their G80 architecture [3]. From a graphics processing point of view, this new architecture was an answer to the requirements imposed by the DirectX 10 API – which is to say that all the operations in a graphics pipeline be performed by unified shaders, and not by separate vertex and pixel shaders as was the case in the past [27, 34]. Thus instead of the graphics pipeline containing (possibly hundreds [3] of) sequential pipeline stages, all the required operations are performed by a standardised shader core – hence the term "unified shader".

Although the G80 architecture was originally intended for graphics, it was also designed in such a way as to provide an entry into the GPGPU market that, in 2006, was really still in its infancy [3]. The hardware formed part of a larger architecture called the Compute Unified Device Architecture (CUDA), providing a well-defined programming model and software tools to harness the power of the GPUs for general purpose computation.

Since the first public release of the CUDA toolkit at the beginning of 2007, the API has developed steadily, providing more functionality and being consistantly updated to accommodate the capabilities of new iterations of the hardware architecture. These include the addition of double precision floating-point support in the GT200 architecture [35], as well as a unified memory model in the Fermi architecture [26].

Although the original G80 architecture was a graphics architecture with the ability to perform general purpose computation, the interest shown from the high performance computing (HPC) sector was phenomenal and led to the development of the Tesla range of products specifically targeted at HPC. These devices are in essences NVIDIA GPU-based devices with no graphics output capabilities. They also offer more memory than their consumer-level counterparts and thus allow for the processing of larger computational problems.

#### 2.2.2 History of the ATI Stream SDK

At about the same time that NVIDIA released the G80 architecture and CUDA, AMD/ATI released CTM (Close To Metal), which gave programmers relatively low-level control over the graphics processing hardware for general purpose GPU computing [28]. This low-level language later evolved into the Compute Abstraction Layer (CAL) and became the supporting API layer for the high-level ATI Brook+. Their combination was called the ATI Stream SDK [36] – AMD's answer to CUDA.

In addition to advances on the software front, hardware from AMD also evolved rapidly. AMD introduced the first ever GPU device with native double precision support, the FireStream 9710. It was six months before NVIDIA brought the GT200 – their first double precision device – to market. The next FireSteam device, the FireStream 9250 was the first device to offer more than 1 TFLOP (one trillion floating-point operations per second) in peak theoretical single precision performance in a very compact form factor [37].

Soon after the ratification of OpenCL (Open Compute Language) [38] in December 2008, AMD decided to replace ATI Brook+ with OpenCL as the development language for programming AMD devices [39]. One reason for this change may be the hope that the use of an industry standard, multi-platform development language will be able to reduce the lead that NVIDIA has enjoyed in the GPGPU segment. Since multi-core CPUs can also be used as OpenCL compute devices [40], this also means that AMD can offer a unified heterogeneous computing solution [39].

Note that, although ATI was originally a separate company, AMD acquired ATI in mid 2006, only a few months before the release of CTM [28]. Although the ATI brand was retained for some time, it was replaced by AMD in August of 2010. Thus there exist a number of devices that – although developed by AMD – have ATI branding, whereas future devices will bear the AMD moniker. As such AMD and ATI are used interchangeably throughout the rest of this

chapter. The purchase of ATI seems to have come to fruition, with the release of AMD's Fusion platform at the end of 2010 [5]. This platform sees the integration of a GPU – acting as a parallel floating-point accelerator – and a number of x86 cores onto a single processor.

#### 2.3 NVIDIA CUDA

As already mentioned, changes to the rendering requirements brought about by APIs such as DirectX 10 lead to new architectures being developed by hardware vendors such as NVIDIA and ATI. The G80 architecture by NVIDIA saw the implementation of a unified shader design [3]. This design saw the traditional rendering pipeling consisting of various stages being replaced by a number of identical shading cores. These cores are highly programmable, which allows them to perform any of the functions that would normally be executed by special-purpose pipeline stages and include both pixel and vertex shading, previously handled by separate hardware.

This change in architecture also had the advantage that the programmability of the hardware for performing general purpose computational tasks was greatly improved. The Compute Unified Device Architecture (CUDA) from NVIDIA is a general purpose parallel computing architecture and provides a computing model, as well as an instruction set architecture (ISA) to leverage the power of the underlying parallel hardware [29], a CUDA-capable device such as a GPU. Due to the multiple market segments in the GPU industry, it is important that such an architecture is scalable, as it allows for development resources to be shared across an entire line of GPUs. In addition, this lends itself well to scalable implementations in terms of performance - often quite difficult to achieve in a traditional parallel programming environment.

#### 2.3.1 Programming model

Before considering the actual hardware associated with a CUDA device, the programming model is addressed. The reasoning for this is that although future generations of hardware may be more complex and provide advanced capabilities, their support for the programming model is guaranteed. Thus if one can develop code for a current generation, this should run on future hardware with little or no modification.

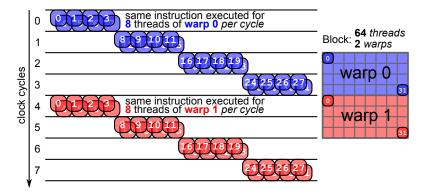

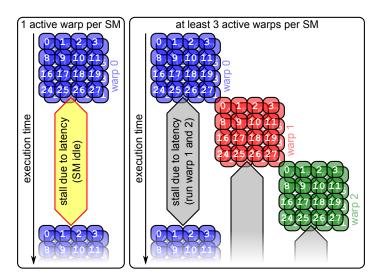

The CUDA programming model consists of three key abstractions, namely, a hierarchy of thread groups, shared memories, and barrier synchronisation, all of which are exposed to the programmer using a series of programming language extensions. The abstractions allow for the management of fine-grained data parallelism at a thread level, nested within coarse-grained data parallelism and task parallelism (which have both been discussed in Section 2.1). This forces the programmer to consider the problem domain and partition it into coarse sub-problems that can be solved independently (possibly in parallel) with each of these sub-problems also being decomposed to a thread level. This is similar to the approach followed by stream processing [41] and since the coarse blocks of work must be independent by definition, their parallel computation should scale well.

It should be noted that the concept of a thread used here is not the same as a thread in a classical CPU-based multi-threaded sense (as in the case of OpenMP [19]). A CUDA GPU thread is a lightweight entity whose context can be switched with zero overhead [27]. This is made possible by the GigaThread engine by NVIDIA which allows for thousands of threads to be in flight during execution [3, 26, 35]. Where the term thread is used in this chapter, it refers to a CUDA thread and not a CPU thread unless otherwise specified.

In order to further the discussion of the CUDA programming model, consider a simple example of adding the contents of two float arrays. The CPU-based C routines add() is shown in Listing 2.1 with the array c being calculated as the sum of a and b (for each of the N elements in the arrays). This is the same example that serves as an introduction to CUDA in [42].

Listing 2.1: An example for adding two float arrays of length N implemented in C.

```

void add ( int N, const float *a, const float *b, float *c )

{

int i = 0;

for ( i = 0; i < N; i++ )

{

c[i] = a[i] + b[i];

}

}</pre>

```

#### CUDA kernel definition

As with stream processing [43], the basic unit where computation can take place in CUDA is known as a kernel. In CUDA terms a kernel is a routine, usually written in C, that is executed on a CUDA-capable device. Listing 2.2 shows the CUDA kernel, add\_kernel(), for the example discussed and shown in Listing 2.1.

Listing 2.2: A simple example of a CUDA kernel for adding two float arrays of length N.

```

__global__ void add_kernel ( int N, const float *pdev_a, const float *pdev_b,

float *pdev_c )

{

// calculate the data index for this instance of the kernel

int i = threadIdx.x + bockDim.x * blockIdx.x;

if ( i < N )

{

// calculate the output value for the given data element

pdev_c[i] = pdev_a[i] + pdev_b[i];

}

}</pre>

```

Listing 2.2 illustrates another important point – the programmability of CUDA-capable devices is provided by a number of C language extensions. This will be discussed in more detail in Section 2.3.4. For now it is sufficient to note that a CUDA kernel is indicated by the \_\_global\_\_qualifier and must be of return type void.

Also evident in Listing 2.2 is that no explicit iterations are performed over the data elements in the arrays. This is due to the fact that the CUDA environment automatically handles the execution of the same kernel for each data element in the problem domain, with many of the executions occurring concurrently. The kernel invocation will be discussed in more detail later.

#### CUDA thread organisation

Before continuing the discussion of this kernel example, the data segmentation options provided by CUDA need to be discussed. In terms of segmentation, the finest granularity is that of a single CUDA thread. When a kernel, such as the one given in Listing 2.2, is executed, it is executed for every thread that has been defined.

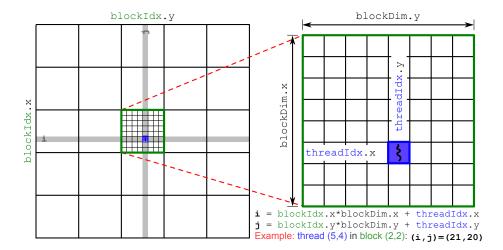

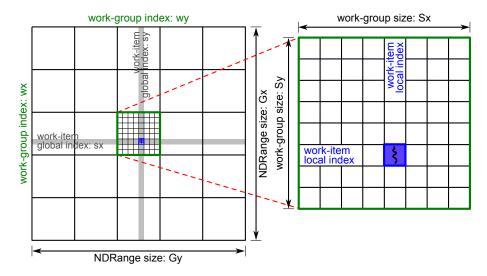

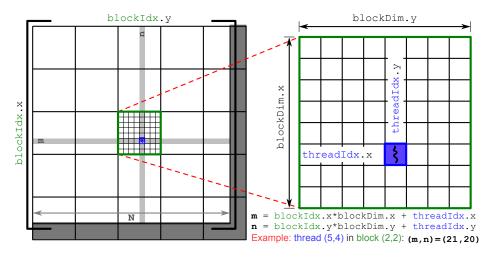

Although these threads allow a fine-grained access to data, it is impractical to use them to individually address the elements in large datasets - especially if the size of the dataset exceeds the number of available threads. Threads are thus grouped into one-, two- or three-dimensional blocks, each with identical dimensions, providing a coarser level of control over the segmentation of the problem space. The blocks are further arranged in a one- or two-dimensional grid at the highest level. An example of such a partitioning is shown in Figure 2.2. This style of

Figure 2.2: Diagram showing the grouping of threads into  $8 \times 8$  blocks in a  $5 \times 5$  grid for computation on a CUDA device. Also shown is the calculation of the global index ((i,j)) of a thread from local thread and block information. Note that although the blocks and grid shown are square, this is not a prerequisite [29].

organisation lends itself particularly well to partitioning one- or two-dimensional data such as vectors, matrices or images. Furthermore, since the local index (in each dimension) of a thread within a block, as well size and position of the block in the grid can be accessed at runtime, the global index of the thread can easily be calculated. This global index could then correspond to a position of a data element in the input or output stream, for example.

Referring to the simple kernel example presented in Listing 2.2, the use of built-in variables threadIdx, blockDim, and blockIdx is shown to calculate the global index of a thread to identify the indices of the array elements that are being operated on by the kernel. These variable are structures with fields x, y, and z depending on their dimension. The use of these variables to calculate the global indices for a two-dimensional problem is also illustrated in Figure 2.2. Here, the global index of a thread in the x direction is calculated as: blockIdx.x\*blockDim.x + threadIdx.x, for example.

#### Hierarchical CUDA memory model

As with many other processor architectures, CUDA devices have a hierarchical memory model, with some of the memory types shown in Table 2.1. A number of other characteristics of the memory types are also shown, including whether or not the memory offers cached access and whether it is read-only. If we consider as an example the shared memory, it is located on chip (explained in more detail in Section 2.3.2), offers fast low latency read-write access, and thus does not need to be cached. In fact, in many algorithms this shared memory is used as a user managed cache for optimal performance [27]. Furthermore, the shared memory can be accessed by all the threads in a block allowing for data reuse and communication between these threads. Due to the fact that the execution order of threads is not known beforehand, it is often required to make use of synchronisation barriers to ensure that the contents of shared memory is consistent. This is achieved by making use of a \_\_syncthreads() function which halts execution for a thread until all threads in a block have reached that point in the code.

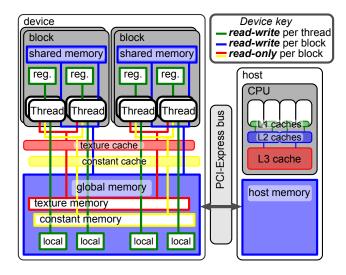

Figure 2.3 shows a graphical representation of the CUDA memory hierarchy, showing the allowed access for each memory types (indicated by the colours of the connecting lines). Also shown in the figure is an abstracted representation of a host which consists of a multi-core CPU, connected to the host memory through a hierarchy of cache memory. In the CUDA sense, the

Figure 2.3: Graphical representation showing the memory hierarchy associated with a CUDA device. Red (-) and yellow (-) pathways represent per-thread read-only memories whereas green (-) and blue (-) pathways represent read-write memories that are accessible by a single thread or a block of threads, respectively. Also shown is the host and the communication with the device's global memory space over the PCI-Express bus.

host is the system where the device (CUDA GPU) is installed, with its own memory.

As seen in Table 2.1 and Figure 2.3, certain parts of the CUDA device's memory (specifically those that reside in global off-chip memory) can be accessed from the host. As part of the CUDA computational process – to be discussed in more detail shortly – data are trasferred from host memory over a bus (such as the PCI Express bus) to the required area of global memory, where they can be accessed by the threads executing on the device [29]. This need to transfer data before they can be operated on often limits the total performance (including data transfer overheads) of CUDA devices, especially for problems that only require a small amount of computation per data-element. The relatively small amount of global device memory installed, when compared to host memory, can also be a limiting factor for computation on the device.

#### The CUDA computational process

At this stage we have discussed the concept of a kernel and the segmentation of data into a grid of thread blocks. It has also been stated that CUDA automatically executes the kernel for each thread in the resultant grid. To further illustrate the CUDA computational process, consider again the kernel of Listing 2.2 used as an example thus far. The inclusion of this simple kernel

| Tab | ole <b>2.1</b> : A | summary of the t | ype a    | and | lo | cality | of various | CUDA | memory areas. |

|-----|--------------------|------------------|----------|-----|----|--------|------------|------|---------------|

| _   | 3.6                | Location         | <u> </u> | ,   | 1  |        | т          | 1    | Accessible    |

| Memory   | Location (on/off chip) | Cached | Access       | Locality | Accessible from host |

|----------|------------------------|--------|--------------|----------|----------------------|

| Register | On                     | No     | R/W          | Thread   | No                   |

| Local    | Off                    | No     | R/W          | Thread   | No                   |

| Shared   | On                     | No     | R/W          | Block    | No                   |

| Global   | Off                    | No     | R/W          | All      | Yes                  |

| Constant | Off                    | Yes    | $\mathbf{R}$ | All      | Yes                  |

| Texture  | Off                    | Yes    | $\mathbf{R}$ | All      | Yes                  |

in a computation is now addressed and introduces a number of other concepts related to GPU computing.

In Listing 2.3 all the auxiliary functions required to run the kernel on the GPU are shown. The first thing to note is that the declaration of the add() function is identical to that of the CPU-based example given in Listing 2.1. This is intentional, as the two functions are designed to perform the same calculations and are thus interchangeable.

**Listing 2.3:** An implementation of the add() routine in Listing 2.1, illustrating the invocation of the simple kernel presented in Listing 2.2 for GPU computation.

```

void add ( int N, const float *a, const float *b, float *c )

// Pointers for device memory

float *pdev_a = 0; float *pdev_b = 0; float *pdev_c = 0;

// Allocate the device memory

cudaMalloc ( (void**) &pdev_a, N*sizeof(float) );

cudaMalloc ( (void**) &pdev_b, N*sizeof(float) );

cudaMalloc ( (void**) &pdev_c, N*sizeof(float) );

// Transfer the input data to the device

cudaMemcpy ( pdev_a, a, N*sizeof(float), cudaMemcpyHostToDevice );

cudaMemcpy ( pdev_b, b, N*sizeof(float), cudaMemcpyHostToDevice );

// Setup the data segmentation

int threads_per_block = 64;

int blocks_per_grid = div_to_next ( N, threads_per_block );

// setup the block and grid using the type dim3

dim3 block ( threads_per_block, 1, 1 );

dim3 grid ( blocks_per_grid, 1, 1 );

// invoke the kernel

add_kernel <<< grid, block >>> ( N, pdev_a, pdev_b, pdev_c );

// Transfer the output data to the host

cudaMemcpy ( c, pdev_c, N*sizeof(float), cudaMemcpyDeviceToHost );

// Free the device memory

cudaFree ( pdev_a ); cudaFree ( pdev_b ); cudaFree ( pdev_c );

}

```

Since the CUDA device is an external accelerator to the host and can, in general, not access the memory of the host directly [29], it is necessary to allocate memory in the device's global memory (see Table 2.1). This can be done using the CUDA cudaMalloc() function. Listing 2.3 contains three such calls. Each call allocates the requested number of bytes in the device's global memory and modifies a pointer accordingly [29]. Thus, after the calls to cudaMalloc(), the pointers pdev\_a, pdev\_b, and pdev\_c, each contain the addresses in global GPU memory where space has been allocated for N single precision floating-point values. Here, the convention of prefixing pdev\_to pointers to device memory is used. As is the case with the standard C malloc() function, the memory that has been allocated must be freed once it is no longer needed. This is done using the cudaFree() function as shown at the end of the listing.

Once the memory has been allocated on the device, the input data (the contents of the arrays a and b, in this case) must be specified. In order to make it available on the device the data must reside in GPU memory. In order to copy the data to the device from the host, the function cudaMemcpy() is used. This is equivalent to the standard C memcpy() routine with the exception that it requires an additional parameter indicating the direction of the copy that must be performed. The possible values for this parameter are:

- cudaMemcpyHostToDevice

- cudaMemcpyDeviceToHost

- cudaMemcpyDeviceToDevice

- $\bullet \ \ {\tt cudaMemcpyHostToHost} \\$

with the names self-explanatory [44]. Note that in the code sample given in Listing 2.3, cudaMemcpyHostToDevice is used to copy the input data to the device, whereas cudaMemcpyDeviceToHost is later used to copy the computed result (stored in pdev\_c on the device) back to the host overwriting the contents of the array c.

The next step in the computational process is to segment the problem domain by dividing it into a grid of thread blocks. Since the example presented here is linear in nature, this process is quite simple, and the code to calculate the division is also given in Listing 2.3. In this case, the number of threads per block (threads\_per\_block) is fixed at 64. Using this value and the div\_to\_next() routine of Listing 2.4, the number of blocks in the grid (blocks\_per\_grid) is determined. Note that all the blocks in the grid must be of equal size and that the total number of threads must be at least equal to the length of the arrays, N.

**Listing 2.4:** A routine to calculate and return the smallest integer value k that satisfies the condition  $k*step \ge N$ . This routine is used to calculate the number of fixed-size blocks are required in a CUDA grid for a given N and with step set to the block dimension.

```

int div_to_next ( int N, int step )

{

if ( N % step )

// if N is divisible by step then simply return the quotient

return N / step;

else

// if N is not divisible by step then return the integer part of the

quotient plus 1

return N / step + 1;

}

```

As seen in Listing 2.4, if N is divisible by step (with step equal to threads\_per\_block when called from Listing 2.3), then the return value (and thus blocks\_per\_grid) is simply N/threads\_per\_block. If this is not the case, blocks\_per\_grid of Listing 2.3 is assigned the return value of N/threads\_per\_block + 1. In the latter case, the last block in the grid will have blocks\_per\_grid \*threads\_per\_block - N threads that will have no data elements associated with them. For this reason, it is important to ensure that when the kernel is executed, these threads do not attempt to access memory locations that are undefined. This is done in Listing 2.2 by checking if i < N before using i as an index in the array. An alternative is to always ensure that the amount of device memory allocated is always a multiple of the block size - effectively padding the input and output data on the device - and has been found to offer some performance improvements over the unpadded case [45].

With the number of threads and blocks determined and used to initialise the two dim3 (a struct with three int fields x, y, and z [29]) variables, block and grid, the CUDA kernel add kernel () of Listing 2.2 can be invoked. This is done in the same way as calling a standard C function, with the addition of specifying the block and grid configuration by including <<< grid, block >>> between the function name and the parameter list. This instructs the CUDA runtime library to launch the kernel for the number of threads defined by the grid. After the kernel execution, the output data can be transferred to the host as already discussed.

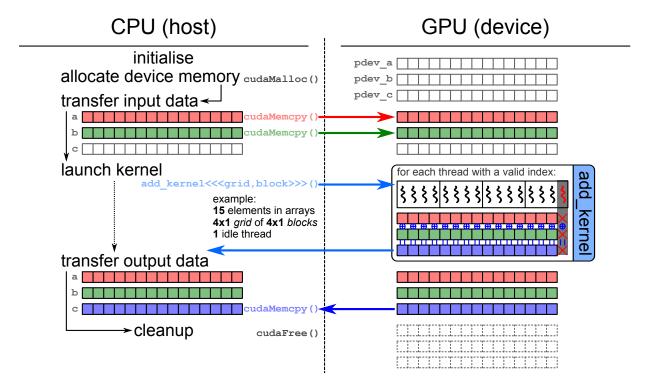

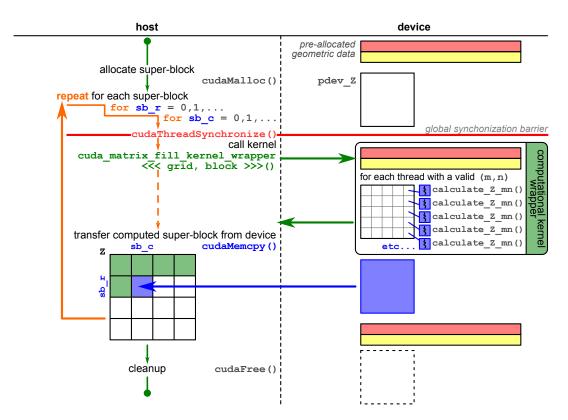

It should be noted that this kernel call is the first point where any code is executed on the device, with all code preceding and following it executing on the host. To clarify this, the process described here and corresponding to Listing 2.3 is depicted graphically in Figure 2.4.

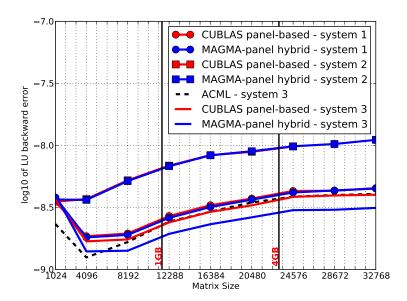

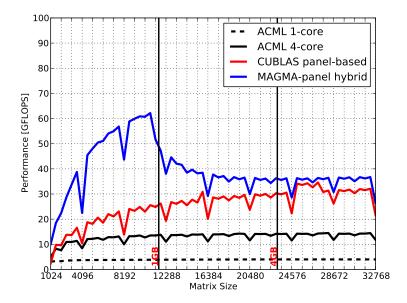

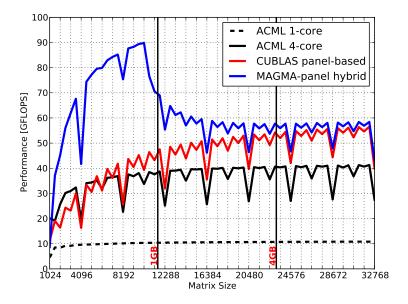

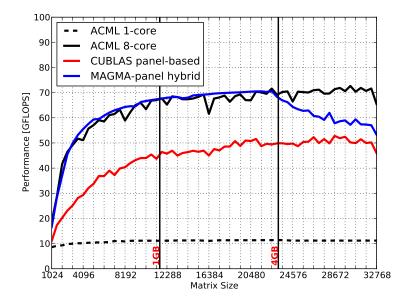

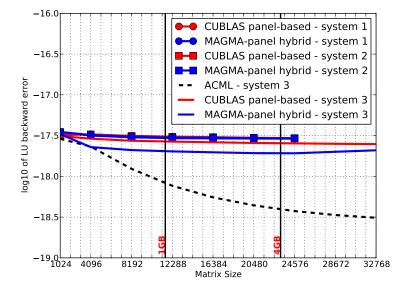

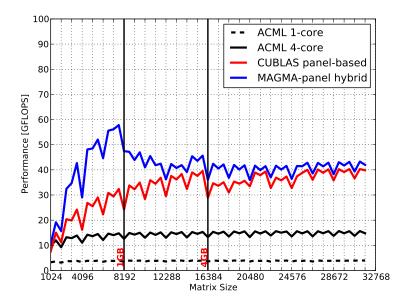

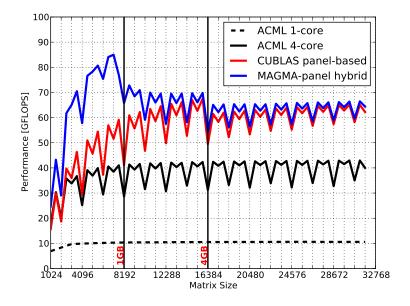

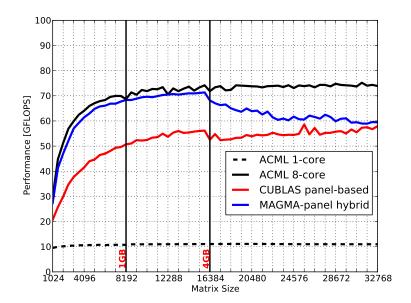

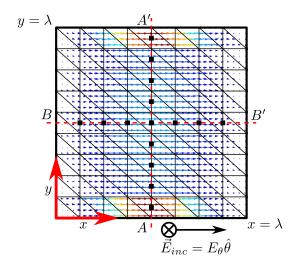

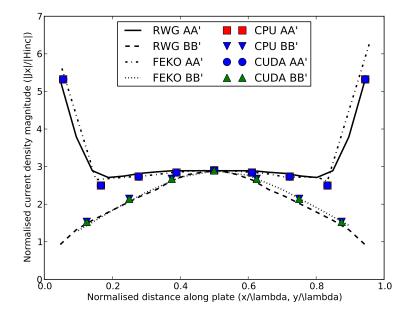

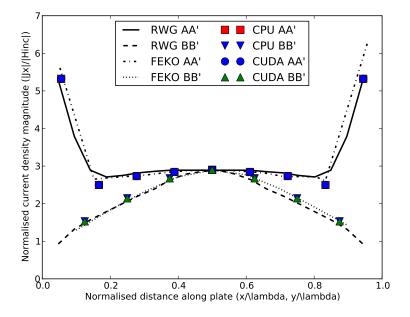

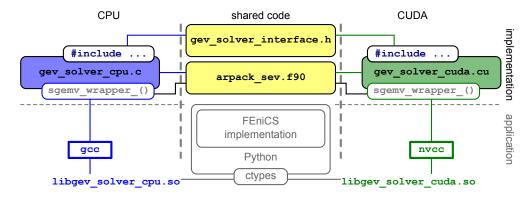

Figure 2.4: The computational process for calculating the sum of two arrays a and b and storing the result in a third array c using the CUDA kernel in Listing 2.2. The listing for the process is given in Listing 2.3.