# FLICKER MITIGATION IN INDUSTRIAL SYSTEMS

LEON DE WIT

Thesis presented in partial fulfilment of the requirements for the degree of Master of Science in Electronic Engineering with Computer Science at the University of Stellenbosch.

Study Leader: Prof. H. du Toit Mouton

April 2006

## **DECLARATION**

I, the undersigned, hereby declare that the work contained in this thesis is my own original work and that I have not previously in its entirety or in part submitted it at any university for a degree.

Ek, die ondergetekende, verklaar hiermee dat die werk in hierdie tesis vervat, my eie oorspronklike werk is en dat ek dit nie vantevore in die geheel of gedeeltelik by enige universiteit ter verkryging van 'n graad voorgelê het nie.

| Signature/Handtekening: |  |

|-------------------------|--|

|                         |  |

| Date/Datum:             |  |

|                         |  |

## **SUMMARY**

This thesis investigates the compensation of voltage flicker in an industrial environment. Industrial loads draw progressively less sinusoidal currents. These currents cause non-sinusoidal voltage drop over the line impedance, causing a distorted line voltage. The light output of incandescent electric lighting systems is quadratically proportional to the line voltage, and thus variations in the line voltage cause irritating variations in the output of such systems.

Two tools to analyse flicker problems are developed: A USB data logger is built to log measured waveforms to computer hard disk. These data are analysed using a MATLAB implementation of the IEC-specified flicker meter.

A converter-based flicker compensator is found to be the only compensator capable of compensating general flicker loads. Such a compensator is developed using the synchronous reference frame filtering technique. Several aspects of the compensator are dealt with in detail including selection of a current control strategy, calculation and implementation of the converter duty cycles and compensation of the various non-idealities in such a controller.

Full compensation is contrasted to reactive compensation – the second option being less expensive but also less effective in the compensation of certain loads. The effectiveness of reactive compensation is found to be dependent not only on the type of load, but also on the type of line feeding the flicker load.

Three industrial flicker loads are measured and analysed: a three-phase welder, a sawmill and a rock crusher. These loads are simulated, and the compensation proposed confirmed via these simulations. The compensation of the three-phase welder is tested using a hardware scale model. This verified the operation of the proposed flicker compensator in practice.

## **OPSOMMING**

Hierdie tesis ondersoek die kompensasie van spanningsflikker in 'n industriële omgewing. Industriële laste trek toenemend minder sinusvormige strome. Hierdie strome veroorsaak 'n niesinusvormige spanningsval oor die lynimpedansie, wat lei tot 'n vervormde lynspanning. Die intensiteit van lig wat uit 'n gloeilamp gestraal word is kwadraties proporsioneel tot die lynspanning, sodat die variasies in lynspanning irriterende variasies in sulke beligtingstelsels se ligintensiteit teweegbring.

Twee gereedskapstukke word ontwikkel: 'n USB dataopnemer word gebou sodat gemete golfvorms op 'n rekenaarhardeskyf gestoor kan word. Hierdie data word verwerk m.b.v. 'n MATLAB-implimentasie van die IEC-gespesifiseerde flikkermeter.

Daar word bevind dat 'n omsettergebaseerde flikkerkompenseerder die enigste kompenseerder is wat algemene flikkerlaste kan kompenseer. So 'n kompenseerder word ontwikkel deur gebruik te maak van die sinchrone verwysingsraamwerk filteringstegniek. Verskeie aspekte van die kompenseerder word in besonderhede bespreek, veral die kies van 'n stroombeheerstrategie, die berekening en implementering van die omsetter dienssiklusse en die kompensasie van die verskeie nie-idealiteite in die beheerder.

Volle kompensasie word teenoor reaktiewe kompensasie gestel. Hier is die tweede opsie goedkoper, maar ook minder effektief in die kompensasie van spesifieke laste. Daar word bevind dat die effektiwiteit van reaktiewe kompensasie afhang nie net van die las nie, maar ook van die soort lyn waardeur die las gevoer word.

Drie industriële flikkerlaste word gemeet en ontleed: 'n driefase sweismasjien, 'n saagmeule en 'n klipvergruiser. Hierdie laste word gesimuleer en die voorgestelde kompensasie word deur simulasie bevestig. Die kompensasie van die driefase sweismasjien word ook getoets deur 'n hardeware skaalmodel. Dit bewys die korrekte werking van die kompenseerder prakties.

## **DANKBETUIGINGS**

Graag rig ek die volgende dankbetuigings aan persone en instansies waarsonder hiedie tesis nie moontlik sou gewees het nie:

- Eerstens, aan my Hemelse Vader alle eer. Van Hom alleen ontvang ons alles wat ons het, en deur Hom alleen bereik ons alles wat ons bereik.

- Aan Prof. Toit Mouton, my studieleier, vir sy kritiese leiding en ondersteuning gedurende die doen van die navorsing en die skryf van hierdie tesis.

- Aan die lede van die Drywingselektronikanavorsingsgroep by die Universiteit van Stellenbosch. Baie dankie aan elkeen wat deur raad en kritiek 'n bydrae gelewer het tot hierdie tesis. Spesifiek dankie aan Wernher Swiegers en Dr. Jaques du Toit wat my gehelp het om die DPQC goed te verstaan en te gebruik. Dankie ook aan Pieter Henning, by wie ek boekdele geleer het oor ingebedde programmering; en aan Aniel le Roux, wie se kennis van beheeralgoritmes van onskatbare waarde was.

- Aan my gesin en vriende, wat my deur hul ondersteuning bygestaan het. Dankie veral aan die mense van die BTK, by wie ek soveel geleer het, en van wie ek soveel ontvang het.

- Aan Hennie Mostert en Yusuf Martin van Eskom, Johan Smit van Cape Sawmills en Luca Clayton van Holcin vir geleenthede om werklike data te bekom en die probleem uit die industrie se oogpunt te sien.

- Laastens, dankie aan Eskom, die NNS en THRIP vir finansiële ondersteuning.

# **CONTENTS**

| Declarat  | ion                                                                 | i    |

|-----------|---------------------------------------------------------------------|------|

| Summar    | у                                                                   | ii   |

| Opsomn    | ning                                                                | iii  |

| Dankbet   | uigings                                                             | iv   |

| Contents  | s                                                                   | v    |

| List of F | igures                                                              | viii |

| List of T | ables                                                               | x    |

| Glossary  | /                                                                   | xi   |

| CHAPTE    | R 1: Introduction                                                   | 1    |

| 1.1.      | Flicker principles                                                  | 1    |

| 1.2.      | Compensation strategies                                             | 2    |

| 1.2.      | 1. Compensation via a new line                                      | 3    |

| 1.2.2     |                                                                     |      |

| 1.2.3     | •                                                                   |      |

| 1.2.4     | 4. Converter-based compensators                                     | 6    |

| 1.3.      | Problem definition                                                  |      |

| 1.4.      | Thesis outline                                                      |      |

| CHAPTE    | R 2: Metering flicker                                               | 9    |

| 2.1.      | Motivation for a flicker meter                                      |      |

| 2.2.      | Available flicker meters                                            | 10   |

| 2.3.      | The IEC flicker meter                                               | 10   |

| 2.3.1     | Block 1: Calibration and scaling                                    | 11   |

| 2.3.2     | 2. Block 2: Model of an incandescent lamp                           | 11   |

| 2.3.3     | 3. Blocks 3 and 4: Model of the response of the human visual system | 12   |

| 2.3.4     | 4. Block 5: Statistical evaluation                                  | 14   |

| 2.4.      | Implementation of the flicker meter in MATLAB                       | 15   |

| 2.5.      | Verification                                                        | 16   |

| 2.6.      | Chapter summary                                                     | 17   |

| CHAPTE    | R 3: A USB data logger                                              | 18   |

| 3.1.      | Motivation for a data logger                                        | 18   |

| 3.2.      | Overview                                                            | 19   |

| 3.3.      | Measurement system                                                  | 21   |

| 3.4.      | PEC33 code and hardware                                             | 22   |

| 3.5.      | PC software                                                         | 23   |

| 36        | Results                                                             | 24   |

| 3.7.   | Chapter summary                                     | 25 |

|--------|-----------------------------------------------------|----|

| CHAPTI | ER 4: Finding a compensation strategy               | 27 |

| 4.1.   | Overview of compensation theory                     | 27 |

| 4.2.   | p-q Theory                                          | 29 |

| 4.2.   | .1. α-β Coordinates                                 | 30 |

| 4.2.   | .2. $p$ - $q$ Theory in $α$ - $β$ coordinates       | 31 |

| 4.3.   | Synchronous reference frame filtering               | 34 |

| 4.4.   | Comparison of p-q and synchronous reference methods | 37 |

| 4.5.   | Chapter summary                                     | 39 |

| CHAPTI | ER 5: Implementation                                | 40 |

| 5.1.   | General notes on current-controlled PWM converters  | 40 |

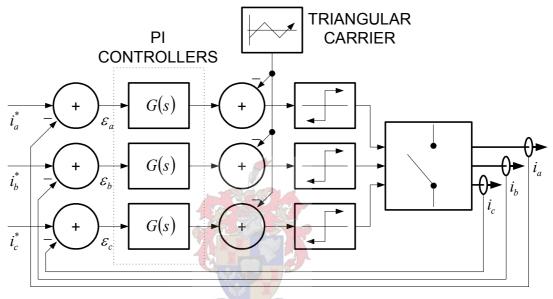

| 5.2.   | Proportional integral control                       | 41 |

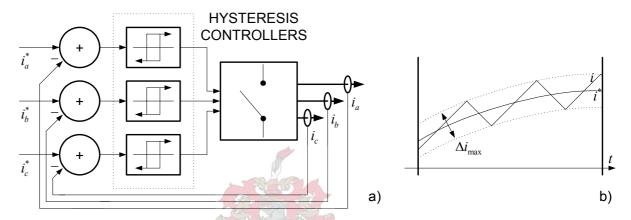

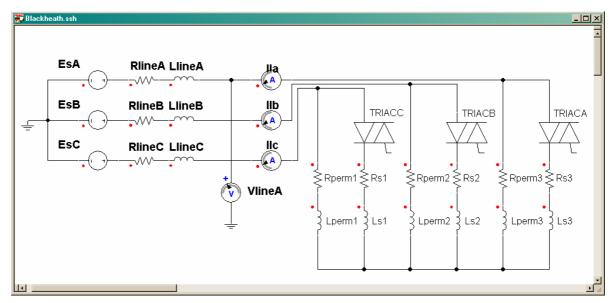

| 5.3.   | Hysteresis Control                                  | 42 |

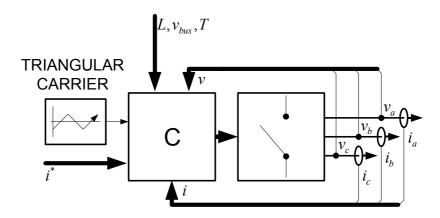

| 5.4.   | Deadbeat control                                    | 43 |

| 5.5.   | Selection of deadbeat control                       | 43 |

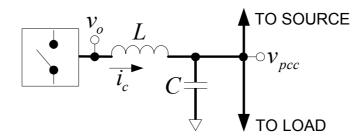

| 5.6.   | Practical considerations                            | 44 |

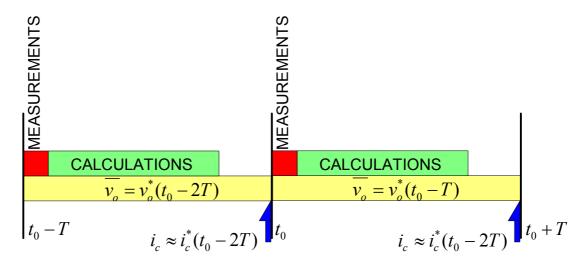

| 5.7.   | Time delays                                         | 45 |

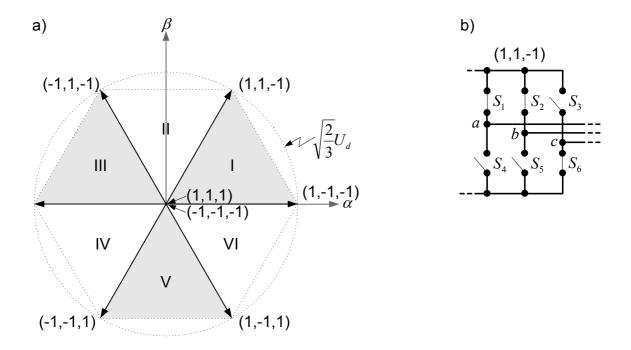

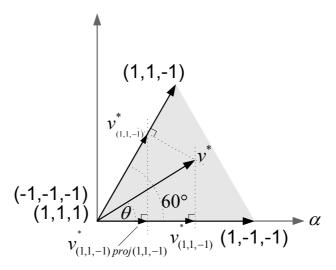

| 5.8.   | Space vector modulation                             |    |

| 5.9.   | Dead time effects                                   | 50 |

| 5.10.  | Generation of switching signals                     | 57 |

| 5.11.  | Chapter summary                                     | 58 |

| CHAPTI | ER 6: Case studies                                  | 60 |

| 6.1.   | Model of the compensator                            | 60 |

| 6.2.   | Case study I: Three-phase arc welder                | 61 |

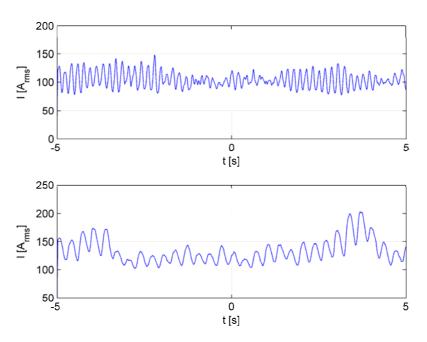

| 6.3.   | Case study II: Sawmill                              | 69 |

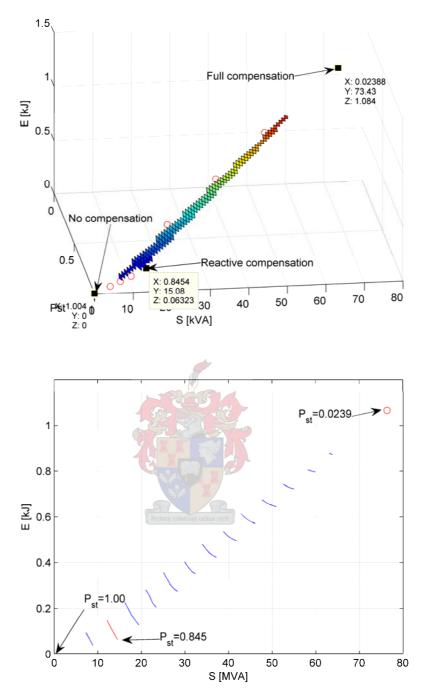

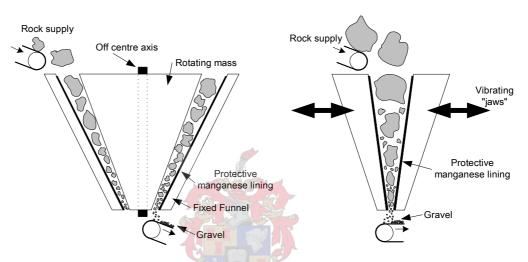

| 6.4.   | Case study III: Rock crusher                        | 76 |

| 6.5.   | Conclusions                                         | 80 |

| 6.6.   | Chapter summary                                     | 81 |

| CHAPTI | ER 7: Comparison with an SVC                        | 82 |

| 7.1.   | Principles of operation                             | 82 |

| 7.2.   | Simulation in Simplorer                             | 83 |

| 7.3.   | Simulation results                                  | 85 |

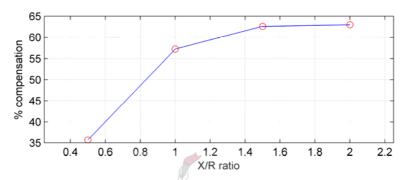

| 7.4.   | X/R sweep                                           | 87 |

| 7.5.   | Chapter summary                                     | 88 |

| CHAPT  | ER 8: Hardware simulation and results               | 89 |

| 8.1.   | Motivation for doing a hardware simulation          | 89 |

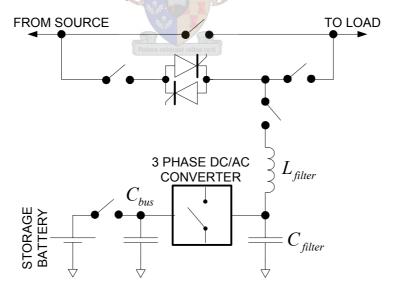

| 8.2.   | The DPQC as compensator                             |    |

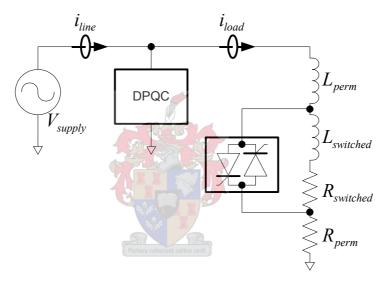

| 8.3.   | Selection and modelling of the three-phase load     | 91 |

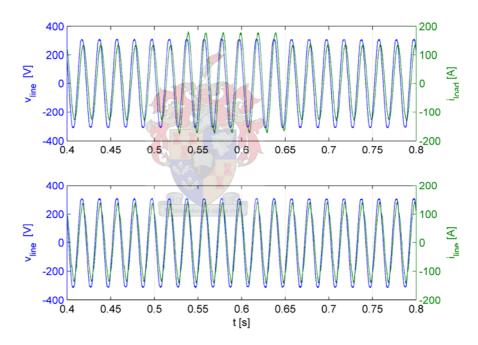

| 8.4.    | Compensation results                                        | 94  |

|---------|-------------------------------------------------------------|-----|

| 8.5.    | Chapter summary                                             | 101 |

| CHAPTI  | ER 9: Conclusion                                            | 102 |

| 9.1.    | Thesis conclusion                                           | 102 |

| 9.2.    | Future work                                                 | 103 |

| 9.3.    | Thesis contribution                                         | 104 |

| Referen | ces                                                         | 105 |

| APPENI  | DIX A: Selected proofs                                      | 109 |

| A.1.    | Active vs. reactive compensation                            | 109 |

| A.2.    | Derivation of the SVC firing angle – impedance relationship | 110 |

| A.3.    | SVC current harmonics                                       | 112 |

| APPEN   | DIX B: MATLAB flicker meter simulation script               | 114 |

| APPEN   | DIX C: USB data logger code & hardware                      | 117 |

| C.1.    | PEC33 DSP code                                              | 117 |

| C.2.    | PEC33 FPGA VHDL code                                        | 138 |

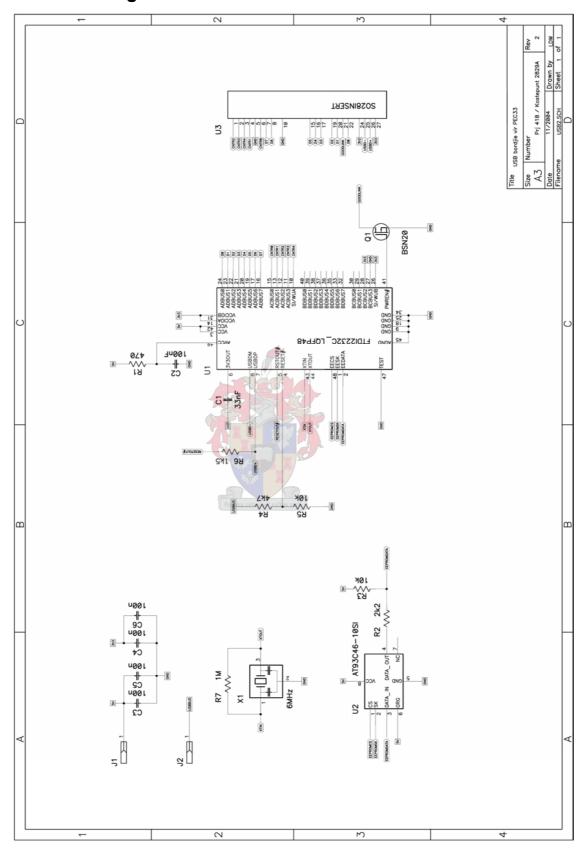

| C.3.    | USB daughter board schematic                                |     |

| C.4.    | C++ code for PC                                             | 147 |

| APPENI  | DIX D: Simulation scripts                                   | 154 |

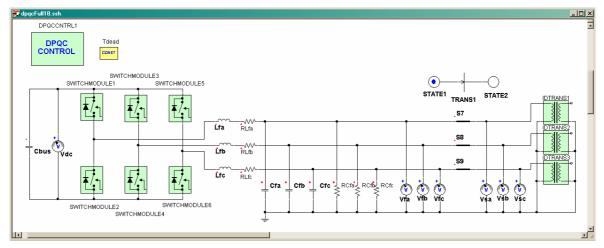

| D.1.    | Simplorer model of the DPQC controller                      | 154 |

| D.2.    | MATLAB simulation of jaw crusher compensation               | 160 |

| APPENI  | DIX E: Flicker generator                                    | 164 |

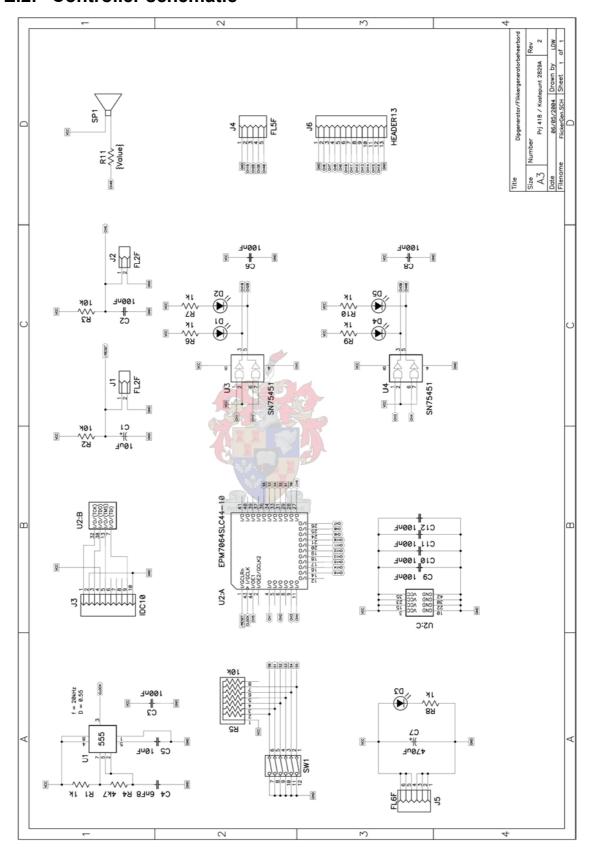

| E.1.    | Controller VHDL code                                        | 164 |

| E.2.    | Controller schematic                                        | 166 |

| APPENI  | DIX F: DPQC code                                            |     |

| F.1.    | Extract from modec.c                                        | 167 |

| F2      | Extract from space c                                        | 168 |

# **LIST OF FIGURES**

| Fig. 1-1: Single-line diagram of a load causing flicker                                    | 2              |

|--------------------------------------------------------------------------------------------|----------------|

| Fig. 1-2: Compensation via a new line                                                      | 3              |

| Fig. 1-3: Capacitive compensation                                                          | 3              |

| Fig. 1-4: Compensation by an SVC                                                           | 4              |

| Fig. 1-5: Resistive load with reactive line impedance                                      | 5              |

| Fig. 1-6: Resistive load with resistive line impedance                                     | 5              |

| Fig. 1-7: Compensation using a power electronics converter                                 | 6              |

| Fig. 2-1: Traditional flicker curve                                                        | 9              |

| Fig. 2-2: Blocks in the IEC flicker meter                                                  | 11             |

| Fig. 2-3: Implementation of block 1                                                        | 11             |

| Fig. 2-4: Block two is simply a squaring operator                                          | 12             |

| Fig. 2-5: Block 4 output                                                                   | 16             |

| Fig. 3-1: Using the data logger                                                            | 18             |

| Fig. 3-2: Data logger block diagram                                                        |                |

| Fig. 3-3: Measurement card schematic                                                       | 21             |

| Fig. 3-4: Data logger filters (normalised)                                                 |                |

| Fig. 3-5: Data logger results                                                              |                |

| Fig. 4-1: Fryze's orthogonal currents                                                      | 29             |

| Fig. 4-2: Traditional three-phase voltage representation and $\alpha$ - $\beta$ voltage re | presentation30 |

| Fig. 4-3: $q$ does not lie in the $\alpha$ - $\beta$ plane                                 | 32             |

| Fig. 4-4: Vector representation in the $\alpha$ - $\beta$ plane                            | 35             |

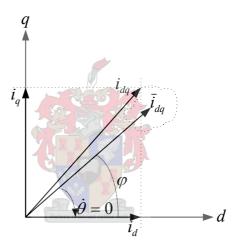

| Fig. 4-5: Vector representation in the synchronous <i>d-q</i> plane                        | 36             |

| Fig. 4-6: Simplorer simulation comparing control strategies                                | 37             |

| Fig. 4-7: Simulation results – p-q Method                                                  | 38             |

| Fig. 4-8: Simulation results – d-q Method                                                  | 38             |

| Fig. 5-1: Control loop                                                                     | 40             |

| Fig. 5-2: P-I Control                                                                      | 41             |

| Fig. 5-3: Hysteresis control                                                               | 42             |

| Fig. 5-4: Deadbeat control                                                                 | 43             |

| Fig. 5-5: Single phase of the converter output filter                                      | 44             |

| Fig. 5-6: Delays in reference calculation                                                  | 45             |

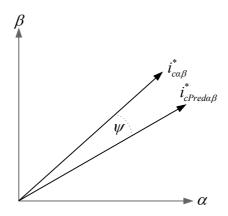

| Fig. 5-7: Rotation in the $\alpha$ - $\beta$ plane                                         | 47             |

| Fig. 5-8: SVM sectors and vectors                                                          | 48             |

| Fig. 5-9: Decomposition of reference voltage                                               | 49             |

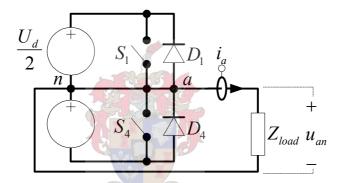

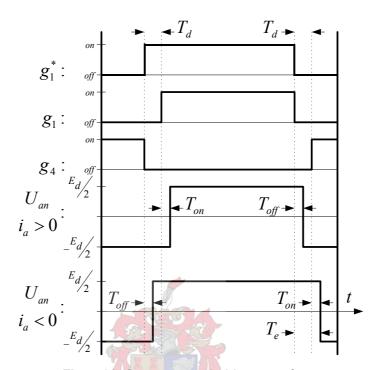

| Fig. 5-10: Single phase arm of a three-phase converter                                     | 51             |

| Fig. 5-11: Converter switching waveforms                                   | 52  |

|----------------------------------------------------------------------------|-----|

| Fig. 5-12: Three-phase converter                                           | 53  |

| Fig. 5-13: PWM generation from duty cycle reference                        | 58  |

| Fig. 6-1: Simplorer simulation of the compensator                          | 61  |

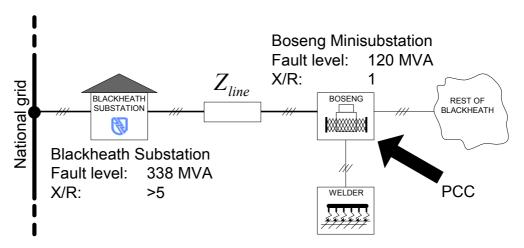

| Fig. 6-2: Single-line diagram of the grid around the welder                | 62  |

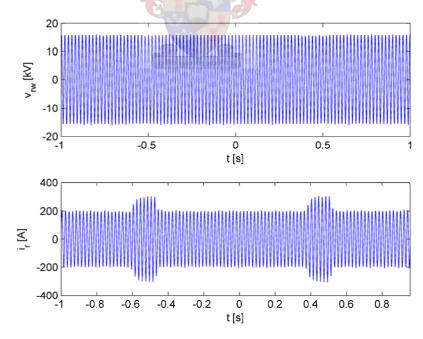

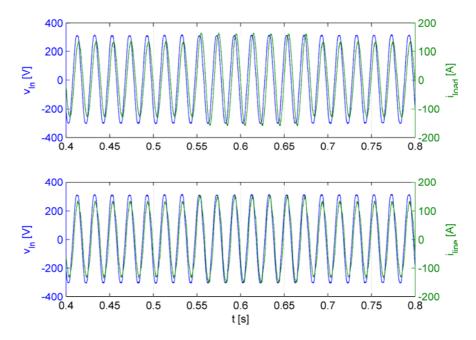

| Fig. 6-3: Voltage and current in Blackheath                                | 62  |

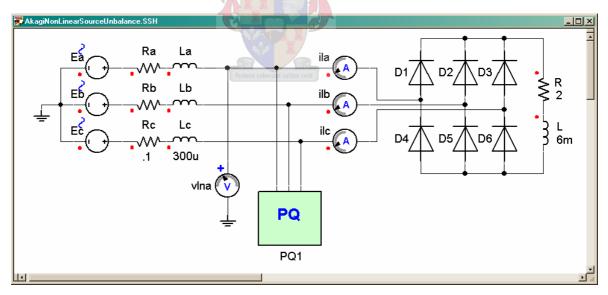

| Fig. 6-4: Simplorer simulation of the three-phase welder as load           | 64  |

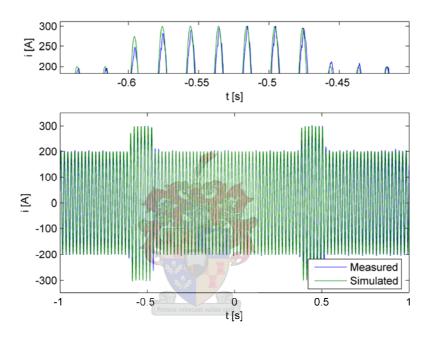

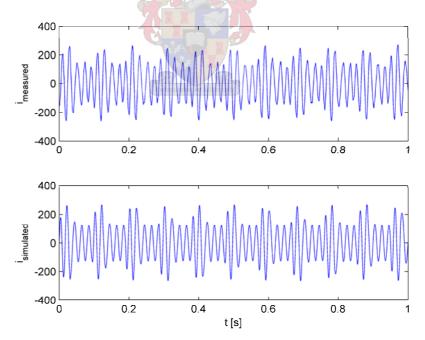

| Fig. 6-5: Comparison of measured and simulated current                     | 65  |

| Fig. 6-6: Effect on the voltage at the PCC                                 | 66  |

| Fig. 6-7: Simulation of three-phase welder with compensator                | 66  |

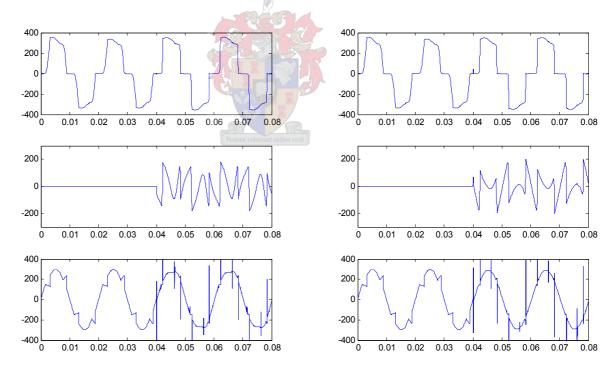

| Fig. 6-8: Three-phase welder simulation results                            | 67  |

| Fig. 6-9: Interaction between saw flywheel and blade                       | 70  |

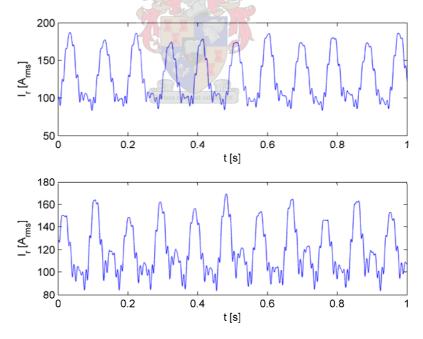

| Fig. 6-10: Sawmill RMS current                                             | 70  |

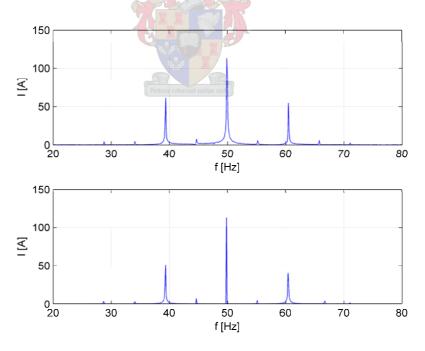

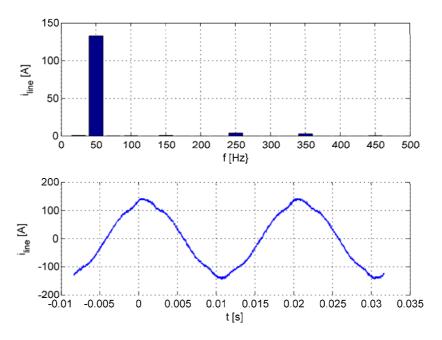

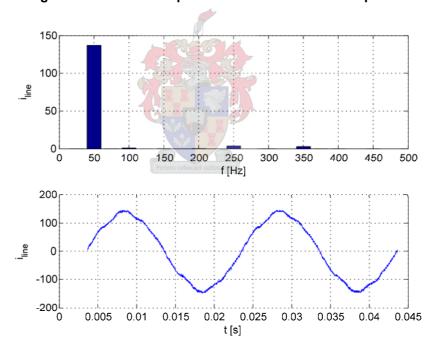

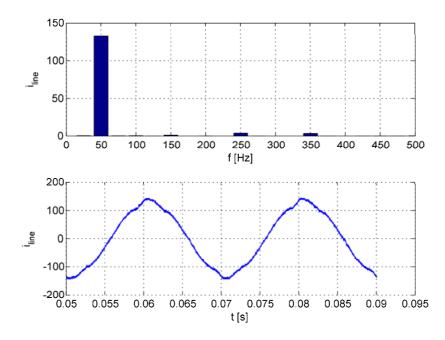

| Fig. 6-11: Sawmill current spectrum                                        | 71  |

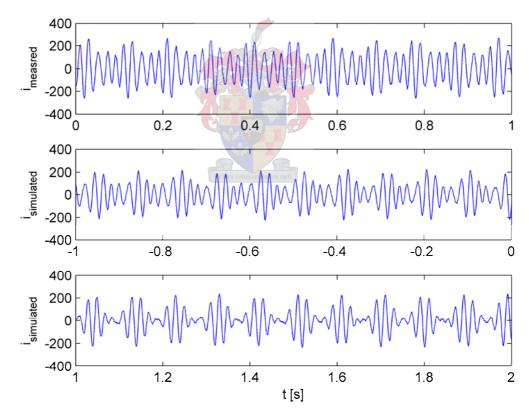

| Fig. 6-12: Sawmill current waveform                                        | 72  |

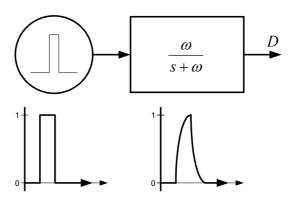

| Fig. 6-13: Implementation of the disturbance function                      | 73  |

| Fig. 6-14: Simulated sawmill current waveform                              | 74  |

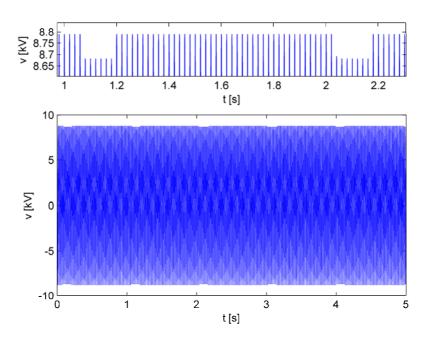

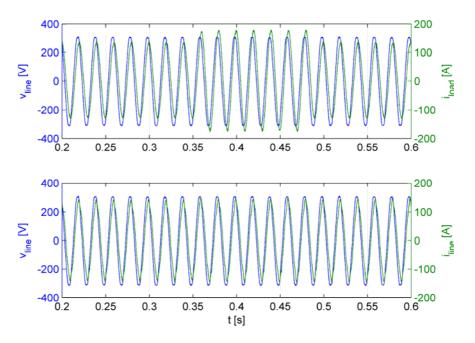

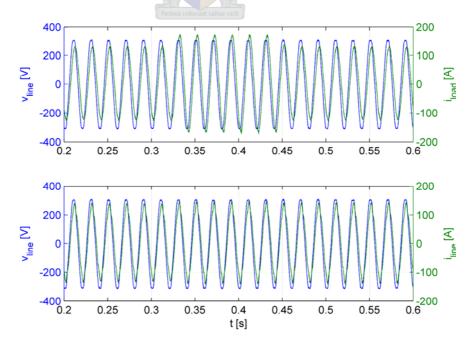

| Fig. 6-15: Sawmill simulation results                                      |     |

| Fig. 6-16: Two types of rock crushers                                      | 77  |

| Fig. 6-17: Crusher RMS currents                                            | 78  |

| Fig. 6-18: Jaw crusher simulation results                                  | 79  |

| Fig. 7-1: Simplorer simulation of an SVC                                   | 83  |

| Fig. 7-2: SVC compensation range                                           | 84  |

| Fig. 7-3: SVC currents                                                     |     |

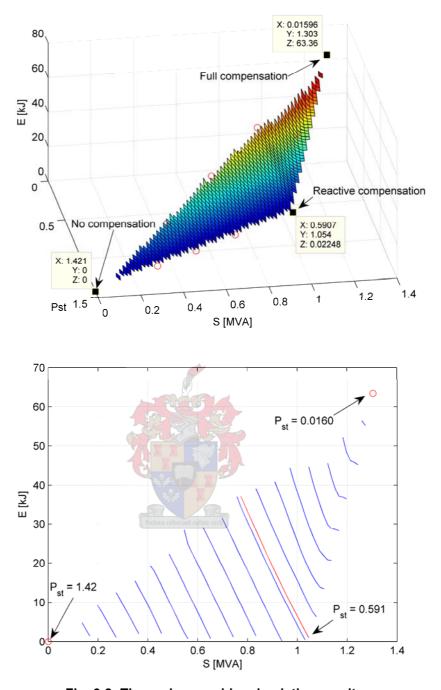

| Fig. 7-4: Compensation sweeping the X/R ratio                              | 87  |

| Fig. 8-1: Block diagram of the DPQC                                        | 89  |

| Fig. 8-2: Hardware simulation of the three-phase welder                    | 92  |

| Fig. 8-3: Photo of the hardware simulation setup                           | 93  |

| Fig. 8-4: Measured compensation results – Basic compensation               | 94  |

| Fig. 8-5: Basic compensation - Spectrum and zoom                           | 95  |

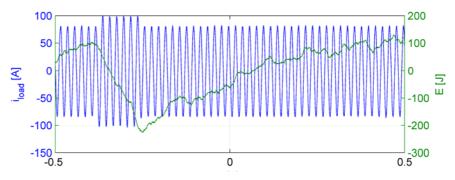

| Fig. 8-6: Measured compensation results – Energy                           | 96  |

| Fig. 8-7: Measured compensation results – Time compensated                 | 97  |

| Fig. 8-8: Time compensated – Spectrum and zoom                             | 97  |

| Fig. 8-9: Measured compensation results – Time and dead time compensated   | 98  |

| Fig. 8-10: Time and dead time compensated – Spectrum and zoom              | 99  |

| Fig. 8-11: Measured compensation results - Reactive compensation           | 100 |

| Fig. 8-12: Measured compensation results – Energy in reactive compensation | 100 |

# **LIST OF TABLES**

| Table 2-1: Low pass filter parameters                                   | 13 |

|-------------------------------------------------------------------------|----|

| Table 2-2: Weighing filter parameters                                   | 13 |

| Table 4-1: Parameter values from simulation                             | 38 |

| Table 6-1: Parameter values for Simplorer simulation of the compensator | 61 |

| Table 6-2: Power variations measured at Blackheath                      | 63 |

| Table 6-3: Parameter values for welder simulation                       | 63 |

| Table 6-4: Fourier coefficients for sawmill simulation                  | 72 |

| Table 6-5: Sawmill simulation parameters                                | 74 |

| Table 7-1: P <sub>st</sub> values from X/R sweep                        | 87 |

| Table 8-1: DPQC parameter values                                        | 90 |

| Table 8-2: Measurement equipment                                        | 90 |

| Table 8-3: Load simulation parameter values                             | 92 |

## **GLOSSARY**

ADC Analog to digital converter

DSP Digital signal processor

EEPROM Electrically erasable programmable read only memory

EPLD Electronically programmable logic device

EMF Electromotive force FIFO First in first out

FPGA Floating point gate array

IEC International electrotechnical commission

IGBT Insulated gate bipolar transistor

PC Personal computer

PCC Point of common coupling

P-I Proportional integral

PLL Phase lock loop

POC Point of compensation

PWM Pulse width modulation

RMS Root mean square

THD Total harmonic disturbance

UPS Uninterruptible power supply

USB Universal serial bus

VHDL Very high speed integrated circuit hardware description language

MATLAB is a registered trademark of The Mathworks Inc.

Simplorer is a registered trademark of Ansoft Corporation.

## **CHAPTER 1: Introduction**

Utilities worldwide face ever increasing problems in power quality. The days of mostly static loads drawing sinusoidal currents are long gone. In their place has come a seemingly endless array of dynamic, non-linear and generally non-sinusoidal load types. Aggravating the problem is the growing divergence between generated power and demand. Economic and environmental constraints simply do not allow utilities to generate power with the wide margin of oversupply that was once the accepted norm. Busses are weaker, while having to supply quality power to increasingly demanding loads.

The results of power quality problems are well known. Harmonics and unbalance are major causes of inefficient power transfer and can cause severe damage to electrical machines experiencing torque pulsations. Failure of an overstressed phase in an unbalanced situation can be a very costly affair. Dips in the supply voltage disrupt plant control systems and can lead to expensive loss of production. Distortion of the voltage waveform is another problem, often amplified by the presence of inter-harmonics and current noise. These phenomena are especially troublesome as their effects are often stochastic or, even worse, chaotic.

A foremost effect of voltage distortion is flicker. Incandescent lamps have a light output proportional to the square of the voltage applied, making them very sensitive to variations in the voltage waveform. The human eye can detect such variations up to frequencies of about 40 Hz, with the most sensitive region being the 6 - 10 Hz range. In this very sensitive area, frequency modulation of the supply voltage of less than 0.5 % can be a severe irritation [01][02].

To solve the power quality problems they face, utilities increasingly look towards power electronics. No other technology can provide the benefits of almost infinite controllability with the ability to deliver power at the levels required. In addition, power electronics can provide much of the functionality of traditional power system components at much reduced losses. New applications are also possible. Many of the active filtering options available today cannot be implemented without using power electronics.

## 1.1. Flicker principles

As a rule, the voltage at the point of generation in a network can be taken as being practically sinusoidal. Designers of generators go to great lengths to minimise the amount of distortion and the harmonics present in the output of power stations. The role of generation in the flicker effect may therefore safely be ignored.

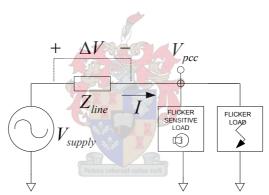

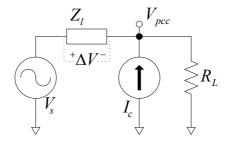

The primary cause of flicker is loads drawing non-sinusoidal currents with frequency components in the visible spectrum. The non-sinusoidal currents drawn cause a non-sinusoidal voltage drop over the line impedance ( $Z_{\rm line}$  in Fig. 1-1). This causes a flicker problem at the point of common coupling (PCC) by distorting the line voltage ( $V_{\rm pcc}$  in Fig. 1-1). Loads both upstream and downstream from the PCC will also be affected by the flicker, although the effect on the upstream loads will diminish as the line impedance diminishes.

As flicker is a current-induced problem, many compensation strategies focus on correcting the non-sinusoidal current flow in the system. From a measurement perspective, it is much easier to measure the variations in current causing the flicker problem than measuring the voltage variation itself. Because of the low expected value of the line impedance, the variations in current will be much larger than the variations in voltage. In spite of both current and voltage measurements being affected by noise, the expected signal to noise ratio (SNR) is much better for current measurements. Thus current-based strategies are to be preferred in compensators reacting to a reference current calculated from measurements.

Fig. 1-1: Single-line diagram of a load causing flicker

## 1.2. Compensation strategies

Several strategies to mitigate flicker problems have been proposed and implemented. These strategies include new lines, capacitive compensation, static var compensators (SVCs) and the use of converter-based active filters.

#### 1.2.1. Compensation via a new line

Fig. 1-2: Compensation via a new line

Providing the flicker-causing load with its own line from a strong bus is an effective mitigation strategy. As the flicker-causing currents drawn by the load no longer flow through the line impedance of the line feeding the flicker sensitive loads, these loads are unaffected by the operation of the flicker load. The obvious problem with this scheme is the cost of the extra line. Nevertheless, this has been the only workable solution for a number of high power flicker problems.

#### 1.2.2. Capacitive compensation

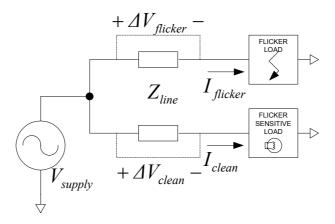

Fig. 1-3: Capacitive compensation

The compensating capacitor has no effect on the flicker problem at the PCC1

Capacitive compensation is aimed at decreasing the effective line impedance between source and PCC. As lines are usually at least partly inductive, this inductance may be cancelled by installing series capacitance. Unfortunately this is true only at one specific frequency. Capacitive compensation is also known to have lead to unwanted oscillations on power grids. This problem tends to be worse in the presence of flicker loads, as the non-linear nature of such loads usually implies the presence of a variety of frequencies in the load current. Capacitive compensation also compensates the flicker problem only at the point where the capacitors are inserted. Loads

upstream of the point of compensation (POC) will not be affected by the compensation, and may still experience intolerable levels of flicker.

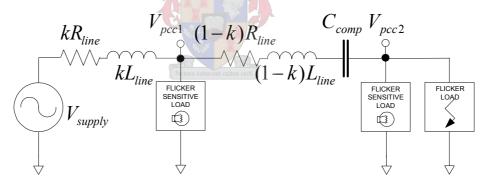

#### 1.2.3. Compensation via an SVC

Fig. 1-4: Compensation by an SVC

Thiristor-controlled reactors (TCRs), thiristor-switched capacitors (TSCs) and static var compensators (SVCs) aim to control the reactive current drawn from the supply, thereby controlling the voltage drop over the line impedance and therefore also controlling the voltage at the PCC. This is done by connecting shunt impedance at the PCC, and varying this impedance to source or sink an appropriate measure of reactive power. The impedance is varied by adjusting the firing angle of thiristors connected in series with the compensator impedance.

In TCRs the impedance is formed by inductors, making a TCR an adjustable sink of reactive power. The left arm of the SVC in Fig. 1-4 is an example of a TCR. In TSCs the impedance is capacitive, making a TSC a variable source of reactive power. Combinations of TCRs, TSCs and fixed impedance produce a compensator capable of either sinking or sourcing reactive power. Such a device is called an SVC. SVCs have been used with success in the compensation of many flicker loads, but in many other cases they tend to be impractically large and expensive. In other cases they are simply ineffective [01]. The reason for these deficiencies is twofold: Because an SVC is switched only twice every cycle, the device frequency response is inherently limited. Also, an SVC is incapable of injecting real power.

To understand why reactive compensation does not provide adequate compensation of all flicker problems, a few special cases will be considered. Note that this discussion is not limited to SVCs, but contrasts reactive and active compensation in general.

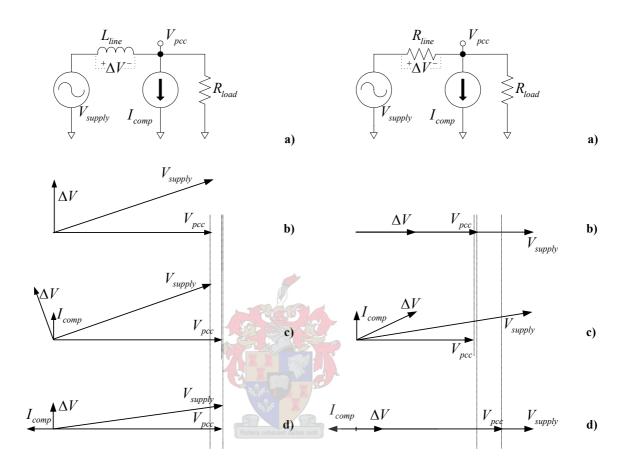

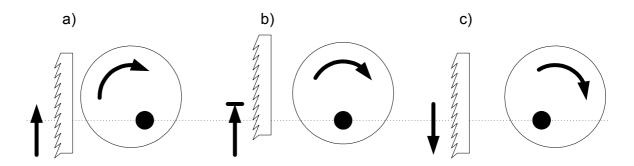

If the load is purely reactive, a reactive power compensator can compensate the full variation in the current drawn. For a substantially resistive load this is not the case. This is illustrated in Fig. 1-5 and Fig. 1-6.

Fig. 1-5: Resistive load with reactive line impedance

a) Diagram, b) Uncompensated, c)

Reactively compensated, d) Actively compensated

Fig. 1-6: Resistive load with resistive line impedance

a) Diagram, b) Uncompensated, c)

Reactively compensated, d) Actively compensated

In the figures, the voltage  $V_{\it pcc}$  is assumed to lie at a specific point in the plane. Compensation will be evaluated by looking at how far a fixed amount of current is able to shift this voltage. The amount of shift is an indication of the controllability of the output voltage by a compensator with a given power rating.

In Fig. 1-5 the line impendence is mostly reactive. The influence of a certain amount of reactive compensation is shown in c). In d), the same amount of active compensation is applied. Neither active nor reactive compensation clearly shifts the voltage supply vector further than the other, indicating that both power components have a relevant influence on the output voltage.

In Fig. 1-6, the line impedance is mostly resistive. Active compensation produces a substantial shift in  $V_{\it pcc}$ , while reactive compensation has very little effect. In this case it is imperative that the compensator employed must be capable of supplying active power in order to compensate effectively.

From the preceding examples it is clear that a reactive power only compensator such as an SVC is unable to compensate general flicker loads. The more resistive a load and the associated line are, the less effective reactive compensation will be. A more mathematical approach leading to the same conclusion may be found in Appendix A.1.

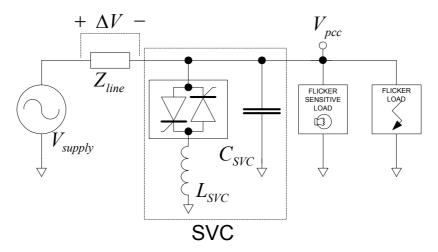

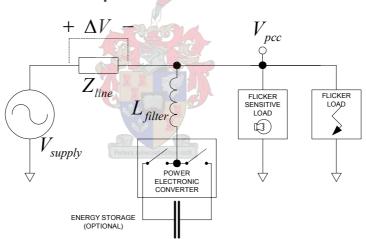

#### 1.2.4. Converter-based compensators

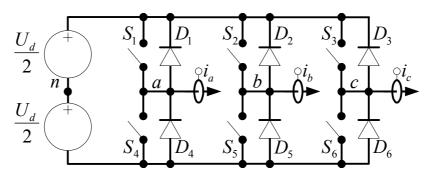

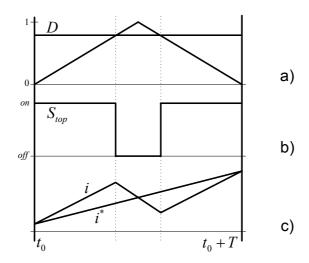

Fig. 1-7: Compensation using a power electronics converter

The solution to the problem of active power injection lies in the use of a power electronic converter. Such a compensator is capable of reactive power injection in the same way as was described for the SVC above. Connecting the compensator to an energy storage device gives the compensator the additional ability to regulate active power flow in the system. As a further advantage over SVCs, converter-based compensators have a much wider bandwidth.

The main disadvantage of converter-based compensators is cost – a suitable converter can cost up to several times the cost of an SVC with a similar power rating. Adding energy storage makes the compensator even more expensive. Thus, an SVC should be used whenever possible. In cases

where active compensation is needed or where SVC compensation is too slow, a converter-based compensator should be used.

#### 1.3. Problem definition

From the previous section, it is clear that there is no single optimum solution for all flicker problems. A strategy that works excellently for one specific load may be quite ineffective or much more expensive than necessary in other circumstances.

New lines and capacitive compensation are methods relatively well understood. Similarly, SVCs have been used since the 1960s, and their operation is well documented in literature [03]. Much less work has been done in the field of converter-based compensators. Although compensators supplying only reactive power have been in use for some time, injecting active power to compensate flicker problems is a much more recent development. This thesis will focus on the use of such compensators, reviewing both the cases of reactive only compensation and compensation by supplying active and reactive power.

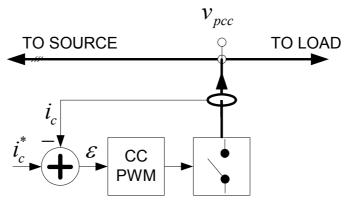

Because many practical flicker loads contain smoothing inductors for current control, inductance from motor windings, etc., these loads appear as current sources when viewed from the perspective of the line. This necessitates the usage of a parallel filter [04]. Parallel filters are also much easier to protect than series filters.

#### 1.4. Thesis outline

This thesis starts with the development of two tools that are necessary for the study of the flicker problems to be compensated. Chapter 2 describes the development of a flicker meter. This is used to gauge the severity of flicker problems and the effectiveness of the proposed compensation throughout the thesis. Chapter 3 follows the development of a data logger capable of capturing voltage and currents over significant periods of time to an ordinary computer hard disk.

In Chapter 4 the compensation techniques used are motivated and developed. This is no straightforward matter, as the topic is still hotly debated in literature by various authors [05]. A choice of strategies is considered, and the d-q static reference frame filtering technique is chosen as the most promising.

Chapter 5 deals with the implementation of the algorithms developed in Chapter 4 in a DSP based controller. Most converter-based compensators are designed to follow a reference current. The controller calculates the output voltage necessary to force the flow of this current, and switches the converter accordingly. Various aspects need to be taken into account when algorithms are

transferred from the mathematical to the physical domain. Timing delays and the need to translate a quasi continuous reference to discrete switching pulses impact on the effectiveness of the compensation. These issues have to be adequately addressed.

In Chapter 6, the developed techniques are comprehensively simulated using the Ansoft Simplorer simulation package. The prospects of the compensation method are reviewed under different load circumstances based on measurements taken in industry. In Chapter 7 a simulation of a static var compensator (SVC) is undertaken to contrast the developed methods with the capabilities of this popular device.

Chapter 8 describes a hardware simulation conducted in laboratory to verify the accuracy of the work done in the previous chapters.

Finally, in Chapter 9, the effectiveness of the proposed strategy is evaluated and assessed. Conclusions are drawn regarding the best way to compensate flicker under different conditions.

Each chapter will begin with a short introduction. The conclusions drawn in a chapter will be summarised at the chapter end.

# **CHAPTER 2: METERING FLICKER**

In this chapter the usage of special measuring techniques when evaluating flicker will be briefly motivated. The International Electrotechnical Commission (IEC) proposed flicker meter will be dealt with in detail. The meter will be implemented in MATLAB, and the implementation will be shown to conform to the IEC standard.

#### 2.1. Motivation for a flicker meter

As was noted in the introduction, flicker is a direct result of voltage variations. To evaluate the severity of the flicker problem at a specific point in the network, and to evaluate the effectiveness of any compensation applied, the expected irritation to humans has to be determined from the voltage waveform at the point of interest. As the human eye is more sensitive to some frequencies than others, a simple total harmonic disturbance (THD) figure does not provide sufficiently accurate information on how a human would perceive the effects of a polluted voltage signal. Weighing the harmonic components before calculating the distortion would be one way of incorporating the human visual spectrum in the measurement. This would still leave the problems of non-linearity and memory effect in human perception unaddressed.

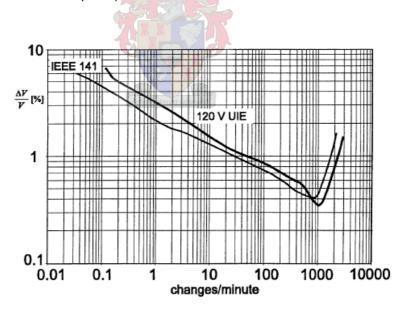

Fig. 2-1: Traditional flicker curve

Traditionally, flicker has been quantified using flicker curves. This is the approach taken in both IEEE 519-1992 [06] and IEEE 141-1995 [07], the two most relevant IEEE standards. An example of such a flicker curve is shown in Fig. 2-1, taken from [08]. The research these curves derive from is more than 50 years old. While incorporating some frequency information, this method shares the

problem of not adequately modelling the human visual response to flicker. This leads to the method being inaccurate in evaluating flicker in voltage waveforms modulated by the complex disturbance functions present in modern power systems. [08]

In recognition of these difficulties, various metering techniques have been developed to accurately measure the severity of flicker. The following paragraph will provide a brief overview of the development of the flicker metering standard used in this thesis, the IEC flicker meter specified in standard IEC 61000-4-15 [02].

#### 2.2. Available flicker meters

The first flicker meter in general use was developed by the UK Electrical Research Association (ERA) in 1972. The meter was developed to enable an objective evaluation of the flicker problems associated with some large arc furnaces. Westinghouse Electric Corporation followed suit in 1974, developing a light weight flicker meter based on the work done by ERA. Meanwhile, another flicker meter was being developed in France by the Electricite' de France (EDF), the meter being introduced in 1976. Japan also developed a flicker meter - in 1978 the Central Research Institute of Electric Power Industry (CRIEPI) produced their  $\Delta V_{10}$  meter.

With the multitude of flicker measuring techniques available at the start of early 1980s, the need for a generally accepted standard of flicker measurement was becoming apparent. The IEC defined an internationally agreed method of measurement along with accepted limits of tolerance. This work was formalised in a standard in 1986 [02].

The formalisation of flicker measurement in a standard does not imply that the work on flicker measurement is done. Considerable effort has been invested in improving the available techniques, prompting the IEC to temporarily update their standard flicker meter. Various authors continue to contribute to this effort. (As an example, see [09][10]) The latest, and most authoritative, version of the standard was published in 1997 and amended in 2003 [02]. This meter is recognised in South African standards by NRS 048-2:2003 par. 4.2.7 [11].

A flicker meter conforming to the IEC standard was constructed and tested in MATLAB. Extensive use was made of the work done by Rogóż [12], especially in the use of his parameter values for some of the flicker meter filters.

#### 2.3. The IEC flicker meter

The IEC standard specifies a flicker meter that models the reaction of the human visual system to flickering light emitted by incandescent light sources. The severity of the disturbance is obtained as

perceived by humans. This data is then statistically evaluated to obtain two figures of merit:  $P_{st}$ , the short-term flicker severity, and  $P_{lt}$  the long-term flicker severity, by which the flicker levels in a network may be quantified.

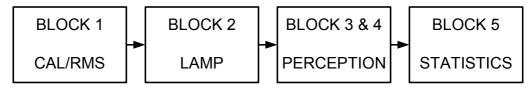

The standard itself discusses the flicker meter in five blocks. Each of these blocks will be treated in detail.

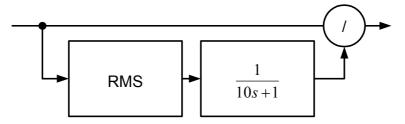

Fig. 2-2: Blocks in the IEC flicker meter

#### 2.3.1. Block 1: Calibration and scaling

Block one fulfils two functions. Firstly a reference input is provided for calibration purposes. Such a reference is especially helpful in hardware implemented meters, where it often increases the accuracy of measurements if the meter is calibrated before use. In a software implementation the block is only needed to do the original calibration of the meter. Secondly the signal is scaled to a reference and represented as an RMS (root mean square) value. This enables the meter to accept input at any carrier amplitude and to provide flicker information on a percentage basis, rather than as an absolute variation.

Fig. 2-3 shows the implementation of this block as done by Rogóż. The input signal is scaled by the inverse of the average RMS value. The low-pass filter in the figure is used as Rogóż found this to be more efficient than computing the average from definition, and graphically proved the equivalence of the two methods in his paper.

Fig. 2-3: Implementation of block 1

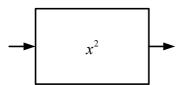

#### 2.3.2. Block 2: Model of an incandescent lamp

The purpose of the second block is to simulate the light output of an incandescent lamp. If the lamp is modelled as being overbearingly resistive (a sound approximation for most household lamps) the

power dissipated in the lamp is directly related to the square of the voltage. Thus the lamp model is simply a squaring operator.

Strictly speaking, the standard defines the function of the second block as a "square law demodulator". In this model demodulation is achieved by filtering in the next block.

Fig. 2-4: Block two is simply a squaring operator

#### 2.3.3. Blocks 3 and 4: Model of the response of the human visual system

The physical meaning of the distinction that the standard makes between blocks 3 and 4 is not clear. Therefore the two blocks will not be treated separately here.

The purpose of these blocks is to model the human visual system response to the varying output of the lamp in block 2. Firstly, as human eyes have a fixed bandwidth, the response of this block should also be bandwidth limited. Rogóż accomplishes this by building a band pass filter from a high and low-pass filter. The high pass filter has the simple transfer function

$$G_{high}(s) = \frac{s}{s + 2\pi 0.05}$$

.

As can be seen from Eq. 2-1, the filter has a 3dB cutoff frequency of 0.05 Hz as specified in the standard.

The low-pass filter needs a sharper cutoff, which prompts the use of a 6<sup>th</sup> order Butterworth filter. A filter of this type and order is of the form

$$G(s)_{low} = \frac{1}{1 + b_1 \left(\frac{s}{\omega_c}\right) + b_2 \left(\frac{s}{\omega_c}\right)^2 + b_3 \left(\frac{s}{\omega_c}\right)^3 + b_4 \left(\frac{s}{\omega_c}\right)^4 + b_5 \left(\frac{s}{\omega_c}\right)^5 + b_6 \left(\frac{s}{\omega_c}\right)^6}.$$

**Eq.** 2-2

The coefficients were found to be:

| Coefficient | Value |

|-------------|-------|

| $b_1$       | 3.864 |

| $b_2$       | 7.464 |

| $b_3$       | 9.141 |

| $b_4$       | 7.464 |

| $b_5$       | 3.864 |

| $b_6$       | 1.000 |

Table 2-1: Low pass filter parameters

Again this is in conformance with the suggestion incorporated in the standard, both in the form of the filter as well as in the cutoff frequency of 35 Hz.

A weighing filter is applied to model the eye-brain response to flicker. The filter is of the form

$$G(s)_{weighting} = \frac{k\omega_1 s}{s^2 + 2\lambda s + \omega_1^2} \underbrace{\begin{pmatrix} 1 + \frac{s}{\omega_2} \end{pmatrix}}_{1 + \frac{s}{\omega_4}} \underbrace{\begin{pmatrix} 1 + \frac{s}{\omega_2} \end{pmatrix}}_{1 + \frac{s}{\omega_4}}.$$

Eq. 2-3

with the parameters

| Coefficient     | Value          |

|-----------------|----------------|

| k               | 1.74802        |

| λ               | $2\pi 4.05981$ |

| $\omega_{ m l}$ | $2\pi 9.15494$ |

| $\omega_2$      | $2\pi 2.27979$ |

| $\omega_3$      | $2\pi 1.22535$ |

| $\omega_4$      | $2\pi 21.9$    |

Table 2-2: Weighing filter parameters

These parameters are specified in the standard. The filter has a resonant frequency of 8.8 Hz, which was found to be the frequency of maximum sensitivity for a 60 W, 230 V lamp. This lamp is

used extensively in Europe and South Africa. For other lamps, the weighing filter would have to be adjusted.

To model human nonlinear response to flicker, block 4 starts with a squaring operator. The signal is then averaged to model the so-called "storage effect" in the brain. This is done by low-pass filtering:

$$G(s)_{low} = \frac{1}{1+\tau s},$$

Eq. 2-4  $au = 300ms$  .

The signal is scaled by a linear amplifier by a factor calculated to produce unity output at the agreed standard threshold of flicker perception.

The output at this stage represents the instantaneous flicker sensation as perceived by humans.

#### 2.3.4. Block 5: Statistical evaluation

To produce the parameters  $P_{st}$  and  $P_{lt}$  a statistical evaluation of the instantaneous flicker sensation is done. The output of block four is sampled at a constant rate and divided into a number of classes. The minimum sampling rate is specified as 50 Hz. The classes are formed by specifying the base amplitude for each class, and a tolerance such that the classes span the entire range of possible output from block 4 without overlapping. Each time a new block four output value is recorded, the appropriate class counter is incremented. Thus a frequency distribution of flicker levels is obtained.

The short-term flicker severity can now be defined as

$$P_{st} = \sqrt{0.0314P_{0.1} + 0.0525P_{1.0s} + 0.0657P_{3.0s} + 0.28P_{10.0s} + 0.08P_{50.0s}} \;, \tag{Eq. 2-5}$$

where  $P_{xs}$  is the flicker level exceeded in x % of the observation period. An s in the subscript indicates the use of a smoothed value:

$$\begin{split} P_{50s} &= \left(P_{30} + P_{50} + P_{80}\right)/3, \\ P_{10s} &= \left(P_6 + P_8 + P_{10} + P_{13} + P_{17}\right)/5, \\ P_{3s} &= \left(P_{2.2} + P_3 + P_4\right)/3, \\ P_{1s} &= \left(P_{0.7} + P_1 + P_{1.5}\right)/3. \end{split}$$

Eq. 2-6

$P_{0.1}$  does not need smoothing as the low-pass filter in block 4 has a time constant of 300 ms, which prevents rapid variations in  $P_{0.1}$ .

The standard specifies the measuring period,  $T_{st}$ , for  $P_{st}$  to be selectable as 1, 5, 10 or 15 minutes.

$P_{lt}$  is always measured over a period  $T_{lt}$  such that  $T_{lt}$  is an integer multiple of  $T_{st}$ . It is defined as

$$P_{lt} = \sqrt[3]{\frac{\sum_{i=1}^{N} P_{st_i}^3}{N}}$$

Usually the short-term flicker severity is sufficient to describe the flicker situation in the region of a problem load if  $T_{st}$  is selected appropriately. For situations where many loads interact to contribute to the flicker problem or where the load has an exceptionally long (and possibly variable) duty cycle (such as is the case with arc furnaces), the long-term flicker value is more suitable to describe the magnitude of the flicker problem.

## 2.4. Implementation of the flicker meter in MATLAB

The IEC flicker meter was successfully implemented in MATLAB. The lsim function was used to simulate the response of the continuous filters. Using continuous to digital domain transformations to specify the whole system as a digital filter was attempted, but the loss of accuracy could not be justified by the increase in speed.

Block 5 was implemented somewhat differently from the specification. Instead of subdividing the output of block 5 into classes, the whole output vector was sorted using the very fast sort function. From this sorted vector, it was easy to find the precise flicker value exceeded in a specific percentage of  $T_{\rm sf}$ . As an example,

$$P_{10} = S \left[ round \left( \frac{10}{100} N \right) \right]$$

Eq. 2-8

where N is the size of the vector and round(x) rounds x to the nearest integer.

Using this method rather than step by step incrementing class counters improved the implementation speed dramatically without impacting on accuracy.

#### 2.5. Verification

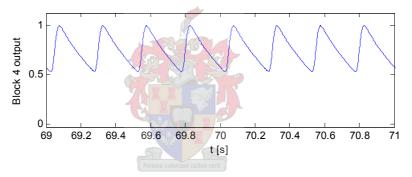

In [12] Rogóż provides figures showing the output of each block of the flicker meter for a predefined test signal, a 50 Hz sine wave modulated to a depth of 0.401 % by a 2 Hz square wave signal. The output obtained from the implemented flicker meter corresponded very well with the outputs as found by Rogóż. Fig. 2-5 shows the output at block 4, the instantaneous perceived flicker. This corresponds closely to Fig. 10 in [12].

Fig. 2-5: Block 4 output

The flicker meter was further tested for conformance to the specifications in Tables 1 and 2 of the standard. These tables show the depth of modulation that should result in an instantaneous flicker value of unity at different frequencies. The implemented flicker meter was tested according to these specifications, and was found to be noticeably more accurate than the permitted 5 % deviation from the tabulated values.

In addition to these tests Rogóż also tested the flicker meter extensively on the basis of work done by Bień *et al.* as presented in [13]. He found the meter to be very accurate in the representation of flicker as perceived by humans.

### 2.6. Chapter summary

In this chapter human response to flicker was shown to be a complicated, highly non-linear process. This motivated the use of special techniques in the evaluation of flicker. After a quick review of flicker meter development, a flicker meter conforming to the IEC standard was developed in MATLAB. This meter models the whole flicker process, including the lamp emitting the flicker as well as a detailed model of the human perception of varying light output. Through the IEC the meter is recognised widely, especially in Europe, and also in South Africa through national standards. The meter was tested extensively and proved to conform to the standard as published.

## **CHAPTER 3: A USB DATA LOGGER**

In this chapter the development of a universal serial bus (USB) data logger is motivated and described. Measured results are presented, verifying the success of the logger as a measurement tool.

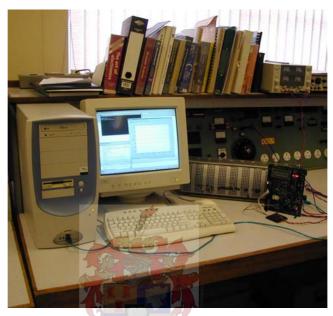

Fig. 3-1: Using the data logger

## 3.1. Motivation for a data logger

Flicker is a stochastic or chaotic phenomenon that incorporates significant variations occurring over periods of time very much longer than a line frequency fundamental period. The IEC flicker meter standard stipulates that short-term flicker severity should be evaluated over periods of 1, 5, 10 and 15 minutes. In contrast, the typical oscilloscope available in the laboratory can only store data spanning at most 10 s sampling at 1 kHz. To accurately analyse and simulate the studied flicker situations, a tool capable of recording waveforms for much longer periods of time was needed.

Several waveform recorders are available on the market. The decision to develop a logger was based on the following considerations:

- Implementing the logger in programmable hardware provided possibilities for customisation not possible if a logger had been purchased.

- Much of the hardware needed was available in the laboratory, making this implementation much cheaper than buying a ready made logger.

#### 3.2. Overview

In designing the data logger, the first task was to identify a suitable storage medium. Two options are available, a hard drive or flash memory. A computer hard drive was selected. Rather than creating a dedicated storage system, the logger was implemented as an add-on to a normal personal computer (PC). This configuration provided a large, fast, reliable storage mechanism. The data was also available immediately for on site evaluation.

The logger itself was implemented on a PEC33 development board. The PEC33 was originally developed as a power electronics controller board [14], and therefore has more than enough computing power available to log data at the required rates. It incorporates a Texas Instruments TMS320VC33 digital signal processor (DSP) and two Altera ACEX EP1K500QC208-3 floating point gate arrays (FPGAs). The analog to digital converters (ADCs) are also from Texas instruments, the 12-bit TLV1570.

The measurement board was realised using a common differential measurement system utilising the Analog Devices AD623 differential amplifier. Voltage was sensed directly, and current was sensed using Universal Technic M1.UB current probes.

The logger was connected to the computer via a USB connection. USB was chosen as many laptops today do not have serial or parallel ports, making it difficult to connect them to equipment via RS232 or RS485. Also, the data rates possible with USB exceed those possible with these standards by far. When the PEC33 was developed originally it provided a USB port via a Philips PDIUSB12 USB driver. In this design, it was decided to discard this driver in favour of an FTDI FT2232C. This choice will be motivated in section 3.5, where the development of the logger software is discussed.

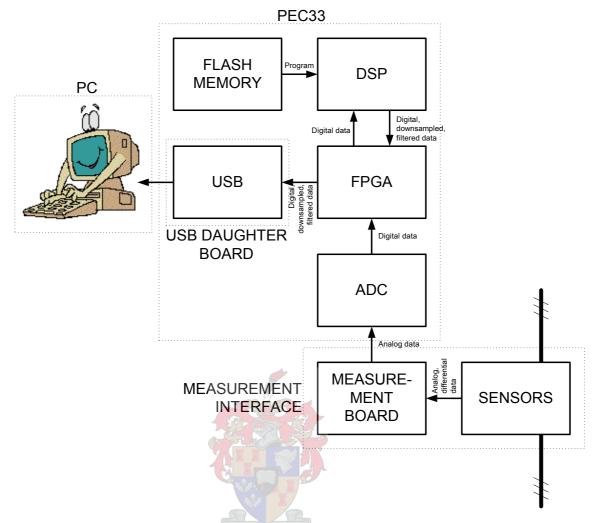

A block diagram of the system is presented in Fig. 3-2.

Fig. 3-2: Data logger block diagram

The basic data path can be seen from the diagram. The voltage signals from the voltage measurement points and the voltage output from the current sensors are fed, differentially, into the measurement board. This board contains the signal-conditioning circuitry and differential amplifiers. From here the signals are fed to the ADCs on the PEC33, where they are digitised and fed to the DSP via an interface in the FPGA. The DSP filters and downsamples the signal. The data is then sent to the PC via an FPGA interface to the USB driver.

The flash memory on the PEC33 was used exclusively to store the DSP program. It plays no direct part in the data stream.

The design of the components of the logger will now be dealt with in detail.

#### 3.3. Measurement system

The purpose of the voltage measurement card is to convert the differentially measured high voltage input signal to a single-ended, scaled and filtered signal suitable as inputs to the PEC33 ADCs. Differential measurement is preferred as the area surrounding a power electronic converter is inherently electrically noisy. While single-ended systems are susceptible to common mode noise, differential systems cause common mode interferences to cancel, giving a much better common mode rejection ratio.

Another potential source of noise is aliasing. To ensure that the ADCs sample at at least two times the maximum frequency in the signal to be converted, the frequency content of this signal must be limited. This necessitates the inclusion of a low-pass filter. As this logger was developed especially for flicker measurements, information at frequencies outside the visible spectrum was irrelevant. Thus an even lower filter cutoff frequency could be chosen.

Lastly, the ADCs were protected by diode-clamping the measurement system output voltage.

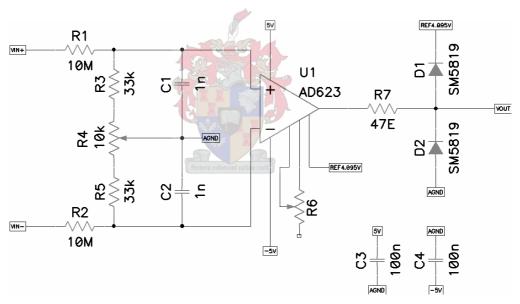

Fig. 3-3: Measurement card schematic

The input voltage scaling circuitry should ideally be specially calculated for each measurement range. Even though the AD623 enables the selection of the circuit gain via  $R_6$  [15], amplifying a signal previously downscaled is poor practice as this noticeably increases system noise. Therefore  $R_6$  was omitted from the circuit, resulting in the AD623 being programmed for unity gain.

With  $R_1$  =  $R_2$ ,  $R_3$  =  $R_5$  and  $C_1$  =  $C_2$  the transfer function of the input stage can be calculated to be

$$G = \frac{R_3 + 0.5R_4}{R_1(R_3 + 0.5R_4)C_1s + R_1 + (R_3 + 0.5R_4)}.$$

Eq. 3-1

The diode clamping on the card output enforces an output range of 0.70-3.40 V, with the usual 0.70 V forward voltage drop assumption made for both diodes. The lower limit comes from the output being connected via reverse-biased diode to signal ground, while the higher limit comes from the diode connection to the ADC reference voltage. With the maximum input voltage specified as 250 V<sub>rms</sub>, the input voltage range can be calculated as 707 V, giving a required scale factor of 3.82. This was easily realised by choosing  $R_1 = 10$  M $\Omega$ ,  $R_4 = 10$  k $\Omega$  and calculating  $R_3 = 33$  k $\Omega$ .

Because  $R_4$  is a variable resistor, difference between the system analog ground and the ground of the input signal can be compensated for. Thus it is possible to guarantee that the input voltage per input pin (relative to analog ground) will not exceed the AD623 input range.

With  $C_1$  selected as 1 nF the input stage cutoff frequency is 4.2 kHz, which is much lower than the 10 kHz sample rate selected for the PEC33 board. No aliasing should occur.

The current probe measurement system was developed in exactly the same way, remembering that the expected output voltage from the current probes is much lower than the input line voltages.

#### 3.4. PEC33 code and hardware

On the PEC33 board the DSP commands the ADCs to sample via an interface implemented in the FPGA. The ADCs sample the input channels, and the values are sent to the DSP. The DSP clocks the ADCs at a rate of 10.0 kHz, much faster than the 1 kHz logging frequency. Thus only every tenth sample is needed. To prevent aliasing the data is digitally filtered before being down-sampled. The filter is of the form

$$G_z = \frac{z+1}{z-0.7285}$$

,

and was calculated from a 500 Hz continuous domain low-pass filter prototype using the Tustin transformation [16].

Again via an FPGA interface, the DSP sends the data to the FT2232C. The DSP also handles the logger user interface. It displays the current logger state on the PEC33 LCD, and offers the user limited control of the logging process through the PEC33 keyboard.

Used in "first in first out" (FIFO) mode, the FT2232C buffers the data and sends it to the logging PC at the first opportunity. Many other options are available, including UART emulation, 'bit bang' and a variety of serial protocols, some implemented via an internal serial engine. FIFO mode was selected as this mode of communication provided robust communications via a simple parallel interface. Mode selection, device identification, etc. is done via an external EEPROM (Electrically erasable programmable read only memory). This EEPROM is programmed via the USB bus using custom software supplied by FTDI. The USB daughter board was designed from the FT2232C datasheet [17].

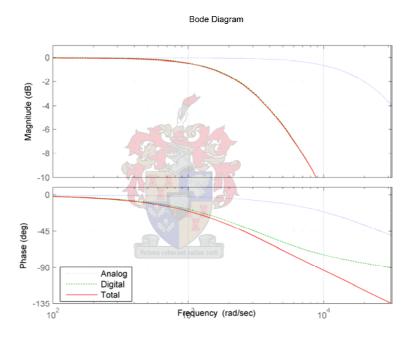

Fig. 3-4: Data logger filters (normalised)

#### 3.5. PC software

One of the features of the FT2232C is the drivers FTDI provides with it. Most other USB protocol chip manufacturers leave the creation of PC side drivers up to the developer. This is a time consuming activity, requiring detailed knowledge of the specific operating system the drivers are written for.

Using the FTDI drivers, it was possible to quickly and easily create the C++ program that writes the data to hard disk. Extensive use was made of the programming manual provided by FTDI [18].

As the amount of data handled was relatively small compared to the memory available in a modern desktop computer, a single file was created for each run of the logger. (As an example of this, logging six channels at 16-bit resolution at the logger logging frequency of 1 kHz for an hour produces only 41.2 Mb of data.) After establishing a link with the logger, the program simply polled the FTDI data available flag to determine whether new samples were available. The data was then buffered in memory until the end of the logging run, at which time the whole file was written to disk.

MATLAB provides many tools for reading files and extracting data. Using some of these features, a MATLAB m-file was written to read the logged data and display the waveforms as a plot. The data was then available for evaluation, simulation, etc.

#### 3.6. Results

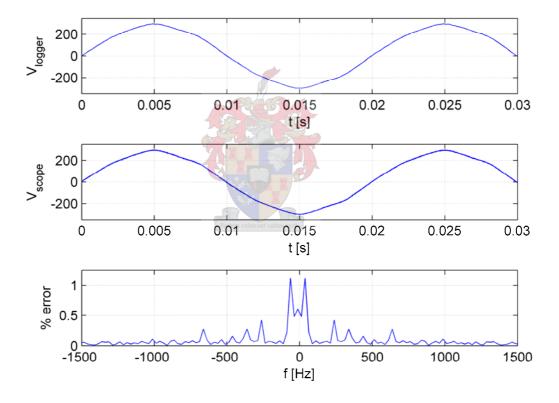

Fig. 3-5: Data logger results

Measurement by logger (top), Measurement by oscilloscope (middle), Fourier analysis of error (bottom)

Results from the data logger are shown in Fig. 3-5. From the top and bottom plots, the logger can be seen to follow the input waveform closely. Better insight into the logger behaviour is gained from

the Fourier analysis of the error signal. The error signal was computed by aligning the oscilloscope output and the data logger output in MATLAB and taking the difference.

Looking at the bottom plot in Fig. 3-5, the main error components tend to be at 50 Hz. This is to be expected, as some slight scaling error in the logging process is inevitable. Any slight misalignment of the oscilloscope and data logger signal will contribute to this error, although this does not represent any real errors in the logger. These errors should not impact on the flicker measured.

The next largest error component lies at zero frequency. As the logger logs only positive values, an arbitrarily chosen number represents zero. Changing this choice could eradicate this slight error. Again it has no bearing on flicker measurements.

The other noteworthy error components lie upwards of the fifth harmonic, or 250 Hz. The logger is expected to have a narrow pass band, given the slow sampling frequency and the numerous low-pass filters it contains, therefore the logged data is not expected to contain high frequency information. The oscilloscope measurement does contain this data, resulting in the apparent error. As no variations in voltage at these high frequencies are visible, they do not contribute to flicker and may safely be ignored. In fact, the low-pass filter character of the logger serves to suppress these high frequency noise components.

No large error components are visible in the area surrounding 50 Hz. The logger performs excellently in the frequency band most sensitive to flicker.

## 3.7. Chapter summary

In this chapter the development of a custom data logger was motivated. A computer hard drive was chosen as the most suitable storage medium, as it provides large capacity in an easy to access format. This motivated the development of the logger as an accessory to a standard desktop or laptop computer.

Most of the necessary logger hardware was found on the PEC33 power electronic controller board. As this controller was readily available, this provided a cost effective solution for much of the required logger hardware.

A USB connection was chosen as the means of communication between the PEC33 and the computer. USB was chosen because of its superior speed when compared to more traditional communication standards. In addition, it enables connectivity to nearly all modern computers. As no drivers were available for the original PEC33 USB interface, a daughter board was developed

using an FT2232C USB interface IC. This chip comes complete with all the necessary drivers to connect to a standard computer.

A C++ program was written to write the received data to disk. A MATLAB script was written to retrieve the data, enabling analysis such as flicker calculations.

Lastly the logger was verified and evaluated by measurement. The logger was found to perform quite satisfactorily in the frequency band needed in flicker analysis.

# CHAPTER 4: FINDING A COMPENSATION STRATEGY

In this chapter, a compensation strategy for implementation in a converter-based compensator is sought. This starts with a short overview of the theory available, after which the two most applicable theories are covered in depth. Finally, the choice of compensation by synchronous reference frame filtering is motivated.

## 4.1. Overview of compensation theory

The world's first commercial power plant was built by Thomas Edison in 1880. This plant employed DC distribution, in which reactive power flow is not a problem. In 1886 George Westinghouse built his first power plant in Great Barrington, Massachusetts. This plant employed AC distribution in order to utilise transformers to alleviate voltage drop. Although AC presented major benefits over DC at the time, the problem of oscillating energy was noted and presented by Stanley and Shallenberger in their respective papers for the American Institute of Electrical Engineers and the Electric World [19][20]. Their explanation, attributing oscillating power in sinusoidal systems to the difference in phase angle between voltage and current is, with minor alterations, the same as that which can be found in textbooks and engineering standards today.

Work on general power theory was continued in the 1920s and 1930s by Budeanu and Fryze. In [21] Budeanu defined reactive power as:

$$Q_B \equiv \sum_{n=1}^{\infty} U_n I_n \sin \phi_n$$

.

The definition comes from a Fourier series decomposition of both the current and voltage. Multiplying the RMS value of each harmonic current  $(I_n)$  with the RMS value of the voltage harmonic at the same frequency  $(U_n)$  and the sine of the phase angle between the two quantities  $(\phi_n)$  produces reactive powers in a manner analogous to that followed for traditional AC circuit analysis.

Hereby a new quantity, named the distortion power by Budeanu was introduced:

$$D_{R} \equiv \sqrt{S^2 - P^2 - Q_{R}^2}$$

,

where S is the apparent power, defined as the product of the RMS voltage and current, and P is the active power, defined as

$$P \equiv \sum_{n=1}^{\infty} U_n I_n \cos \phi_n$$

.

Despite objections from many authors, notably Fryze in [22], the Budeanu model gained wide acceptance both in academia and in industry. In 1977 Emanuel stated that "Budeanu's model is today universally accepted" [23].

Budeanu's theory presented a number of problems. Firstly, it was notoriously difficult to measure the distortion and reactive power, the first instruments capable of these measurements only appearing some fifty years after these powers were first defined [24]. Also, more and more authors questioned the validity of the definitions as proposed by Budeanu. Czarnecki in [24] and later also Emanuel in [25] finally proved that the Budeanu powers have no physical meaning.

Whereas Budeanu tried to define reactive power flow with the use of harmonics, Fryze's definitions, as published in [22], are based on a wholly time-based approach. Fryze decomposed the current into a component having the same waveform as the source voltage,  $i_a$ , and a residual component,  $i_n$ , using the equations [05]:

$$i_a \equiv rac{P}{\left\|u

ight\|^2} u$$

and

$$i_n \equiv i - i_a$$

where  $\|u\|$  is the voltage RMS value and P is the average active power over a period.

The component  $i_a$  represents the active current component, while the component  $i_n$  represents the current associated with non-active power. These currents are mutually orthogonal, giving

$$\|i\|^2 = \|i_n\|^2 + \|i_n\|^2$$

.

This can be seen from the definition as well as from Fig. 4-1, presented below.

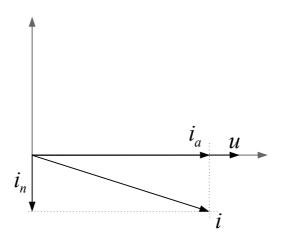

Fig. 4-1: Fryze's orthogonal currents

Multiplying Eq. 4-5 by  $\|u\|^2$  produces the following definition of non-active power:

$$S^2 = P^2 + Q_F^2$$

, Eq. 4-6  $Q_F \equiv \|u\| \|i_n\| = \sqrt{S^2 - P^2}$ .

Fryze's theory has been demonstrated to be correct [26], and has provided a basis for many other authors' theories.

Since the 1970s power electronics enabled the development of compensators that could follow a nearly arbitrary reference signal. This prompted renewed efforts to define non-active power for multiphase systems. An instantaneous method, rather than an average method such as the Fryze theory discussed above, was needed to control compensators providing real-time compensation with very fast response times.

Many theories have been put forward. Some have since been totally refuted, and some have been upheld for certain conditions but rejected in other cases. In almost all cases these theories have been extended and deliberated on by numerous authors. Only a few of these theories, relevant to the flicker compensator, can be discussed here. No less important, however, are the contributions of [27][28][29][30] and many others.

# 4.2. *p-q* Theory

In 1983 Akagi et al. introduced a novel definition of instantaneous active and imaginary powers [31]. Akagi followed Fryze's lead in defining the active current to be a dot product of the current and

voltage. In contrast to Fryze his definition of imaginary power was based on a cross product, and therefore completely different from any previous definition.

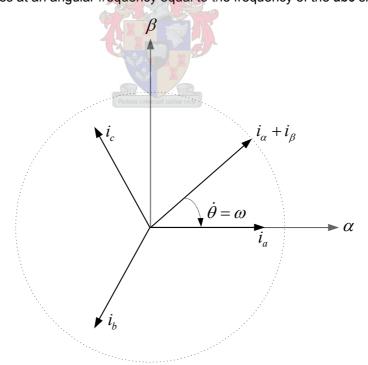

Akagi's theory is defined in the  $\alpha - \beta$  coordinate system. This coordinate system is briefly described in the following paragraph.

## 4.2.1. $\alpha$ - $\beta$ Coordinates

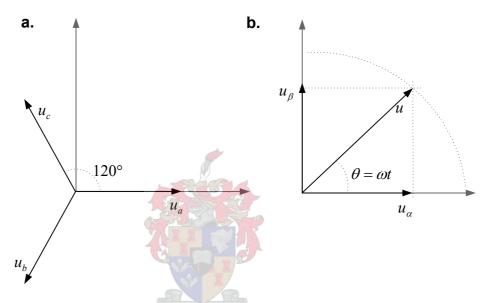

Traditionally, three-phase voltages are viewed as three voltage vectors in a plane, ideally separated by exactly 120°.

Fig. 4-2: Traditional three-phase voltage representation and  $\alpha$ - $\beta$  voltage representation

This representation contains redundant information. As the voltages are represented in a plane, only two variables should be necessary to uniquely describe the three-phase voltages.

As an example, it should be clear from Fig. 4-2a that the  $\alpha$  -component of the voltage vector  $u_c$  may, via simple trigonometry, be found to be:

$$u_{c\alpha} = \cos(120^\circ) \times u_c = -\frac{1}{2} \times u_c \,. \label{eq:uca}$$

Eq. 4-7

The full transform, known as the Clark transform, is given in Eq. 4-8:

$$\begin{bmatrix} u_{\alpha} \\ u_{\beta} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} u_{a} \\ u_{b} \\ u_{c} \end{bmatrix}.$$

Eq. 4-8

The  $\sqrt{\frac{2}{3}}$  scalar factor does not follow from the trigonometry, but is added for convenience in power calculations.

This transformation is also valid for three-phase currents, by virtue of the same arguments that were followed for voltages.

## 4.2.2. p-q Theory in $\alpha-\beta$ coordinates

Conventional instantaneous power in a three-phase circuit may be defined as:

$$p \equiv u \bullet i = u_a i_a + u_b i_b + u_c i_c , \qquad \qquad \textbf{Eq. 4-9}$$

with the voltages referenced to an artificial common node such that

$$u_a + u_b + u_c = 0$$

.

It can be shown that

$$p = u_{\alpha} \bullet i_{\alpha} + u_{\beta} \bullet i_{\beta}$$

Eq. 4-11

also holds. This is an expected result, as Eq. 4-11 is basically a reaffirmation of Eq. 4-9, stated in a different coordinate system. Akagi goes further and defines a new quantity q:

$$q=u_{\alpha} imes i_{\beta}+u_{\beta} imes i_{\alpha}$$

. Eq. 4-12

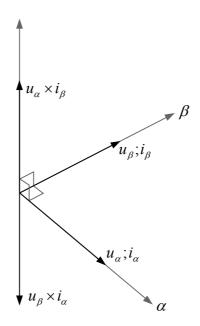

Fig. 4-3: q does not lie in the  $\alpha$ - $\beta$  plane

From Fig. 4-3 it can be seen that q does not lie in the  $\alpha - \beta$  plain, but is perpendicular to it. Consequently, q cannot be regarded as being a conventional electrical quantity. The unit of q can be neither W, VA nor VAR. Akagi names this new quantity "instantaneous imaginary power".

The current components in terms of the powers p and q are found by taking:

$$\begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} = \begin{bmatrix} u_{\alpha} & u_{\beta} \\ -u_{\beta} & u_{\alpha} \end{bmatrix}^{-1} \begin{bmatrix} p \\ q \end{bmatrix}$$

$$= \begin{bmatrix} u_{\alpha} & u_{\beta} \\ -u_{\beta} & u_{\alpha} \end{bmatrix}^{-1} \begin{bmatrix} p \\ 0 \end{bmatrix} + \begin{bmatrix} u_{\alpha} & u_{\beta} \\ -u_{\beta} & u_{\alpha} \end{bmatrix}^{-1} \begin{bmatrix} 0 \\ q \end{bmatrix}$$

$$= \begin{bmatrix} i_{\alpha p} \\ i_{\beta p} \end{bmatrix} + \begin{bmatrix} i_{\alpha q} \\ i_{\alpha q} \end{bmatrix}$$

where

Eq. 4-13

$$\begin{split} i_{\alpha p} &= \frac{u_{\alpha}}{u_{\alpha}^2 + u_{\beta}^2} \, p, \\ i_{\alpha q} &= \frac{-u_{\beta}}{u_{\alpha}^2 + u_{\beta}^2} \, q, \\ i_{\beta p} &= \frac{u_{\beta}}{u_{\alpha}^2 + u_{\beta}^2} \, p, \\ i_{\beta q} &= \frac{u_{\alpha}}{u_{\alpha}^2 + u_{\beta}^2} \, q. \end{split}$$

The instantaneous real power can now be found in terms of the component powers *p* and *q*:

$$\begin{bmatrix} p_{\alpha} \\ p_{\beta} \end{bmatrix} = \begin{bmatrix} u_{\alpha}i_{\alpha} \\ u_{\beta}i_{B} \end{bmatrix} = \begin{bmatrix} u_{\alpha}i_{\alpha p} + u_{\alpha}i_{\alpha q} \\ u_{\beta}i_{\beta p} + u_{\beta}i_{\beta q} \end{bmatrix}$$

Eq. 4-15

$$p = p_{\alpha} + p_{\beta} = \frac{u_{\alpha}^{2}}{u_{\alpha}^{2} + u_{\beta}^{2}} p + \frac{-u_{\alpha}u_{\beta}}{u_{\alpha}^{2} + u_{\beta}^{2}} q + \frac{u_{\beta}^{2}}{u_{\alpha}^{2} + u_{\beta}^{2}} p + \frac{u_{\alpha}u_{\beta}}{u_{\alpha}^{2} + u_{\beta}^{2}} q.$$

Eq. 4-16

A number of important conclusions may be drawn from Eq. 4-16:

- The second and fourth terms in Eq. 4-16 sum to zero, indicating that q forms no part of the power flowing from the source to the load.

- Because q does not contribute to the power flow, but does increase line currents, (and therefore losses and possibly voltage distortion) q should be compensated.

- Because q is not associated with a flow of real power, a compensator compensating q

only should not require any mechanism for energy storage.

The instantaneous real power p may further be divided into a constant component,  $\overline{p}$ , and a fluctuating component  $\widetilde{p}$ . As p represents the flow of power from source to load, the component  $\widetilde{p}$  must necessarily imply the variation in the power flow. For times when

$$-\widetilde{p}>\overline{p}$$

Eq. 4-17

the net flow of power is negative (from load to source) which implies an exchange of energy between load and source.

Unfortunately neither  $\overline{p}$  nor  $\widetilde{p}$  can be determined instantaneously but must be calculated by filtering  $\overline{p}$  as the DC component from p. A compensator attempting to cancel  $\widetilde{p}$  would require an energy storage capability.

The instantaneous imaginary power q may also be divided into a constant component,  $\overline{q}$ , and a fluctuating component  $\widetilde{q}$ . In a three-phase, balanced, sinusoidal circuit  $\overline{q}$  is numerically equivalent to the conventional reactive power Q. Filtering this component from the power to be compensated prevents the compensator from doing power factor correction. In cases where compensating harmonics and noise is important, but the power factor is not, this enables the design of an adequate compensator with a reduced power rating. In non-sinusoidal, unbalanced cases this property may still be utilised as an approximation. Care should however be taken as this may introduce substantial errors into the compensation effort.

Akagi's p-q theory has been extensively implemented in industry, and generally performs well as a control philosophy in symmetrical systems. Under asymmetrical conditions the performance is not as good. The reason for this lies at the very heart of the theory. Akagi never motivates the choice of the definitions of q, other than by proving that q, as defined in his paper, causes currents to flow that does not contribute to the transmission of power. It is therefore completely possible that other power terms may be defined similarly, contributing to the currents flowing in the system but not contributing to the flow of real power. Czarnecki analyzes the non-symmetrical case in [32], and finds p-q theory to be less than satisfactory in explaining the power phenomena in such cases. Kohata in [33] also reported such errors in an applied compensator.

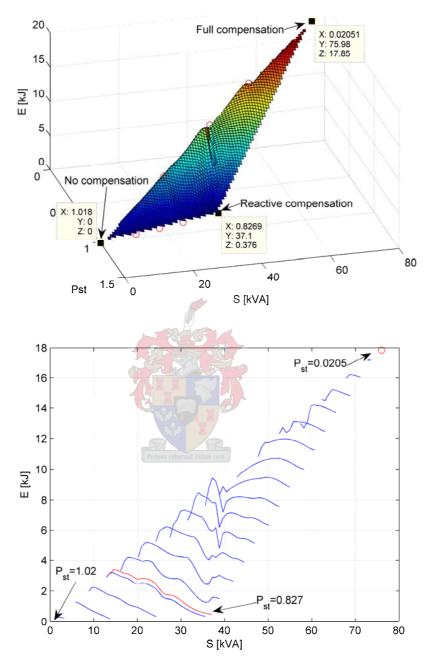

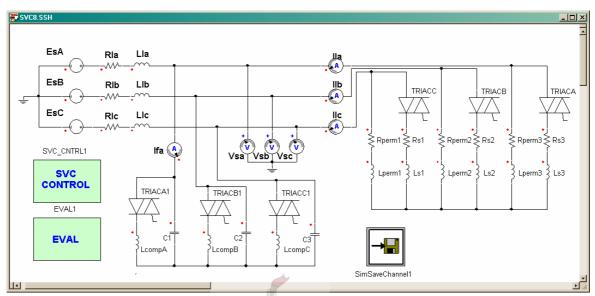

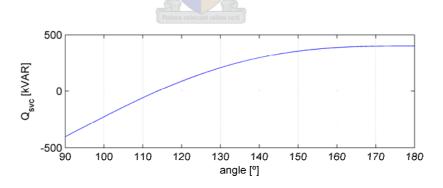

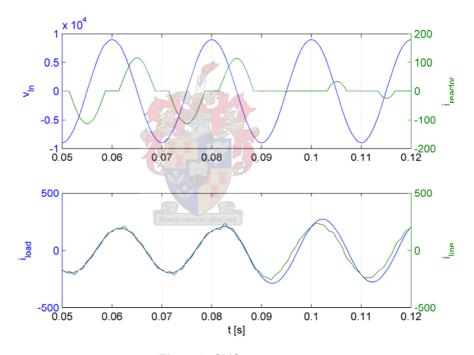

In 1992 Willems [34] extended p-q theory to multiphase systems. As the industrial flicker sources in this study are three-phase only, this extension is not investigated in this thesis.