### A Tool Kit for the Design of Superconducting Programmable Gate Arrays

#### **Coenrad Johann Fourie**

Dissertation presented for the Degree of **Doctor of Philosophy in Engineering** at the University of Stellenbosch

#### **Promoter:**

Prof. W. J. Perold

December 2003

#### Declaration

I, the undersigned, hereby declare that the work contained in this dissertation is my own original work, unless stated otherwise, and that I have not previously in its entirety or in part submitted it at any university for a degree.

Signature: .....

Date: 31 October 2003

## **Abstract**

The development of a tool kit for the design of superconducting programmable gate arrays (SPGAs) is discussed. A circuit optimizer using genetic algorithms is developed and evaluated. Techniques and a program are also developed for the generation of segmentized 3D models with which to calculate inductance in circuit structures through FastHenry. The ability to add random variations to the dimensions of the models is included. These tools are then used to design novel latching elements that allow the construction of reprogrammable Rapid Single Flux Quantum (RSFQ) circuits. A circular process is used, whereby layouts are converted back to circuit diagrams through element extraction, and reoptimized if necessary. Two programmable frequency dividers are then designed; one for testing the routing and switch structures and programming architecture of an SPGA, and another compact one for testing the latching elements and off-chip interface. The dissertation concludes with an overview of the circuits necessary for the implementation of a fully functional SPGA.

# **Opsomming**

Die ontwikkeling van 'n gereedskapstel vir die ontwerp van supergeleier FPGA's (SPGA's) word bespreek. Eerstens word 'n stroombaanoptimeerder, wat met genetiese algoritmes funksioneer, ontwikkel en geëvalueer. Daarna word tegnieke en 'n program ontwikkel om driedimensionele segmentmodelle te genereer waaruit *FastHenry* die induktansie van stroombaanstrukture kan bepaal. Die vermoë om toevalsveranderinge by die dimensies van die modelle te voeg, is ook ingesluit. Hierdie gereedskap word dan gebruik om nuwe grendelelemente te ontwerp waarmee herprogrammeerbare *Rapid Single Flux Quantum* (RSFQ) stroombane gebou kan word. 'n Sirkulêre proses word gevolg, waarvolgens uitlegte na stroombaandiagramme teruggeskakel kan word (deur elementonttrekkings) en, indien nodig, heroptimeer kan word. Twee programmeerbare frekwensiedelers word daarna ontwerp; een om die pulsvervoer- en skakelstrukture, asook programmeringsargitektuur van 'n SPGA te toets, en 'n ander, kompakter een om die grendelelemente en warmlogika koppelvlakke mee te toets. Die proefskrif sluit af met 'n oorsig oor die stroombane benodig vir die implementering van 'n volledig funksionele SPGA.

## Acknowledgements

Thanks go to everybody who endured countless questions – from the inquisitive and well-prepared down to the stupidly impulsive – from me during the most critical stages of the design and layout of the programmable frequency divider. Oleg Mukhanov, Masoud Radparvar, Steve Kaplan and Sergey Tolpygo of Hypres were particularly harassed through e-mail. Other foreign contributors were Anna Kidiyarova-Shevchenko and Thomas Ortlepp. I am also particularly indebted to Steve Whiteley and his array of programs, as well as support, that made most of the simulations for this project possible.

Local colleagues who endured a barrage of questions include Petrie Meyer, John Cloete, Keith Palmer, Riana Geschke and Ludwig Schwardt.

To Héndri – thanks for the late-night sessions in probability theory.

To Willem Perold, thank you for supporting me in taking my work and theories to faraway conferences.

Lastly, a big thank you to my inquisitive students who asked such hard and uncompromising questions, especially on my approach to circuit modelling.

# **Contents**

|        |     | JRES                                                  |    |

|--------|-----|-------------------------------------------------------|----|

|        |     | LES                                                   |    |

|        |     | URE                                                   |    |

| Снарті |     | TE - INTRODUCTION                                     |    |

| 1.1    | _   | perconducting logic families                          |    |

| 1.2    |     | ctrical simulation tools, models and equations        |    |

| 1.3    |     | nmary of dissertation                                 |    |

|        |     | VO - CIRCUIT OPTIMIZATION THROUGH GENETIC ALGORITHMS  |    |

| 2.1    |     | oduction                                              |    |

| 2.2    |     | nte Carlo parameters and procedures                   |    |

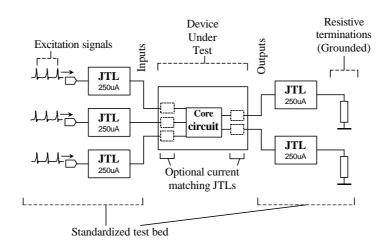

| 2.2    |     | Uniform test setup                                    |    |

| 2.2    |     | Monte Carlo models                                    |    |

| 2.2    |     | Trimming                                              |    |

| 2.2    |     | Failure detection                                     |    |

| 2.2    | 5   | Closed-loop design                                    | 13 |

| 2.3    | Ma  | rgin analysis                                         | 13 |

| 2.4    |     | netic algorithms                                      |    |

| 2.5    |     | ness evaluation                                       |    |

|        | .1  | Summary of evalution constraints                      |    |

|        | .2  | Mapping theoretical yield to fitness                  |    |

| 2.5    |     | Noise in yield-based fitness values                   |    |

| 2.6    |     | FQ DC-Resettable latch example                        |    |

| 2.7    |     | mparison of genetic and random optimization methods   |    |

| 2.8    |     | nclusions                                             |    |

|        |     | REE - INDUCTANCE EXTRACTION                           |    |

| 3.1    |     | oduction                                              |    |

| 3.2    |     | uctance tolerance and the effect on RSFQ circuits     |    |

| 3.3    |     | uctance calculation techniques                        |    |

|        | .1  | Mathematical and 2D approach                          |    |

|        | .2  | Numerical calculations on 3D models                   |    |

| 3.4    | _   | mented 3D models                                      |    |

|        | .1  | Segments and filaments                                |    |

| 3.4    |     | Current flow considerations – injection and cornering |    |

| 3.4    | -   | Basic structures used to build 3D models              |    |

| 3.4    |     | Hollow models for conductors                          |    |

| 3.5    |     | thod of images                                        |    |

| 3.5    | . – | Reflection plane                                      |    |

| 3.5    |     | Scaling factors for finer discretization              |    |

| 3.6    |     | mplex structures                                      |    |

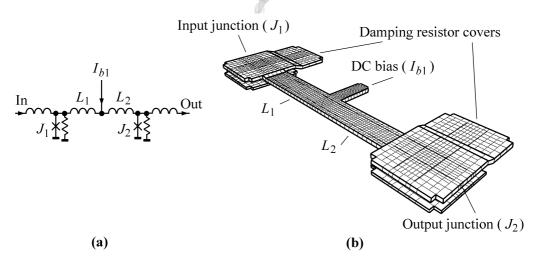

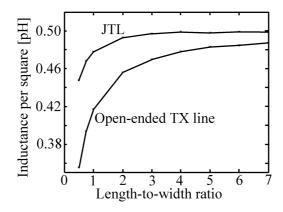

| 3.6    |     | Josephson transmission line                           |    |

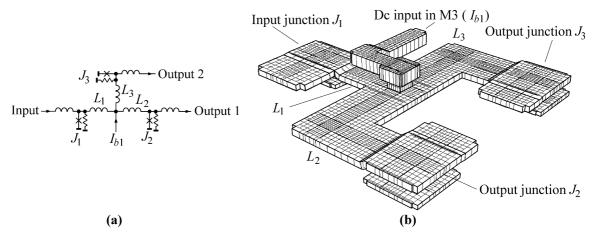

| 3.6    |     | RSFQ pulse splitter                                   |    |

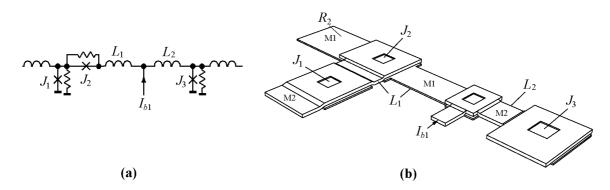

| 3.6    | .3  | Series junctions                                      | 44 |

| 3.6        | .4 Damping resistors                                               | 45  |

|------------|--------------------------------------------------------------------|-----|

| 3.6        | .5 Simplifying models                                              | 47  |

| 3.7        | Mutual inductance                                                  | 48  |

| 3.8        | Utilization of 3D inductance models in design process              | 51  |

| 3.9        | Simulated inductance spreads                                       |     |

| 3.10       | Conclusions                                                        | 53  |

| Снарте     | R FOUR - NOVEL COMPONENT DESIGN                                    | 55  |

| 4.1        | Introduction                                                       | 55  |

| 4.2        | RSFQ elements                                                      | 55  |

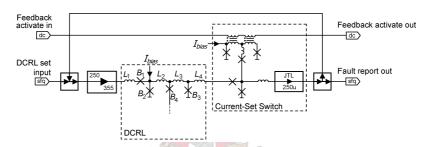

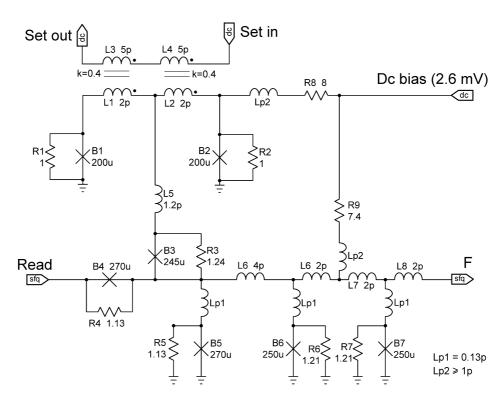

| 4.2        | .1 DC-Resettable Latch                                             |     |

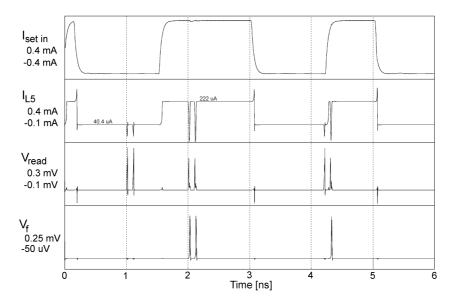

| 4.2        | .2 Current-Set switch                                              | 58  |

| 4.3        | COSL elements                                                      |     |

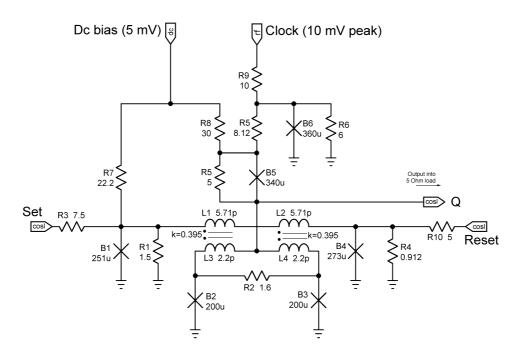

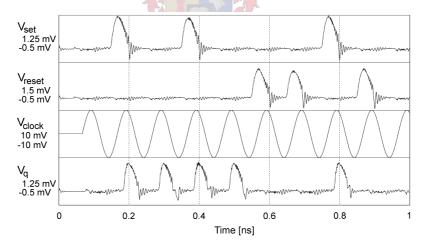

| 4.3        | .1 Set-Reset flip-flop                                             |     |

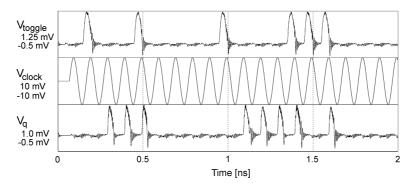

| 4.3        | .2 Toggle flip-flop                                                |     |

| 4.4        | Hybrid logic elements                                              |     |

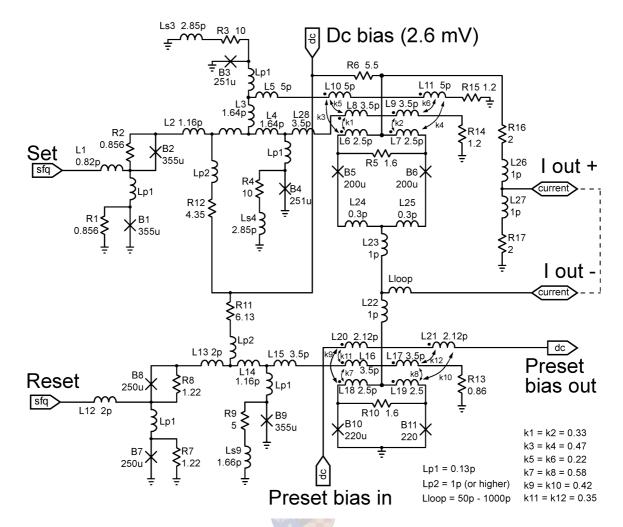

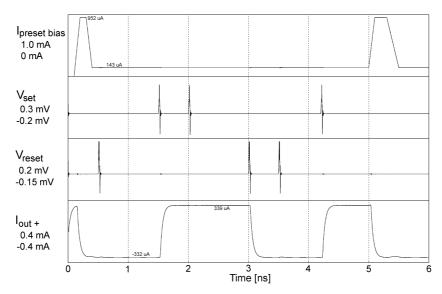

|            | .1 HUFFLE bipolar current switch                                   |     |

|            | .2 RSFQ-to-COSL converter                                          |     |

| 4.5        | Conclusion – Review of the recursive design process                |     |

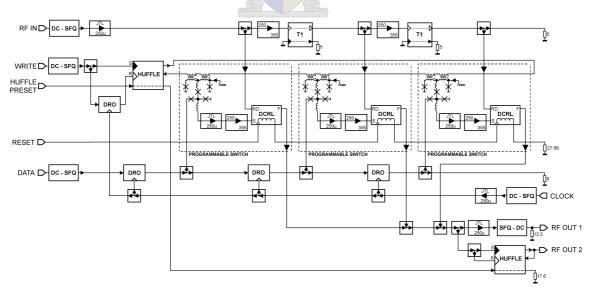

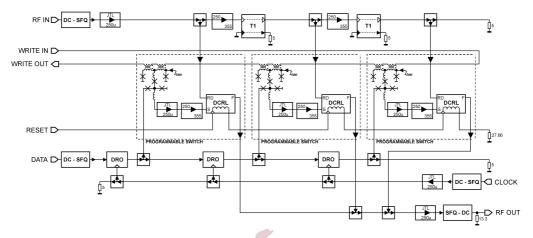

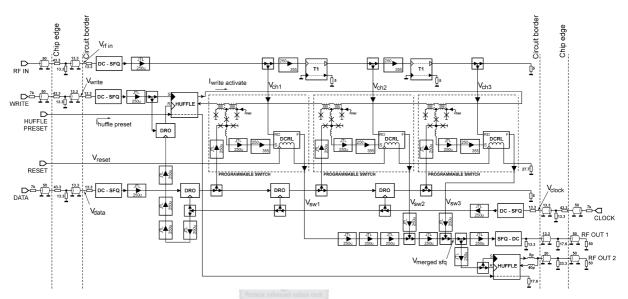

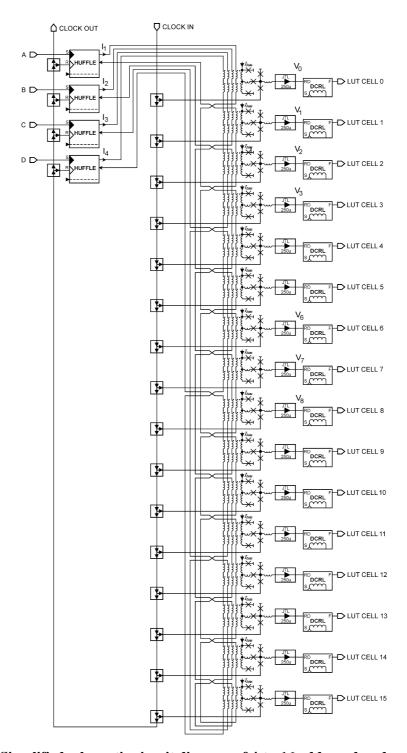

|            | CR FIVE - IMPLEMENTATION OF PROGRAMMABLE FREQUENCY DIVIDER         |     |

| 5.1        | Introduction                                                       |     |

| 5.2        | The FPGA as foundation to reprogrammable circuitry                 |     |

| 5.3        | Interconnection switches                                           |     |

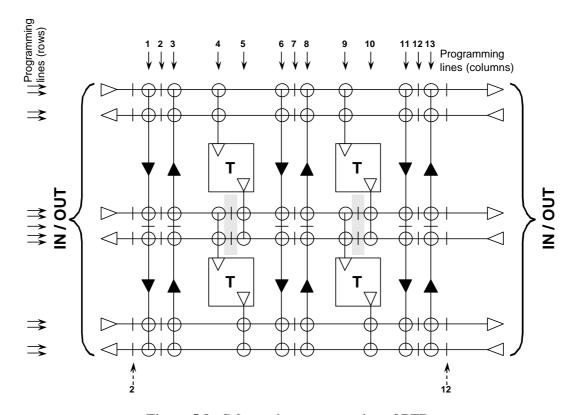

|            | .1 Crossbar switch                                                 |     |

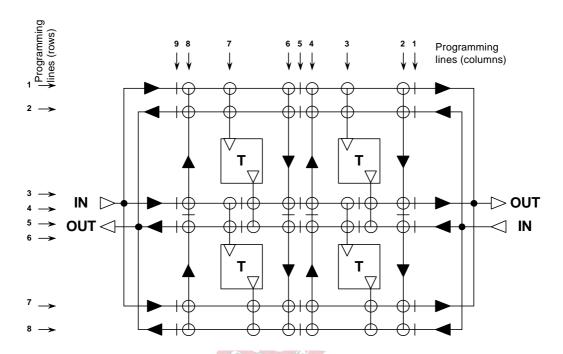

|            | .2 Inline switch                                                   |     |

| 5.3        |                                                                    |     |

| 5.4        | Architecture, routing channels and switch blocks                   |     |

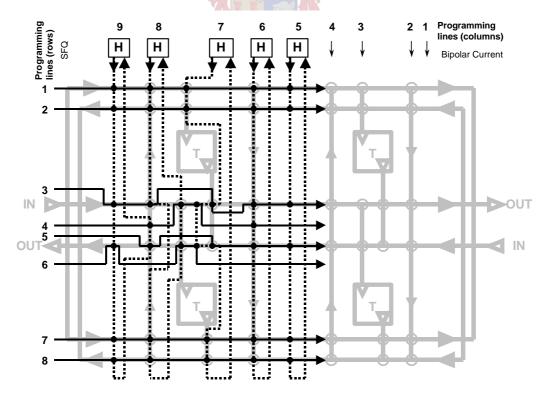

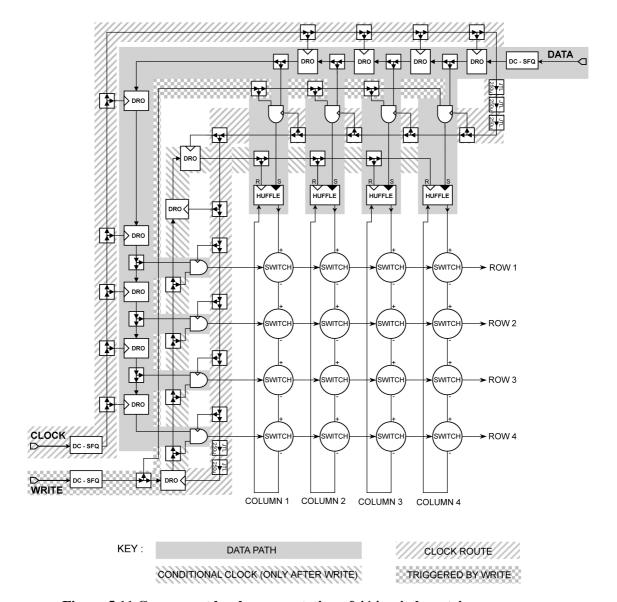

| 5.5        | Switch programming architecture                                    |     |

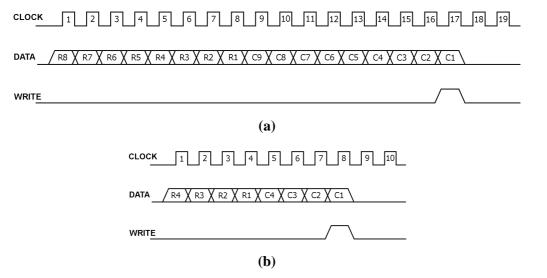

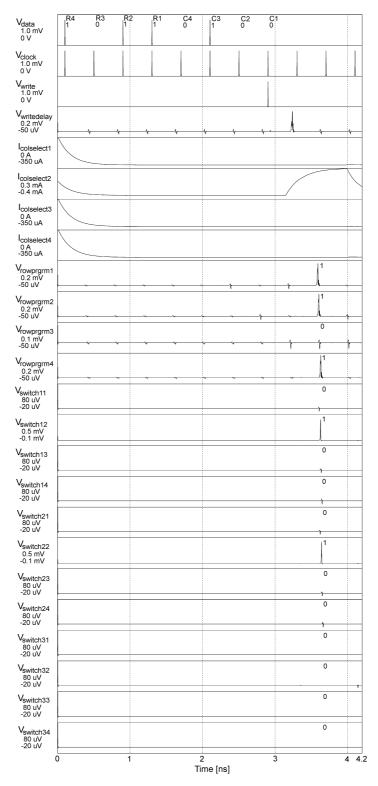

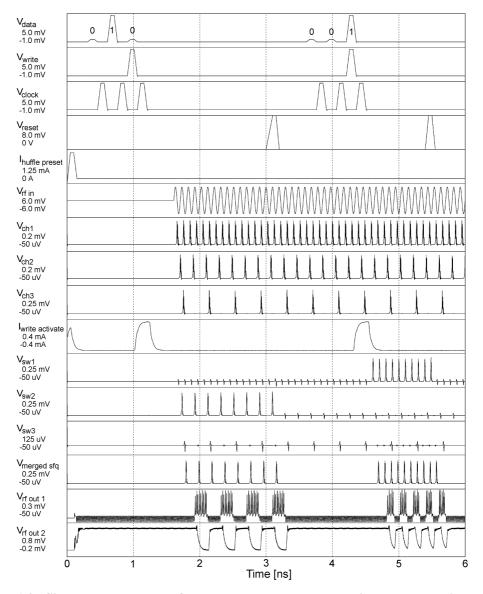

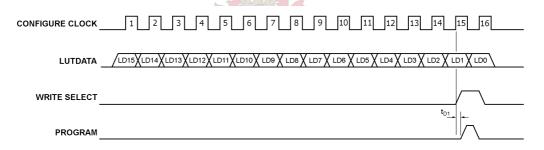

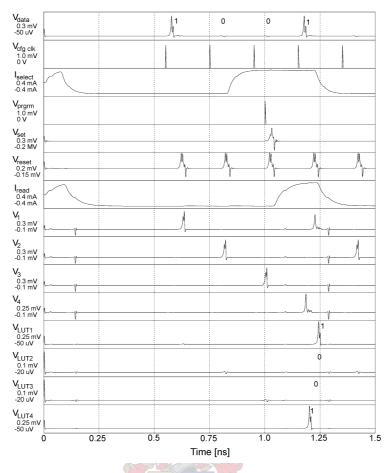

| 5.6        | Simulation results for switch programming                          |     |

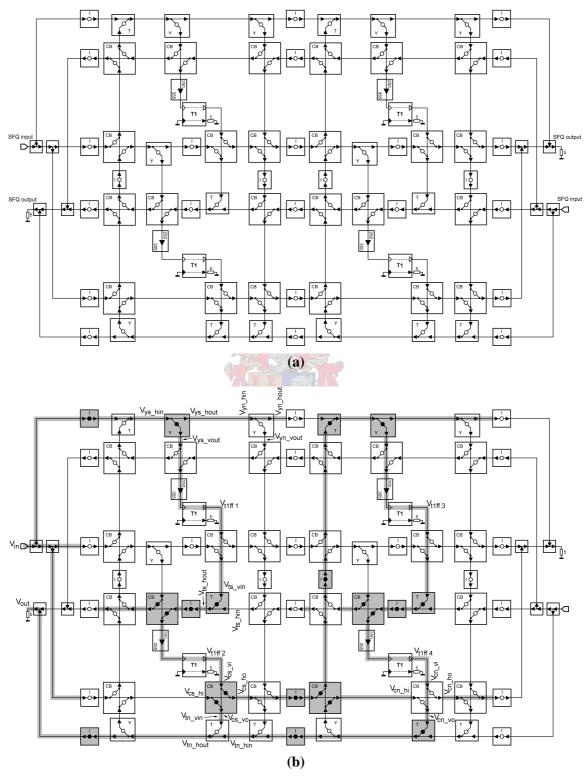

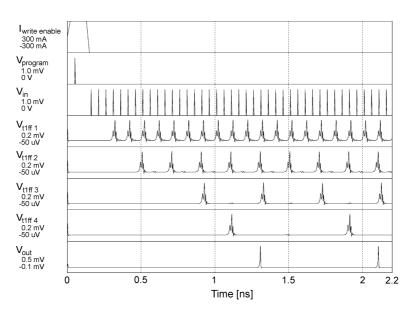

| 5.7        | Simulation results for a PFD configured for divide-by-16 operation |     |

| 5.8        | Conclusions                                                        |     |

|            | CR SIX - COMPACT PFD                                               |     |

| 6.1        | Introduction                                                       |     |

| 6.2        | Functional design                                                  |     |

|            |                                                                    |     |

| 6.3<br>6.4 | Programming specifications and timing                              |     |

| 6.5        |                                                                    |     |

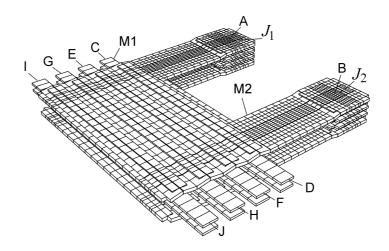

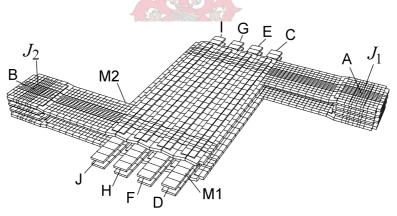

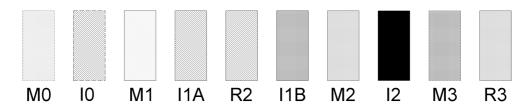

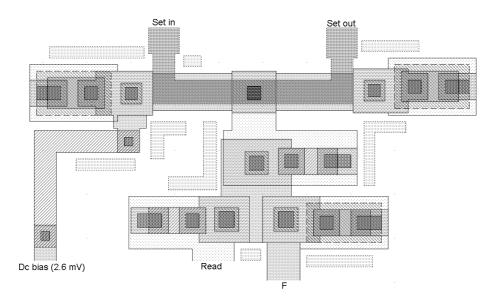

| 6.5        | Layout                                                             |     |

|            | $\mathcal{E}$ 3 1 1                                                |     |

| 6.5        |                                                                    |     |

| 6.5<br>6.5 | 1 3 11                                                             |     |

|            |                                                                    |     |

| 6.6        | Conclusions                                                        |     |

|            | R SEVEN - TOWARDS A FULL SPGA                                      |     |

| 7.1        | Introduction                                                       |     |

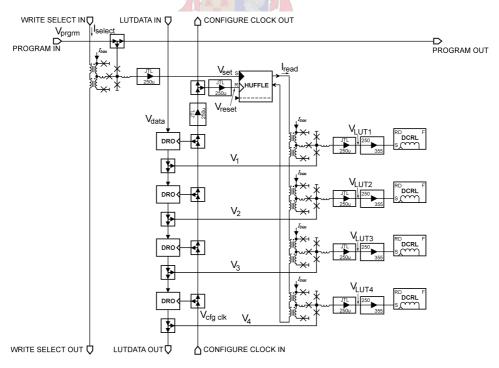

| 7.2        | Switch boxes                                                       |     |

| 7.3        | Subsystems of a configurable logic block                           |     |

| 7.3        | 1                                                                  |     |

| 7.3        | 1 6 6                                                              |     |

| 7.4        | Conclusions                                                        |     |

|            | R EIGHT - CONCLUSIONS                                              |     |

| Refere     | NC BS                                                              | 104 |

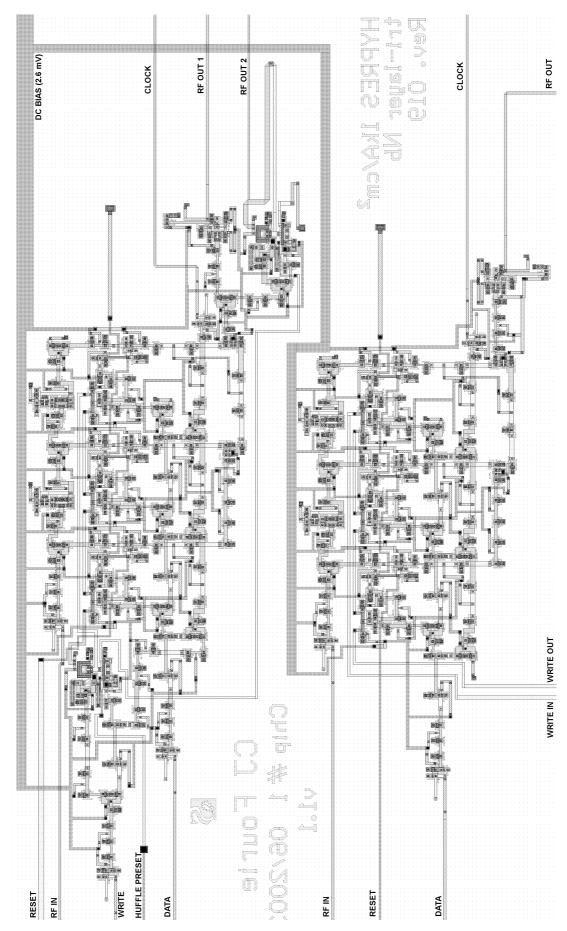

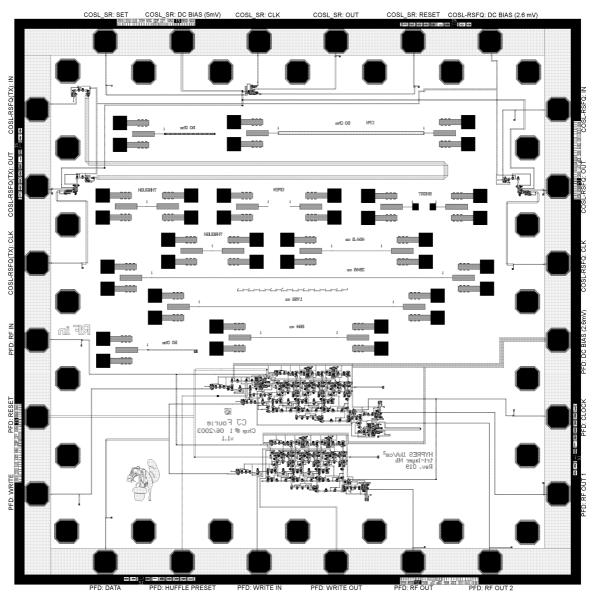

| APPENDIX A  | - SELECTED CIRCUIT SCHEMATICS AND LAYOUT MASKS                  | 110 |

|-------------|-----------------------------------------------------------------|-----|

| A.1 Ne      | w circuits                                                      | 110 |

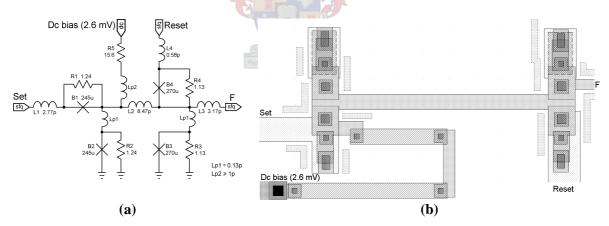

| A.1.1       | RSFQ DCRL                                                       | 110 |

| A.1.2       | Current-Set switch                                              | 111 |

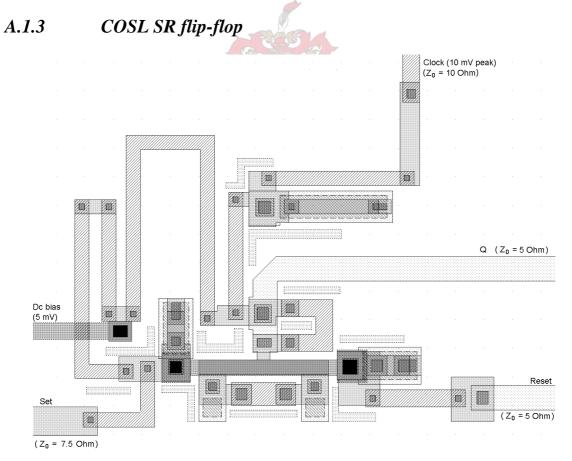

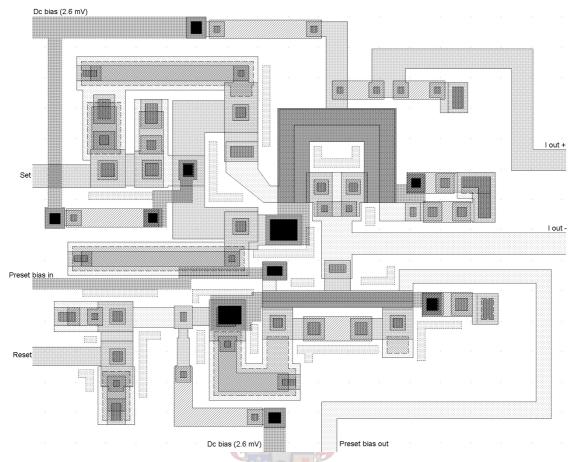

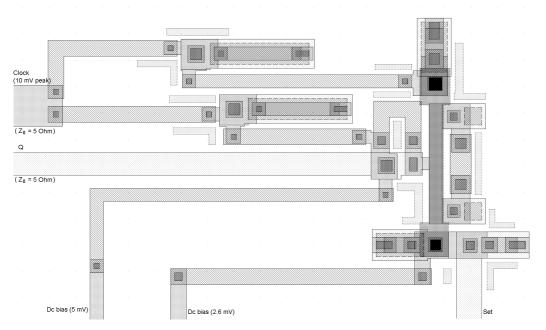

| A.1.3       | COSL SR flip-flop                                               | 111 |

| A.1.4       | HUFFLE                                                          | 112 |

| A.1.5       | RSFQ-to-COSL converter                                          | 112 |

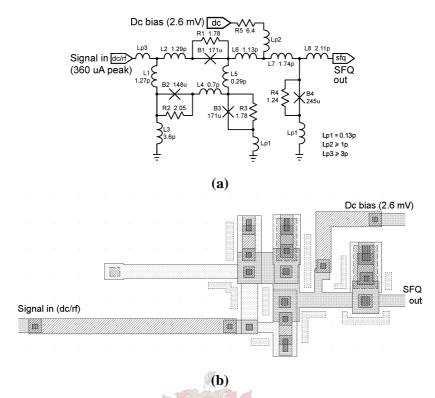

| A.2 Ex      | isting circuits                                                 | 113 |

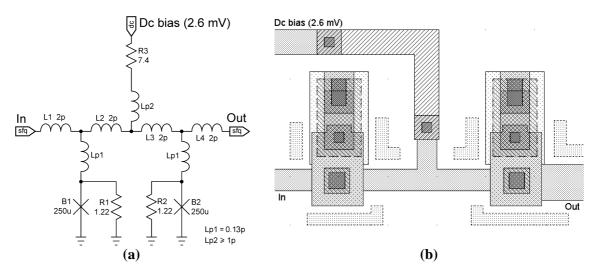

| A.2.1       | 250 μA JTL                                                      | 113 |

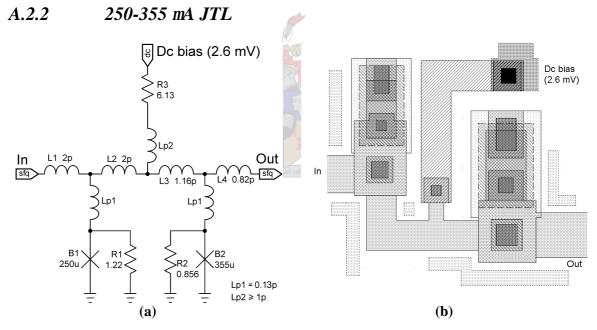

| A.2.2       | 250-355 μA JTL                                                  | 113 |

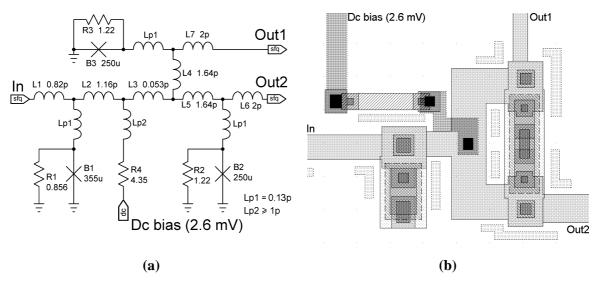

| A.2.3       | RSFQ pulse splitter                                             | 114 |

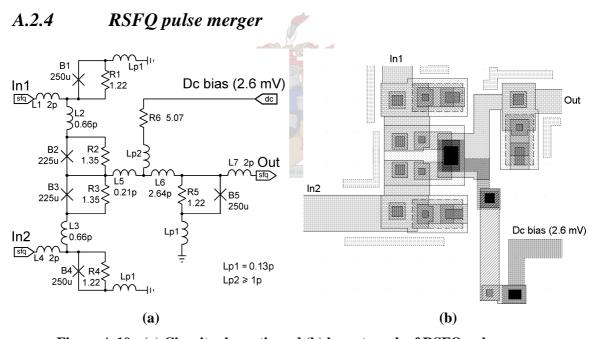

| A.2.4       | RSFQ pulse merger                                               | 114 |

| A.2.5       | RSFQ T1 flip-flop                                               | 115 |

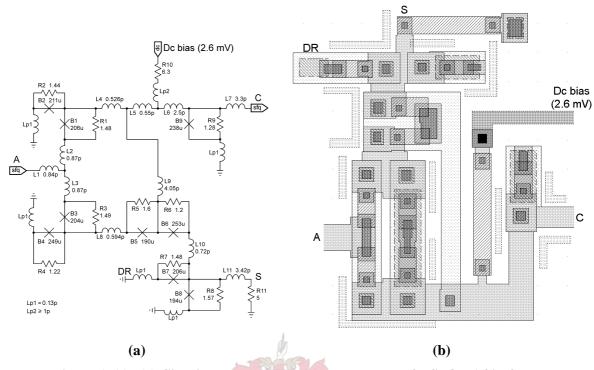

| A.2.6       | RSFQ DRO                                                        | 115 |

| A.2.7       | DC-to-SFQ converter                                             | 116 |

| A.2.8       | SFQ-to-DC converter                                             | 116 |

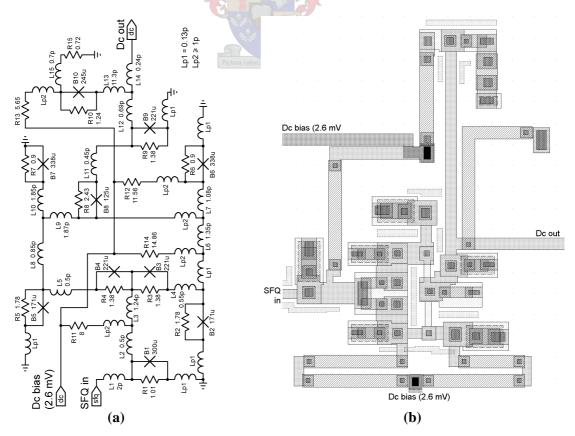

| A.3 PF      | D and subsystems                                                | 117 |

| A.3.1       | Inline switch                                                   | 117 |

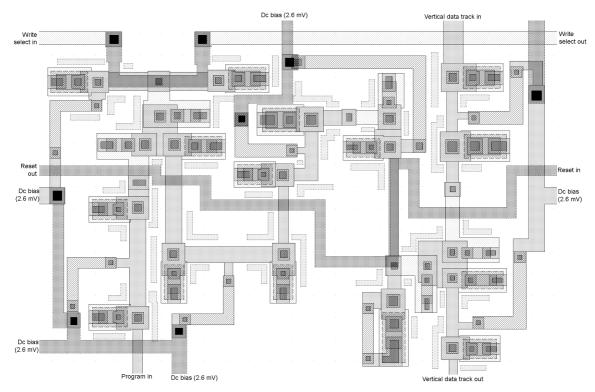

| A.3.2       | PFD layout                                                      | 117 |

| A.3.3       | Complete integrated circuit                                     | 119 |

|             | - SELECTED SOURCE CODE AND SIMULATION FILES                     |     |

|             | RSpice                                                          |     |

| B.1.1       | SFQ source                                                      |     |

| B.1.2       | Simulation input file for generic Monte Carlo analysis          |     |

| B.1.3       | Simulation input file for Monte Carlo analysis on layout model  |     |

|             | stHenry 3.0wr                                                   |     |

| B.2.1       | Example for microstrip over ground plane                        |     |

| B.2.2       | Sample output for two-conductor mutual inductance calculation v |     |

|             | of images                                                       |     |

|             | luct Pectura ruburant cultus reett                              |     |

| B.3.1       | Example for two microstrips over ground plane                   |     |

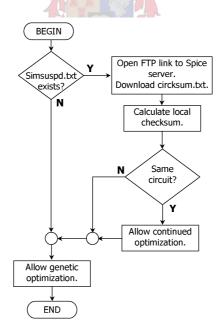

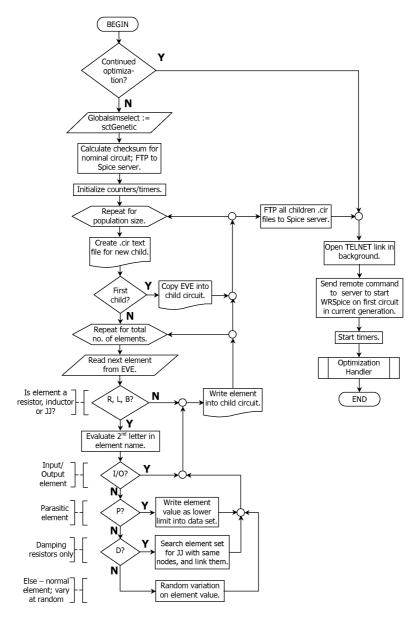

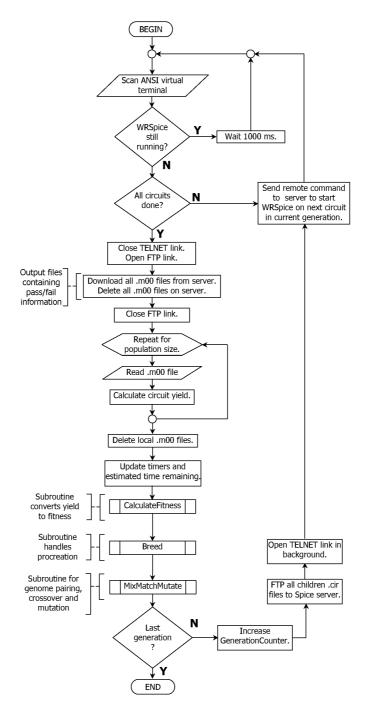

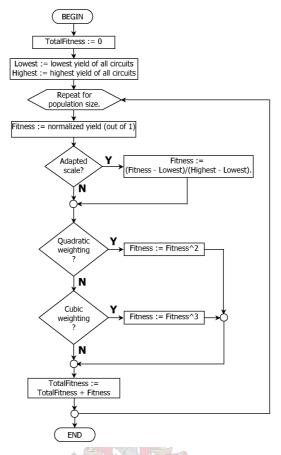

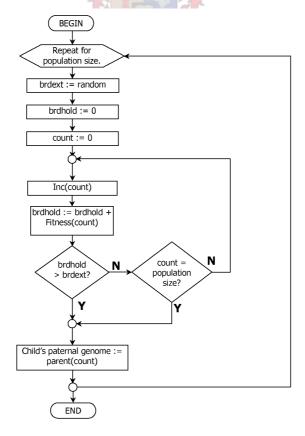

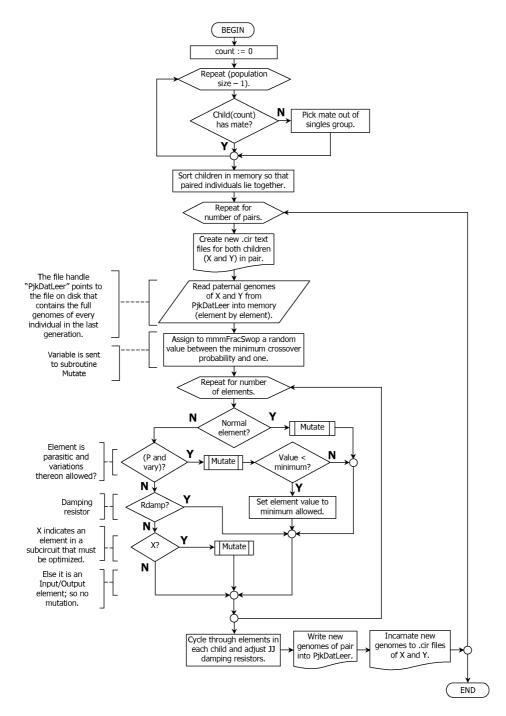

|             | - GENETIC OPTIMIZATION PROGRAM OVERVIEW                         |     |

|             | gorithmic flow charts                                           |     |

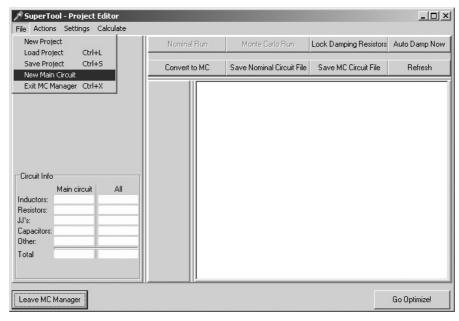

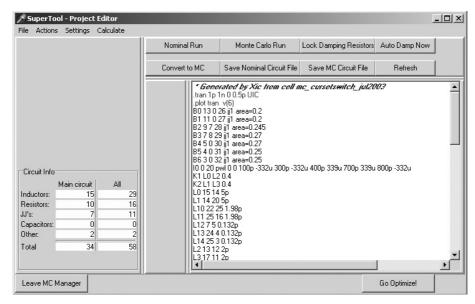

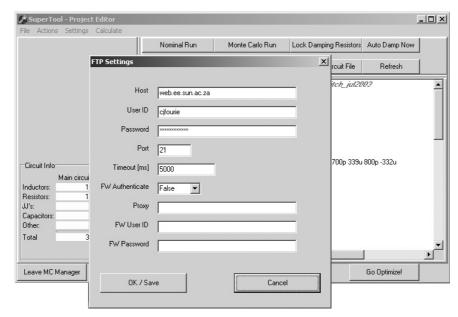

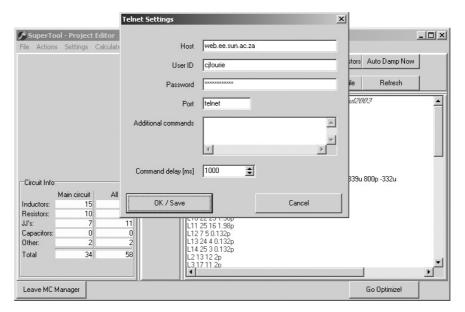

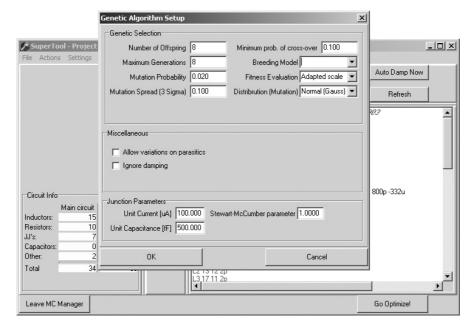

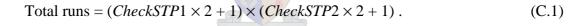

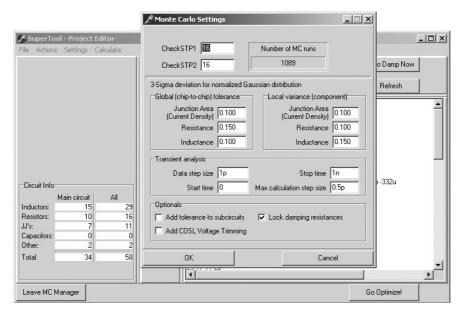

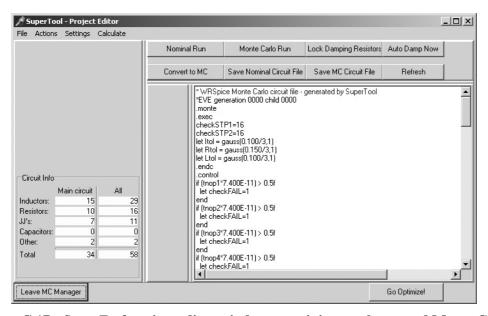

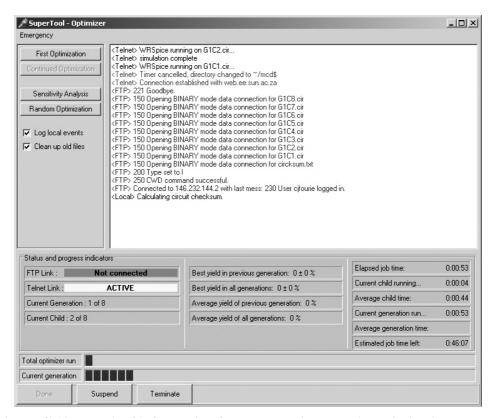

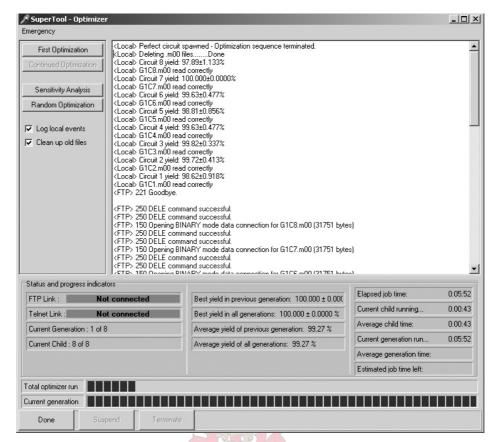

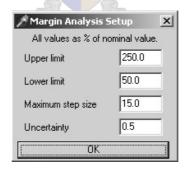

|             | reenshots and operating overview                                |     |

|             | oject save file header                                          |     |

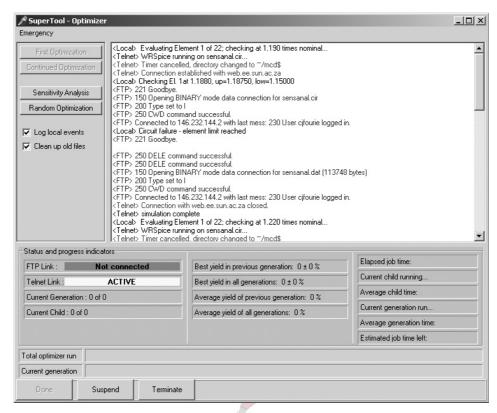

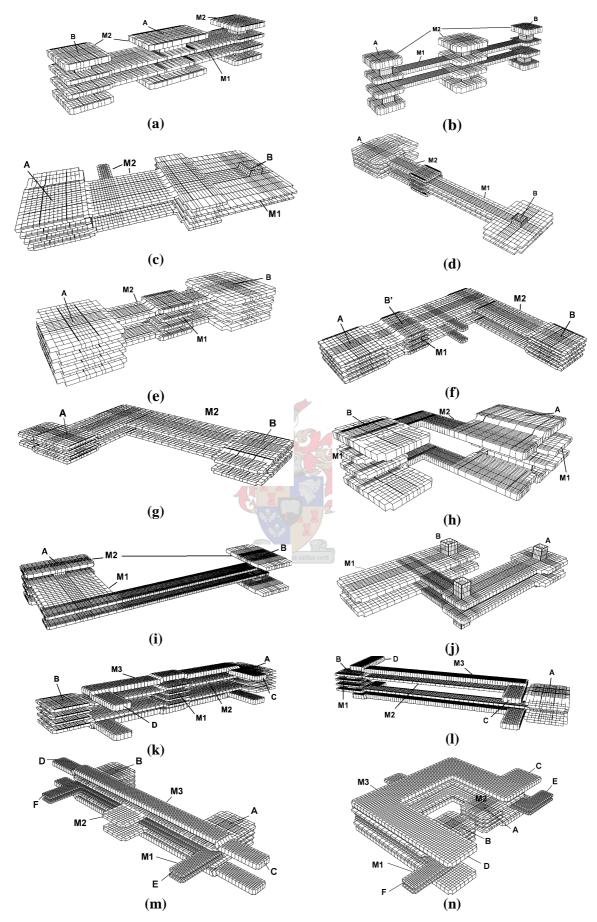

| APPENDIX I) | - FULL SET OF 3D INTER-JUNCTION INDUCTANCE MODELS               | 140 |

# **List of Figures**

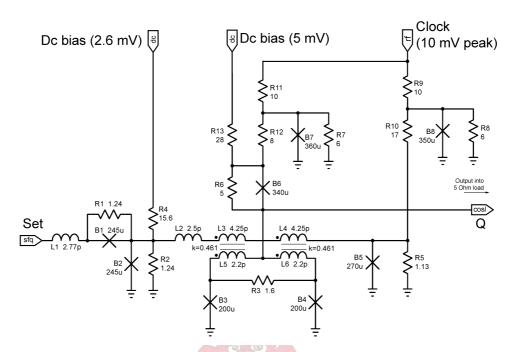

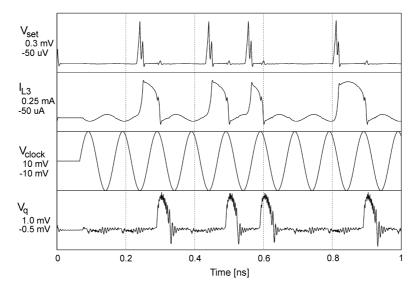

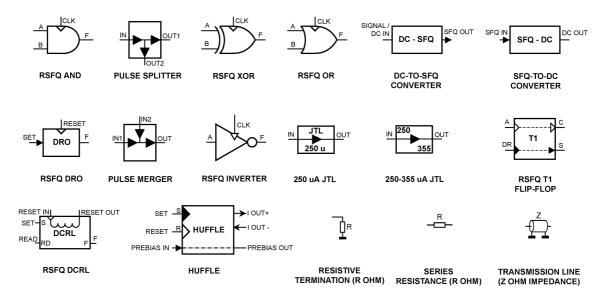

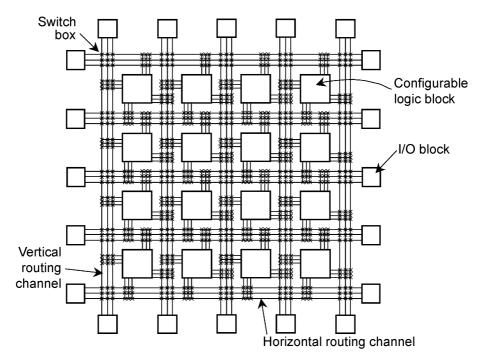

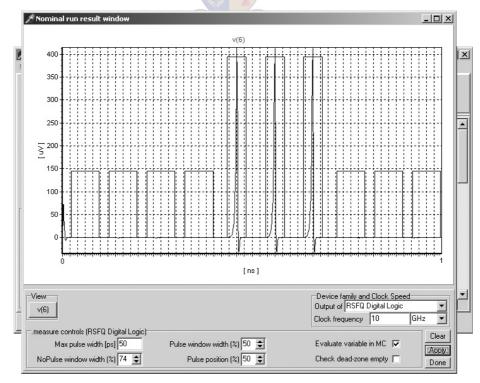

| Figure 2.1: Standard test setup for Monte Carlo analysis of RSFQ circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

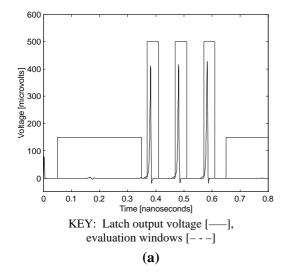

| Figure 2.2: Evaluation constraints for RSFQ DC-Resettable latch: (a) nominal voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | e    |

| output vector and (b) nominal flux-loop current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12   |

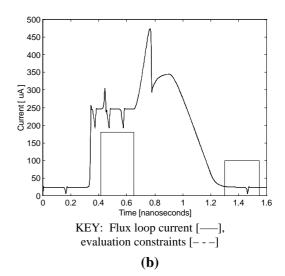

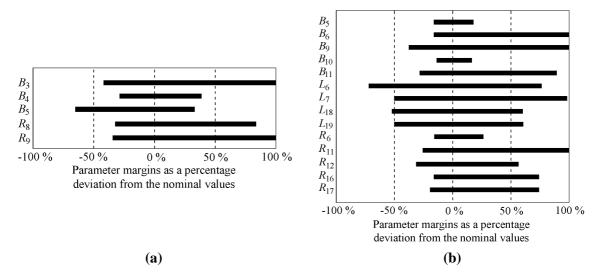

| Figure 2.3: Margin analysis results for the most critical parameters of (a) the Current-S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Set  |

| switch and (b) the HUFFLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14   |

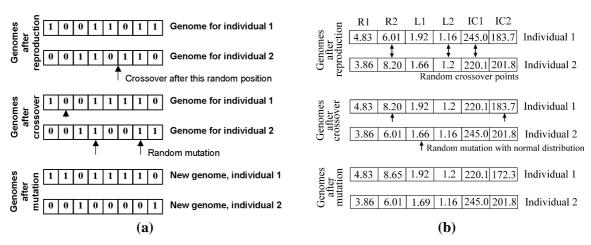

| Figure 2.4: Graphical representation of the genetic optimization process using (a) bina                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ıry  |

| string genomes and punctuated crossover and (b) real-valued genomes and random                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | n    |

| crossover                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15   |

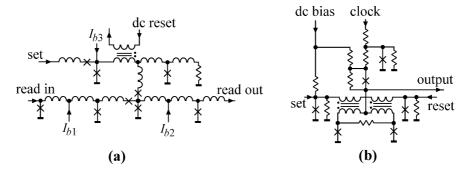

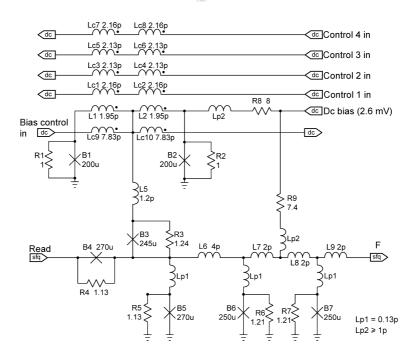

| Figure 2.5: Simplified schematic circuit diagrams for (a) RSFQ DC-Resettable latch as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nd   |

| (b) COSL Set-Reset flip-flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17   |

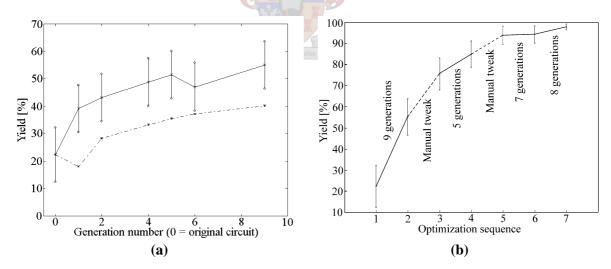

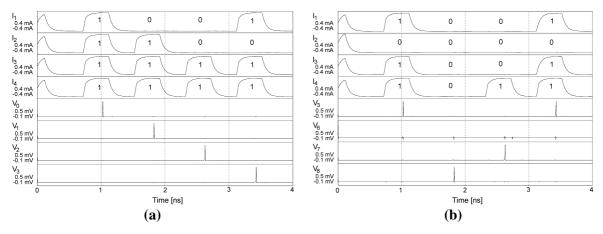

| Figure 2.6: Genetic optimization results for RSFQ DCRL: (a) yield vs generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| number for first sequence and (b) yield vs sequence for entire process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 18   |

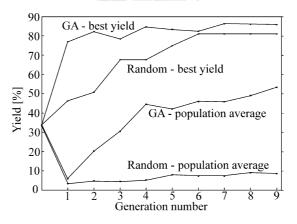

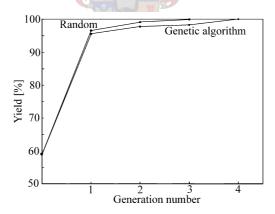

| Figure 2.7: Comparative results for a genetic algorithm and random optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| sequence starting with the same unoptimized COSL Set-Reset flip-flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19   |

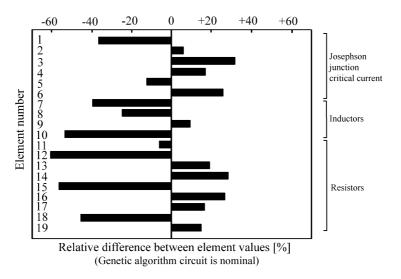

| Figure 2.8: Relative difference between the elements of the best COSL Set-Reset flip-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| flop from the genetic and random optimization processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20   |

| Figure 2.9: Comparative results for genetic and random optimization sequences starting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ıg   |

| with the same unoptimized COSL negative-output OR-gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20   |

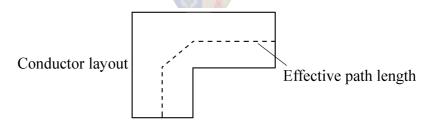

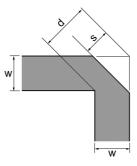

| Figure 3.1: Traditional approximation of the effective path length for inductance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| estimation around a corner in a thin-film conductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22   |

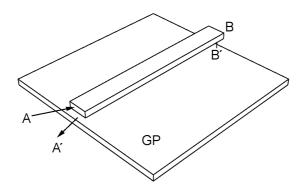

| Figure 3.2: Uniform microstrip over ground plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23   |

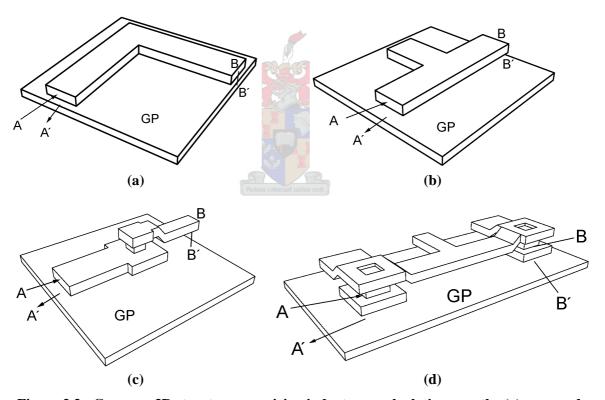

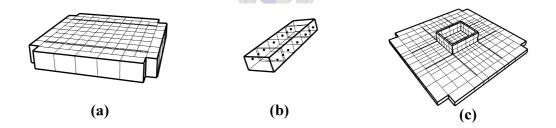

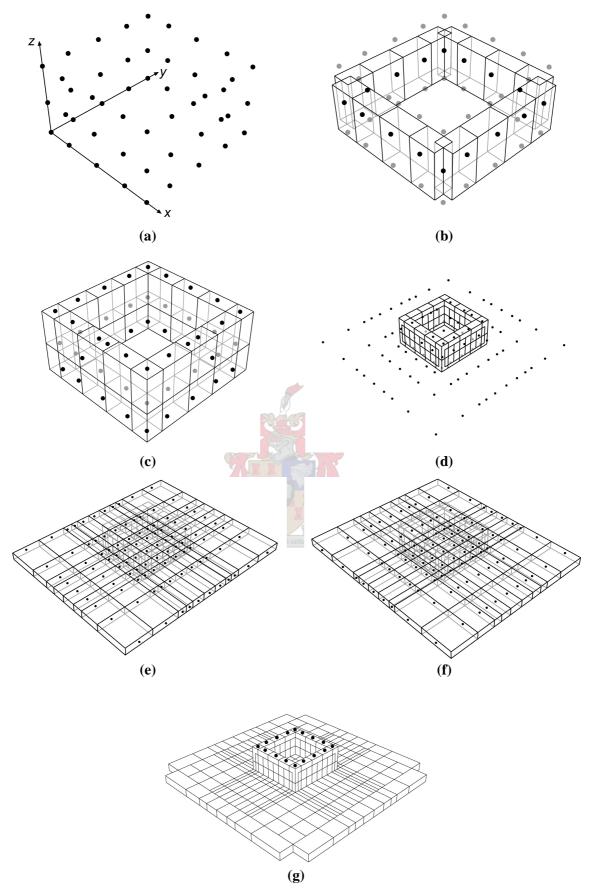

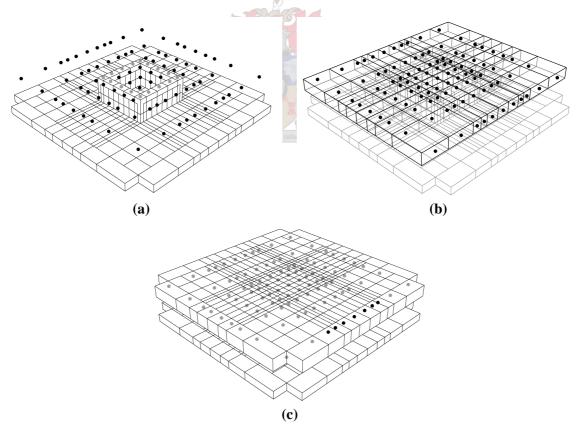

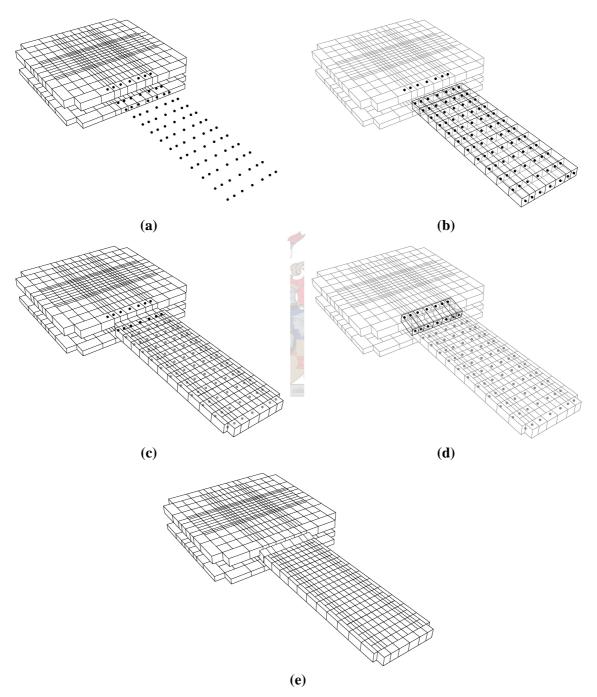

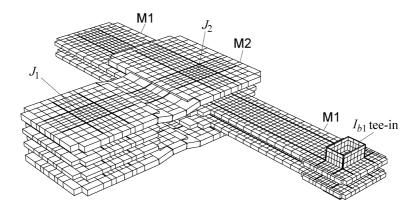

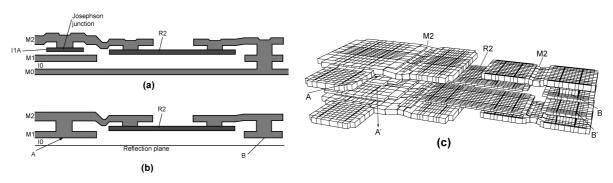

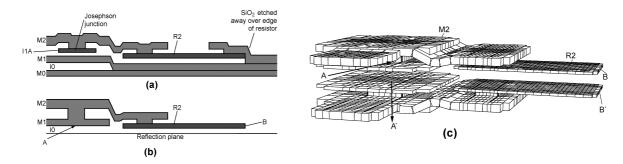

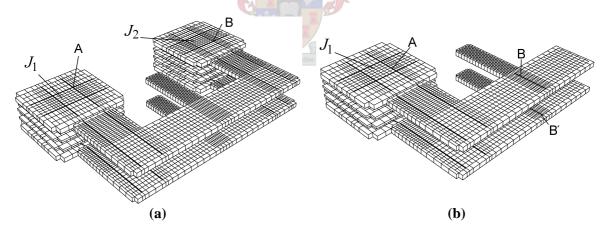

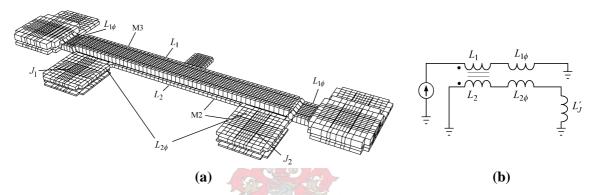

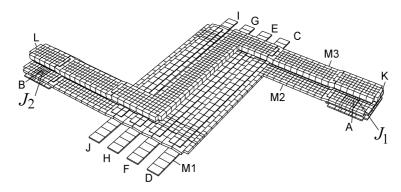

| Figure 3.3: Common 3D structures requiring inductance calculations are the (a) corner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | red  |

| microstrip, (b) microstrip with tee-in, (c) via-connected microstrips and (d)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| microstrip connecting two Josephson junctions, including damping resistor covers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| and dc tee-in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23   |

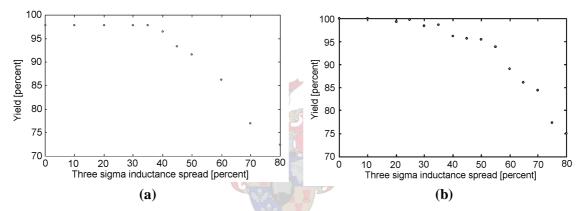

| Figure 3.4: Yield as a function of inductance spread for (a) HUFFLE and (b) RSFQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| DCRL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24   |

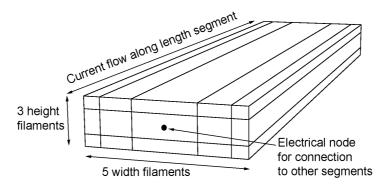

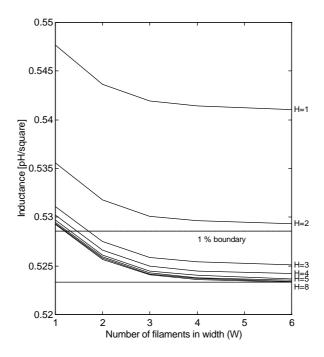

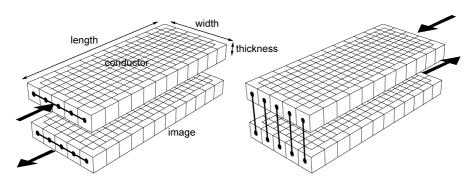

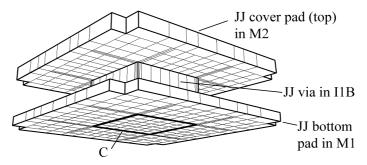

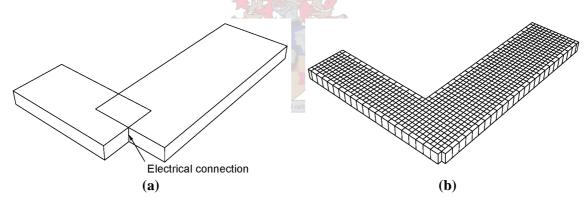

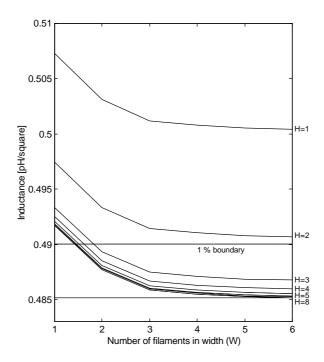

| Figure 3.5: FastHenry line segment shown with filaments and connection node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27   |

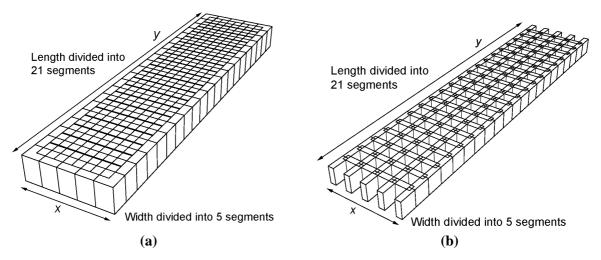

| Figure 3.6: Segmented line (a) as it really looks and (b) graphical representation with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| segment widths shrunk to one third of their actual values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 28   |