# Automated program generation

# Bridging the gap between model and implementation

Johannes A. Bezuidenhout

THESIS PRESENTED IN PARTIAL FULFILMENT

OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF SCIENCE

AT THE UNIVERSITY OF STELLENBOSCH.

Supervised by: Dr. Jaco Geldenhuys

# Declaration

Signature: Bezuichenhaut Date: 05/03/2007

# Abstract

The general goal of this thesis is the investigation of a technique that allows model checking to be directly integrated into the software development process, preserving the benefits of model checking while addressing some of its limitations. A technique was developed that allows a complete executable implementation to be generated from an enhanced model specification. This included the development of a program, the Generator, that completely automates the generation process. In addition, it is illustrated how structuring the specification as a transitions system formally separates the control flow from the details of manipulating data. This simplifies the verification process which is focused on checking control flow in detail. By combining this structuring approach with automated implementation generation we ensure that the verified system behaviour is preserved in the actual implementation. An additional benefit is that data manipulation, which is generally not suited to model checking, is restricted to separate, independent code fragments that can be verified using verification techniques for sequential programs. These data manipulation code segments can also be optimised for the implementation without affecting the verification of the control structure. This technique was used to develop a reactive system, an FTP server, and this experiment illustrated that efficient code can be automatically generated while preserving the benefits of model checking.

# **Opsomming**

Hierdie tesis ondersoek 'n tegniek wat modeltoetsing laat deel uitmaak van die sagtewareontwikkelingsproses, en sodoende betroubaarheid verbeter terwyl sekere tekorkominge van die tradisionele modeltoetsing proses aangespreek word. Die tegniek wat ontwikkel is maak dit moontlik om 'n volledige uitvoerbare implementasie vanaf 'n gespesialiseerde model spesifikasie te genereer. Om die implementasie-generasie stap ten volle te outomatiseer is 'n program, die GENERATOR, ontwikkel. Daarby word dit ook gewys hoe die kontrolevloei op 'n formele manier geskei kan word van data-manipulasie deur gebruik te maak van 'n staatoorgangsstelsel struktureringsbenadering. Dit vereenvoudig die verifikasie proses, wat fokus op kontrolevloei. Deur dié struktureringsbenadering te kombineer met outomatiese implementasie-generasie, word verseker dat die geverifieerde stelsel se gedrag behou word in die finale implementasie. 'n Bykomende voordeel is dat data-manipulasie, wat gewoonlik nie geskik is vir modeltoetsing nie, beperk word tot aparte, onafhanklike kode segmente wat geverifieer kan word deur gebruik te maak van verifikasie tegnieke vir sekwensiëele programme. Hierdie data-manipulasie kode segmente kan ook geoptimeer word vir die implementasie sonder om die verifikasie van die kontrole struktuur te beïnvloed. Hierdie tegniek word gebruik om 'n reaktiewe stelsel, 'n FTP bediener, te ontwikkel, en dié eksperiment wys dat doeltreffende kode outomaties gegenereer kan word terwyl die voordele van modeltoetsing behou word.

# Acknowledgements

I wish to express my sincere gratitude and appreciation to the following persons and institutions:

- My Heavenly Father.

- The Computer Science Department of the Stellenbosch University for their assistance.

- My promoter, Dr. Jaco Geldenhuys, for his guidance, encouragement, critical evaluation and assistance during this study.

- My parents, for their love, support and encouragement during all my years of studying.

- My wife, Mareli, for being her exceptional self, for her constant love and support, and all the cups of coffee.

# Contents

| A              | bstra | ıct    |                                        | iii          |

|----------------|-------|--------|----------------------------------------|--------------|

| O <sub>2</sub> | psom  | ıming  |                                        | iv           |

| A              | ckno  | wledge | ments                                  | $\mathbf{v}$ |

| 1              | Intr  | oducti | ion                                    | 1            |

| 2              | A S   | urvey  | of Software Verification               | 4            |

|                | 2.1   | Forma  | l Verification                         | 4            |

|                | 2.2   | Model  | Checking                               | 6            |

|                |       | 2.2.1  | Different Approaches to Model Checking | 7            |

|                |       | 2.2.2  | Temporal Logic                         | 8            |

|                |       | 2.2.3  | LTL Model Checking                     | 11           |

|                |       | 2.2.4  | The Spin Model Checker                 | 14           |

|                | 2.3   | Model  | s versus Implementations               | 17           |

|                |       | 2.3.1  | Benefits of Model Checking             | 17           |

|                |       | 2.3.2  | Limitations of Model Checking          | 18           |

|                |       | 2.3.3  | The Specification Gap                  | 20           |

|                | 2.4   | Implei | mentation Generation                   | 21           |

|   |     | 2.4.1          | A Promela-to-C Compiler                | 21         |

|---|-----|----------------|----------------------------------------|------------|

|   |     | 2.4.2          | Domain-Specific Languages              | 23         |

|   |     | 2.4.3          | A Transition System Approach           | 24         |

|   | 2.5 | Model          | Extraction                             | 25         |

|   |     | 2.5.1          | Manual Approach                        | 25         |

|   |     | 2.5.2          | Java PathFinder I                      | 26         |

|   |     | 2.5.3          | Bandera                                | 27         |

|   |     | 2.5.4          | FeaVer                                 | 28         |

|   | 2.6 | Progra         | am Model Checking                      | 29         |

|   |     | 2.6.1          | Specialised Implementation Languages   | 29         |

|   |     | 2.6.2          | VeriSoft                               | 30         |

|   |     | 2.6.3          | SLAM                                   | 31         |

|   |     | 2.6.4          | Java PathFinder II                     | 32         |

| 3 | Imp | olemen         | tation Generation                      | <b>3</b> 4 |

|   | 3.1 | Transl         | lating Promela to C . Prove of the ref | 36         |

|   |     | 3.1.1          | Metaterms                              | 36         |

|   |     | 3.1.2          | Inline Functions                       | 37         |

|   |     | 3.1.3          | Symbolic constants                     | 37         |

|   |     | 3.1.4          | Processes                              | 38         |

|   |     | 3.1.5          | Variables, Message Channels and Scope  | 44         |

|   |     |                |                                        |            |

|   |     | 3.1.6          | Basic Data Types                       | 46         |

|   |     | 3.1.6<br>3.1.7 | Basic Data Types                       | 46         |

|   |     |                | · ·                                    |            |

|   |                | 3.1.10                              | Repetition                                                                                                                | 52                               |

|---|----------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|   |                | 3.1.11                              | Predefined Constants, Variables and Functions                                                                             | 53                               |

|   |                | 3.1.12                              | Embedded C Code                                                                                                           | 54                               |

|   | 3.2            | Extend                              | ding Promela                                                                                                              | 55                               |

|   |                | 3.2.1                               | Embedded Code Fragments                                                                                                   | 55                               |

|   |                | 3.2.2                               | Additional Options                                                                                                        | 58                               |

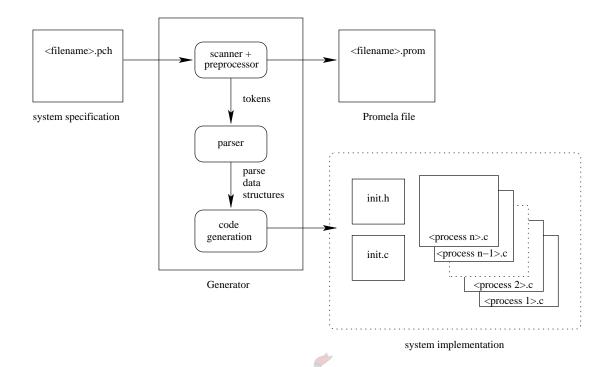

|   | 3.3            | The G                               | ENERATOR                                                                                                                  | 58                               |

|   |                | 3.3.1                               | Architecture                                                                                                              | 59                               |

|   |                | 3.3.2                               | Scanner                                                                                                                   | 60                               |

|   |                | 3.3.3                               | Parser                                                                                                                    | 60                               |

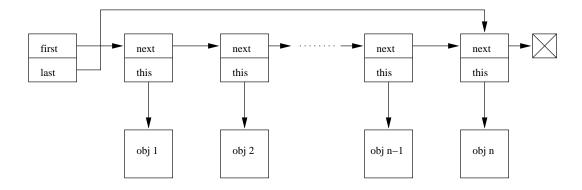

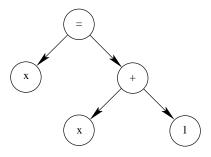

|   |                | 3.3.4                               | Data Structures                                                                                                           | 61                               |

|   |                | 3.3.5                               | Code Generation                                                                                                           | 63                               |

|   |                |                                     |                                                                                                                           |                                  |

| 4 | Cas            | e Stud                              | lies                                                                                                                      | 67                               |

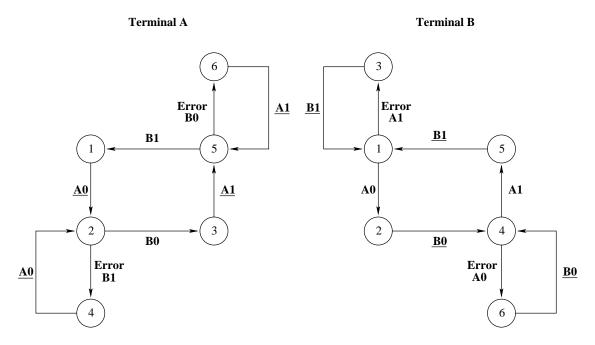

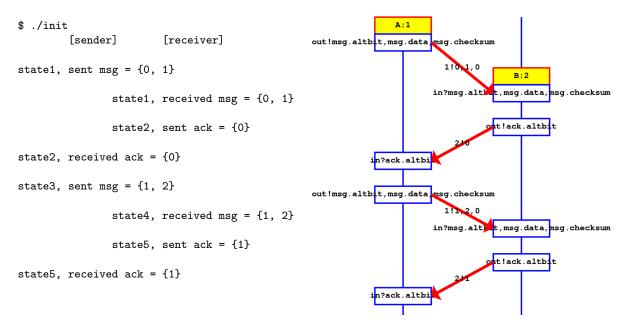

| 4 | <b>Cas</b> 4.1 |                                     | dies  Ilternating Bit Protocol                                                                                            | <b>67</b>                        |

| 4 |                |                                     |                                                                                                                           |                                  |

| 4 |                | The A                               | lternating Bit Protocol                                                                                                   | 67                               |

| 4 |                | The A 4.1.1                         | PROMELA Specification                                                                                                     | 67<br>68                         |

| 4 |                | The A 4.1.1 4.1.2 4.1.3             | PROMELA Specification                                                                                                     | 67<br>68<br>70                   |

| 4 | 4.1            | The A 4.1.1 4.1.2 4.1.3             | PROMELA Specification  Specifying an Implementation  Verification                                                         | 67<br>68<br>70<br>74             |

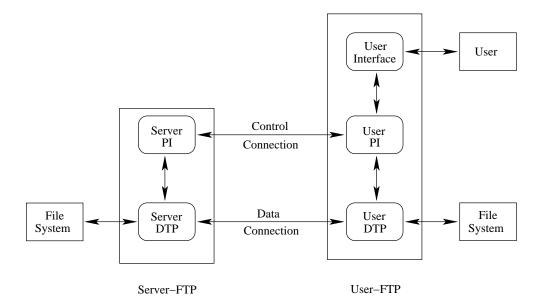

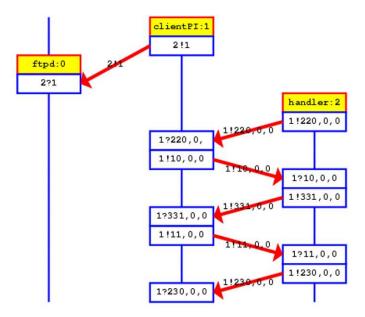

| 4 | 4.1            | The A 4.1.1 4.1.2 4.1.3 FTP S       | PROMELA Specification                                                                                                     | 67<br>68<br>70<br>74<br>76       |

| 4 | 4.1            | The A 4.1.1 4.1.2 4.1.3 FTP S 4.2.1 | Ilternating Bit Protocol  PROMELA Specification  Specifying an Implementation  Verification  Server  System Specification | 67<br>68<br>70<br>74<br>76<br>78 |

# Chapter 1

# Introduction

Formal methods aim to bring software engineering in line with the more traditional engineering disciplines. Because of the need to balance the issues of cost and reliability, the use of these methods are usually only justified when the cost of possible errors is very high, as is the case with applications involving safety and security. As formal methods evolve and mature, and growing computational power diminish previous practical limitations, some of the focus is shifting from achieving basic functionality to enhancing formal methods in terms of effectiveness and usability. One example of this is the relatively new trend of software model checking [54], where the focus has shifted from verifying hand-built models to applying model checking directly at the implementation level. One way to achieve this is to automatically generate an executable implementation from the verified specification, and this thesis investigates such an approach.

Model checking is an automated formal method for the verification of finite-state concurrent systems. Due to the nature of concurrent systems, normal development tools are insufficient in general. Just reasoning about the expected behaviour of concurrent systems without the use of automated tools is extremely hard, even impossible. This is because of the possibly infinite execution interleavings. An erroneous execution of a concurrent system depends on a specific combination of the execution paths of each of the processes in the system, which in turn depends on the timing of events. Since this exact execution path is only one of a possibly infinite number of execution paths of the system, testing techniques may not reveal such behaviour, and is therefore not a satisfactory method for guaranteeing correctness or reliability. Even if an erroneous execution were detected it would, in general, be impossible to reproduce, since even with the same input variables it is not possible to control the exact timing of all events. Model checking addresses these issues by allowing the verification of a

requirements property for all possible executions of a given system specification, in a formal and highly automated manner.

The traditional model checking approach is to manually construct an abstract model of the system, which is is then verified against its formal requirements specification. A model checker checks every possible execution of the model and verifies that none of the paths in the reachable state space violates the formal specification. If a violation is detected, a counterexample is generated in the form of an execution trace that leads to the violation. Models are described in a special modelling language which is usually specific to the model checker, and is also generally more restrictive than a general programming language, so as to facilitate analysis and verification.

The fact that the traditional model checking approach is based on a manually constructed model of the system is one of its biggest limitations — the keywords being model and manual. The problem is that there exists a discrepancy, or gap, between the specification that is verified (the model) and the specification that represents the actual implementation (the implementation source code). This is what we refer to as the specification gap, and it is the source of two major problems. Firstly, a verified model does not guarantee that the implementation satisfies the requirements if informal implementation techniques are used. Even with the use of formal methods, if there are any manual steps involved in the translation between model and implementation, the possibility always exists that errors are introduced that will invalidate the verification. Secondly, manually constructing a model that is both accurate as well as tractable is a non-trivial exercise, introducing issues of timing and relevance. If the effort of constructing the abstract model is not significantly less than the actual development effort itself, the verification effort will either hold up the development process, or quickly start to lag behind the current version of the system and eventually become incomplete, inaccurate, or even completely irrelevant. These are some of the main reasons that led to research in the formal methods community to be directed at development of techniques for applying model checking directly at the implementation level, rather than on system model specifications.

It is currently possible to distinguish between three different general approaches in software model checking, based on how the program source is interpreted: model extraction, program generation and model checking programming languages directly. Model extraction refers to automatically generating abstract models from existing implementations, program generation refers to automatically generating correct implementation skeletons from verified models, and directly model checking programs means that entire implementations are used as input to the model checker.

3

This thesis investigates a technique where a full implementation is generated from a verified model. To formalise the translation step we propose using the same structure (a state transition system) for the model and the implementation. A transition system approach allows us to separate the flow of control from data manipulation. This benefits verification as well as testing. Model checking focuses on verifying the correct flow of control, and testing now has only to be applied to clearly designated pieces of code that perform data manipulation. These code fragments can be tested independently and in isolation from the environment of the system. This structuring approach has been shown to be effective in [15] where implementations are derived from verified formal specifications. Whereas the authors of [15] manually derive the implementations, we will automatically generate a full implementation from a verified model. The design and implementation of a generator tool that can parse specially enhanced models and generate full implementations forms the core of this thesis.

It was decided to use the SPIN verification system as a framework for our tool since it is mature, well-known, and freely available. The input language for SPIN, PROMELA, is also one of the more programming-language-like modelling languages. ANSI C was chosen as implementation language, for two reasons. Firstly, it is a popular programming language and one of our aims is to make model checking more attractive to the general programmer. Secondly, it integrates well into the SPIN system — PROMELA resembles C and SPIN itself is implemented in C. Since concurrent reactive systems [49], such as communication protocols, are well suited to the transition system approach, we restrict our focus to this type of application.

The thesis is structured as follows. Chapter 2 is a survey of the relevant background literature and covers model checking, the SPIN verification system, and software model checking. Chapter 3 explores the approach taken in this investigation and documents the design and implementation of the GENERATOR, the program that automates the implementation generation step. Chapter 4 contains case studies that demonstrate the application of the proposed technique and the use of the GENERATOR. Conclusions are presented in Chapter 5.

# Chapter 2

# A Survey of Software Verification

This chapter provides a survey of software verification in as much as it pertains to the use of model checking in the software development process. This will provide the necessary background for the tool we introduce in the next chapter. Much of the information here comes from the summary articles of Clarke [19, 23], Holzmann [61], and Katoen [80].

The goal of software verification is to ensure that a system conforms to its requirements specification, where it is assumed that the requirements correctly represent what is really expected from the application. Verification techniques can be classified as either static or dynamic verification. Dynamic verification is performed by executing a system implementation, and includes testing and simulation, or experimentation. Static verification, on the other hand, is a process of checking the description of a system against certain requirements by way of physical inspection. One example of static verification is formal verification.

### 2.1 Formal Verification

As Dijkstra pointed out, testing can only show the presence of errors, never their absence [31]. Formal verification on the other hand can prove, or disprove the correctness of a system description with respect to certain requirements. The basic idea behind this approach is as follows. A formal *model* is constructed which represents the possible behaviour of the system, and the correctness requirements for the system are written in a formal requirements specification that represents the desired behaviour of the system. Using formal methods it is then verified whether the possible behaviour corresponds to the desired behaviour.

Formal verification can be applied to sequential programs in the following fashion. First the desired behaviour is formalised using pre- and postconditions formulated in predicate logic. A precondition describes the set of initial states, and a postcondition describes the set of desired final states. Once this is done, the sequential program is coded in some abstract pseudo-code language, such as Dijkstra's guarded command language [32], and it is proven in a stepwise manner that the abstract system description satisfies the specification. The actual proof is constructed from a set of proof rules, which generally corresponds to program constructs. These rules are written in the form:

$\{\phi\}S\{\psi\}$

where  $\phi$  is a precondition, S is a program statement, and  $\psi$  is a postcondition. This is known as a *Hoare triple*, due to the work of Tony Hoare [57]. This formula can be read as follows: Whenever  $\phi$  holds in the state before the execution of S, then  $\psi$  will hold afterwards. The formula is partially correct if any terminating computations of S that starts in a state satisfying  $\phi$ , terminates in a state satisfying  $\psi$ . It is totally correct if any computation of S that starts in a state satisfying  $\phi$ , terminates and finishes in a state satisfying  $\psi$ .

Deterministic programs always provide the same results when provided a given input, and it naturally follows that this type of program lends itself more freely to the approach just described. The introduction of parallelism, however, also leads to the introduction of non-determinism. Concurrent processes can potentially interact at any point during their execution, which means that the results of a given execution may depend strongly on the order of execution. Also, very importantly, the execution of parallel systems does not necessarily terminate; this is the case for most reactive systems. Thinking of a program as a function that produces a certain desired output when provided certain allowed input is no longer appropriate when reasoning about concurrent systems in general. Instead of reasoning only in terms of the state of a system before and after an execution, we need to reason about the different executions of the system by making statements about the executions themselves.

Although various efforts have been made to generalise the classical formal verification approach as described above, it just does not scale well for realistic concurrent systems. The proof rules are very complex and the proof systems quickly become very large. This makes the process lengthy, tedious and easily susceptible to errors. *Proof assistants* and *theorem provers* are both tools that address some of these issues, but there is a formal method generally more suited to the verification of concurrent systems, namely *model checking*.

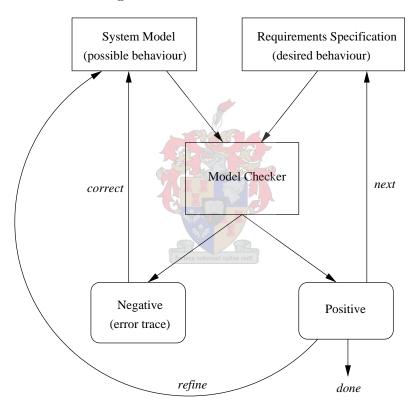

# 2.2 Model Checking

Model checking is an automated, model-based verification technique for finite concurrent systems. Given a description of a system in the form of a finite-state model (the possible behaviour) and a description of the requirements specification (the desired behaviour) for that system, a model checker automatically verifies whether the modelled system satisfies the requirements. If the model satisfies the requirements, the model checker returns a positive result, and negative otherwise. In the case of a negative result, the model checker can (in most cases) provide a counterexample that indicates exactly how the requirements are violated. This is usually in the form of an execution trace of the system model. This verification methodology is illustrated in Figure 1.

Figure 1: Model Checking Methodology.

The system description or model is an abstract representation of the system, and should only represent the behaviour of the system necessary to verify the specific requirements. The reason for this is that a model checker can in general not efficiently handle the complexity of a complete system implementation. Moreover, excluding irrelevant details may make the model more comprehensible for users of the verification, and therefore produce more useful counterexamples.

There are two basic approaches to applying this verification methodology to the software development process. The first, and also most ideal, approach is to develop a correct, i.e., verified, system description or model of the system, and then derive the actual implementation from the verified model. The second approach is to derive a system model from a preexisting implementation. The reason the first approach is considered ideal is that the earlier problems are identified in the development of an application, the less costly they are to rectify. However, the second approach is unfortunately more representative of real-world development practices. This is also the only option if verification has to be applied to a previously developed software application.

Regardless of whether the implementation is derived from the model, or vice versa, the verification results obtained for the model is ultimately translated to the system implementation. If the verification is successful, the model can be further refined and the verification repeated, until the model is considered sufficiently representative of the system. It is also possible that the requirements were specified incorrectly, in which case the result of the verification is called a *false negative*. If the model was derived from an actual implementation, the counterexample produced can be checked against the implementation to determine its validity. If the behaviour can be reproduced in the implementation, it represents a true error, and the implementation can be corrected. If the behaviour is not reproducible, it indicates that the system model is not sufficiently accurate, and can be used to refine the model.

The basic operation of a typical model checker can be described as an exhaustive state space search of the system model. This means that the model checker checks that for each state of the model, the desired behaviour is satisfied. In its most basic form this is known as reachability analysis. With reachability analysis it is possible to prove invariant properties, which are properties that should hold in every state of a computation, as well as freedom from deadlock. To check for deadlock it is sufficient to determine whether there exists a reachable state in the model without any successors. Simple reachability analysis is, however, insufficient for reasoning about the behaviour of the system over time, such as claims concerning the relative order of events.

## 2.2.1 Different Approaches to Model Checking

We can distinguish between two main approaches to model checking, based on the way the desired behaviour, or requirements specification, is represented. The first is a *logic-based* or *heterogeneous* approach, and the second a *behaviour-based* or *homogeneous* approach.

In the logic-based approach, the desired behaviour is captured as a set of properties in some appropriate logic. The system description, or possible behaviour, is usually modelled as some form of finite-state automaton. The system is considered correct with respect to the requirements if it satisfies the properties for a given set of initial states. Formally, this can be stated as

$$\mathcal{M}, S \models \phi$$

where  $\mathcal{M}$  is the system, S is the set of initial states, and  $\phi$  is a logic formula representing a requirements property. In formal logic,  $\mathcal{M}, S$  is known as model for property  $\phi$ , which is where the term model checking comes from. (We also refer to  $\mathcal{M}$  as a model of the implementation, which may be slightly confusing, but generally does not lead to any problems.) This approach originates from the independent work of Clarke and Emerson [20, 21], and Queille and Sifakis [101]. Both these approaches are based on  $temporal\ logic$ , which was first introduced to Computer Science by Pnueli [98].

In the behaviour-based approach, both the desired and possible behaviours are specified using the same formalism, and equivalence relations (or pre-orders) are then used as a correctness criterion. Equivalence relations capture the notion "has exactly the same behaviour as", whereas pre-order relations represent the notion "has at least the same behaviour as". A system is then considered correct if the desired and the possible behaviour are equivalent (or ordered) with respect to the equivalence (or pre-order) attribute under investigation. This approach is most commonly associated with process algebras, pioneered by Milner [87, 88] and Hoare [58, 59].

From here on we will only be focusing on the logic-based model checking approach, with the requirements specified in temporal logic. In the literature this is sometimes referred to as temporal logic model checking.

#### 2.2.2 Temporal Logic

As already mentioned, predicate or propositional logic is not adequate for reasoning about concurrent systems. We therefore turn to temporal logic, which allows us to express properties involving the relative ordering of events, without having to explicitly mention the time at which the events occur. The concept of temporal logic was already introduced in the 1960s by Arthur Prior, in the field of Philosophy, but its introduction to Computer Science for the purpose of specification and verification is due to Pnueli [98].

For example, if we were reasoning about the behaviour of a railway crossing controller, we would like to make statements like

A: When a train is in the crossing, the gate will always be down.

and

B: If the gate is down, it will eventually again be up.

Temporal logic extends propositional logic by introducing operators that express properties of system states over time. Examples of such operators are  $\mathbf{U}$  (until),  $\mathbf{G}$  (globally, or always), and  $\mathbf{F}$  (future, or eventually).  $\phi$   $\mathbf{U}$   $\psi$  specifies that property  $\phi$  holds in the current state and in all subsequent states until a state is reached where  $\psi$  holds,  $\mathbf{G}$   $\phi$  specifies that  $\phi$  holds in the current state and all subsequent states (in other words, it will always hold), and  $\mathbf{F}$   $\phi$  specifies that  $\phi$  holds in the current state or will hold in some future state. Using these operators we can formally define our statements as follows. We first define the atomic or primitive propositions:

$p \equiv$  "a train is in the crossing"

$g \equiv$  "the gate is down"

The first statement can then be expressed in temporal logic as

$$\mathbf{G}\ (p\Rightarrow g)$$

which reads: "always, if p then g", or by expanding the propositions: "it is always so that if a train is in the crossing, the gate is down". The second statement is a bit more tricky, and can be expressed as

$$\mathbf{G}\ (g\Rightarrow\mathbf{F}\ (\neg g))$$

where  $\neg g$  indicates the negative form of g ("the gate is up"). This reads: "always, if g then eventually  $\neg g$ ", or "it is always so that if the gate is down now, then in some future state the gate is up again".

Temporal logics come in two varieties:

1. Linear time temporal logic allows reasoning about an individual system execution as a linear sequence of events. The qualitative notion of time is linear, meaning that at each

moment of time there is only one possible successor state, and thus only one possible future. The best-known example of this kind is *propositional linear time logic*, or LTL, introduced by Pnueli [98].

2. Branching time temporal logic introduces the idea that at each moment there may be several different futures. In other words, for every state of the model there possibly exists multiple successor states. A statement in branching time temporal logic reasons about a tree of states, rather than a sequence, with each path in the tree representing a single possible computation. There exists various types of branching time temporal logic that differ in expressiveness. The best known example is computation tree logic, or CTL, introduced by Clarke and Emerson [20].

Although it may appear from the above description that linear time temporal logics are not suited for reasoning about concurrent systems, this is not so. For a system to satisfy a linear time property  $\phi$ , all the executions of the system must satisfy the property.

These two varieties of temporal logic has led to two different directions of research in model checking. Both these directions have led to unique algorithms and implementations, and both have their own strengths and weaknesses. There are various verification tools based on each of these two approaches, some purely for research, but others that have been used to verify production software. Two examples of such tools are the SPIN [61] model checker for LTL, and the SMV [85] model checker for CTL.

For this thesis, it was decided to implement our technique within the SPIN verification system. There are several reasons for this decision, which will be pointed out later. At this point we can point out that SPIN is one of the most mature model checking tools. This claim is supported by the fact that SPIN has been successfully used for the verification of substantial and diverse applications [39, 52, 68, 74, 79, 102], as well as the SPIN workshop held annually since 1995. Moreover, the current and up-to-date SPIN source code is available freely online (http://spinroot.com/), and is well documented.

SPIN and SMV are only two examples of formal verification tools. Yahoda (http://anna.fi.muni.cz/yahoda/), an online database of verification tools, currently lists 43 model checking tools.

### 2.2.3 LTL Model Checking

The basic model checking problem is to verify that a formally defined system satisfies a formally defined requirements specification. The general approach for model checking LTL that we describe below is known as *automata-theoretic* model checking, and was first proposed by Vardi and Wolper [107, 113].

A labelled finite state automaton, or LFSA, is a tuple  $(\Sigma, S, S^0, \rho, F, l)$ , where:

- $\Sigma$  is a non-empty set of symbols,

- $\bullet$  S is a finite, non-empty set of states,

- $S^0 \subseteq S$  is a non-empty set of initial states,

- $\rho: S \to 2^S$  is a transition function,

- $F \subseteq S$  is a set of accepting states, and

- $l: S \to \Sigma$  is a labelling function for states.

We denote the set of finite sequences over  $\Sigma$  as  $\Sigma^*$ , and the set of infinite sequences as  $\Sigma^{\omega}$ .

A run,  $\sigma$ , is a finite or infinite sequence of states, starting from an initial state such that each state in the sequence can be reached via a transition from its predecessor state. A run is accepting if it ends in an accepting state. A finite word  $w = a_0 a_1 \dots a_n$  is accepted by LFSA A if and only if there exists a finite run  $\sigma = s_0 s_1 \dots s_n$  such that  $l(s_i) = a_i$  for  $0 \le i \le n$  and  $s_n \in F$ . The language accepted by A, denoted  $\mathcal{L}(A)$ , is the set of finite words accepted by A:

$$\mathcal{L}(A) = \{ w \in \Sigma^* \mid w \text{ is accepted by } A \}.$$

Since we are interested in proving properties that refer to infinite behaviour, we need to define how infinite runs are accepted. This is called  $B\ddot{u}chi$ -acceptance, and automata with this alternative definition of accepting runs are called  $B\ddot{u}chi$  or  $\omega$ -automata. A labelled  $B\ddot{u}chi$  automaton, or LBA, can then be defined as an LFSA that accepts infinite words. An infinite word  $w = a_0 a_1 a_2 \dots$  is  $B\ddot{u}chi$ -accepted by LBA A if and only if there exists an infinite run  $\sigma = s_0 s_1 s_2 \dots$  such that  $l(s_i) = a_i$  for  $i \geq 0$  and for each i there exists  $j \geq i$  such that  $s_j \in F$ . The language of an LBA A, denoted  $\mathcal{L}_{\omega}(A)$ , is then defined as the set of infinite words accepted by A:

$$\mathcal{L}_{\omega}(A) = \{ w \in \Sigma^{\omega} \mid w \text{ is accepted by } A \}.$$

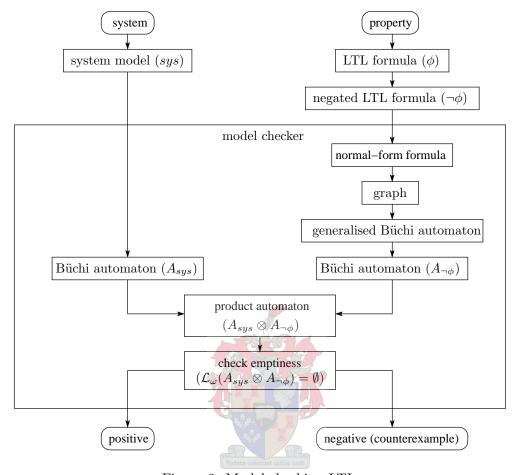

With this background we can now describe the basic scheme for LTL model checking. An overview of this process is shown in Figure 2.

Figure 2: Model checking LTL.

The very first step is of course to formally define the system behaviour as well as the desired behaviour. The language used to model the system is specific to the model checker implementation, which means that the translation of the model to automata form is also model checker dependent. The desired behaviour is formalised as a requirements specification, with the properties specified as LTL formulas.

In the next step, the system model and requirement specification are translated to Büchi automata  $A_{sys}$  and  $A_{\phi}$ , respectively. Vardi and Wolper showed that all LTL formulas can be translated to Büchi automata [108, 113], but most practical implementations are based on the more efficient algorithm in [38]. Thus, the language of the LBA  $A_{sys}$  describes the possible behaviour of the system model, and the language of the LBA  $A_{\phi}$  describes the desired behaviour. We need to check that:

$$\mathcal{L}_{\omega}(A_{sys}) \subseteq \mathcal{L}_{\omega}(A_{\phi})$$

in which case the system satisfies  $\phi$ . Unfortunately, deciding language inclusion for Büchi automata is PSPACE-complete. This means that, according to our current knowledge, the problem requires a running that is at least exponential in the size of the two automata. Fortunately there is an alternative approach we can take. Computing whether the desired behaviour includes the possible behaviour, is equivalent to computing whether the undesired behaviour does not include any possible behaviour. This amounts to checking whether the runs accepted by  $A_{sys}$  and  $\overline{A_{\phi}}$  are disjoint, or formally:

$$\mathcal{L}_{\omega}(A_{sys}) \subseteq \mathcal{L}_{\omega}(A_{\phi}) \Leftrightarrow (\mathcal{L}_{\omega}(A_{sys}) \cap \mathcal{L}_{\omega}(\overline{A_{\phi}}) = \emptyset)$$

where  $\overline{A}$  is the complement of A, and accepts the language  $\Sigma^{\omega} \setminus \mathcal{L}_{\omega}(A)$ . Complementation of Büchi automata is also PSPACE-complete, but again there is a workaround. The complement automaton of  $A_{\phi}$  is equal to the automaton for the negation of  $\phi$ :

$$\mathcal{L}_{\omega}(\overline{A_{\phi}}) = \mathcal{L}_{\omega}(A_{\neg \phi})$$

and we can therefore implement the model checking process for the negation of the formula, as Figure 2 illustrates. If the LTL formula  $\phi$  represents a desired property, its negated form  $\neg \phi$  represents an undesired property. The added negation does not significantly increase the complexity of the transformation. The Büchi automaton  $A_{\neg \phi}$  is constructed by first translating the formula to normal form, then to a graph form, and then to a generalised Büchi automaton. (The details of these intermediate forms fall outside the scope of this thesis). The automaton represents all undesired behaviour. Since the size of the automaton can be exponential on the length of the formula, the automaton for the negated formula can possibly be larger than that for the original formula. The product of the automata for the system and the negated property  $(A_{sys} \otimes A_{\neg \phi})$  represents all possible computations of the system that violate  $\phi$ . Verifying whether the system model sys satisfies the property  $\phi$  then boils down to checking the emptiness of the language accepted by the resulting automaton, which can be formally stated as the emptiness problem:

$$\mathcal{L}(A_{sys} \otimes A_{\neg \phi}) = \emptyset.$$

The language of the product automaton is empty if it does not accept any infinite words. If this is true, the system model does not contain any behaviour that violates property  $\phi$ . If the language is not empty, it consists of the set of Büchi-acceptance runs that correspond to the executions that violate  $\phi$ , and can then be used to produce counterexamples.

One of the advantages of this approach is that it allows for on-the-fly model checking. It is possible to check for violating accepting runs during construction of the product automaton  $(A_{sys} \otimes A_{\neg \phi})$ , and once a violation is detected, the model checker can immediately report it and abandon the construction. If the system satisfies the requirements, the complete product automaton has to be constructed. Fortunately, approaches such as abstraction techniques [23, 27], symmetry methods [22, 28, 34, 77], and partial order reduction [42, 69, 70, 95, 106] can also be applied to limit the size of the product automaton.

Examples of techniques that reduce the memory requirements of the model checker, as listed by Geldenhuys in [37], are state compaction [36] and byte masking, run-length encoding and Huffman encoding [67], closed (rehashing) hash tables, open (chaining) hash tables [41], bit-state hashing [60], hash compaction [103, 112], recursive indexing [62, 109], minimising automata-based techniques [71], sharing trees (or GETSs) [46], and difference compression [94].

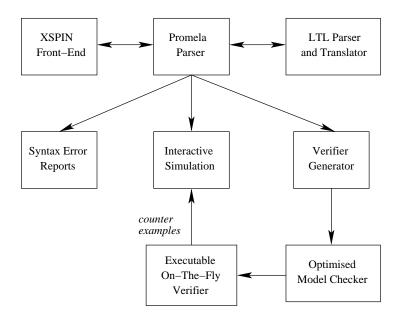

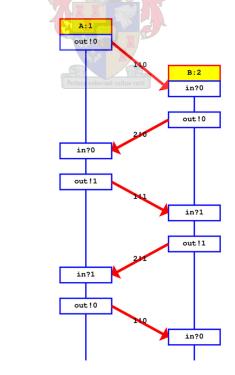

## 2.2.4 The Spin Model Checker

SPIN is an efficient verification system that supports the design and verification of asynchronous systems [61, 66]. Besides implementing LTL model checking, SPIN also provides for the simulation of the system model specification. A graphical overview of the structure of the system is given in Figure 3. SPIN is implemented as a command-line program, but a graphical front-end, XSPIN, is also provided with the system. The direct command-line approach allows more flexibility and has the possibility of delivering a more specialised verification in the hands of an experienced user, whereas the graphical interface provides a more user-friendly approach by automatically generating many of the required options for the user, and providing menu options for the rest. XSPIN also provides a graphical display of the system execution as a message sequence chart, which is often more helpful than the textual output provided by the command-line.

The system model specifications accepted by Spin are written in the language Promela, which is an acronym for Process Meta Language. Promela is described in detail in the next chapter, so only a basic introduction is given here.

A Promela model specifies an asynchronous system of concurrently executing processes, that can communicate via message channels and shared variables. The language is heavily

Figure 3: The structure of Spin simulation and verification.

influenced by the guarded command language of Dijkstra [32]. The syntax of expressions, declarations and assignments in Prometa resemble that of the C programming language.

Typically, the first step is to use SPIN to perform a random simulation of the system. This is an easy way to check that the model at least appears to behave as expected. The next step is to actually prove that it is behaving correctly in terms of the requirements. This is done by expressing the formal requirements as LTL formulas and using SPIN to model check the system specification against the correctness requirements.

SPIN generates an optimised on-the-fly verifier as an ANSI C program source based on the system and requirement specifications. This program performs the actual verification and implements the LTL model checking approach described in the previous Section, albeit with many more options and features. The program is first compiled and then executed. During all three of these steps, generation, compilation and execution of the C program, it is possible to specify additional options to fine tune the verification. For example, it is possible to add options when compiling the program to specify which reduction algorithms are to be used. When executed, the verifier returns with a positive result if there are no property violations, and provides a counterexample in the case of a violation. The counterexample is in the form of an execution trail of the model, and the simulation functionality of Spin can be used to perform an interactive playback of the trail to examine the cause of the violation.

By default, SPIN checks for the absence of deadlock, unspecified reception of messages and

unexecutable code. Additionally it is also possible to verify the model against specific correctness requirements by using inline assertions, state labels, LTL properties or never-claims. The Promela assert statement works exactly like its programming language counterpart, and provides an easy way to check simple safety properties. The statement takes any valid PROMELA expression as argument and traps violations of the property specified by the expression. This works in simulation as well as verification mode, but the simulation of course only checks the assertion for one random execution, whereas the verification checks it for all possible executions of the system. Another way to make specific assertions about the model behaviour is through the use of state labels. End-state labels are used to indicate valid end states, that should not be seen by SPIN as constituting a deadlock. In the same way it is also possible to define progress-state labels. These are used to specify liveness properties, and marks a state that must be visited infinitely often in any infinite system execution. Another label for specifying liveness properties is the acceptance-state label. These are used to formalise Büchi acceptance conditions, but since they are in most cases automatically generated from LTL formulas, it is rarely necessary to manually add them. To verify anything more than basic correctness properties, it is necessary to specify the desired behaviour as a never-claim or LTL formula.

A PROMELA never-claim is a formalism that describes the desired behaviour of the system, in the same way that the model specifies the possible behaviour. Never-claims are more expressive that LTL, and any LTL formula can be translated to a corresponding never-claim. Although never-claims are more expressive, LTL formulas are in general easier to formulate. Recent versions of Spin therefore allow requirements to be specified as LTL formulas, and automatically derive the corresponding never-claims. This process uses the algorithm from [38] with some optimisations from [35]. Spin does not allow the use of the  $\mathbf{X}$  (next) temporal operator, so the logic accepted by Spin is referred to as LTL- $\mathbf{X}$ . One other subtle difference is that Spin never-claims also accept finite runs. This is achieved by applying a stutter extension to a finite run to make sure it is Büchi-accepted. A stutter extension of a finite run  $\sigma$  of finite state automaton A is the infinite run that is derived from  $\sigma$  by appending an infinite number of copies of the last state.

This was just a general introduction to the SPIN system. For a complete description of the tool the reader is referred to the SPIN reference book [65]. The SPIN website http://spinroot.com/ is another source, and contains tool documentation, tutorials, sample applications, the actual program source, as well as information about SPIN workshops.

# 2.3 Models versus Implementations

It is only recently that the development of efficient algorithms and ever growing computing power allowed model checking to become a practically viable option for formal verification method. Active research in the field has produced steady improvement in the efficiency and usability of the technology, and computing power per unit cost has continued to evolve according to *Moore's Law* [89]. This has led to model checking being successfully applied to the development of reliable software as well as debugging of existing systems. In recent years these advances have led to a new direction in model checking research, where the attention has shifted from the development of the basic capability to perform logic model checking at the design level on abstract system models, to the development of methods that allow the application of logic model checking directly at the implementation level. Before discussing these methods, let us first take a look at the benefits and limitations of the basic, or traditional, model checking approach that led to this development. In describing model checking we have already touched on some of these.

## 2.3.1 Benefits of Model Checking

Model checking is a formal method based on a sound mathematical foundation. This makes it appealing from a Computer Science perspective, since we can scientifically reason about it. Software engineering on the other hand, as an engineering discipline, focuses on the application of the technique to software development.

Model checking is **highly automated**. Given a finite-state system description and the LTL formulation of the correctness requirements, a model checker can automatically check whether the property holds. Other techniques (such as automated theorem proving) requires significantly more expertise and effort to achieve the same result.

A verification run returns a **definite 'yes' or 'no' answer** (if the question is at all decidable). In the case of a property violation, a **counterexample** is produced to show the exact behaviour that causes the violation.

Erroneous behaviour is **reproducible**. Concurrent behaviour of reactive systems is highly dependent on intricate event timings, which makes it difficult to reproduce errors with testing. Model checking systematically examines all possible behaviours, so that, if a property violation is matched once, any future verifications will match the exact same violation (for the same model and property). Also, the counterexample can then be used to trace the precise steps

in the model execution that led up to the error.

Model checking supports **partial verification**, which means that it can be applied to a partial design. Only the behaviour relevant to the requirement has to be modelled, and it is possible to tailor the specification to the specific verification. This can result in improved efficiency.

Model checking is a **general approach** not fixed to any one specific application area. This includes hardware as well as software, high level designs as well as low level embedded systems, and even business models [78].

When applied in the context of formal software development, model checking does not necessarily cost more than testing and simulation, and has been shown to be more effective in its intended application area. In some cases the use of model checking has even been shown to reduce development time.

### 2.3.2 Limitations of Model Checking

Model checking is subject to **decidability issues**. Generally speaking, even simple properties can be formally undecidable. Model checking is based on the exploration of the system state space, which means that its application is restricted to systems with behaviour that can be modelled as **finite-state automata**. Event-driven, distributed, and concurrent systems, which we are focusing on, all fall in this category.

Given a finite-state model, another fundamental issue for model checking is the **state space explosion problem**. For a model checker to effectively traverse the state space, the states has to fit in primary memory. However, the size of a system's state space is in the worst case proportional to the Cartesian product of the state spaces of its components. The state representation can be swapped in and out of primary memory as needed, but this is inefficient. The verification is therefore limited by the physical constraints of memory and time. It is possible to only check a partial state space, but then it cannot be shown that the property being checked holds for the complete system behaviour. Any errors found in the explored state space are, however, valid errors. Effective algorithms and techniques, as well as the constant increase in available computing resources has ameliorated the impact of this problem.

Due to the nature of model checking it is more suited to the verification of flow of control than data manipulation in a system. Data intensive operations usually do not carry a lot of useful state information when compared to the significant increase in state space caused by

the large data ranges.

A model checker implementation, as a software application, might itself be unreliable. However, since model checking is based on standard and well known logically sound algorithms, confidence is achieved in model checker implementations through thorough verification and intensive use. This is similar to the situation for compilers. In some cases theorem provers have been used to verify components of the model checker implementation.

In contrast to theorem proving, it is in general not possible to check generalisations with model checking. Properties verified for a fixed number of variations does not scale to the general case. Using model checking to prove a property for specific cases, it could, however, be possible to use an automated theorem prover to generate the proof for the general case.

This brings us to the issue that we aim to address in this thesis, the model construction problem. The problem is twofold, in that the process of constructing a system model can be both error-prone and time consuming. (This argument is of course equally valid for the process of deriving the implementation from the model.) The problem stems from the fact that there exists a discrepancy, or gap, between the artifacts representing the actual system implementation and those accepted by most current verification tools. This is due to the difference in semantics, as well as syntax, of the specification formats used for implementation and modelling. Software is developed using general-purpose programming languages, such as C and Java, while most verification tools accept specification languages designed to be more convenient for formal methods through simpler, more tailored semantics and syntax. Typical examples of formal specification languages are purely logic-based languages used in theorem provers [45, 92, 26], and guarded command languages used in model checkers [86, 81]. This is the so called specification gap.

Similar to the system model, the user also has to formally specify the requirements. Correctly specifying complex properties in temporal logic also requires expertise. Developing easier ways for normal developers with minimal model checking experience to specify these properties is an active area of research, but is considered outside the scope of this thesis. Two attempts worth mentioning is the Timeline Editor of the FeaVer system [74], and the Bandera Specification Language (BSL) [24, 50]. Another issue is the fact that the system is only verified for the stated requirements, and no guarantees can be made about the correctness or completeness of the requirements specification. This is true for any verification technique, though.

## 2.3.3 The Specification Gap

The first issue raised by the specification gap is the possibility of discrepancies between the behaviour being verified and that of the actual implementation. Since a model of the system is model checked, and not the actual system implementation itself, we are not guaranteed that properties verified to hold for the model also hold for the implementation. Manually constructing a verification model that is true to the actual system, as well as tractable, is a task that for non-trivial systems require skill and expertise not normally associated with software development. Wolper stated that "Manual verification is at least as likely to be wrong as the program itself" [111], and although the actual verification is formal and automated, the possibility of human-error in the translation between model and implementation could still invalidate the verification.

The second issue is that constructing the system model is time consuming, which can be prohibitive when developing non-trivial applications. Time spent on development of course directly translates to cost in the industry. As already mentioned, this process also requires specialised expertise, which again could increase production costs if these skills are not already available in-house. It has, however, been shown that the actual cost of applying model checking is in many cases not that high when compared to other verification methods, and is usually outweighed by the benefits it offers. Unfortunately this remains a perceived issue, which because of the pressure to reduce design and development time ("time to market") is hindering the adoption of model checking in the industry. This is sometimes referred to as the technology transfer problem [10, 48]. Perhaps more relevant are the issues of timing and relevance. In a typical software development environment where teams of developers work on a project, the system design or implementation can change rapidly, even daily. Constructing the model, however, can take a lot longer, up to weeks or even months for a sizable system. This means that either the development is held up waiting for the verification results, or that the results will most likely be irrelevant when they become available since they are based on a previous version of the system.

The purpose of formal methods is to enable the development of correct software applications (i.e., that satisfy their specification), but powerful verification techniques are useless if not adopted by the developers of these applications. Software developers in general prefer to use general program languages such as C, C++ and Java, and are reluctant to adopt development techniques that require use of specialised languages that are also generally less expressive. It is also true that many project managers do not recognise that time spent on model checking is beneficial in the long run, and tend to view it as time not spent on actual system

implementation.

This has led to research being directed at making model checking a more attractive option for software development. The idea is that by addressing the *specification gap* and the issues associated with it, model checking can be made easier to use and more efficient at ensuring reliability of the actual system implementation. Current research in this field can be grouped into three directions: In the first group an implementation is generated from a verified specification or model, in the second a verification model is extracted from existent program source code, and in the third the program source is model checked directly. We discuss the techniques, as associated with each group, in more detail in the following Sections, along with some of the more prominent research projects in each group.

# 2.4 Implementation Generation

Of the three approaches, the first is the closest to the method traditionally prescribed for formal software development. In accordance with traditional software engineering methodology, the system is first specified in terms of its design and requirements, the design verified against the requirements, and the verified design then used to implement the actual system. Although it has been stated many times that this last step of deriving the implementation from the model could potentially be automated, it has largely remained a manual process. Logical refinement techniques during the extraction process can help to preserve the essential correctness properties, but as long as the process is not automated, the specification gap remains a problem. Automating this step addresses both the issues of reliability and cost; one such an attempt is the system by Löffler and Serhrouchni for creating C code implementations from Promela models.

#### 2.4.1 A Promela-to-C Compiler

The approach taken by Löffler and Serhrouchni extends SPIN to allow for the generation of an implementation from a Promela specification [82, 84]. As explained in subsection 2.2.4, SPIN generates a verifier in ANSI C from the Promela specification. The generated source code for the verifier already contains code for all the transitions and actions; this is isolated and extended with additional code to produce an implementation. This discussion assumes some knowledge of SPIN and Promela. For any unfamiliar concepts the reader is referred to the next chapter which contains a detailed discussion of the Promela language.

The additional code implements a pseudo runtime environment that replaces the SPIN code that drives the state machine. It consists of a scheduler, as well as some code that implements timer and external communication functionality. This additional code is then compiled together with the code implementing the state machine to produce a singe UNIX program. When this program is compiled and executed, the built-in runtime environment schedules the execution of the Prometa processes and handles all communication.

Non-determinism is handled by randomly choosing one of the executable branches for the first selection, and thereafter selecting the first executable branch. If a process has no executable next branch, it blocks, and if all the processes are blocked the actual UNIX program is also blocked until an external event occurs or a timer expires. Since version 2.0, Spin allows the system to switch to another process if the current process blocks within an atomic sequence (a code sequence that is executed as an indivisible unit). The generated scheduler does, however, not have as much control over the system as Spin, and consequently does not know if a process waiting for an external event will deadlock or not. For this reason the implementation differs from the model behaviour in that a process blocking in an atomic sequence will stay blocked until it unblocks itself. This example shows how it is possible to interpret the semantics of PROMELA differently even when using the same system specification representation.

Both the timer mechanism and external communication are implemented using message channels. For the timer mechanism three channels are provided: set\_timer is used to set a timer, timer is used to listen for a timer expiring, and del\_timer is used to delete a timer before it expires. Whereas the runtime environment provides this functionality in the implementation, an additional process has to be added to the model for simulation and verification.

External communication channels are defined with the prefix 'ext\_'. Again, for simulation and verification purposes, additional processes are included into the model to represent the environment. An implementation of this external behaviour is placed in a separate file and included in the main model. An option to generate the PROMELA specification as separate UNIX processes is available. External communication is based on server-client model. The server handles all the external communication and keeps track of the queue content, handles requests for reads from a channel, and notifies all clients if the content of any external channel changes. The actual communication is implemented using AF\_UNIX domain sockets, which can be manually changed to AF\_INET sockets for distributed communication.

The usefulness of this extension to Spin is limited, and the authors themselves describe its application field as the creation of test scenarios and the rapid prototyping of validated protocol implementations. One example is the generation of an implementation for the "Steam Boiler Control Specification Problem" [83].

### 2.4.2 Domain-Specific Languages

The dilemma facing any attempt to automate the generation of implementations is that, since system models should be kept as simple as possible for model checking, the specification generally does not contain enough information to allow the automated derivation of a detailed and efficient implementation. *Domain-specific languages* address this issue by optimising the process for a specific application area. Many of these languages are supported by compilers that can generate an application from the specification.

One such language is Esterel [8], which was designed for specifying synchronous reactive systems. The Esterel compiler generates a unique automaton from the specification. In the specific application area of protocol development, the HIPPCO optimising compiler [16] was developed to generate efficient protocol code from a protocol specification written in Esterel. Just like PROMELA, Esterel can be considered to be insufficiently expressive, which led to the development of PROMELA++ [6, 7, 5].

#### Promela++

Developed as part of a language-based framework for protocol construction, PROMELA++ is based on PROMELA and has been designed with a rich set of domain-specific constructs to facilitate protocol construction. This enables the PROMELA++ compiler to perform domain specific optimisations. The compiler can automatically convert protocol specifications in PROMELA++ to protocol models in PROMELA for verification, or to efficient C code for execution.

In a PROMELA++ program the control structure is separated from the low-level network access and data manipulation routines. This is done by specifying the control structure in PROMELA++, which can be converted directly to PROMELA, and implementing the low-level routines as blocks of C code embedded in the program. The C code that is allowed is restricted, specifically in the use of pointers, but still provides adequate functionality, especially in the form of access to system resources. When a PROMELA model is generated from a PROMELA++ specification the C code is not included and the model represents a finite-state automaton that encapsulates the control flow.

PROMELA++ has been used to implement protocols such as Horus and TCP, and generate

code with comparable performance to hand-optimised monolithic implementations. Unfortunately, Promela++ is restricted to the implementation of layered communication protocols.

### 2.4.3 A Transition System Approach

Bull and De Villiers have proposed a more general approach for the generation of reliable reactive systems, namely separating the flow of control from data manipulation [15, 14]. Using the same structure for the system model and implementation can help to ensure that the benefits obtained from the verification of the model is carried over to the implementation code. The authors suggested the use of transition systems as a general structure for reactive systems.

A transition system is identical to a finite-state automaton, but without any notion of acceptance [1]. A transition system can be represented as a graph, with the graph vertices representing the unique system states and the edges representing the transitions between the states. Each transition has a finite set of events associated with it, and the occurrence of any of these events enables the corresponding transition. Only enabled transitions are executable. A unique action is executed in response to each event, where actions are small independent code fragments that implement operations that may modify the system state.

Because reactive systems are usually event-driven, they naturally lend themselves to be structured as transition systems. Furthermore, transition systems are also suited to automata-theoretic model checking (as described in Section 2.2).

While the flow of control is model checked, it is still necessary to verify the details of data manipulation, but this is significantly simplified by the structure of the transition system. Since data manipulation is restricted to the separate, independent code segments that execute independently of unpredictable external events, their correctness can be ensured through the use of sequential program verification techniques such as weakest preconditions described in Section 2.1. These data manipulation code segments can also be optimised for the implementation without affecting the verification of the control structure.

Bull and De Villiers used this technique to implement a version of the alternating bit protocol with assembly level coding, and a minimal implementation of the TCP protocol in C as an example of a larger application. The TCP implementation turned out to be less efficient, but the authors claim that the problem is not inherent in the technique. More importantly, however, is the fact that the implementations were done by hand, which means that timing and relevance still remain issues, as well as the (albeit reduced) problem of reliability caused

by manual derivation. Again, automating the process of deriving the implementation from the verified model would address these issues, and the benefits of this approach would be preserved.

## 2.5 Model Extraction

Where in the first approach model checking is applied during the analysis and design phase, the approach described here is applied further down the software development process. A model is constructed from an actual implementation, the model verified, and the verification results applied to the implementation. The use of abstraction techniques is usually necessary to construct a tractable model from an implementation. This approach originates from investigations into the application of model checking to verify existing applications. In the first case studies the models were manually derived from the implementation code, but it quickly became apparent that for this approach to be viable the extraction process would have to be automated. This led to program model checking based on automated model-extraction, where the program is translated into the input notation of an existing model checker.

# 2.5.1 Manual Approach

The use of Spin to support the automated verification of time partitioning in the Honeywell DEOS real-time scheduling kernel [96, 97] is a good example of the manual application of this approach. The goal of the experiment was to investigate whether model checking with minimal abstraction could be used to find a subtle implementation error that was originally discovered and fixed during the standard formal review process.

To apply model checking, a core slice of the DEOS (Dynamic Enforcement Operating System) scheduling kernel was manually translated from C++ to PROMELA. To close the system for verification an abstraction of the system environment also had to be constructed. This was found to be the most difficult task in the original experiment. It was also found that program abstraction techniques are critical in making verification tractable.

The experiment was successful in rediscovering the known error in the implementation, showing that model checking could find errors in real programs that testing techniques did not. After the original experiment the model was expanded to bring it up-to-date with the kernel implementation. This update was done in one day by a Honeywell developer with no prior knowledge of PROMELA or SPIN, and on the first model checking run after the update a new

error was discovered by SPIN. The update of the model was based on a slightly outdated version of the DEOS code, and the error had already been discovered by Honeywell the previous week. However, where it originally took three days to discover the cause of the error, with SPIN it was possible to easily replay the error trace and identify the error.

A similar case-study was the application of SPIN to analyse part of the Remote Agent space craft controller [52]. This effort revealed four previously unknown classic concurrency errors. A very interesting development was that when the Remote Agent was finally activated in space it suffered a critical malfunction, which was later identified to have been caused by a coding error similar to one of those found using SPIN. This was in a part of the system not analysed in the case study, and it demonstrated to NASA that model checking can successfully be used to find mission critical errors.

These experiments clearly showed that model checking could be applied to implementation level code, and was successful in identifying critical errors that easily slip by traditional testing techniques.

#### 2.5.2 Java PathFinder I

Java PathFinder was developed as a first attempt by the Automated Software Engineering group at NASA Ames to automate the process of using model checking to analyse programs written in traditional programming languages [51, 53]. They chose to develop the system for Java, since they wanted to base it on a programming language that was object oriented, as well as popular. The tool was renamed to Java PathFinder 1 (JPF1) after the Mars PathFinder rover that explored Mars in 1997 [54].

JPF1 translates a given Java program into a PROMELA model, which can then be model checked using Spin. The model is generated with the same state space characteristics as the Java program (no analysis is applied to reduce the state space), which restricts the application to Java programs with finite and tractable state spaces. The Java programs may contain assertions that are translated to PROMELA assertions. Spin can then be used to check the model for deadlock and assertion violations. It is of course also possible to use Spin to check general LTL properties.

JPF1 only accepts a subset of Java 1.0, which restricts the possible program input. The authors do note, however, that at the time it translated more of Java than any other similar tool. A bigger issue is that certain features such as recursion and, more importantly, predefined class libraries are not supported. This severely restricts the applicability of the tool.

After this first implementation, it was realised that these restrictions could be avoided by instead applying model checking on the byte-code form of a Java program, without incurring a big loss in efficiency. This led to the development of Java PathFinder 2 (described in Subsection 2.6.4).

JPF1 was, however, considered a successful first experiment. It was used to detect a deadlock situation in a game server with 1400 lines of code, as well as to successfully locate the error that caused the malfunction of the Remote Agent (described above). A similar project is the JCAT tool that also generates PROMELA models from Java source code, for verification with SPIN and dSPIN [30].

#### 2.5.3 Bandera

Bandera is a tool for model checking Java source code, and implements a component-based architecture for model extraction designed to maximise scalability, flexibility and extensibility [25, 33]. While it is similar to the JPF and JCAT tools in the sense that it also translates Java source code to the input language of one of several existing model-checking tools (which includes PROMELA), it is much more than just a translator, and specifically differ from these tools in that it implements techniques that allow the generation of verification models tailored to the property to be checked. The Bandera toolset is an integrated collection of program analysis, transformation and visualisation components. It takes as input Java source code and a software requirement formalised in Bandera's temporal specification language, and generates a program model specification in the input language of one of several existing model-checking tools, which includes Spin [61], dSpin [29], SMV [85], and Java PathFinder [12].

Bandera generates a custom program based on the specific property to be checked through the use of program slicing and abstraction. A library of abstractions are available for the user to choose from, or optionally add new abstraction definitions to. The reduced representation of the program is fed to the Bandera backend, which generates a finite-state model in the input language of a verification tool as chosen by the user. The output generated by the verifier is then interpreted by Bandera, and any counterexample is mapped back to the original source code. Bandera also allows the user to inspect the error trail interactively.

Although Bandera can handle realistic classes of Java programs, it accepts a restricted set of Java. Several other limitations are described in [50], but it should be noted that Bandera is not so much an industrial-strength tool, as a large collection of diverse tools to facilitate further experimentation. A similar tool was developed by the Hardware Verification Group at

Stanford University [93]; it translates Java to SAL, an intermediate language for interfacing model checking and theorem proving tools.

#### 2.5.4 FeaVer