# LF: A Language for Reliable Embedded Systems

# A THESIS SUBMITTED TO THE DEPARTMENT OF COMPUTER SCIENCE OF THE UNIVERSITY OF STELLENBOSCH IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

By F.A. van Riet November, 2001

# Declaration

I the undersigned hereby declare that the work contained in this thesis is my own original work and has not previously in its entirety or in part been submitted at any university for a degree.

# Abstract

Computer-aided verification techniques, such as model checking, are often considered essential to produce highly reliable software systems. Modern model checkers generally require models to be written in **CSP**-like notations. Unfortunately, such systems are usually implemented using conventional imperative programming languages. Translating the one paradigm into the other is a difficult and error prone process.

If one were to program in a process-oriented language from the outset, the chasm between implementation and model could be bridged more readily. This would lead to more accurate models and ultimately more reliable software.

This thesis covers the definition of a process-oriented language targeted specifically towards embedded systems and the implementation of a suitable compiler and run-time system.

The language, **LF**, is for the most part an extension of the language **Joyce**, which was defined by Brinch Hansen. Both **LF** and Joyce have features which I believe make them easier to use than other **CSP** based languages such as **occam**. An example of this is a selective communication primitive which allows for both input and output guards which is not supported in **occam**.

The efficiency of the implementation is important. The language was therefore designed to be expressive, but constructs which are expensive to implement were avoided. Security, however, was the overriding consideration in the design of the language and runtime system.

The compiler produces native code. Most other **CSP** derived languages are either interpreted or execute as tasks on host operating systems. Arguably this is because most implementations of **CSP** and derivations thereof are for academic purposes only. **LF** is intended to be an implementation language.

The performance of the implementation is evaluated in terms of practical metrics such as the time needed to complete communication operations and the average time needed to service an interrupt.

# Opsomming

Rekenaar ondersteunde verifikasietegnieke soos programmodellering, is onontbeerlik in die ontwikkeling van hoogs betroubare programmatuur. In die algemeen, aanvaar programme wat modelle toets **CSP**-agtige notasie as toevoer. Die meeste programme word egter in meer konvensionele imperatiewe programmeertale ontwikkel. Die vertaling vanuit die een paradigma na die ander is 'n moelike proses, wat baie ruimte laat vir foute.

Indien daar uit die staanspoor in 'n proses gebaseerde taal geprogrammeer word, sou die verwydering tussen model en program makliker oorbrug kon word. Dit lei tot akkurater modelle en uiteindelik tot betroubaarder programmatuur.

Die tesis ondersoek die definisie van 'n proses gebaseerde taal, wat gemik is op ingebedde programmatuur. Verder word die implementasie van 'n toepaslike vertaler en looptyd omgewing ook bespreek.

Die taal, **LF**, is grotendeels gebaseer op **Joyce**, wat deur Brinch Hansen ontwikkel is. **Joyce** en op sy beurt **LF**, is verbeterings op ander **CSP** verwante tale soos **occam**. 'n Voorbeeld hiervan is 'n selektiewe kommunikasieprimitief wat die gebruik van beide toevoer- en afvoerwagte ondersteun.

Omdat 'n effektiewe implementasie nagestreef word, is die taal ontwerp om so nadruklik moontlik te wees, sonder om strukture in te sluit wat oneffektief is om te implementeer. Sekuriteit was egter die oorheersende oorweging in die ontwerp van die taal en looptyd omgewing.

Die vertaler lewer masjienkode, terwyl die meeste ander implementasies van CSP-agtige tale geinterpreteer word of ondersteun word as prosesse op 'n geskikte bedryfstelsel— die meeste CSP-agtige tale word slegs vir akademiese doeleindes aangewend. LF is by uitstek ontwerp as implementasie taal.

Die evaluasie van die stelsel se werkverrigting is gedoen aan die hand van praktiese maatstawwe soos die tyd wat benodig word vir kommunikasie, sowel as die gemiddelde tyd benodig vir die hantering van onderbrekings.

# Acknowledgements

I gratefully acknowledge the help and support of all the individuals and companies who made this thesis possible.

- Dr. P.J.A de Villiers for his support, guidance and countless pep talks.

- SAN People for their generous bursary which made this paper possible.

- All of my friends especially Pierre and Hanli for helping me maintain my sanity.

# Contents

| A | bstra           | ct     |                                                  | iii |

|---|-----------------|--------|--------------------------------------------------|-----|

| O | $\mathbf{psom}$ | ıming  |                                                  | iv  |

| A | cknov           | wledge | ments                                            | v   |

| 1 | Intr            | oducti | on                                               | 1   |

| 2 | LF:             | A Pro  | cess oriented language                           | 4   |

|   | 2.1             | Langu  | age concepts                                     | 4   |

|   |                 | 2.1.1  | Processes                                        | 4   |

|   |                 | 2.1.2  | Communication                                    | 5   |

|   |                 | 2.1.3  | Other Language attributes                        | 10  |

|   | 2.2             | Type   | rules                                            | 13  |

|   | 2.3             | Design | considerations                                   | 13  |

|   |                 | 2.3.1  | Ports                                            | 13  |

|   |                 | 2.3.2  | Reference parameters                             | 16  |

|   |                 | 2.3.3  | Process instantiation                            | 17  |

|   |                 | 2.3.4  | Polling semantics                                | 17  |

|   |                 | 2.3.5  | Channel sharing                                  | 19  |

|   | 2.4             | Securi | ty claims                                        | 19  |

|   | 2.5             |        | fined entities and implementational dependencies | 20  |

|   | 2.6  | The LF compiler $\dots$                     | 21 |

|---|------|---------------------------------------------|----|

|   |      | 2.6.1 Code generation                       | 23 |

|   |      | 2.6.2 Examples of code generated            | 26 |

|   |      | 2.6.3 Final remarks                         | 31 |

| 3 | LF   | examples                                    | 32 |

|   | 3.1  | Simple                                      | 32 |

|   | 3.2  | Generate                                    | 33 |

|   | 3.3  | Copy                                        | 34 |

|   | 3.4  | Merge                                       | 34 |

|   | 3.5  | Suppress                                    | 35 |

|   | 3.6  | Buffer                                      | 36 |

|   | 3.7  | Recursive instantiation                     | 37 |

|   | 3.8  | Simple device driver                        | 38 |

|   | 3.9  | A Linked List                               | 41 |

|   | 3.10 | Remarks                                     | 42 |

| 4 | Rur  | ntime System                                | 44 |

|   | 4.1  | Design Criteria                             | 44 |

|   | 4.2  | The modular structure of the runtime system | 45 |

|   | 4.3  | Design overview                             | 46 |

|   | 4.4  | Memory allocation                           | 46 |

|   | 4.5  | Process Management                          | 48 |

|   |      | 4.5.1 Process creation                      | 48 |

|   |      | 4.5.2 Context switches                      | 50 |

|   |      | 4.5.3 Process termination                   | 52 |

|   | 4.6  | Interrupt handling and Devices              | 52 |

|   | 4.7  | The scheduler                               | 53 |

|   | 4.8  | Fairness                                                                                | 55 |

|---|------|-----------------------------------------------------------------------------------------|----|

|   | 4.9  | Communication                                                                           | 56 |

|   |      | 4.9.1 Simple Communication                                                              | 56 |

|   |      | 4.9.2 Implementing the SELECT                                                           | 58 |

|   | 4.10 | Communications performance                                                              | 60 |

|   | 4.11 | Runtime checks                                                                          | 64 |

|   | 4.12 | Clock cycle analysis                                                                    | 67 |

|   |      | 4.12.1 Effective overhead of runtime checks                                             | 69 |

|   |      | 4.12.2 Index, overflow and NIL-dereference checks $\dots \dots \dots \dots \dots \dots$ | 69 |

|   |      | 4.12.3 Overhead of variable initialisation                                              | 70 |

|   |      | 4.12.4 Cost of a system call                                                            | 71 |

|   |      | 4.12.5 Interrupt latency in the LF Runtime system                                       | 73 |

|   |      | 4.12.6 Actual Performance                                                               | 73 |

|   |      | 4.12.7 Copying messages                                                                 | 76 |

|   | 4.13 | The size of the runtime system                                                          | 76 |

|   | 4.14 | Stackless execution model                                                               | 77 |

|   | 4.15 | Conclusion                                                                              | 78 |

|   | Fvo  | luation and Conclusion                                                                  | 80 |

| , |      |                                                                                         | 80 |

|   | 5.1  | Evaluation of the LF language                                                           |    |

|   | 5.2  | Evaluation of the Compiler and Runtime System                                           | 81 |

|   | 5.3  | Future work                                                                             | 82 |

|   | 5.4  | Final Remarks                                                                           | 83 |

| A | EBI  | NF                                                                                      | 84 |

|   |      | A.0.1 Declarations                                                                      | 84 |

|   |      | A.0.2 Statements                                                                        | 85 |

|   |      | A.0.3 Expressions                                                                       | 85 |

|   |      |                                                                                         |    |

# List of Tables

| 1 | Predefined types                            | 20 |

|---|---------------------------------------------|----|

| 2 | General functions                           | 22 |

| 3 | Bitwise functions                           | 22 |

| 4 | I/O functions                               | 22 |

| 5 | Heap manager functions                      | 22 |

| 6 | Instructions and clock cycles on the i386EX | 68 |

| 7 | Actual context switch times                 | 75 |

| 8 | Size of the Runtime System                  | 77 |

| 9 | Runtime system memory overhead (bytes)      | 7  |

# List of Figures

| 1  | The null program                       | 5  |

|----|----------------------------------------|----|

| 2  | A program defining two processes       | 6  |

| 3  | Defining a port type                   | 8  |

| 4  | Simple communication                   | 8  |

| 5  | Channel sharing                        | 9  |

| 6  | The structure of a SELECT              | 10 |

| 7  | Waiting on an interrupt                | 11 |

| 8  | Variables at physical addresses        | 11 |

| 9  | Simple use of pointers                 | 12 |

| 10 | No output guards                       | 17 |

| 11 | Output guards                          | 18 |

| 12 | Sets in Oberon                         | 21 |

| 13 | Sets in LF                             | 21 |

| 14 | GetReg for rArch                       | 23 |

| 15 | GetAdrReg for i386                     | 24 |

| 16 | GetReg for <i>i386</i>                 | 25 |

| 17 | An expression requiring sign extension | 25 |

| 18 | Sign extension                         | 25 |

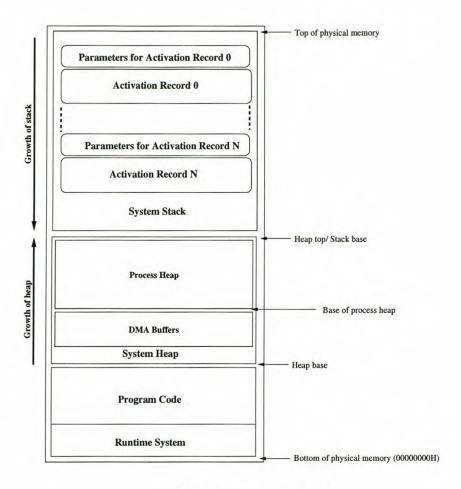

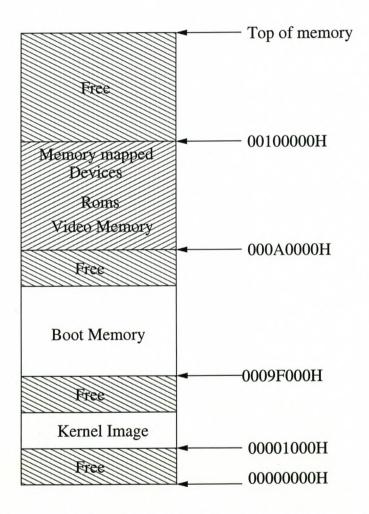

| 19 | System memory layout                   | 47 |

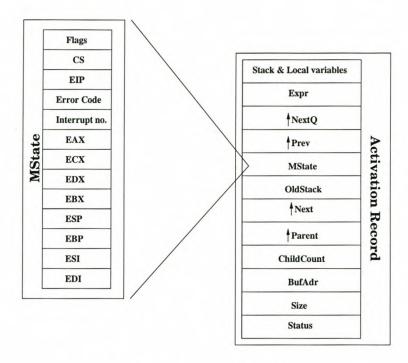

| 20 | Internal representation of processes   | 49 |

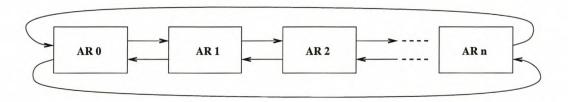

| 21 | Ring of process ARs                                  | 49 |

|----|------------------------------------------------------|----|

| 22 | State of stack during context switch                 | 51 |

| 23 | The skeleton of an interrupt handler                 | 51 |

| 24 | Continue                                             | 52 |

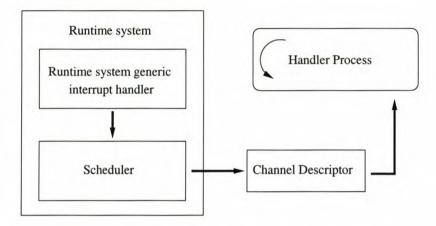

| 25 | The interrupt mechanism $\hdots$                     | 53 |

| 26 | The scheduler                                        | 54 |

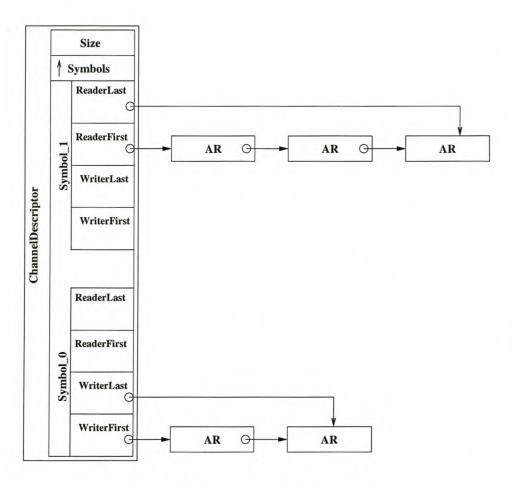

| 27 | Communications channels                              | 57 |

| 28 | HookIt                                               | 58 |

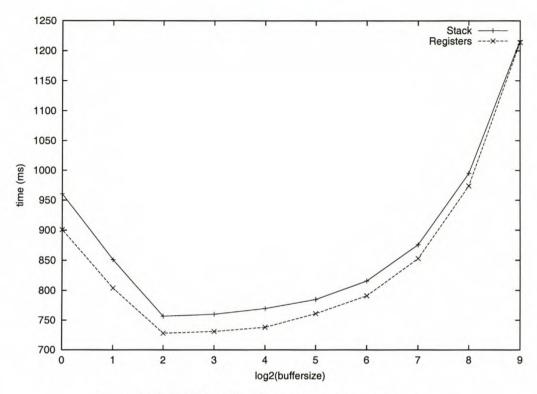

| 29 | IPC with and without registers to pass parameters    | 61 |

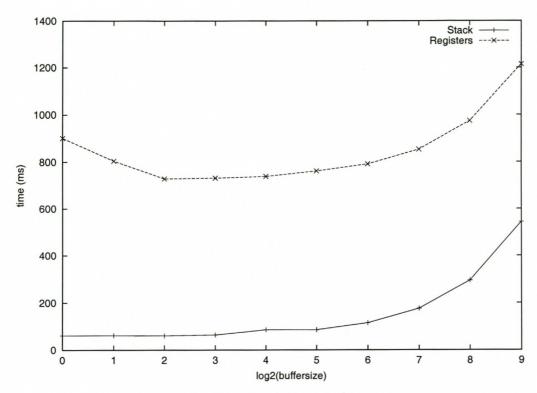

| 30 | IPC vs. Procedure Call                               | 62 |

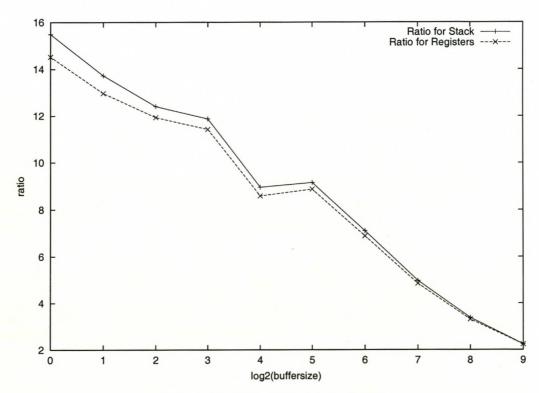

| 31 | IPC to Procedure call ratio                          | 62 |

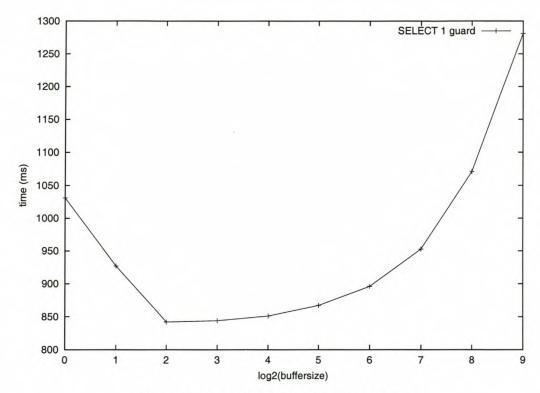

| 32 | Times for a SELECT with one guard                    | 63 |

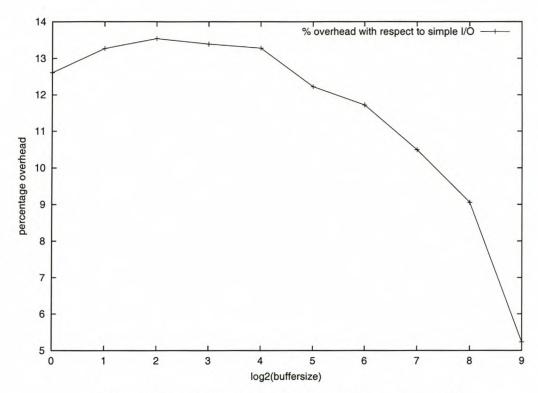

| 33 | Percentage overhead of select relative to simple I/O | 64 |

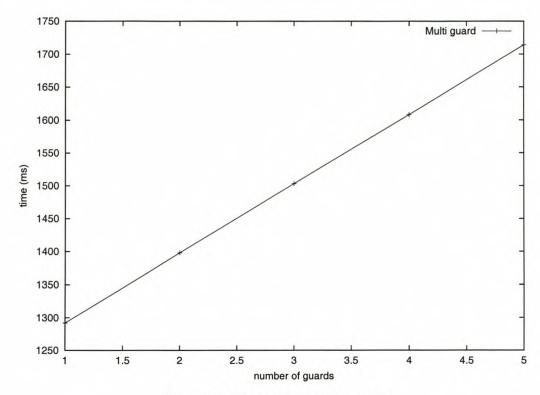

| 34 | Test program for multiple-guard SELECT               | 65 |

| 35 | Select with multiple guards                          | 66 |

| 36 | Index checks                                         | 69 |

| 37 | NIL checks                                           | 69 |

| 38 | A simple array reference                             | 70 |

| 39 | Index checks                                         | 70 |

| 40 | System call restoring machine state                  | 72 |

| 41 | Overhead of a null system call                       | 72 |

| 42 | An empty procedure                                   | 73 |

| 43 | Interrupt overhead                                   | 74 |

| 44 | Test code for interrupts                             | 76 |

| 45 | System memory layout as created by the boot loader   | 88 |

# Chapter 1

# Introduction

To produce correct software is inherently difficult. Commercial software is typically put through exhaustive testing to ascertain its correctness. This approach not only consumes much time, but does not identify all the errors in programs. Formal methods, such as model-checking, have emerged to try and address the problem of checking program correctness. A major stumbling block in the use of model checkers is the disparity between the notations of formal specifications and the programming languages in general use. Many model checkers employ specification languages that are either derived from CSP [17] (such as SPIN's Promela) or check CSP directly (FDR[12]).

If one wishes to incorporate the use of model checkers into the software development cycle, one of two approaches is possible. A model of the program can be developed as part of the specification process. The model can then be used as a basis from which to derive the source code. Alternatively one may infer the model from existing source code.

The abstract process algebraic notation of **CSP** does not have a direct mapping onto conventional programming constructs. The ideal would be to have a programming language that is both useful and practical as an implementation tool, but also allows for easy translation to and from a formal **CSP** specification.

In this thesis I propose a language that strives to meet this challenge. The proposed language, LF, aims to be an implementation language with constructs similar to that of CSP. This will facilitate automatic or semi-automatic conversion to (and possibly from) formal CSP notation<sup>1</sup>. The greatest challenges in this endeavour are:

- To design a language that is expressive enough for the purpose of programming embedded applications.

- 2. To ensure that no construct within the language compromises the efficiency of LF as an

<sup>&</sup>lt;sup>1</sup>Indeed the process of translating **LF** to **Promela** and model checking it, is the topic of another Masters project currently under way [9].

implementation language.

3. To ensure that translation to the notation accepted by a model checker is possible.

LF is intended primarily for use in embedded systems. A precise definition of an embedded system is an elusive concept. Broadly speaking one may define embedded software as: software executing on a platform with relatively limited resources, typically performing control functions that are intimately related to the hardware, but which are imperceivable to the user. Embedded systems exhibit the following attributes:

- The embedded software is often a monolithic piece of code. It may therefore be implemented in a single secure programming language.

- Embedded software is intricately involved with the hardware on which it runs. This implies that the hardware should be readily accessible to the programmer.

- Furthermore, it generally requires efficient management of limited resources. Scheduling that is highly responsive to interrupts, is often required. Efficiency both in terms of performance and memory usage is important.

- The need for low level operations introduces many opportunities for corrupting the system.

A compromise needs to be reached between making the language expressive enough for low level programming, and imposing sufficient constraints on the programmer to allow some measure of safe-guarding in the language.

**LF** is claimed to be a secure language. Hoare describes the concept of security in the following way [15]:

"... Firstly, the notations (of a programming language) should be designed to reduce as far as possible the scope for coding error; or at least to guarantee that such errors can be detected by a compiler ... Certain programming errors cannot always be detected in this way, and must be cheaply detectable at run time; in no case can they be allowed to give rise to machine or implementation dependent effects that cannot be explained in terms of the language itself ... '

Simply put, a **secure system** is one in which code that adheres to the syntactic and semantic constraints of the language is guaranteed not to corrupt the system. A corrupt system is loosely defined as a system existing in a state that is not defined by the program. Semantic constraints refer to the "rules of use" of constructs and include typing constraints.

In practice such a strict form of security is not a viable proposition. A less rigorous form of security is needed. **LF** therefore offers the guarantee that code that adheres to the syntactic and semantic constraints of the language cannot lead to corruption of the allotted memory of a process by another process.

The need for a relaxed form of security arises primarily because of the use of embedded systems as the target environment. Such systems need to access hardware directly. This has the potential of placing the processor or other hardware components in inconsistent states. A simple example should suffice:

Assume that an embedded system consists of two processes one of which, p, is an interrupt handler and some other process, q, that inadvertently writes to the wrong I/O port. Let us further assume that this port controls the interrupt controller hardware. If the interrupt which is to be handled by p is now disabled, process p will be rendered useless. All of this has however taken place within the syntactic and semantic constraints of the language.

Unfortunately no practical way of imposing a safe hardware abstraction at this low level could be identified.

As a somewhat philosophical aside, one might argue that a program that conforms to the stated criteria for security, may indeed not be secure in the sense formerly defined if compiled by a faulty compiler. For the purposes of this thesis however we will assume a correct compiler implementation.

LF is based on the Joyce system proposed by Brinch Hansen [7]. Essentially Joyce (and LF) presents the programmer with the means to implement concurrent processes that may communicate by way of synchronous message passing. Apart from the fact that Joyce was not put to much practical use, the system employed a P-Code interpreter which is not an efficient execution environment. As such this project offers valuable insight into the practicality of the programming paradigm introduced by Joyce.

#### Outline of this thesis:

- In Chapter 2 the grammar and semantics of LF are presented. The choice of language

constructs and features are examined. Important similarities as well as differences with other

CSP-derived languages such as Joyce and occam are discussed [7, 21]. A brief discussion

of the compiler and code generation concludes the chapter.

- Some examples of **LF** code are presented in **Chapter 3**. These examples highlight the most important features of the language.

- The runtime system is explained in detail in **Chapter 4**. The design of the system is motivated and performance figures are presented.

- Chapter 5 is a critical evaluation of the system both in terms of the language and the runtime system. Future extensions to the system are also discussed.

# Chapter 2

# LF: A Process oriented language

LF is a practical, secure, programming language with strong ties to CSP. The compiler and runtime checks enforce the integrity of the system, thereby obviating the need for hardware memory protection. In this chapter the grammar and semantics of LF are discussed. Considering the concurrent nature of the language, the syntactic and semantic definition of the language should not preclude future multiprocessor implementations. The language definition is presented as it pertains to a single processor implementation.

# 2.1 Language concepts

The basic notation of **LF** is similar to that of **Oberon** and other members of the **Pascal** family [36, 34]. For this reason and the sake of brevity, the focus of this discussion is on the features of the language which relate to concurrency. The complete grammar of **LF** in **EBNF** notation may be found in Appendix A.

#### 2.1.1 Processes

An **LF** program consists of a set of communicating processes. An initial process is instantiated and may then spawn other (child) processes dynamically. Child processes execute concurrently with their parents. A simplified **EBNF** definition for an **LF** program is shown below.

```

\label{eq:program} $::= PROGRAM identifier; $$ \langle \operatorname{declarations} \rangle \langle \operatorname{processes} \rangle ::= { \langle \operatorname{process} \rangle ::= \{ \langle \operatorname{process} \rangle ::= PROCESS identifier[\langle \operatorname{parameter list} \rangle]; \langle \operatorname{declarations} \rangle \langle \operatorname{body} \rangle; $$ \langle \operatorname{body} \rangle ::= BEGIN \langle \operatorname{command list} \rangle END identifier$$

```

```

PROGRAM Null;

(*

The simplest possible LF program.

*)

BEGIN (* main process *)

END Null.

```

Figure 1: The null program

The null program is listed in Figure 1. Process instantiation follows the same syntax as procedure invocation in most imperative languages. Examples of process instantiation may be found in lines 17 and 18 of Figure 2. The instantiation of processes is hierarchical in nature. The BEGIN-END block which is associated syntactically with the reserved word PROGRAM, is called the *main process*. Lines 16 to 19 of Figure 2 constitute a main process. In the main process, processes P1 and P2 are instantiated. Process P2 is instantiated with the value parameter x. From line 01 it should be evident that x has the value 42. All processes with the exception of the *main process* have a parent. Unbounded (recursive) instantiation of processes is supported.

In keeping with **CSP**, no global variables are allowed. The use of global variables are inherently dangerous in concurrent systems, as it amounts to shared memory. The variables of a process are inaccessible to other processes. The encapsulation of data is therefore done at process level.

Parent processes only terminate once all their children have terminated. This, in addition to the tree structure of process invocation, simplifies memory management: An activation record is created for each instance of a process. The tree structure of activation records can be physically represented as a stack—with the top of the stack representing the most recently activated process. As processes terminate, their activation records are popped from the stack. Processes reaching the end of their execution are automatically terminated, provided that the above constraint is satisfied. In Figure 2 process P1 will execute indefinitely while process P2 will terminate after setting local variable x to 1. When a process terminates, its local variables are destroyed.

Processes may pass information to one another in one of two ways:

- Inter-Process Communication primitives which will be discussed in the next section.

- Value parameters are used for passing values to processes upon instantiation.

## 2.1.2 Communication

Processes communicate by way of messages which are transmitted over *channels*. A channel constitutes the logical link between two communicating processes. Processes create channels dynamically. Channels are accessed by way of port variables. Port variables are therefore references to the logical entities called channels and are instances of a type definition, a port type. An analogue exists in terms of dynamic memory. A port may be likened to a pointer and a channel likened to the

```

PROGRAM ProcessInstantiation;

(*

This program defines and instantiates

two additional processes.

*)

00 CONST

01 x = 42;

02 PROCESS P1;

03 VAR

04 x : UINT8;

05 BEGIN

06 \quad x := 0;

WHILE TRUE DO

07

x := x+1

80

09

END

10 END P1;

11 PROCESS P2( x : UINT32 );

(*

x is a value parameter

*)

12 BEGIN

13 x := 0;

14 x := x+1

15 END P2;

16 BEGIN

17 P1; (* instantiate P1 *)

18 P2(x) (* instantiate P2 *)

19 END ThreeProcess.

```

Figure 2: A program defining two processes

memory which was dynamically allocated and is referenced by the pointer. Just as pointers may be required to point to instances of a specific type in languages such as **LF** and **Oberon**, a port also has a specific type.

```

\langle \text{porttype} \rangle ::= [\langle \text{alphabet} \rangle];

\langle \text{alphabet} \rangle ::= \langle \text{symbol} \rangle \{, \langle \text{symbol} \rangle \}

\langle \text{symbol} \rangle ::= identifier [(\langle \text{type} \rangle)]

```

Ports (as all types) in **LF** are typed using name equivalence. Types are associated with ports by way of alphabets. An alphabet consists of a fixed set of symbols. A symbol may optionally have a type associated with it. When no type is associated with a symbol, the symbol is referred to as a signal. As the name implies, signals are used to signal events. A signal does not copy any data. As such, the use of signals is more efficient in cases where messages are used only for synchronisation.

In Figure 3 a port type named Chan is defined with an alphabet consisting of symbols a and b. Port variable chan is an instance of port type Chan. The type of symbol a is UINT32. Symbol b is a signal.

A message is a value of the same type as the appropriate symbol in the appropriate port type, which is copied from one process to another, using the channel as logical communication medium. Signals do not strictly conform to the above definition. One can however regard all signals as having some implicit generic type. As far as the actual transmission of data is concerned, a signal does not require the actual transfer of data, but the runtime system still needs to perform all of the operations needed to transfer a normal message except for the actual copying of the data. A symbol does therefore not directly relate to an entity but is merely used to facilitate strict type checking. The use of symbols and messages will become apparent shortly.

During a given communication between two processes, a channel may carry any one (and only one) of these symbols. The programmer must explicitly state the direction of communication over the channel. The reserved words IN and OUT indicate this direction. Note that the semantics of LF therefore prohibits the same process from communicating, in both directions, over the same channel. This makes it impossible for a process to deadlock by communicating with itself over the same channel. Clearly few programmers will make this mistake during design, but it is easy to mistype a '!' for a '?' (See below).

Syntactically, communication in **LF** is similar to **CSP**. This is evident from the following **EBNF** definition.

```

\begin{aligned} &\langle \text{io} \rangle ::= \langle \text{bang} \rangle | \langle \text{hook} \rangle \\ &\langle \text{bang} \rangle ::= \langle \text{variable access} \rangle \; ! \; \textit{identifier}[(\langle \text{expression} \rangle)] \\ &\langle \text{hook} \rangle ::= \langle \text{variable access} \rangle \; ? \; \textit{identifier}[(\langle \text{variable access} \rangle)] \end{aligned}

```

The statement c ! a(i) in Figure 4 sends the value of the variable i over channel c. Assume that the type Chan has the same definition as in Figure 3. Notice the type equivalence between

```

PROGRAM AlphabetDefinition;

TYPE

Chan = [a(UINT32),b];

PROCESS P1(IN c : Chan);

BEGIN

END P1;

VAR

OUT chan : Chan;

BEGIN

P1(chan)

```

Figure 3: Defining a port type

```

VAR

OUT c : Chan;

IN d : Chan;

i : UINT32;

BEGIN

c ! a(i); c ! b

d ? a(i); d ? b

```

Figure 4: Simple communication

the definition of symbol b and the actual variable i. Symbols therefore represent the set of the types of messages that may be sent, whereas the **value** of variable i is sent over the channels as the actual message. The statement d ? a(i) receives a value of type UINT32 over the channel and assigns this value to variable i. The commands c ! b and d ? b are analogous but use signals.

When an **LF** process p (the sender) is ready to send a message to another process q (the receiver) which is ready to accept the message, p and q are said to match and communication is feasible. Strictly speaking the communication commands within the processes are matched, but in the interest of brevity these two meanings are taken to be equivalent. The Bang and Hook then execute simultaneously. Both processes will continue concurrently. This approach to message passing is also used by Joyce and occam. On a uni-processor system only a single process can actually execute at any given time. The precise order of execution is determined by the scheduler. Scheduling is discussed in Chapter 4.

Several processes may share a channel. Channel sharing is achieved by passing port variables as value parameters to processes. In Figure 5 processes P1 and P2 have access to a common channel through port variable c. Because of channel sharing processes may match in various combinations. In Figure 5, the *Hook* in process P2 may match with any one of the instances of process P1. Communication takes place in a first-come-first-served manner in this event. When a communication statement is not matched, the process issuing the command (either a *Bang* or

```

PROGRAM Share;

Chan = [a(UINT8)];

PROCESS P1( c : Chan );

VAR

i : UINT8;

BEGIN

c ! a( i )

END P1;

PROCESS P2;

VAR

c : Chan;

i : UINT8;

BEGIN

NEW(c);

P1(c); P1(c);

c?a(i)

END P2;

BEGIN

END Share;

```

Figure 5: Channel sharing

Hook) behaves in one of two ways. If the communication statement was used as part of a simple input/output command (a Bang or Hook command) the process is blocked until communication is feasible. A process may also issue a communication command as part of a guard in a SELECT statement as explained below.

```

\langle \mathrm{select} \rangle ::= \mathtt{SELECT} \langle \mathrm{select\ guard} \rangle \ \mathtt{THEN} \langle \mathrm{command\ list} \rangle   \{ \ [\ ] \langle \mathrm{select\ guard} \rangle \mathtt{THEN} \langle \mathrm{command\ list} \rangle \}   \mathtt{END}.   \langle \mathrm{select\ guard} \rangle ::= \langle \mathrm{variable\ access} \rangle \langle \mathrm{io} \rangle [\& \langle \mathrm{expression} \rangle].

```

As shown in the above box, a SELECT construct consists of a set of guards, with a command list associated with each guard. Each guard consists of a communication statement with an optional boolean expression. A guard evaluates to true when the communication statement is matched and the boolean expression evaluates to true. The SELECT will non-deterministically choose one of the guards which evaluates to true and execute its command list. When no guards are true the construct as a whole blocks until a guard becomes true. The structure of a SELECT statement is outlined in Figure 6. Each  $S_i$  refers to a command list and each  $chan_i$  refers to a channel. Note the use of boolean expressions in the guards and the fact that these expressions refer to the variables used in the communication. The relevance of this facility is discussed in Section 2.3.4.

```

SELECT  \begin{array}{c} \operatorname{chan}_1 ? \ \operatorname{c}(\ x\ ) \ \& \ x \ > \ 0 \ \mathrm{THEN} \\ S_1 \\ [] \ \operatorname{chan}_2 \ ! \ \operatorname{s}(\ y\ ) \ \mathrm{THEN} \\ S_2 \\ \mathrm{END} \end{array}

```

Figure 6: The structure of a SELECT

Note that two *SELECT* statements cannot match. The need for this restriction is explained in Section 2.3.4.

## 2.1.3 Other Language attributes

The syntax and semantics of assignments as well as the definition of variables, constants and types are similar to that of **Pascal** and more specifically, **Oberon**. The syntax of these constructs can be seen in the examples presented in Chapter 3. A complete **EBNF** definition may be found in Appendix A. The most notable language attributes not already discussed and the reasoning behind their use are outlined below.

• The LF runtime system transforms an interrupt event into a message. An array of ports is predefined. Each element of the array corresponds to one of the possible interrupts that may occur on a specific target platform. The size of the array is therefore implementation specific (it is referred to as MaxInt below). Listed below is a definition of the array —called IntChannels— as it would appear to the programmer.

```

TYPE

IntPort = [sig];

VAR

IntChannel = ARRAY MaxInt OF IntPort;

```

This introduces a platform dependence into the language specification, but since only the size of the array changes on different platforms it is of little consequence to the programmer. This approach makes the use of the system consistent by not having special constructs related to interrupts. From the programmer's point of view interrupt handling does not represent a deviation from the general language constructs. Figure 7 shows a process that continuously waits on interrupt 32. The definition of IntChannels clearly assumes an underlying architecture which supports interrupt vectoring, but the scheme as proposed here will work on platforms which do not implement it explicitly. Interrupt vectoring can be cheaply implemented in the runtime system. The variable IntChannels is visible to the programmer, but not the type IntPort. Therefore one cannot declare a variable of type IntPort. The details of interrupt handling within the runtime system are discussed in Section 4.6. Chapter 3 contains a complete example of interrupt handling within an LF process. The language occam

```

BEGIN

NEW( IntChannels[32] ); (* use of predefined array IntChannels *)

WHILE TRUE DO

IntChannels[32] ? sig

END

```

Figure 7: Waiting on an interrupt

```

(* Accessing a memory mapped display *)

TYPE

DisplayPage = ARRAY 2000 OF RECORD

char,attr : UINT8

END;

VAR

dp : DisplayPage AT $b8000;

BEGIN

dp[0].char = 65; (* write "A" to (0,0) on the screen *)

:

```

Figure 8: Variables at physical addresses

uses a similar abstraction. In **occam**, however, each channel is associated with a specific device driver implemented in the **occam** runtime system —so-called *hard channels* [26]. **LF** offers more flexibility than **occam** since **LF** does not implement device drivers as part of its runtime system.

- LF allows the programmer to define a data structure at a specific physical address. This allows the development of device drivers that need to access memory mapped devices. The display memory is a good example. The possible violation of the system integrity is minimised by the fact that the address value has to be a constant. Once a variable is defined at a physical address, no other variable may be defined within an overlapping memory range. The range is defined by the size of the variable. The compiler keeps a table which ensures that these memory ranges do not overlap. Of course only one instance of a process that declares a specific absolute variable may be instantiated. A bitmap is kept by the runtime system which sets a bit corresponding to each process defining such a variable. When the process is instantiated, the bit is set and when it is destroyed, the bit is cleared. Once the bit is set, the creation of another such process will result in a runtime exception. In Figure 8, an example of how to access a memory mapped display page is given for the IBM PC.

- Typed pointers are supported. No arithmetic operations are allowed on pointers. This limits (but does not completely remove) the inherent dangers of pointers. A heap essentially introduces shared memory, as would be the case with reference parameters. Only structured types (RECORDs, ARRAYs) may be allocated on the heap. This discourages the indiscriminate use of small allocations on the heap. The allocation of a 32-bit integer variable would for

```

TYPE

PAr = POINTER TO ARRAY 10 OF UINT16;

P = POINTER TO Rec;

Rec = RECORD

n : P

END;

VAR

r : Rec;

p : PAr;

BEGIN

NEW( r );(* initialise r *)

r \(^n := NIL;

NEW( p );

p \(^10) := 0

}

```

Figure 9: Simple use of pointers

instance require up to 8 bytes of heap management overhead. It should be clear from Figure 9 that syntactically the use of pointers is identical to that of **Pascal**. Pointers are dereferenced with the "↑" character.

- All variables are zero initialised. This allows for the detection of the dereferencing of uninitialised pointers and the detection of references to uninitialised channels. All references to pointers and channels (which are represented in the runtime system by pointers) are compared to 0. An uninitialised channel will have a pointer with the value 0 and a runtime exception will be generated in such a case. A pointer with the value 0 is not necessarily uninitialised, as the programmer may have assigned the value NIL to it, but dereferencing of a pointer with the value of 0/NIL, will always cause a runtime exception. Variable initialisation may introduce significant runtime overhead upon process instantiation, but is vital in ensuring the security of the system. All variables are zero initialised as this is generally more efficient, both in terms of code size and execution time, than selective initialisation.

- Record structures are packed i.e. no padding to align fields on machine word boundaries

is performed. This leads to a significant reduction in execution speed on most hardware

platforms. Padding, however, wastes a substantial amount of memory. Moreover, padding

causes problems with the allocation of variables at specific physical addresses.

- Separate compilation is not supported. The whole program needs to be in a single file. The

system produces a single statically linked code image that is loaded by a boot-loader. The

image contains both the LF object code and the runtime system. This is well suited to

small embedded applications. The boot-loader as well as the structure of the static image

are discussed in Chapter 4 and Appendix B.

# 2.2 Type rules

Strict type checking, by way of name equivalence, is enforced over communication channels and also applied to all other variables. Type compatibility between integer types is governed by special rules. Six integer types, representing signed and unsigned values in 8, 16 or 32 bits, are defined, (U) INT32 being a 32 bit variable, (U) INT16 a 16 bit variable and (U) INT8 an 8 bit variable. (U) INT16 and (U) INT8 may be regarded as subsets of (U) INT32. Similarly (U) INT8 is a subset of (U) INT16. The 'U' prefix refers to unsigned values in each case.

All integer types within either the signed **or** unsigned class may be compared. Assignment however requires that a subset type be assigned to a superset type. Unsigned and signed types are **not** assignment compatible, nor may they be compared.

# 2.3 Design considerations

This section motivates many of the design decisions that were made with respect to communication and other aspects of the language. The options pertinent to each aspect of communication are discussed in **general terms** and the ones adopted for **LF** are then explained.

Barring the value parameters passed at process initialisation, inter-process communication (*IPC*) is the only means of exchanging information between processes. *IPC* may be implemented by way of two primitives [25]:

- send(x,message)

- receive(y, message)

The variables x and y refer to the destination and source of the message respectively. A process P wishing to transmit a message to process Q does so by invoking the send primitive. The send and  $receive\ IPC$  primitives in  $\mathbf{LF}$  are called Bang(!) and Hook(?), as in  $\mathbf{CSP}$ . The process Q accepts the message by way of the receive primitive. A communication link must exist which logically connects the receiving and sending processes.

#### 2.3.1 Ports

To send messages, processes must be logically linked to each other. Some means of referencing or naming the other process must therefore exist. Naming may be either direct or indirect. Direct naming requires a communication partner to directly name the other. The send and receive primitives would therefore be defined as follows:

• send(P, message)

• receive(Q, message)

In the above P and Q are the process identifiers for the processes participating in the communication. Direct naming would not work well within the  $\mathbf{LF}$  system as processes are created dynamically. Explicitly referencing a given instance of a process would be cumbersome if not impossible. Each instance of a given process would have to be explicitly referenced. These references need to be resolved by the compiler. As the number of instances is not known at compile time it is unclear how the compiler would be able to resolve the references.

With  $Indirect\ naming\ messages\ are\ sent\ to\ and\ received\ from\ a\ port.$  A port uniquely identifies each link. It therefore functions as a means of access to a common communication link. The port p must be visible to, and is used by, both the sender and receiver. This implies the following notation for send and receive. In this case p refers to a port.

- send(p, message)

- receive(p, message)

In general, the use of ports has the following properties:

- A link is established between a pair of processes only if they share a port.

- Multiple processes may be associated with a single port.

- Processes may be linked by multiple ports.

- Links may be either bi- or uni-directional. In other words a message may be passed in either direction or only one direction over the link respectively.

Indirect naming clearly offers considerable flexibility. The use of ports presents the implementer of the IPC primitives with a number of choices:

#### Multiple receivers

A process P may issue a send command to a given port. This port may for instance have two processes Q and R which use it, both of which execute a receive. The question of which of these two processes should receive the message arises. Note that allowing both processes to receive the message is not an option. Only one process is allowed to receive any given message. Three possible solutions are:

• Allow only two processes to be associated with a given port. One process to *send* and one to *receive*. This circumvents the problem, by removing it by construction. This approach is inflexible for the simple reason that it does not allow multiple receivers of a message.

- Allow only one process to issue a *receive* primitive at a given time. This is cumbersome as runtime checks would have to be performed on each *receive* operation.

- Allow the runtime system to decide. This clearly offers much more flexibility —in terms

of both implementation options and having a non-restrictive language definition— than the

other two options. This is the solution employed in LF. The method also has the distinct

disadvantage of implementation dependence. Therefore no assumptions should be made as

to the recipients of messages. This caveat in my view is far surpassed by the flexibility

offered.

#### Port ownership and process termination

According to Silberschatz and Peterson, ports may be owned either by processes or by the runtime system [25]. Port ownership refers to who has the ability to create and destroy the ports. It was decided to let processes own the ports as this arrangement fitted well into the hierarchical process instantiation scheme. A process may declare a port variable. Such variables may be passed to new instances of processes as parameters. A port variable is a reference to a channel. The parent process has the responsibility of initialising the port by way of the NEW system call. This process is then the owner of the port. Since reference parameters are not allowed, a child process which inadvertently initialises a port which was passed to it as a parameter, only cuts off its own access to the port.

Processes terminate in a bottom-up order. It is therefore impossible for the owner of a port to terminate (and subsequently destroy a port) before its children (which may potentially also use the port) have terminated. It is however possible for a parent process to attempt communication with a child process which has already terminated. This may result in the indefinite suspension of the parent process. References to uninitialised ports result in a runtime exception.

#### Uni- and bi-directionality

LF implements uni-directional communication for a number of reasons. Uni-directional communication is employed by CSP. It is easier to implement than bi-directional communication. Bi-directional links would require additional queueing space as both senders and receivers on a link need to be queued as opposed to either one in the case of uni-directional links. It is unclear to the author when one would benefit from using bi-directional links, apart from perhaps having fewer links. Uni-directional links may be combined to simulate a bi-directional connection in such cases. The use of uni-directional links should also help to avoid some programming errors by forcing the programmer to explicitly state the direction of travel of messages over the link.

## Blocking vs. Non-blocking primitives

The communication primitives may be implemented as either blocking or non-blocking. Blocking primitives enforce synchronous transfer of messages as a process is blocked until its communication partner is ready to send(receive) the message. It has the advantage that it provides for an intrinsic method of synchronising processes. More importantly, there is no need to buffer messages within the runtime system as the message remains in the address space of the sender until another process is ready to accept it. Since a process blocks on the first message sent, no flow control techniques are required.

Non-blocking primitives do not impose synchronisation on the processes. This may lead to a possibly unbounded growth in the length of the message buffer for the relevant channel. Apart from the obvious concerns of running out of memory, large buffers also introduce a response latency as new messages are delayed, as previously buffered messages are cleared. Even when an upper bound is placed on the size of the buffer, once the buffer is full, blocking again needs to be imposed. Asynchronous primitives do however allow a higher degree of parallelism, as processes do not need to wait for their communication partner to receive the message. Blocking primitives are also significantly easier to implement than their non-blocking counterparts [22, 29]. Gehani presents similar arguments to the above in [13]. Blocking primitives are used in systems such as **Amoeba** and **V** [23, 5]. The **LF** system employs blocking primitives.

#### Loss or corruption of messages

When dealing with a distributed implementation of the **LF** system, the occurrence of message loss or corruption is a distinct possibility. For the purposes of the language definition however, a reliable transmission medium is assumed. The choice of reliable transfer protocol is left to the implementer of the runtime system.

## 2.3.2 Reference parameters

Reference parameters are not supported. Value parameters are supported to allow for startup conditions to be set. This allows for some measure of flexibility, without the dangers of reference parameters. The use of reference parameters would require complex mutual exclusion constructs in the runtime system. Furthermore, the implementation of reference parameters on a non-shared memory multiprocessor, would have to be implemented along similar lines to communication over channels. One would then have two syntactic constructs linked to the same runtime implementation. The extra complexity is therefore unwarranted. The functionality of reference parameters is implemented using IPC. Chapter 3 demonstrates how to use communication instead of reference parameters.

```

PROCESS Buffer(IN prod : Chan; OUT cons : Chan);

VAR

buffer : ARRAY 9 OF CHAR;

notFull,notEmpty : BOOLEAN;

in,out : UINT32;

BEGIN

(* initialise *)

WHILE TRUE DO

SELECT

prod ? buffer[in] & notFull THEN

S1

[] cons ? sig(); notEmpty THEN

cons ! buffer[out];

S2

END

END

END

END

END

```

Figure 10: No output guards

#### 2.3.3 Process instantiation

**LF** allows for the dynamic creation of processes (as does **Joyce**[7]). This instantiation may be unbounded(recursive). **CSP** allows only for a fixed number of processes all of which terminate simultaneously. The dynamic instantiation of processes removes the need for indexed processes as in **CSP** and **occam**. Recursion was added with little complexity to the runtime system. The considerable elegance and flexibility of recursion surely justifies the added effort.

## 2.3.4 Polling semantics

The original CSP and occam both restrict polling to input commands [16]. In other words only *Hooks* and no *Bangs* are allowed as part of the guards of a SELECT statement. The occam equivalent of the LF SELECT is the ALT construct. Ada contains the select-accept construct. All of these constructs are based on the CSP general choice operator ('\(^1\)'). This prevents a sender and receiver from polling the same channel at the same time. It was decided in the interest of flexibility and symmetry to allow output polling as well. Furthermore, Hoare states that output guards are 'mathematically possible' within the model of CSP [17]. A classic example of the advantage of allowing output guards in a SELECT is adapted from Raynal [27]. It shows the implementation of a buffer. First without the use of an output guard, and then with the use of one. Notice how in Figure 10 the required output is performed in two stages. Firstly the producer and consumer are synchronised. Secondly the desired output is performed. In Figure 11 an elegant, symmetrical, solution to the same problem, is presented.

Two SELECT statements cannot match. A process executing a SELECT can only match with a

Figure 11: Output guards

process executing an input/output command (a *Bang* or *Hook* command). This is similar to the scheme proposed by Silberschatz [30] and the scheme used in **Joyce**.

A number of 'enhanced' implementations of CSP have been proposed which generalise the SELECT construct. This generalisation allows for output guards and/or the ability for SELECT statements to match. Various protocols have been suggested to implement this functionality, for instance one by Bernstein [6]. Buckley and Silberschatz give an overview of several of these protocols, as well as defining one of their own [8]. Their protocol, albeit one of the more general protocols, was described by Raynal as 'cumbersome and complicated' [27]. The basic problem in the implementation of a generalised input-output construct stems from the possible number of guards that need to be evaluated. Every guard  $G_i$  in a SELECT statement must be compared to every guard  $G_j$  in every other process it references (be it via ports or direct naming). If one factors in the unbounded instantiation supported by LF the problem becomes even more daunting. Moreover, no example could be envisioned in which matching SELECTs would be necessary.

It is the programmer's responsibility to ensure that a SELECT statement is matched by an input/output statement. If this restriction is violated the SELECT statements will **never terminate**, effectively blocking the processes containing it indefinitely and possibly leading to the deadlock of the system as a whole. One might view this as a flaw in the language design, which will lead to many defective programs. However, the security of the system is not compromised and the approach taken is much more efficient than the alternatives. Potential deadlocks are also relatively easy to detect by using a model checker.

LF allows for the specification of a boolean guard in conjunction with the input/output guard. Moreover, the boolean guard is allowed to reference the variables involved in the input/output guard. SR also allows this, but does not allow output guards [4]. Allowing such boolean guards makes the language more expressive. Essentially it allows a process to examine the message to see

whether it wants to accept it. The alternative would be to have the process accept all messages and then re-send them to another process, or implement some sort of buffering scheme if it wishes to use the information in the message at a later stage.

## 2.3.5 Channel sharing

If every channel were to be used by two processes only, a resource process would have to be connected to users by means of a channel array. Reasonable performance is expected from shared channels for 'lightly' used channels. Brinch Hansen presents the same argument in [7]. Fairness problems may however arise for channels carrying large amounts of traffic. A quantifiable definition of light usage as well as the extent of fairness problems which may arise will vary from application to application and remains a topic for investigation.

## 2.4 Security claims

It is claimed that **LF** processes cannot adversely affect each other's address spaces. In conventional programming languages memory interference may occur in the following circumstances:

- Stack overflows are a common cause of corruption in programs. The LF compiler determines the maximum stack depth for a process at compile time and consequently allocates sufficient stack space.

- Shared memory manifests itself in different incarnations:

- The use of global variables are a common cause of software failures. LF (as CSP) does

not allow the use of global variables.

- Reference parameters in the context of concurrent programs are dangerous because they

essentially allow for the aliasing of a variable; allowing multiple processes to change the

same variable without any form of synchronisation.

- LF places severe restrictions on the use of pointers. Pointer arithmetic is disallowed.

Pointers are strongly typed. Pointers may only point to variables i.e. pointers may not be assigned an arbitrary value.

- LF allows for variable instances at specified addresses by way of the AT construct. This construct is also subject to restrictions. Only a single instance of such a variable is allowed. This implies that only one instance of a process instantiating such a variable may be allowed. A runtime check enforces this constraint. The ranges of memory that are available for use by such variables are implementation specific. Such addresses are intended to correspond to those addresses used by memory mapped devices, and should therefore not overlap with the memory used by either process activation records or the runtime system. Compiler and runtime checks enforce this requirement.

| INT8, INT16, INT32  | The signed integer types   |

|---------------------|----------------------------|

| UINT8,UINT16,UINT32 | The unsigned integer types |

| CHAR                | The character type         |

| BOOLEAN             | The boolean type           |

| SET8,SET16,SET32    | The set types              |

Table 1: Predefined types

- Strict index checking is performed on arrays.

- Runtime checks trap references to uninitialised channels, and dereferences of NIL pointers.

As noted, all pointers are initialised to NIL by the compiler, which makes the dereferencing of uninitialised pointers impossible.

- Overflows on arithmetic operations are detected by the runtime system.

#### Additional checks are also performed:

- Runtime checks detect when the system has run out of memory.

- Strict type checking as described in Section 2.2 ensures that variables of different types are not used interchangeably.

In the event of the failure of a runtime check, a machine exception is generated. The exception handler may be defined by the programmer by writing a handler process for the appropriate interrupt. Runtime failures however almost exclusively indicate a serious program error. By default, execution of the system in its entirety is stopped. Note that it is possible to redefine an exception handler that is implemented in the runtime system. This could render the system insecure. It was decided not to make any distinctions between the interrupt handlers that may be defined as this would lead to unnecessary overhead.

# 2.5 Predefined entities and implementational dependencies

LF predefines a number of entities. Foremost of these are the standard types as listed in Table 1.

Sets are generally implemented in one of two ways. Either as having a direct mapping onto a word in the target machine (**Oberon** and **LF**), or having some other arbitrary size. In **Pascal** the size of the set representation is implementation specific. Values typically range from 64 to 2040 members [10]. Compilers generally allow the cardinality of sets to be at least as large as that of the char type [10]. The approach of **Oberon** is efficient as it can make use of specialised machine instructions. A major disadvantage of using sets which are mapped onto a machine word becomes apparent when dealing with hardware devices. In such cases it is convenient to manipulate bits by using sets. More often than not, these bits need to be read(written) from(to) a hardware port. These ports may not have the same number of bits as the machine word. A proliferation of type

```

(* Oberon code *)

VAR

s: CHAR;

BEGIN

PORTIN( 123,s );

IF 1 IN SYSTEM.VAL( SET,s ) THEN

```

Figure 12: Sets in Oberon

```

(* LF code *)

VAR

s: SET8;

BEGIN

PORTIN( 123,s );

IF 1 IN s THEN

```

Figure 13: Sets in LF

casts then appears. The author has observed that failure to type cast the values read from ports in **Oberon** to the correct size has been a consistent source of program failures among novice programmers.

By using sets of differing sizes, **LF** syntactically does away with these type casts. Note that no runtime efficiency is gained as zero extensions of smaller data types to that of a machine word are still needed to use the specialised machine instructions. Figures 12 and 13 compare the usage of sets in the manipulation of hardware ports. Note the use of the SYSTEM.VAL type cast mechanism in the **Oberon** code, which is not needed in **LF**.

The integer and set types are listed in Table 1 as defined for the current implementation (Intel i386). Additional types may be added (for instance in the case of a 64-bit architecture). Similarly the data types used by the predefined procedures may also vary according to the target platform. The set types are intended to evolve in a similar fashion.

As was noted in Section 2.1.3 the array of ports IntChannels, is also predefined with an implementational dependence. This dependence is, however, less intrusive than variations in the size of the machine word.

Two constants **TRUE** and **FALSE** referring to the boolean values are defined. Finally **LF** also predefines a number of routines as listed in Tables 2 to 5.

# 2.6 The LF compiler

The **LF** experimental system generates code in two stages. The first stage is a single pass compiler which accepts the **LF** source code and generates assembly listings as output. A separate assembler

| ORD(a): UINT8               | Returns the ordinal value of character a.                        |

|-----------------------------|------------------------------------------------------------------|

| CHR(a): CHAR                | Returns the character (ASCII) value of ordinal value a.          |

| INC(a,b)                    | Increments an integer variable $a$ (signed or unsigned) by $b$ . |

|                             | Note that both parameters must be signed or both unsigned.       |

| DEC(a,b)                    | Decrements an integer variable $a$ (signed or unsigned) by $b$ . |

|                             | Note that both parameters must be signed or both unsigned.       |

| ABS(a): Signed Integer type | Returns the absolute value of integer variable a. The result is  |

|                             | a signed integer type with the same width as the argument.       |

Table 2: General functions

| INCL(a,b)              | Sets bit number $b$ (unsigned) from set variable $a$ .                      |

|------------------------|-----------------------------------------------------------------------------|

| EXCL(a,b)              | Clears bit number $b$ (unsigned) from set variable $a$ .                    |

| IN(a,b): BOOLEAN       | Check whether bit number $b$ is set within set variable $a$ .               |

|                        | The same sign convention as above applies.                                  |

| SHL(a,b): Integer Type | Performs a left bitwise shift of $b$ (unsigned) bytes for integer variable  |

|                        | a(any sign). The result is of the same type as the $a$ argument.            |

| SHR(a,b): Integer Type | Performs a right bitwise shift of $b$ (unsigned) bytes for integer variable |

|                        | a(any sign). The result is of the same type as the $a$ argument.            |

| AND(a,b): SetType      | Performs the bitwise AND operation on two variables of set types.           |

| OR(a,b): SetType       | Performs the bitwise OR operation on two variables of set types.            |

| XOR(a,b): Set Type     | Performs the bitwise XOR operation on two variables of set types.           |

Table 3: Bitwise functions

| PORTIN(a):     | Integer OR Set Type | Reads a value from hardware port number a.                |

|----------------|---------------------|-----------------------------------------------------------|

| PORTOUT( a,b ) |                     | Writes the Integer OR SET value $b$ to port number $a$ .  |

|                |                     | The number of bytes written depends on the width of $b$ . |

Table 4: I/O functions

| NEW( ptr )         | Creates a new instance of a given pointer or port type.                      |

|--------------------|------------------------------------------------------------------------------|

| DISPOSE( ptr )     | Releases the memory allocated by NEW.                                        |

| MEMFREE(): UINT32  | Returns the amount of free memory.                                           |

| MAXFREE(): UINT32  | Returns the size of the largest contiguous block of heap memory.             |

| NEWDMA( ptr,size ) | Allocated a DMA buffer.                                                      |

| DISPOSEDMA( ptr )  | Releases the buffer allocated by NewDMA.                                     |

| RELEASEDMA( ptr )  | Relinquishes a given amount of memory allocated for DMA to the heap manager. |

Table 5: Heap manager functions

```

PROCEDURE GetReg( VAR r : LONGINT );

VAR i : INTEGER;

BEGIN

WHILE (i < 32) & (i IN regs) DO INC( i ) END;

INCL( regs,i ); r := i

END GetReg;

```

Figure 14: GetReg for rArch

then produces the object code from these listings [32]. This route was taken because it allows the programmer to hand optimise speed critical sections of his code with relative ease. Although this clearly impacts on the security of the code generated, one should bear in mind that this is an experimental system. An optimising compiler falls beyond the scope of this thesis. The use of assembler listings made it possible to experiment with earlier incomplete compiler implementations. This section is intended to give the reader a broad idea of the quality of code generated to place the performance measures that will be presented in Chapter 4 into perspective. Parsing was implemented through standard recursive descent techniques.

## 2.6.1 Code generation

If one considers the fact that this is not an optimising compiler, very reasonable code is produced. The code generation of the compiler is based on a scheme used by Wirth to generate code for a theoretical RISC architecture which I shall call rArch (Chapter 9 of Wirth [35]).

Wirth's scheme was developed for a non-optimising compiler for a subset of **Oberon**. It was therefore a matter of applying the techniques used by Wirth to the Intel *i386* CISC architecture; the target platform. The most important problem that had to be contended with was the scarcity of registers in the *i386*.

The first challenge was therefore to develop a scheme to utilise this limited resource. Since this was not an exercise in compiler design a simple approach was favoured. With *rArch* the compiler designer has 32 general purpose registers at his disposal (R0..R31). This, for instance, allows Wirth the luxury of dedicating a register to contain the value 0.

Wirth uses a very simple method of register allocation. The registers are numbered 0 to 31. When a register is required the first available one is returned by a procedure called GetReg (Figure 14). The variable regs is a globally defined set. The reader will notice that the assumption is made that a free register is always available. This is a valid assumption considering the number of registers and the relative simplicity of expressions encountered in practice. A register is freed whenever its value is no longer needed. Because so few registers are available, no attempt is made to keep frequently referenced variables in registers.

With the i386 four general purpose registers are placed at the disposal of the compiler designer

```

CONST

rEBX=0; rEAX=3; rEDI=4; rESI=5;

PROCEDURE GetAdrReg( VAR r : LONGINT );

VAR i : INTEGER;

BEGIN

i := rEDI;

WHILE (i < rESI+1) & (i IN regs) DO INC( i ) END;

INCL( regs,i ); r := i;

IF i = 4 THEN Halt("Out of registers") END

END GetAdrReg;</pre>

```

Figure 15: GetAdrReg for i386

EAX, EBX, ECX and EDX. Two additional registers are available for indexing (EDI and ESI) <sup>1</sup> Each of the former four registers encapsulates a 16-bit register. For example AX maps onto the lower 16-bits of EAX. Similarly the 16-bit registers encapsulate two 8-bit registers i.e. AL and AH map onto the low order and high order byte of AX <sup>2</sup>. ESI and EDI do not have this sub-division. This forces the compiler designer to only use EAX through EDX for the evaluation of expressions. One may of course go to the trouble of implementing highly specialised code for dealing with 32-bit values only, but the added functionality is hardly worth the effort. The already dire situation is compounded by the highly irregular nature of the *i386* instruction set. The registers EAX and EDX are specifically required for a number of instructions, notably division and multiplication.

The above constraints led to the development of a register allocation mechanism which deviates slightly from that of Wirth's. Two different allocation procedures are used. It was decided to allocate EDI and ESI to store the addresses of variables to which assignments are made, so-called **lvalues** (Figure 15). The basic operation of the algorithm in Figure 15 and Figure 16 entails the following:

The globally defined **regs** is tested for inclusion of the presence of the bit corresponding to the appropriate register. If the register has already been allocated then the bit will be set. If the register is in use then the next register is examined. When a free register is found, the register is reserved by setting the pertinent bit.

Another procedure allocates general purpose registers for the evaluation of expressions (Figure 16). The EAX register is never available for allocation. This leads to a significant reduction in complexity in implementing the instructions which explicitly require this register. The alternative would have been to implement complex register shuffling, possibly augmented with store and load instructions.

The EDX register is allocated last since it is used in most of the instructions which specifically require EAX as well. As the code fragments (Figures [15,16]) indicate the compiler terminates

<sup>&</sup>lt;sup>1</sup>The register ESP is used as the stack pointer and EBP is used to point to activation records.

<sup>&</sup>lt;sup>2</sup>For the sake of brevity the name EAX may be used —depending on the addressing mode— in instances which actually refer to AX or AL

```

PROCEDURE GetReg( VAR r : LONGINT );

VAR i : INTEGER;

BEGIN

i := 0;

WHILE (i < 4) & (i IN regs) DO INC( i ) END;

INCL( regs,i ); r := i;

IF i = 4 THEN Halt("Out of registers") END

END GetReg;</pre>

```

Figure 16: GetReg for i386

```

VAR i : UINT32;

b : UINT8;

BEGIN

i := i+b

:

```

Figure 17: An expression requiring sign extension

execution in the event of running out of registers. This is clearly not an ideal situation. The fact that this is only an experimental version of the compiler and that the scheme works well in most cases is regarded as enough of a justification for the less than optimal implementation. Another simplification made to the register allocation scheme relates to the sub-division of registers. When an 8-bit operand is loaded into a register, the entire 32-bit register is allocated. This simplifies the implementation by virtue of its generality. If the registers were sub-divided in such cases the compiler would have eight more registers at its disposal when processing 8-bit expressions.

Another complication that had to be dealt with was the fact that the *rArch* only implements 32-bit operands (with the exception of the load and store instructions). The *i386* has 8-,16- and 32-bit operands. The compiler must generate type casts when processing expressions containing data types of differing sizes. A simple example of an expression requiring operand extension is presented in Figure 17.

This generates the assembly code shown in Figure 18. Zero- and sign-extensions often lead to the allocation of an additional register. The extension instructions require a register as target

```

LEA EDI,-4[EBP] ; load linear address of 'i'

MOV EBX,-4[EBP] ; load value of 'i' into EBX

MOV CL,-9[EBP] ; load value of 'b' into ECX

MOVZX ECX,CL ; zero extend contents of CL to ECX

ADD EBX,ECX ; add ECX to EBX - result stays in EBX

MOV [EDI],EBX ; store result

```

Figure 18: Sign extension

operand. It is therefore not only good programming practice to avoid mixing data types as much as possible, but may also mean the difference between being able to compile a complex expression or not.

The LF compiler produces labels instead of offsets when emitting control transfer instructions (JUMP,CALL and RET instructions). This makes it significantly easier to alter the resultant assembly listings. Unfortunately this requires a relatively large amount of bookkeeping to keep track of the textual label.

## 2.6.2 Examples of code generated

A few examples of the code generated are now presented. Comparisons are made to the code generated by the **Oberon** compiler for similar structures. One should bear in mind that the Oberon compiler is significantly more complex than the **LF** compiler, and therefore has an advantage when one compares the quality of the code produced. Please note that neither the code to create activation records nor the code to allocate and initialize local variables for either **LF** or **Oberon** is shown.

Code for common loop operations are shown below, in both  ${\bf Oberon}$  (left) and  ${\bf LF}$  (right):

```

PROCESS P;

PROCEDURE P;

VAR

VAR

i : LONGINT;

i : UINT32;

BEGIN

BEGIN

i := 0;

i := 0;

WHILE i < 10 DO

WHILE i < 10 DO

INC( i,1 )

INC(i)

END

END

END P;

END P;

```

27

```

PROCEDURE P

labP0:

LEA EDI, -4 [EBP]

000DH: mov

ebx,0

MOV [EDI], DWORD O

0012H: mov

-4[ebp],ebx

0015H: jmp

9 (0000023H)

001AH: mov

ebx,-4[ebp]

labWHILE1:

MOV EBX, -4 [EBP]

001DH: add

ebx,1

CMP EBX,10

0020H: mov

-4[ebp],ebx

JAE labExitWHILE1

0023H: mov ebx,-4[ebp]

labStatement1:

0026H: cmp

ebx,10

LEA EDI,-4[EBP]

0029Н: jl

-17 (0000001AH)

INC [EDI]

JMP labWHILE1

labExitWHILE1:

```

The reader will notice that the code produced by the **LF** compiler for the above example is virtually identical to that of the **Oberon** compiler.

```

PROCEDURE P;

PROCESS P;

VAR

VAR

i : LONGINT;

i : UINT32;

BEGIN

BEGIN

WHILE TRUE DO

WHILE TRUE DO

INC( i,1 )

INC(i)

END

END

END P;

END P;

labP0:

PROCEDURE P

labWHILE0:

9 (000001BH)

000DH: jmp

labStatement0:

0012H: mov

ebx,-4[ebp]

LEA EDI, -4 [EBP]

0015H: add

ebx,1

0018H: mov

-4[ebp],ebx

INC [EDI]

JMP labWHILEO

001BH: mov

bl,1

labExitWHILE0:

bl,1

001DH: cmp

-16 (00000012H)

0020H: jz

```

In the above example the **LF** compiler actually outperforms the **Oberon** compiler. The **LF** specially optimizes the WHILE TRUE DO construct, as it occurs frequently in **LF** programs.

#### CHAPTER 2. LF: A PROCESS ORIENTED LANGUAGE

```

PROCESS P;

PROCEDURE P;

VAR

VAR

i : UINT32;

i : LONGINT;

BEGIN

BEGIN

i := 0;

i := 0;

IF i = 0 THEN

IF i = 0 THEN

i := 1

i := 1

ELSIF i = 2 THEN

ELSIF i = 2 THEN

i := 3

i := 3

ELSE

ELSE

i := 0

i := 0

END

END

END P;

END P;

labP0:

000DH: mov ebx,0

LEA EDI, -4 [EBP]

0012H: mov -4[ebp], ebx

MOV [EDI], DWORD O

0015H: mov ebx,-4[ebp]

MOV EBX, -4 [EBP]

0018H: cmp ebx,0

CMP EBX,0

001BH: jnz 13 (0000002EH)

JNE labnextGuard1

0021H: mov ebx,1

labStatement1:

0026H: mov -4[ebp],ebx