# High Power LDMOS L-Band Radar Amplifiers

by

Stuart Roderick Arthur McIver

Thesis presented in partial fulfilment of the requirements for the degree of Master of Science in Engineering at Stellenbosch University

Supervisors: Dr C van Niekerk, Prof P.W. Van Der Walt Department of Electrical and Electronic Engineering

# Declaration

By submitting this thesis electronically, I declare that the entirety of the work contained therein is my own, original work, that I am the owner of the copyright thereof (unless to the extent explicitly otherwise stated) and that I have not previously in its entirety or in part submitted it for obtaining any qualification.

March 2010

Copyright © 2010 Stellenbosch University  $\label{eq:copyright} \text{All rights reserved}$

# Abstract

The thesis details the design, construction and experimental evaluation of 30W, 35W and 250W L-Band LDMOS Radar amplifiers. Each amplifier module contains an integrated high speed power supply in order to optimize RF pulse repeatability and to improve radar MTI factor (Moving Target Indication.) As part of the work, a pulsed RF measurement system for measuring the dynamic I-V curves of a power FET was developed. Work was also done on low impedance S-parameter measurement test fixtures for the characterisation of power FETs. These measurement systems generated design information which was used in the development of the L-Band power amplifiers.

# **Opsomming**

Hierdie tesis beskryf die ontwerp, bou en experimentele evaluering van 'n 30W, 35W en 250W L-band LDMOS radarversterker. Elke versterker bevat ook 'n geintegreerde hoë-spoed kragbron om optimum RF pulsherhaalbaarheid te verseker en die radar se 'MTI (Moving Target Indication)' te verbeter. 'n RF-pulsmetingstelsel is ook ontwikkel om die dinamiese I-V kurwes van 'n hoë-krag FET te meet. Verder is daar ook gewerk aan 'n toetsopstelling vir lae-impedansie S-parameters om hoë-krag FETs te karakteriseer. Hierdie toetsopstelling is gebruik om ontwerpsdata te genereer wat gebruik is in die ontwerp van die L-band kragversterkers.

# Table of Contents

| Declaration                                      | i   |

|--------------------------------------------------|-----|

| Abstract                                         | ii  |

| Opsomming                                        | iii |

| Table of Contents                                | iv  |

| List of Figures                                  | vii |

| List of Tables                                   | Xi  |

| Chapter 1 – Introduction                         | 1   |

| 1.1 History of Amplifiers                        | 1   |

| 1.2 Background to Power Amplifier Design         | 1   |

| 1.3 Power Amplifier Design in RADAR Applications | 3   |

| 1.4 Problem Statement                            | 3   |

| 1.5 Investigation Aims                           | 4   |

| 1.6 Thesis Approach                              | 5   |

| Chapter 2 - Pulsed I-V Measurement System Design | 7   |

| 2.1 Introduction                                 | 7   |

| 2.2 System Overview                              | 8   |

| 2.3 Gate Pulser                                  | 9   |

| 2.3.1 Sinusoidal Signal Generation               | 10  |

| 2.3.2 External Signal Relay                      | 13  |

| 2.3.3 Amplitude Variation                        | 13  |

| 2.2.4 Level Detection                            | 14  |

| 2.3.5 DC and Level Addition                      | 15  |

| 2.3.6 Pulse Modulation                           | 16  |

| 2.4 Test Fixture for Power FETS                  | 16  |

| 2.5 Control System                               | 18  |

| 2.7 Calibration                                  | 19  |

| 2.8 Results                                      | 20  |

| 2.9 Recommended System Improvements              | 23  |

| 2.10 Conclusions                                 | 23  |

| Chapter 3 - Advanced Low Impedance TRL Fixture   | 24  |

| 3.1 Introduction                                 | 24  |

| 3.2 Low Impedance TRL design                     | 24  |

| 3.2.1 Klopfenstein Taper Design                  | 24  |

| 3.2.2 Mechanical Fixture Design                  | 26  |

| 3.3 Testing and Validation                       | 32  |

| 3.4 Conclusion                                            | 37 |

|-----------------------------------------------------------|----|

| Chapter 4 - LDMOS Equivalent Circuit Parameter Extraction | 38 |

| 4.1 Introduction                                          | 38 |

| 4.2 LDMOS Package Parameter Extraction                    | 38 |

| 4.3 Extrinsic Parameter Extraction                        | 42 |

| 4.4 Intrinsic Parameter Extraction                        | 46 |

| 4.5 Conclusion                                            | 53 |

| Chapter 5 – Power Supply Design                           | 54 |

| 5.1 Introduction                                          | 54 |

| 5.2 Operating Principals                                  | 54 |

| 5.3 Practical Implementation                              | 55 |

| 5.4 Test and Evaluation                                   | 56 |

| 5.5 Conclusion                                            | 59 |

| Chapter 6 – BLF2045 Amplifier Design                      |    |

| 6.1 Introduction                                          | 60 |

| 6.2 Amplifier Design                                      | 61 |

| 6.2.1 Optimum Load Line placement                         | 61 |

| 6.2.2 Output Network Design to Achieve Power Match        | 62 |

| 6.2.2.1 Output Bias Network Design                        | 62 |

| 6.2.3 Input DC Bias Network Design                        | 66 |

| 6.2.4 Input Matching Network Design                       | 67 |

| 6.3 Results                                               | 70 |

| 6.3.1 Measurement setup                                   | 70 |

| 6.4 Conclusion                                            | 76 |

| Chapter 7 – BLL1214-35 RADAR Amplifier Design             | 7′ |

| 7.1 Introduction                                          | 77 |

| 7.2 Design                                                | 78 |

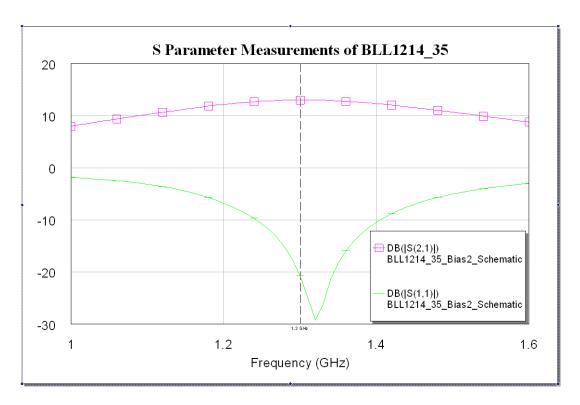

| 7.2.1 S-Parameter Measurement                             | 78 |

| 7.2.2 Output DC Bias Network Design                       | 78 |

| 7.2.3 Output Impedance Matching Network Design            | 79 |

| 7.2.4 Input DC Bias Network Design                        | 80 |

| 7.2.5 Input Impedance Matching Network Design             | 80 |

| 7.3 Measurement Setup                                     | 83 |

| 7.4 Results                                               | 84 |

| 7.4.1 Recommendations                                     | 88 |

| 7.5 Conclusion                                            | 89 |

| Chapter 8 – BLL1214-250 RADAR Amplifier Design            | Qı |

| 8.1 Introduction.                              | 90  |

|------------------------------------------------|-----|

| 8.2 Design                                     | 91  |

| 8.2.1 S-Parameter Measurement                  | 91  |

| 8.2.2 Output DC Bias Network Design            | 91  |

| 8.2.3 Output Impedance Matching Network Design | 91  |

| 8.2.4 Input DC Bias Network Design             | 92  |

| 8.2.5 Input Impedance Matching Network Design  | 93  |

| 8.3 Measurement Setup                          | 96  |

| 8.4 Results                                    | 98  |

| 8.4.1 Recommendations                          | 103 |

| 8.5 Conclusion                                 | 104 |

| Chapter 9 – General Conclusion                 | 109 |

| 9.1 Conclusion                                 | 109 |

| 9.2 Recommendations                            | 110 |

| Bibliography                                   | 111 |

# List of Figures

| Figure 1 - Layout of a typical cascaded power amplifier system which includes driver amplifiers, main power                 | r    |

|-----------------------------------------------------------------------------------------------------------------------------|------|

| amplifiers as well as splitters, combiners, circulators and high power 50 Ohm terminations used to dissipate                | any  |

| reflected power.                                                                                                            | 4    |

| Figure 2 - Diagram showing the approach to the thesis. The diagram shows the steps required to design the thesis.           | hree |

| amplifiers as well as the flow of information generated by the stages.                                                      | 5    |

| Figure 3 - A figure showing an example of a pulsed sinusoidal signal applied to the gate of the DUT in order                | r to |

| generate the required I-V curves. The signal shows gate voltage against time                                                | 8    |

| Figure 4 - A figure showing pulsed measurement system overview including the control equipment needed to                    | .О   |

| automate the measurement.                                                                                                   | 9    |

| Figure 5 – Figure full schematic of gate pulser system                                                                      | 11   |

| Figure 6 - Figure showing the schematic of active diode full-wave rectifier                                                 | 15   |

| Figure 7 - Figure showing final Pulsed I-V measurement setup                                                                | 16   |

| Figure 8 - Figure of gate driver block and DUT fixture block                                                                | 17   |

| Figure 9 - Photo of fixture assembly shown in two separate sections. The section on the left shows the pulsed               | d I- |

| V signal generation circuit. The section on the right shows the gate driver amplifiers attached to the power F              | ΈT   |

| test fixture                                                                                                                | 18   |

| Figure 10 - Figure showing schematic of the control system.                                                                 | 19   |

| Figure 11 - Figure showing pulsed RF I-V curve of Silicon Carbide transistor P259_4_T03F3                                   | 20   |

| Figure 12 - Figure showing pulsed DC I-V curve of Silicon Carbide transistor P259_4_T03F3                                   | 21   |

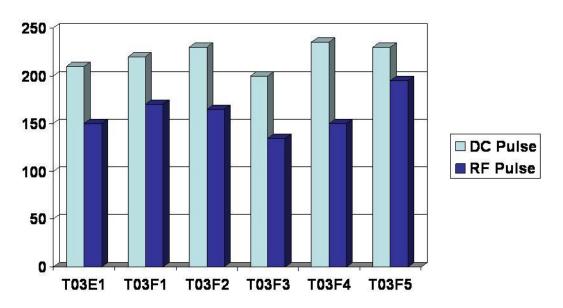

| Figure 13 - Diagram comparing the measured Ids of RF vs. DC pulsed measurements                                             | 21   |

| Figure 14 - Graph showing pulsed RF I-V curves for BLF2045 LDMOS device                                                     | 22   |

| Figure 15 - Graph showing DC I-V curves for various $V_{GS}$ of the BLF2045 LDMOS device                                    | 22   |

| Figure 16 - Figure Showing Klopfenstein Taper Profile of BLF2045 and BLL1214-35 measurement fixtures                        | ;    |

| including mounting holes for screws.                                                                                        | 25   |

| Figure 17 - Figure showing the coaxial to microstrip conversion including the dimensioning of the coaxial to                | )    |

| microstrip transition implemented in order to maintain a 50 $\Omega$ impedance.                                             | 27   |

| Figure 18 - Figure showing approximation of the cross section of a waveguide channel at coaxial-microstrip                  |      |

| transition                                                                                                                  | 28   |

| Figure 19 - Figure showing the design plan of the calibration standards as well as their launch lines and                   |      |

| calibration planes.                                                                                                         | 28   |

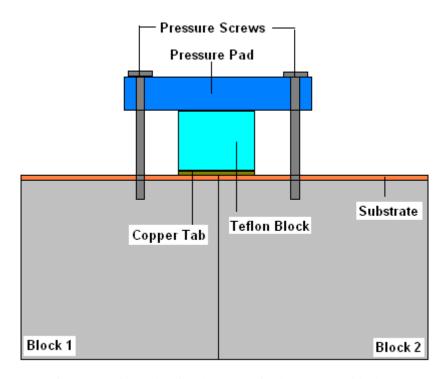

| Figure 20 - Figure showing the cross section of the DUT fixture block                                                       | 30   |

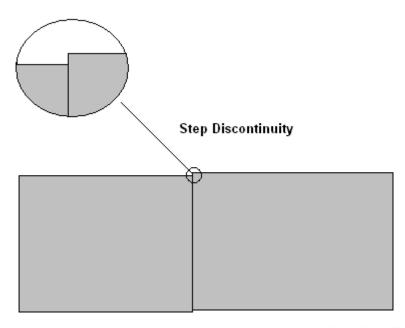

| Figure 21 - Figure showing the possible step discontinuity in the ground surface of two fixture blocks                      | 31   |

| Figure 22 - Figure showing the connection between two blocks                                                                | 31   |

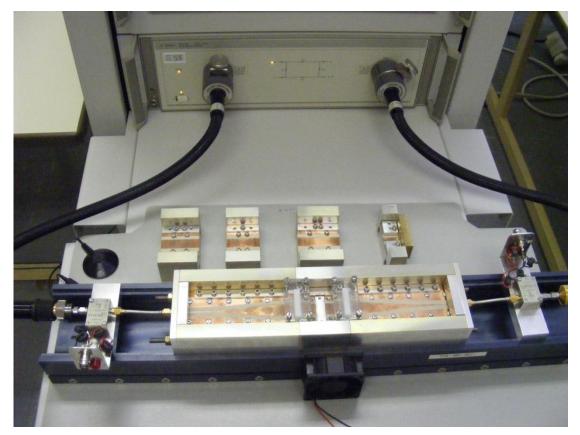

| Figure 23 - Figure showing the final Low-Impedance Test Fixture including calibration standards                             | 32   |

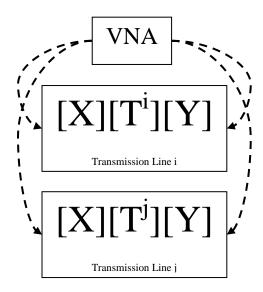

| Figure 24 – Figure showing the representation of the low impedance TRL validation system. Two transmissi                    | ion  |

| lines are represented. The un-calibrated VNA, cable and fixture errors are represented by the matrixes $\boldsymbol{X}$ and | d Y. |

| The transmission lines are represented by matrixes $T^i$ and $T^j$                                                          | 33   |

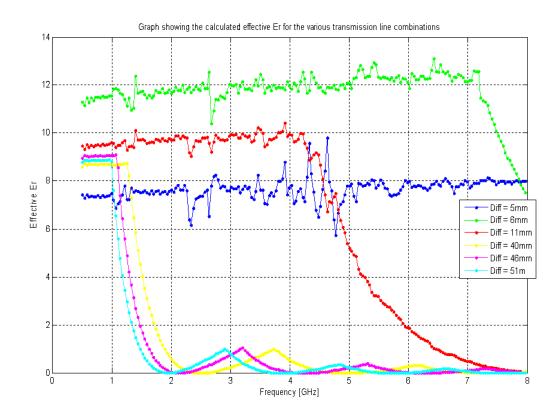

| Figure 25 - Graph showing effective $\epsilon_{r}$ as well as areas of validity and variation due to length differences for | the  |

| various transmission line combinations                                                                                      | 36   |

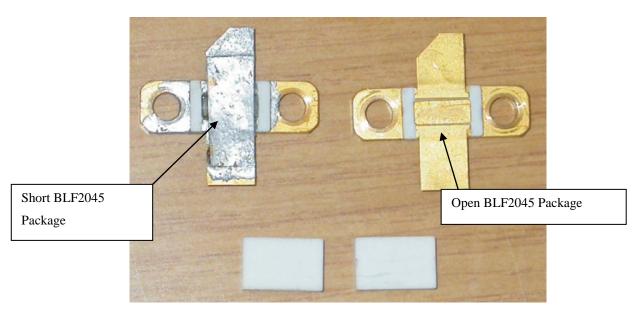

| Figure 26 - Figure showing the open and "short-all" packages of the BLF2045                                     | 39     |

|-----------------------------------------------------------------------------------------------------------------|--------|

| Figure 27 - Figure showing the open standard BLL1214-35 model                                                   | 39     |

| Figure 28 - Figure showing the 'short-all' standard BLL1214-35 model                                            | 40     |

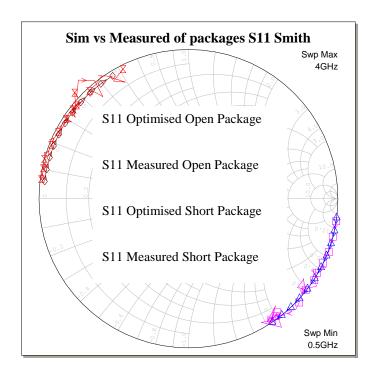

| Figure 29 - Figure showing the Smith chart of the measured vs. the simulated S11 data of the open and short     |        |

| standards                                                                                                       | 41     |

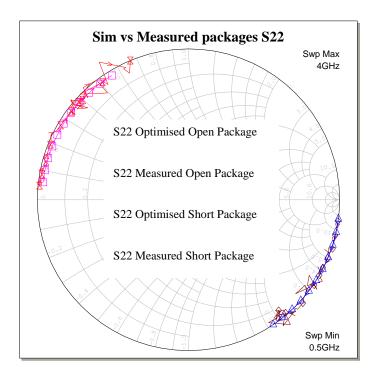

| Figure 30 - Figure showing the Smith chart of the measured vs. the simulated S22 data of the open and 'short    | t-all' |

| standards                                                                                                       | 41     |

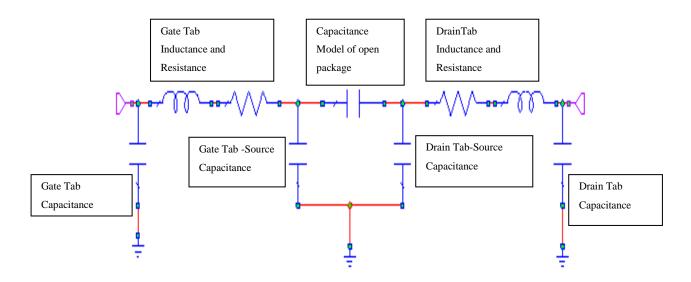

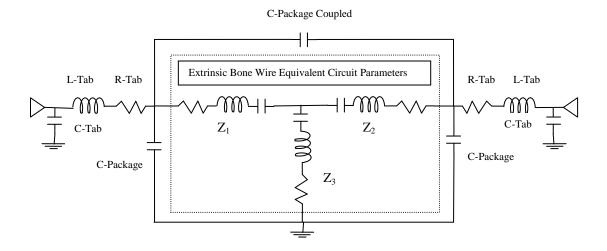

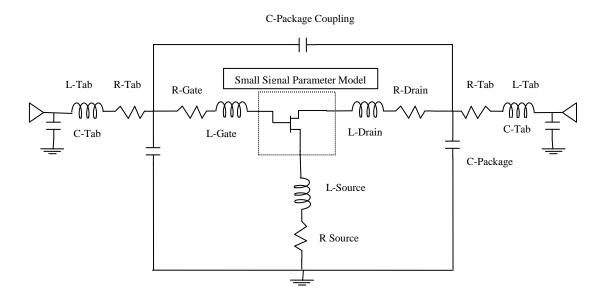

| Figure 31 - Figure showing the model of both the package parameters and the extrinsic bond wire parameters      | s of   |

| a BLF2045 transistor. This model is used for calculations but not to represent the device.                      | 43     |

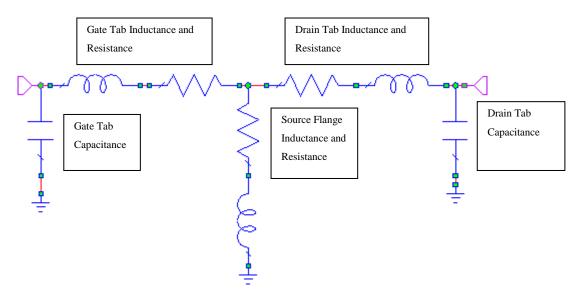

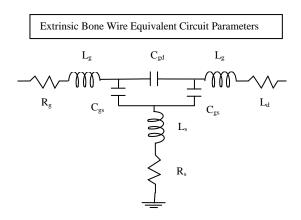

| Figure 32 - Figure showing the model of both the package parameters and the extrinsic bond wire parameters      | s of   |

| a BLF2045 transistor. This model is used for calculations but not to represent the device.                      | 44     |

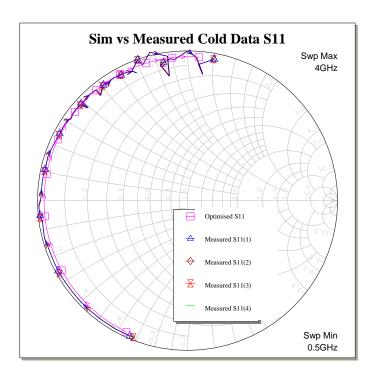

| Figure 33 - Figure showing the S11 of the cold data measurement vs. the model measurements for the BLF20        | .045   |

| device                                                                                                          | 44     |

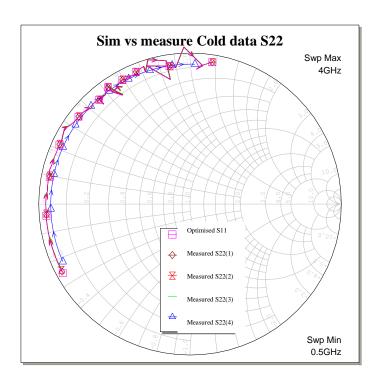

| Figure 34 - Figure showing the S22 of the cold data measurement vs. the model measurements for the BLF20        | .045   |

| device                                                                                                          | 45     |

| Figure 35 - Figure showing the intrinsic small signal device model within the extrinsic and package elements    | s.     |

| The bond wire capacitances are included in the small signal device model.                                       | 47     |

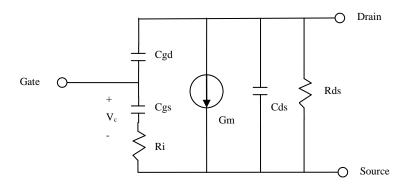

| Figure 36 - Figure showing the intrinsic small signal parameter model                                           | 47     |

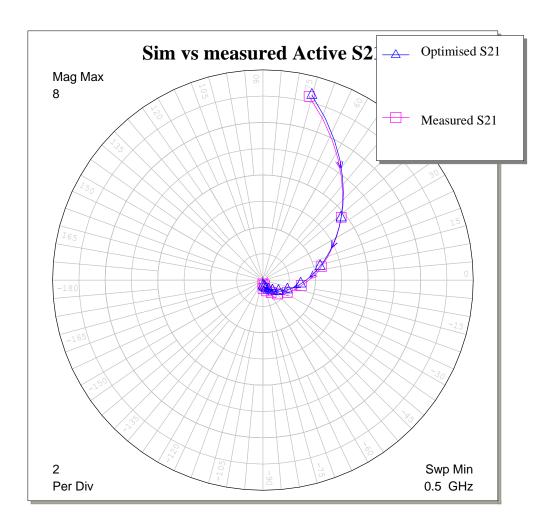

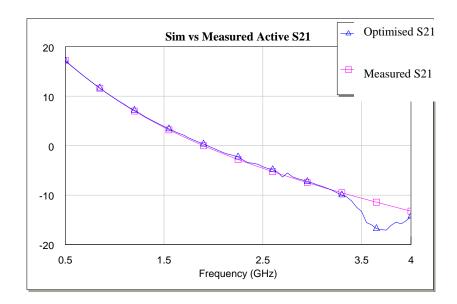

| Figure 37 - Figure showing the measured S21 of the BLF2045 vs. the optimised model response                     | 49     |

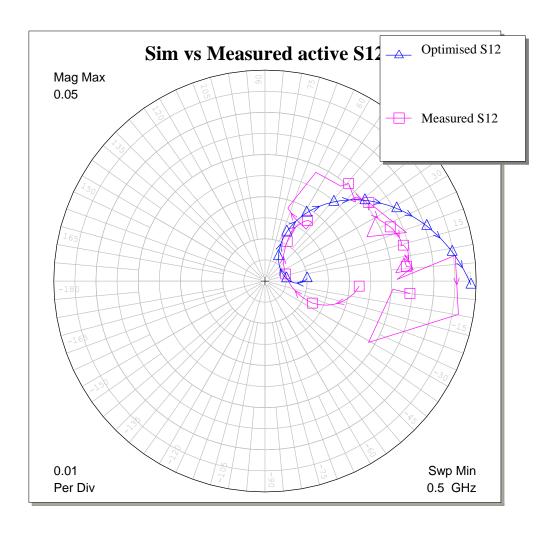

| Figure 38 - showing the measured S12 of the BLF2045 vs. the optimised model response                            | 50     |

| Figure 39 - showing the measured magnitude of the S21 of the BLF2045 vs. the optimised model response           | 51     |

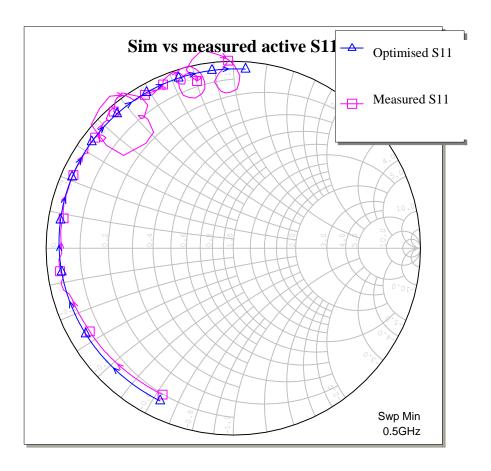

| Figure 40 - showing the measured input reflection S11 of the BLF2045 vs. the optimised model response           | 51     |

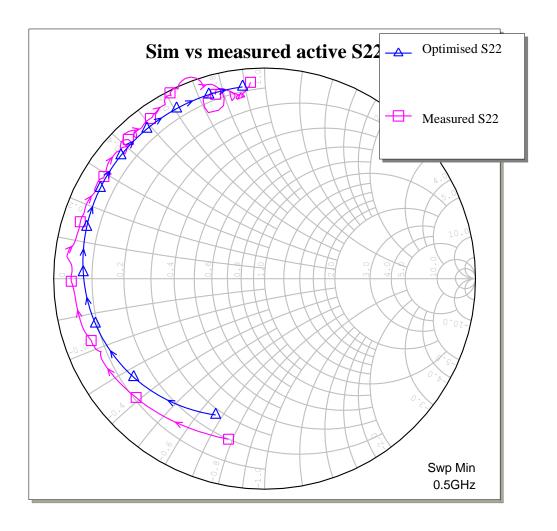

| $Figure~41-showing~the~measured~output~reflection~S22~of~the~BLF2045~vs.~the~optimised~model~response~\dots \\$ | 52     |

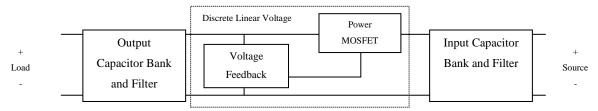

| Figure 42 - Block Diagram of pulsed power supply                                                                | 54     |

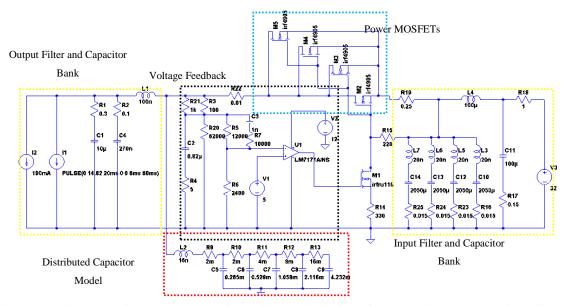

| Figure 43 - Figure showing model schematic used in the simulation of the pulsed power supply including the      | e      |

| distributed capacitor model used to predict the pulsed response of the power supply                             | 55     |

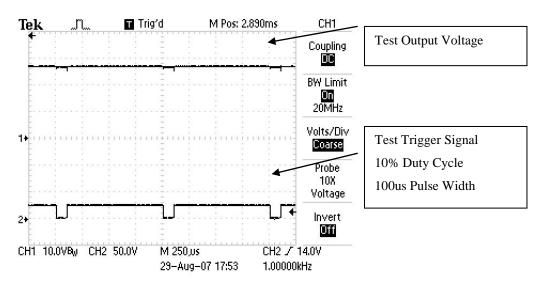

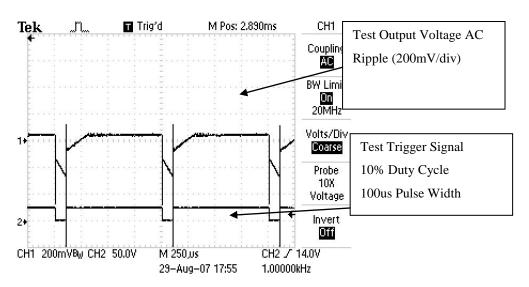

| Figure 44 - Figure showing output voltage of power supply during initial tests at the maximum specifications    | s of   |

| 10% duty cycle and 100us pulse length                                                                           | 57     |

| Figure 45 - Figure showing power supply AC ripple during initial tests at the maximum specifications of 109     | %      |

| duty cycle and 100us pulse length.                                                                              | 57     |

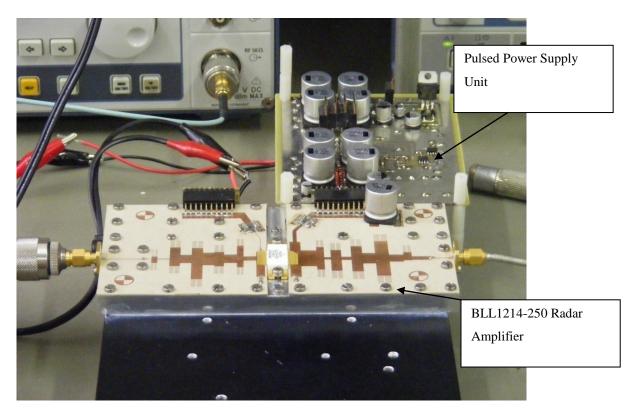

| Figure 46 - Figure showing the power supply connected to the BLL1214-250 250W amplifier used in the fin         | ıal    |

| power supply evaluation.                                                                                        | 58     |

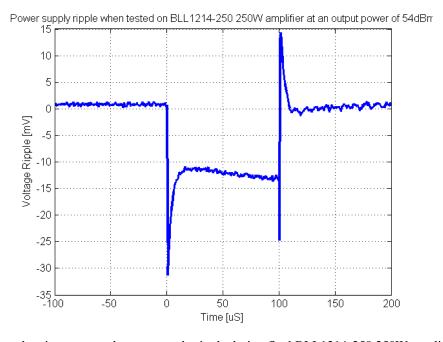

| Figure 47 - Figure showing measured power supply ripple during final BLL1214-250 250W amplifier operate         | tion   |

| at output power of +-54dBm at a 10% duty cycle.                                                                 | 58     |

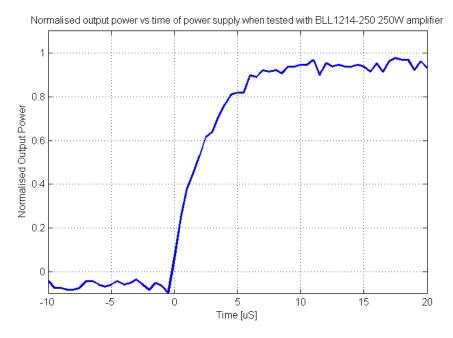

| Figure 48 - Figure showing the normalised power output of the BLL1214-250 250W amplifier, indicating the        | .e     |

| power supply's ability to rapidly supply current to the amplifier.                                              | 59     |

| Figure 49 - Figure showing the pulsed I-V curve and load line placement                                         | 61     |

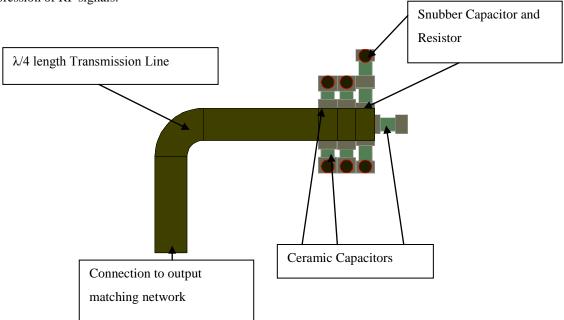

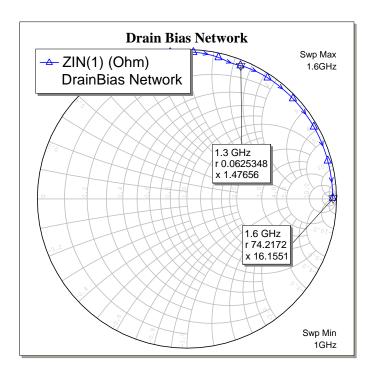

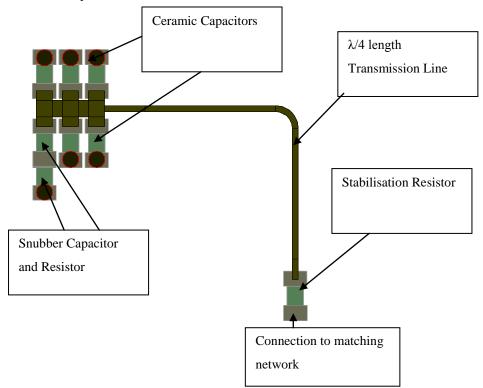

| Figure 50 - Figure showing the model layout of the output DC bias network                                       | 62     |

| Figure 51 - Figure showing the smith chart of the output DC bias network                                        | 63     |

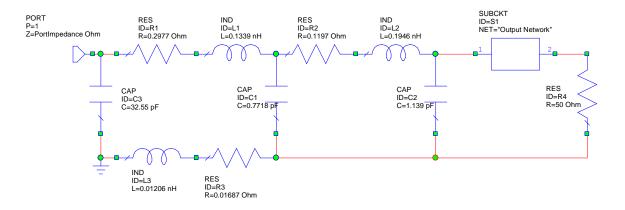

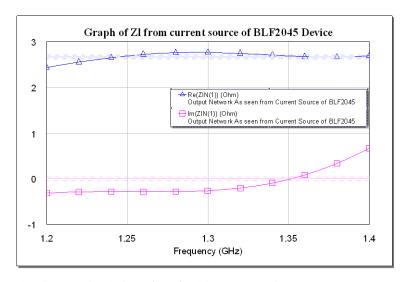

| Figure 52 - Figure showing the schematic of the load as seen from the current source within the BLF2045        |        |

|----------------------------------------------------------------------------------------------------------------|--------|

| including the output matching network which takes the DC bias network into account                             | 63     |

| Figure 53 - Figure showing the simulation of the final load as seen from the current source after optimisation | ı . 65 |

| Figure 54 - Figure showing the final output matching network of the BLF2045 amplifier including the DC by      | ias    |

| network, the impedance transformation network and the DC de-coupling capacitor                                 | 65     |

| Figure 55 - Figure showing the design of the output DC bias network                                            | 66     |

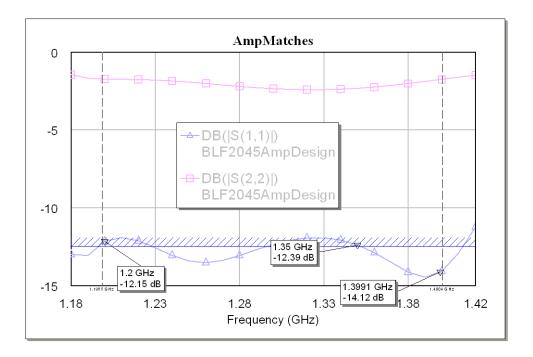

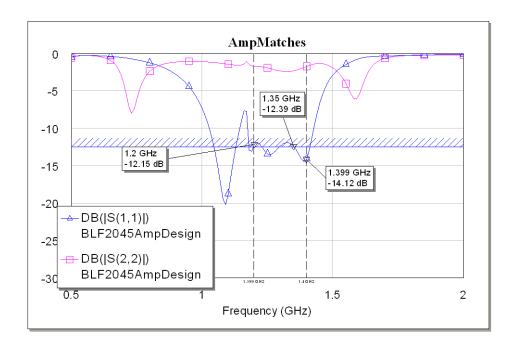

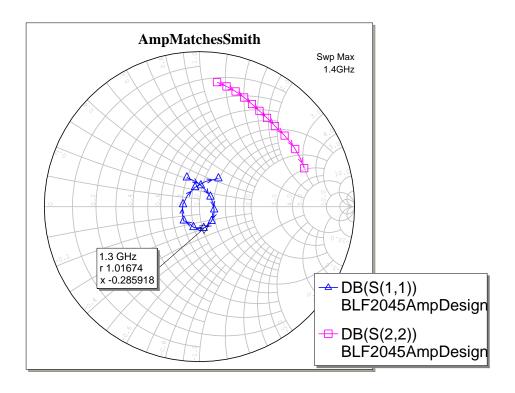

| Figure 56 - Figure showing the final simulated S11 and S22 of the amplifier within the operating L-Band        | 67     |

| Figure 57 - Figure showing the simulated S11 and S22 of the final amplifier over from 0.5-2Ghz                 | 68     |

| Figure 58 - Figure showing the smith chart of S11 and S22 of the final BLF2045 amplifier design                | 68     |

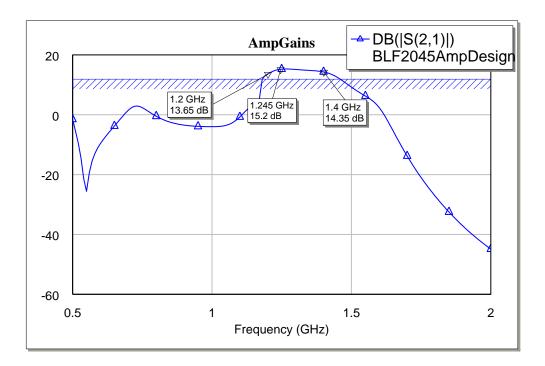

| Figure 59 - Figure showing the simulated S21 of the final BLF2045 amplifier design from 0.5-2GHz               | 69     |

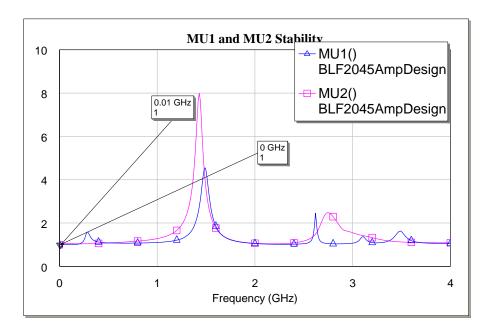

| Figure 60 - Figure showing graphs of μ1 and μ2 stability criteria                                              | 70     |

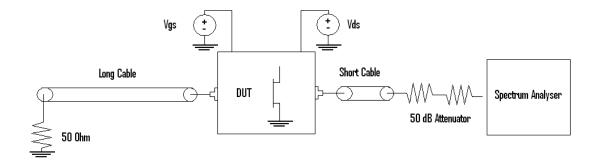

| Figure 61 - Figure showing the setup to test the stability of a DUT                                            | 71     |

| Figure 62 - Figure showing the measured small signal s-parameter S11 measurement of the BLF2045 30W            |        |

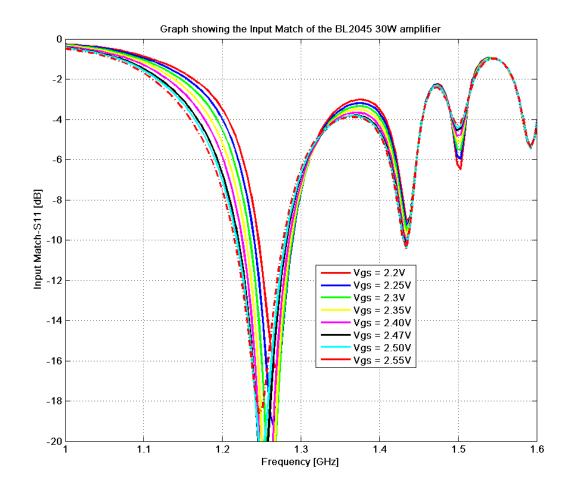

| amplifier                                                                                                      | 72     |

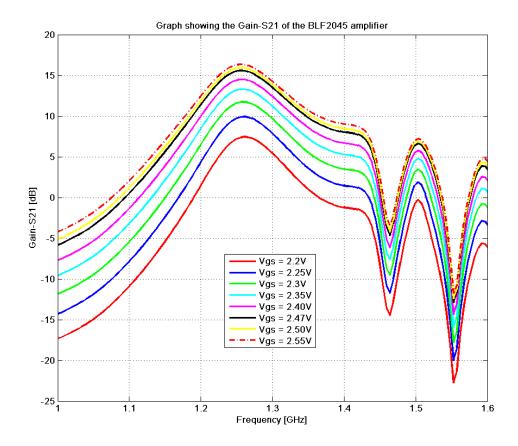

| Figure 63 - Figure showing the measured small signal S21 gain measurement of the BLF2045 30W amplifier         | r.73   |

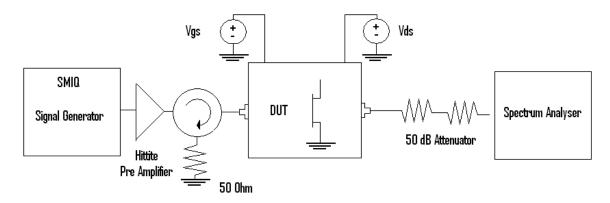

| Figure 64 - Figure showing the equipment setup used to measure the high power response of the BLF2045          | 74     |

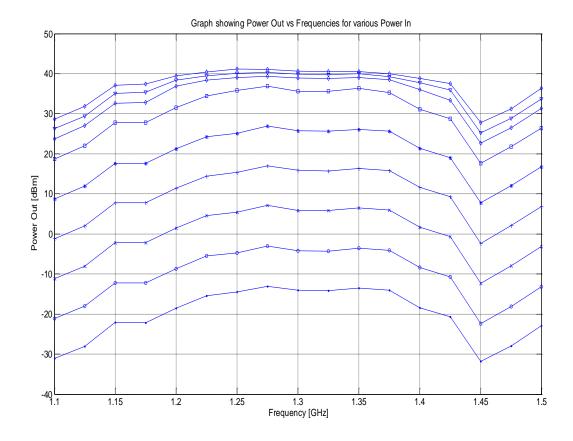

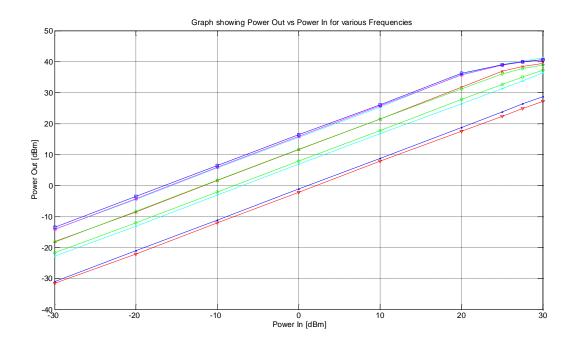

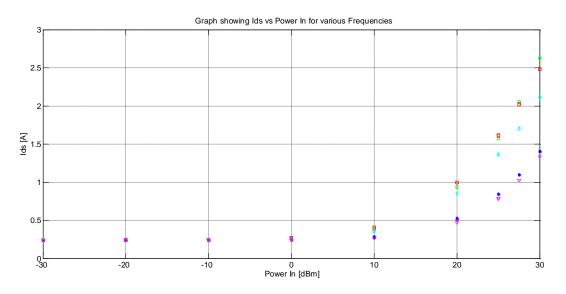

| Figure 65 - Figure showing the measured BLF2045 amplifiers Output Power vs. Frequencies for various Inp        | ut     |

| Powers                                                                                                         | 74     |

| Figure 66 - Figure showing the measured results from the BLF2045 amplifier showing the Output power vs.        | the    |

| Input power for various frequencies                                                                            | 75     |

| Figure 67 - Figure showing the measured results from the BLF2045 amplifier showing the Drain Current (Id       | s)     |

| vs Input Power for various frequencies                                                                         | 75     |

| Figure 68 - Graph Showing S-Parameter Measurement of BLL1214-35 gained from Low Impedance TRL To               | est    |

| Fixture                                                                                                        |        |

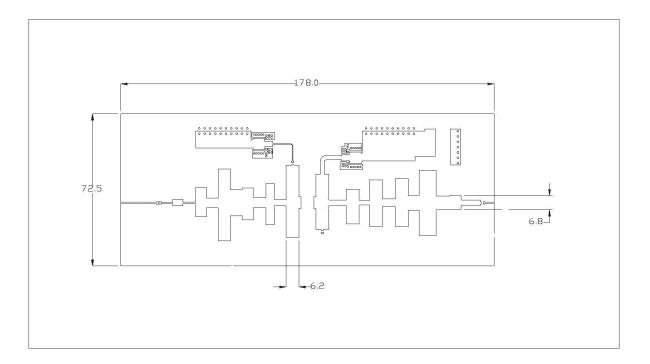

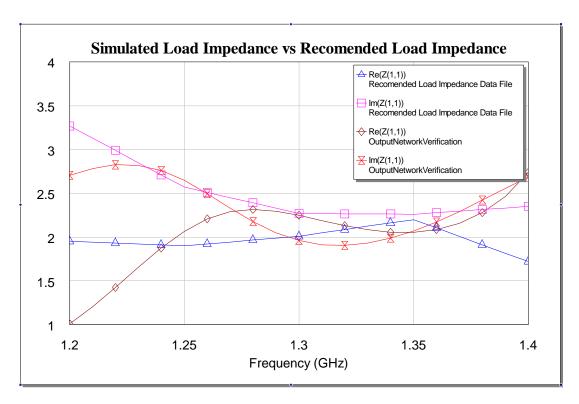

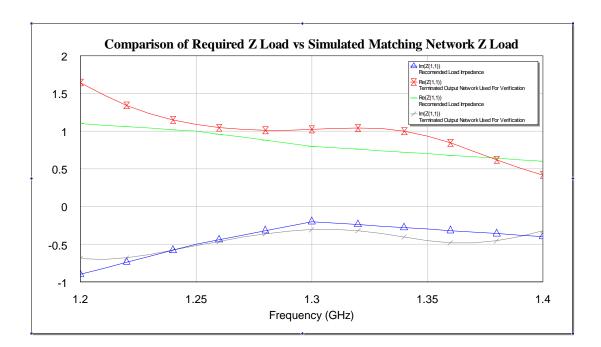

| Figure 69 - Figure Showing Simulated Load Impedance vs. Recommended Load Impedance                             | 80     |

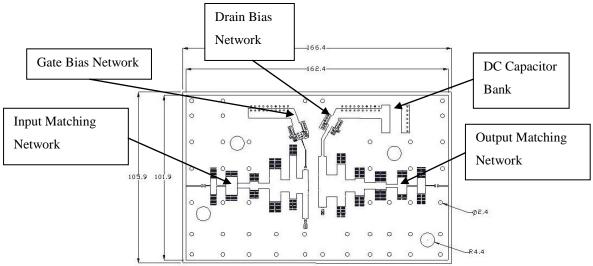

| Figure 70 - Figure showing the final layout of the BLL1214-35 amplifier including both the input and output    | t      |

| matching networks                                                                                              | 81     |

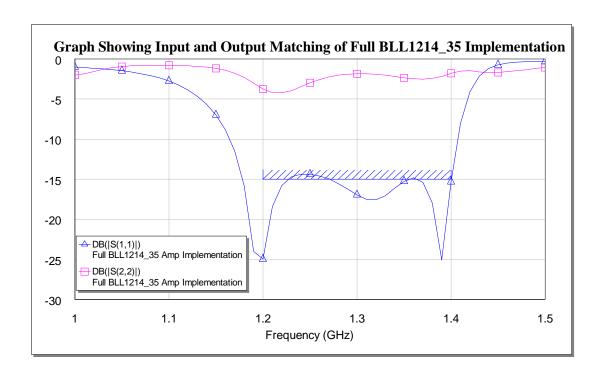

| Figure 71 - Figure Showing Simulated Input and Output Matching of BLL1214-35 35W Amplifier                     | 82     |

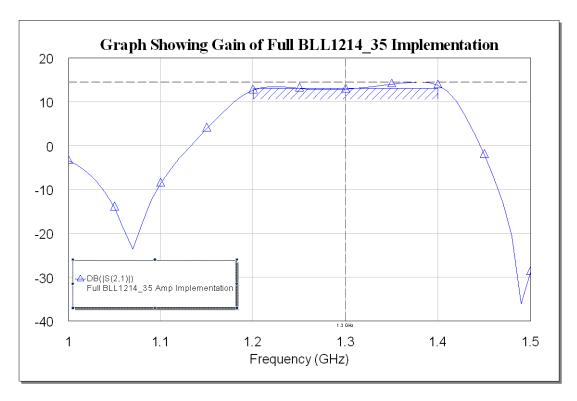

| Figure 72 – Figure showing Simulated Gain (S21) of BLL1214-35 35W Amplifier                                    | 82     |

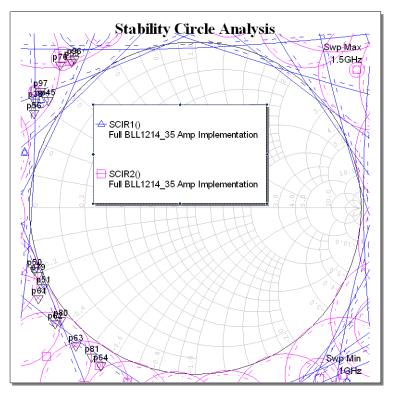

| Figure 73 – Figure showing Simulated Stability Circle Analysis of BLL1214-35 35W Amplifier                     | 83     |

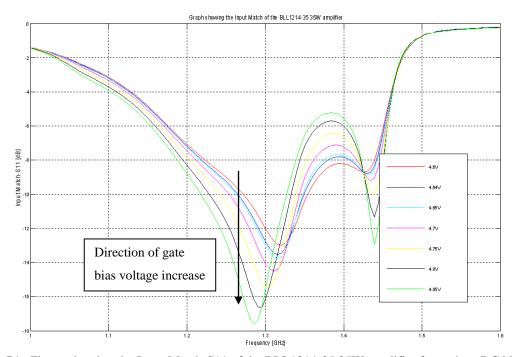

| Figure 74 - Figure showing the Input Match-S11 of the BLL1214-35 35W amplifier for various DC bias points      | nts    |

|                                                                                                                | 84     |

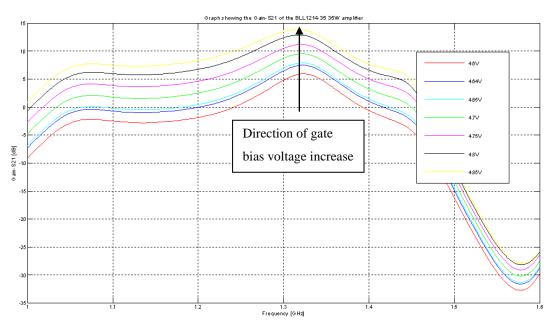

| Figure 75 - Figure showing the Gain-S21 of the BLL1214-35 35W amplifier for various DC bias points             | 85     |

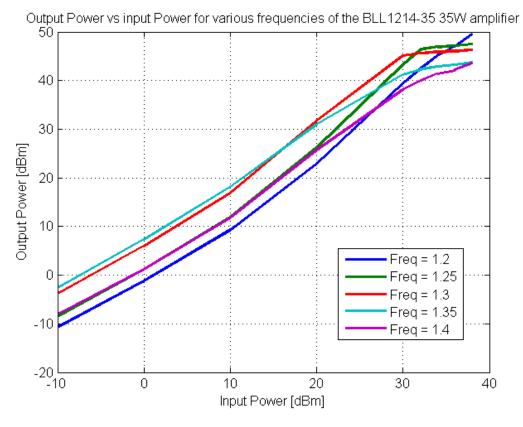

| Figure 76 - Figure showing the output power of the BLL1214-35 35W amplifier with respect to the input po       | wer    |

|                                                                                                                | 85     |

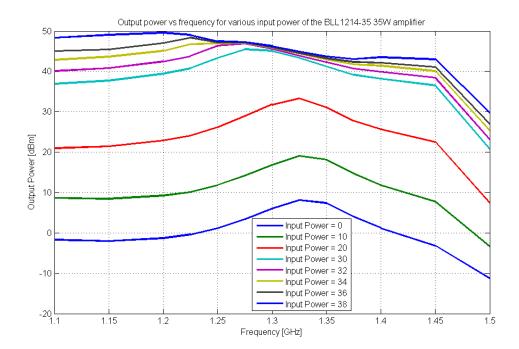

| Figure 77 - Figure showing the Output power of the BLL1214-35 35W amplifier with respect to the frequency      | су     |

|                                                                                                                | 86     |

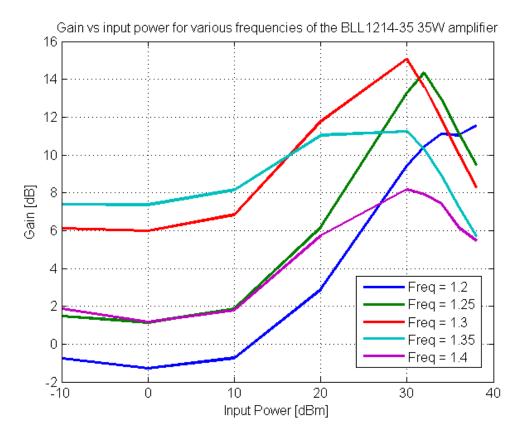

| Figure 78 - Figure showing the gain of the BLL1214-35 35W amplifier with respect to the input power            | 87     |

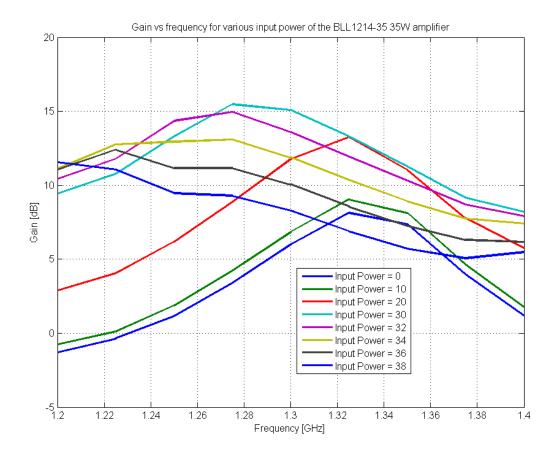

| Figure 79 - Figure showing the gain of the BLL1214-35 35W amplifier with respect to frequency                  | 88     |

| Figure 80 - Graph Showing Comparison between Required Drain Impedance and Simulated Matching N        | etwork   |

|-------------------------------------------------------------------------------------------------------|----------|

| Impedance                                                                                             | 92       |

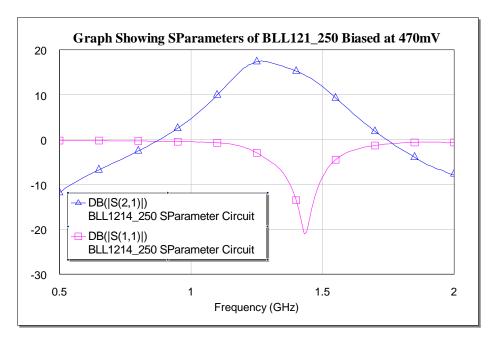

| Figure 81 - Graph Showing S-Parameter Measurement of BLL1214-250 gained from Low Impedance The        | RL Test  |

| Fixture                                                                                               | 93       |

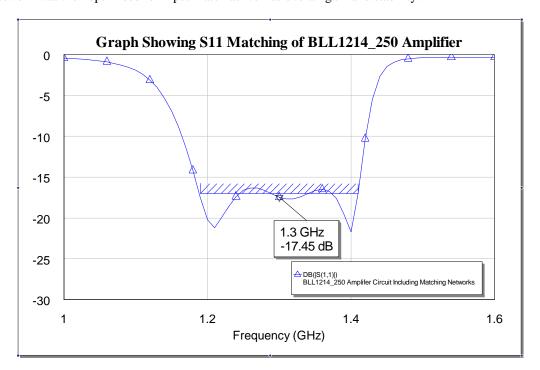

| Figure 82 - Graph showing Simulated Impedance Match of BLL1214-250 Amplifier                          | 94       |

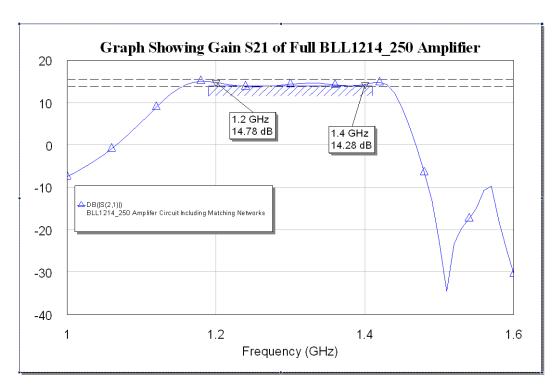

| Figure 83 - Graph showing Simulated S21 Gain of BLL1214-250 Amplifier                                 | 95       |

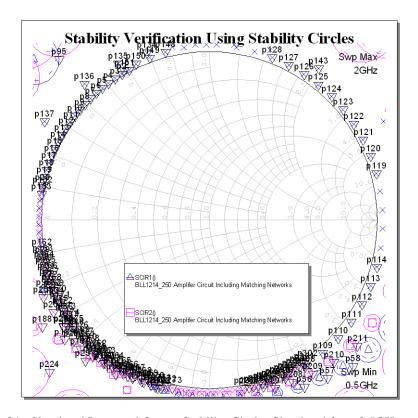

| Figure 84 - Simulated Input and Output Stability Circles Simulated from 0.5GHz to 3GHz                | 95       |

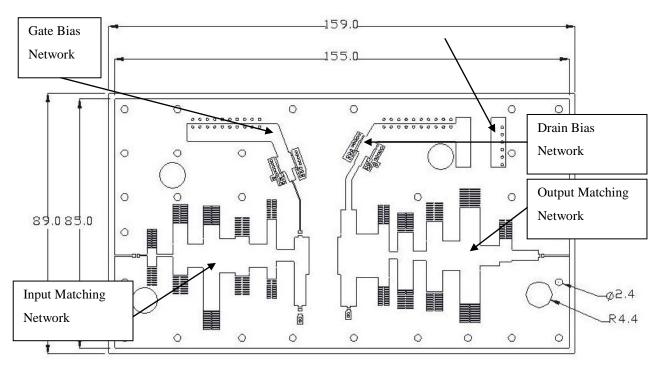

| Figure 85 - Figure showing the layout of the BLL1214-250 250W amplifier including the input and outp  | ut DC    |

| bias networks                                                                                         | 96       |

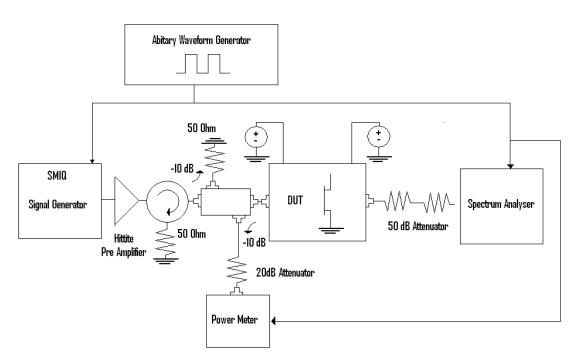

| Figure 86 - Figure showing the high power input match measurement setup                               | 97       |

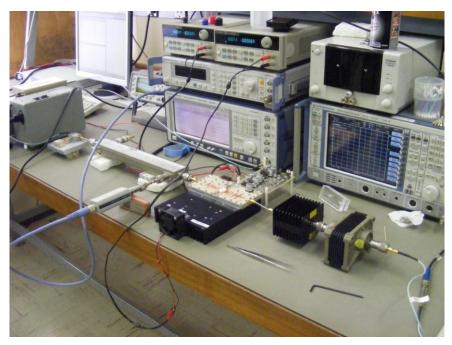

| Figure 87 - Figure showing implementation of high power input match and output power measurement s    | etup .98 |

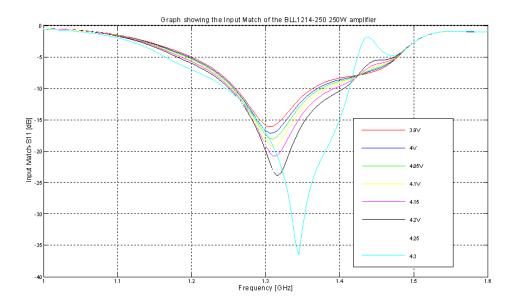

| Figure 88 - Figure showing the initial small signal S11 measurement of the BLL1214-250 250W amplifi   | er98     |

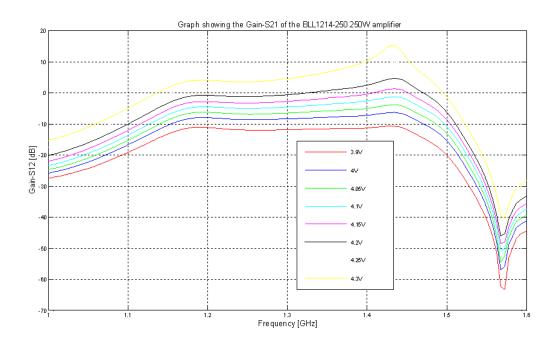

| Figure 89 - Figure showing the initial small signal gain (S21) measurements                           | 99       |

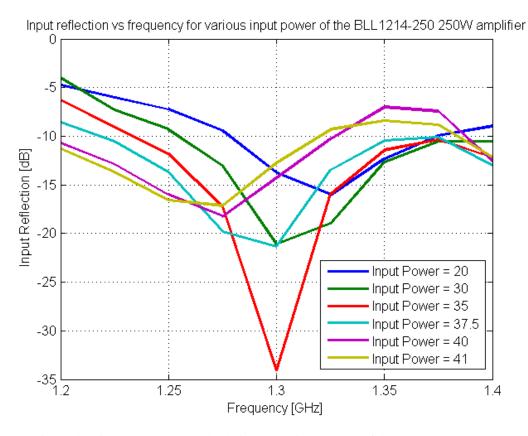

| Figure 90 - Figure showing the measured pulsed high power input match of the BLL1214-250 250W am      | plifier  |

|                                                                                                       | 99       |

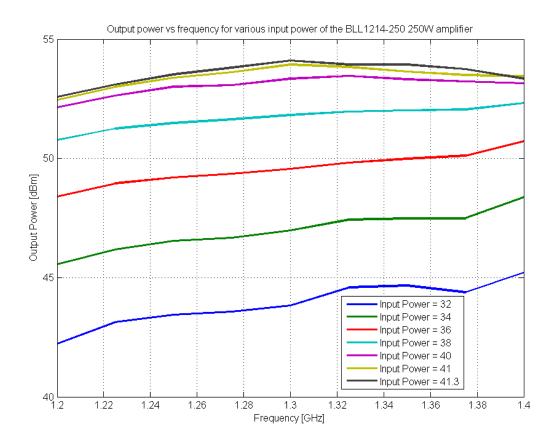

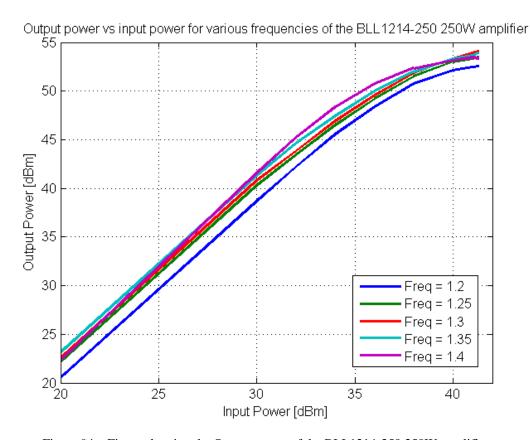

| Figure 91 - Figure showing the Output Power of the BLL1214-250 250W amplifier                         | 100      |

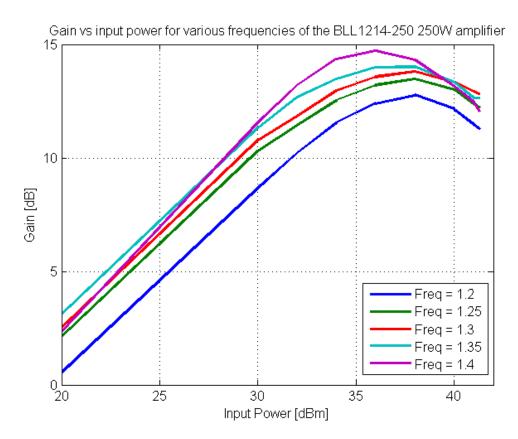

| Figure 92 - Figure showing the gain of the BLL1214-250 250W amplifier with respect to the input power | r 101    |

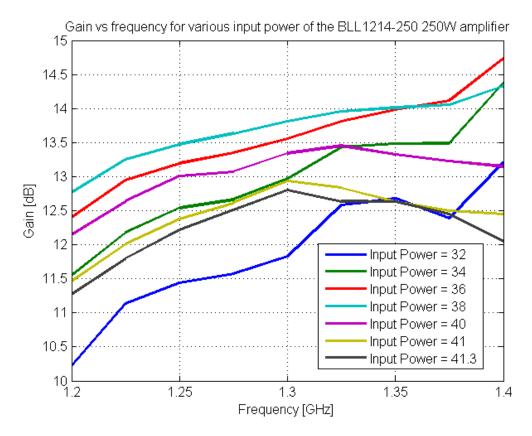

| Figure 93 – Figure showing the gain curve of the BLL1214-250 250W amplifier with respect to frequency | cy 102   |

| Figure 94 – Figure showing the Output power of the BLL1214-250 250W amplifier                         | 103      |

# List of Tables

| Table 1 - Table showing the relative electrical lengths of LINE 1 calibration Standard (12mm)                  | . 29 |

|----------------------------------------------------------------------------------------------------------------|------|

| Table 2 - Table showing the relative electrical lengths of LINE 2 calibration standard (6mm)                   | . 29 |

| Table 3 - Table showing Calculated Er (real) for the various line length differences                           | . 37 |

| Table 4 - Table showing the extracted package parameters vs. the optimised package parameters                  | . 42 |

| Table 5 - Table showing the initial calculated element values of the cold measurements vs. the optimised value | ies  |

| of the corresponding elements                                                                                  | . 46 |

| Table 6 - Table showing the extracted values of the intrinsic parameters of the BLF2045 vs. the optimised      |      |

| intrinsic parameter values for the BLF2045                                                                     | . 53 |

| Table 7 - Table of Manufacturers Specified Input and Output Impedances of BLL1214-35                           | . 79 |

| Table 8 -Table of Manufacturers Specified Input and Output Impedances of BLL1214-250                           | .91  |

# Chapter 1 – Introduction

# 1.1 History of Amplifiers

RF and microwave power amplifiers are widely used in applications such as wireless communications, jamming, imaging, radar and RF heating. Their development began between the late 19<sup>th</sup> century and the mid 1920s. This was with spark, arc and alternator technologies. These technologies were capable of generating up to 5kW at frequencies from LF to MF. With the advent of vacuum tube technology in 1907, a means of electronically generating and controlling RF signals was available. This technology became dominant in the late 1920s and lasted until the mid 1970s. They remain in use even today in some applications as they provide an inexpensive and rugged means of generating over 10kW of power at RF frequencies. Discrete solid state RF power devices began to appear in the 1960's with the introduction of Silicon bipolar transistors (BJT). Following this, in the 1970's, was the introduction of Gallium Arsenide Metal Semiconductor Field Effect Transistors (GaAs MESFET). These allowed solid state to be used in power applications at lower microwave frequencies.

The introduction of solid-state-RF-Power devices facilitated the use of lower voltages, higher currents, and relatively low load resistances. From the late 1980's and 1990's this technology has led to the proliferation of a large variety of new solid state devices such as high electron mobility transistors (HEMT's), pseudomorphic HEMT's, hetero-junction FET's and hetero-junction bipolar transistors (HBT's) from a variety of new materials including Silicon Carbide (SiC), Gallium Nitride (GaN) and others such as InP (Indium Phosphide). With these it was possible to offer amplification at frequencies up to 100GHz or more. [1] [2] [3] [4] [5] [6] [7].

Amplifiers are made up of five basic sections. These are the input and output matching networks, the input and output biasing networks and the transistor itself. In an amplifier design, the actual amplification is performed within the device. But it is the design of the matching and biasing networks that pose the greatest challenge for the designer. The biasing networks, both input and output, ensure that the transistor device has the correct DC bias point. They also supply the device with the energy required to provide the necessary amplification. The input matching network ensures that the power supplied to the amplifier is actually transferred to the device and not reflected back to the source. The output matching network ensures that the device "sees" the correct load at its terminals as well as ensuring that the power delivered by the amplifier is absorbed by the load [8].

# 1.2 Background to Power Amplifier Design

In general power amplifier design theory, the method of using a conjugate match of the external networks connected to the input and output of the transistor devices, would seem to suffice. In practical situations this does not take into account the limitations of the devices. To utilize the maximum current and voltage swing of

the transistors, a lower value of load resistance is required. This is commonly known as the "load-line match". It is commonly stated that using a load-line match instead of a conjugate match will result in large reflection (VSWR) issues. Practical experience has shown that this is not as large a problem as is sometimes perceived. In a simple load-line matched PA connected to an antenna matched to 50  $\Omega$ , VSWR measurements have shown that reflected power is entirely a function of the degree of match between the antenna and the 50  $\Omega$  system. The PA, although, does present a reverse mismatch, which could cause a problem in some situations. This can however be solved using an isolator, circulator or balanced configurations of the system. [8]

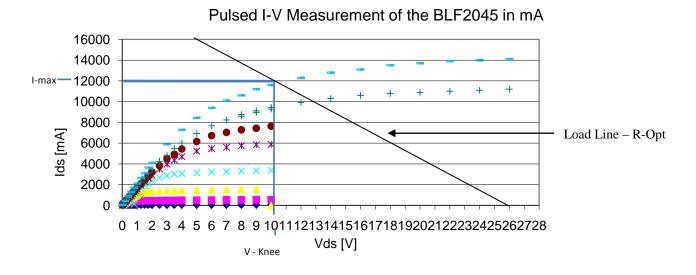

In order to optimally place a load line, measurements of the current-voltage (I-V) curves are required. These I-V curves provide information on the maximum drain-source voltage ( $V_{ds}$ ) and current ( $I_{ds}$ ). Using Cripps's method of load-line matching, along with the measurements of  $V_{ds}$  and  $I_{ds}$ , an optimal load resistance  $R_{opt}$  can be calculated [8].

This method poses a few problems. The main problem it the measurement of I-V curves. Traditional I-V curve measurements make use of DC stimulation of the device under test (DUT) in order to generate the curves. In PA design this poses a serious problem as at higher power the DUT heats up beyond its thermal safe operating area (SOA), and thus attempting to place a load line using this data relies greatly on estimation. A secondary problem is that DC measurements do not show the performance of the DUT under practical RF situations. Using a pulsed RF I-V measurement overcomes this problem by using high frequency DUT stimulation to generate the I-V curves, thus a more accurate optimal load-line placement is possible.

A further issue that requires attention is that of the effect that the DUT package has on the final product's performance. In order to correctly take into account this effect, an accurate package characterization in required. This allows for the incorporation of firstly, the effect of the gate and drain leads, secondly, the effect the bond wires that connect the leads to the transistor die, and finally, the extraction of the intrinsic FET model [9].

A further general PA issue is that of thermal effects. In PA systems where the efficiency is relatively low, the ability of a system to remain thermally stable becomes important. Fluctuations in the temperature of the transistor and surrounding elements can cause large unwanted, unpredictable effects and can even lead to system failure.

Further problems arise when designing a power amplifier (PA). The largest of these is the question of how to accurately characterise a device, such as power transistors, in order to predict behaviour. This would allow for the optimal design of the amplifier. Since measuring total current and total voltage at higher frequencies is difficult, S-parameters are generally used. These allow the behaviour of the power transistor to be characterised in familiar terms such as gain, loss and reflection coefficient. Another advantage of using S-parameters as a design tool is that they can be cascaded in order to get a prediction of the overall performance of a system. They can also be de-embedded from a system measurement in order to gain an understanding of the behaviour of separate sections of the system that are otherwise not available for measurement. With respect to power

amplifier measurement, this allows for the de-embedding of the behaviour of the transistor package, which results in the understanding of the characteristic of the device itself [10].

The S-parameter measurements are not entirely straightforward. These measurements require a test fixture to connect the device to the coaxial-based test equipment. This fixture must facilitate the smooth transition from coaxial to microstrip transmission lines. It must also convert the 50  $\Omega$  based impedances of the network analysers and other measurement systems, to the much lower impedances associated with high power transistors. These two features of the test fixture, along with ensuring that the track widths of the test fixture transmission lines do not differ from the widths of the transistor package tabs, greatly help in reducing the large unwanted discontinuities that may occur during the high frequency S-parameter measurements.

# 1.3 Power Amplifier Design in RADAR Applications

This thesis has, so far in this section, explained some of the general problems that a designer encounters when designing a PA. These problems apply for PA's in the kHz range to PA's that operate in the high GHz range. When designing a PA specifically for the radar bands, further issues become evident.

The first of these issues is cost. Manufacture's of transistors charge very high prices for radar specific transistors. A second issue is the availability of radar transistors. Due to the fact that radar band transistors have obvious military applications, manufacturers might not sell radar band transistors to smaller companies and to companies outside the country of origin. This is both due to loyalty to bigger local companies and to the desire to maintain a military technological advantage.

#### 1.4 Problem Statement

One possible solution, to the issue of cost and availability of devices for RADAR applications, is to use transistors that are designed for other frequencies. These transistors are easily available and in most cases much cheaper. This idea comes with its own problems, mainly that these transistors are pre-matched to other frequency bands. This increases the complexity of the input and output matching circuits that are required for optimal performance.

Designing a PA for a radar band, places greater constraints on the specifications of the system. Firstly, consecutive pulses must be highly repeatable. This allows the system to remove stationary clutter from a radar image. This is especially important when viewing slow moving targets. Secondly, the pulse shape must be stable over a wide variety of pulse lengths, without 'drooping' or fading. The final main constraint is that the PA must be able to operate at wide enough frequencies. This would allow a radar system to be adaptable to different situations, such as different types of scans, improve resolution, as well as facilitating immunity to 'jamming.'

The focus of this work is to approach the problem of RADAR power amplifier design under these constraints.

# 1.5 Investigation Aims

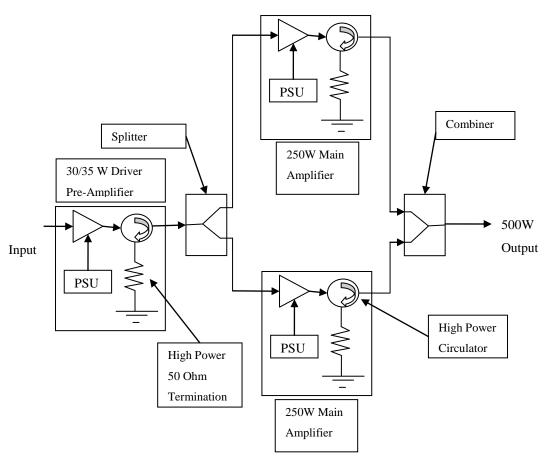

This thesis aims to investigate the development of three separate L-Band RADAR amplifiers using commonly available transistor devices as well as pre-matched military devices. These amplifiers would be combined in a cascade design in order to provide a high gain, high output power RADAR amplifier, as shown in Figure 1. In the investigation of these developments, certain aims need to be considered. Firstly, and most importantly for RADAR amplifier design, is the available output power. It was decided that the designs should, at least, meet the specified output power of the device being used. Secondly, the amplifiers should provide this output power over the specified bandwidth. In this case all three amplifiers need to operate in the L-band, which stretches from 1.2 to 1.4 GHz. Thirdly, the input match of the amplifiers should be below -15dB across the specified band. Finally the gain of the amplifiers should be as flat as possible. A gain variation of less than 3dB was deemed to be acceptable.

A further investigation criterion of the amplifiers is the pulse repeatability as well as the pulse droop.

Figure 1 - Layout of a typical cascaded power amplifier system which includes driver amplifiers, main power amplifiers as well as splitters, combiners, circulators and high power 50 Ohm terminations used to dissipate any reflected power.

# 1.6 Thesis Approach

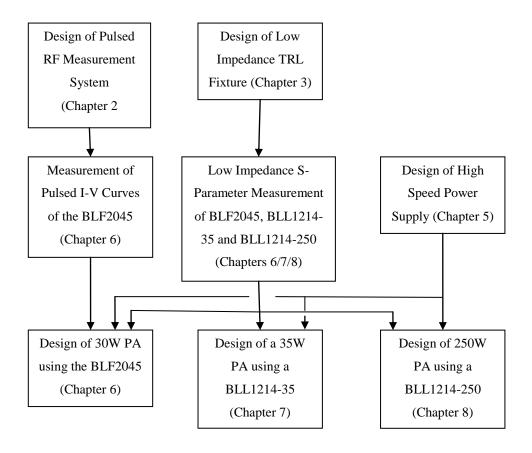

The problem is divided into three sub-problems. The first is the design of the measurement systems used to characterise devices. The second involves the use of these systems to characterise the three devices used. The pulsed RF measurement system for the generation of the pulsed RF I-V curves of the BLF2045, and the low impedance TRL fixture for the measurement of low impedance S-parameters of all three devices. Finally, the information obtained is used to design the three power amplifiers. A peripheral problem that was also addressed was that of a high speed power supply capable of rapid rise time current pulses to the amplifiers while maintaining a very stable voltage at the drain of the device.

Figure 2 - Diagram showing the approach to the thesis. The diagram shows the steps required to design the three amplifiers as well as the flow of information generated by the stages.

This document is divided into eight chapters.

Chapter 2 describes the design of the pulsed I-V measurement system. It will also describe the control of the system, calibration, and results obtained from the various devices.

Chapter 3 describes the design of a low impedance TRL fixture. This chapter also describes the testing procedures as well as the system validation.

Chapter 4 describes the small-signal parameter extraction procedure performed on the BLF2045 device.

Chapter 5 describes the design of a high speed power supply.

Chapter 6 outlines the design of a 30W PA using an unmatched commercial BLF2045 device using results obtained in chapters 2 and 4.

Chapter 7 outlines the design of a 35W PA using a pre-matched BLL1214-35 device. This is an L-band radar specific device, and the design of the PA is mainly used as a comparative tool in the evaluation of the design procedure of the unmatched BLF2045 device.

Chapter 8 outlines the design of a 250W PA using a pre-matched BLL1214-250 device. The design procedure of this PA follows the same lines as the 35W PA described in the previous chapter.

Chapter 9 provides a conclusion to the work. It brings the various ideas together and critically discusses the successes and shortcomings of the design processes and procedures.

# Chapter 2 - Pulsed I-V Measurement System Design

## 2.1 Introduction

When designing any power amplifier, with the exception of those using pre-matched devices, an intricate knowledge of the functioning of the device is required. The approach here uses a pulsed I-V measurement system in order to generate some of the information that can be used in the load line placement that will be described in Chapter 6. It would be appropriate, at this stage, to discuss why a pulsed I-V measurement system is chosen when DC measurements have been sufficient until now.

In order to answer this question, one must examine the shortcomings of the traditional DC measurement scheme as well as the ways in which a pulsed system overcomes these problems.

The main issue with the traditional DC measurement scheme is that it has a very limited safe area of operation (SOA). This is due to the fact that the high voltages and currents result in large self heating of the device, which, if large enough, can result in permanent damage to the device. The pulsed measurement system overcomes this problem by applying a short pulse with a relatively long time between pulses in order to maintain a constant quiescent condition, effectively showing the RF behaviour of the device at an unchanging bias. This allows the testing of the device well beyond the SOA thus providing much needed information of the device at high power operating points.

The second problem with a DC measurement scheme is that that of dispersion. These dispersion effects contribute to large differences between the measured DC curves and the practical HF operation. Various dispersion mechanisms include thermal, rate-dependant and electron trapping phenomena [2]. These mechanisms are usually slow acting, so that a DC stimulus of the device affects them greatly, whereas an HF stimulus does not. These effects are also dependant on the substrate used in manufacturing the devices. Silicone LDMOS transistors are less prone to dispersion effect where as transistors build on other substrates, such as Gallium Arsenide are more so. A pulsed measurement scheme is thus used to acquire characteristic I-V curves that are free of dispersion. The strategy is to maintain a constant quiescent point while measuring the I-V curves. The period between pulses is normally long enough to allow the quiescent condition to recover from any perturbation that may occur during each pulse. Pulsed measurements yield characteristic curves that show a greater correspondence to the RF behaviour of the device than DC I-V curves.

It bears mentioning at this stage, that the pulsed measurement system was utilized to test two different substrates. Initially the system was tested at IMEC in Belgium. There it was used to test Gallium Arsenide and Silicone Carbide 'on-wafer' transistors. This was used as both an initial system verification test as well as an opportunity to obtain data on pulsed RF measurements of non-Silicone transistors. The main test was performed in Stellenbosch, on the Si LDMOS FET mentioned in Chapter 1.

# 2.2 System Overview

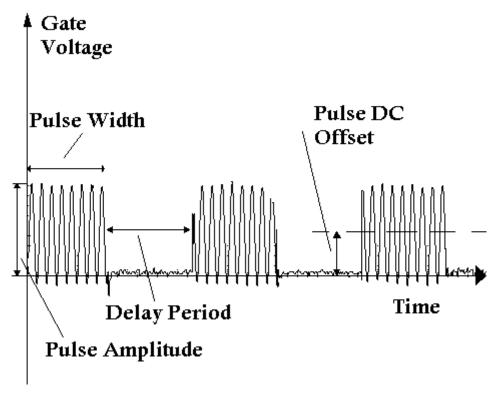

Before going into the specific details of the pulsed measurement system, it would be advisable for one to view the operating principals of the system as a whole, as well as an example of the signals that the system will generate in order to measure the pulsed I-V curves. In the simplest form of the system, a sinusoidal pulse, with a DC offset of 0V, would be applied to the gate of the device under test (DUT). The pulse width as well as the delay between pulses can be arbitrarily chosen. In most cases the pulse width would be in the order of a 10% duty cycle to ensure that self heating does not occur. This gate voltage would cause a current to flow from the drain to the source, with a magnitude dependant on the instantaneous gate voltage. Thus by applying varying gate voltage amplitudes, I-V curves can be established. A further form of the system allows the system to apply a sinusoidal pulse which can be provided with a DC offset within the pulse. Thus the offset can sweep from 0V at the minimum to some arbitrary voltage at the maximum.

Figure 3 - A figure showing an example of a pulsed sinusoidal signal applied to the gate of the DUT in order to generate the required I-V curves. The signal shows gate voltage against time.

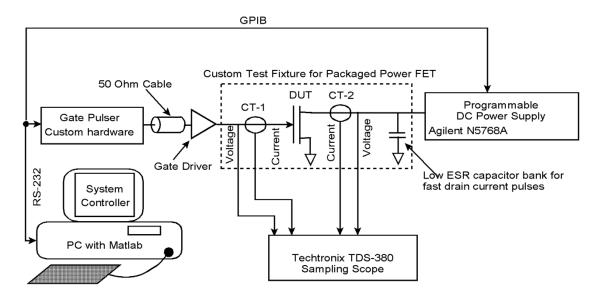

The system is comprised of 4 main sections, namely:

- 1. Gate Pulser hardware.

- 2. Custom Test Fixture for Packaged Devices.

- 3. A Programmable DC power supply at the drain.

- 4. Control System.

#### RF Pulsed I-V Measurement System Prototype

Figure 4 - A figure showing pulsed measurement system overview including the control equipment needed to automate the measurement.

The first section is the gate pulser hardware. This hardware generates the sinusoidal signal, applies the amplitude variation as well as the required DC offset, and modulates the signal.

The second section is the custom test fixture. This allows for the mounting of the specific DUT package, as well as mounting for current and voltage sensors at both the gate and the drain of the DUT. These sensors are measured using a Tektronix TDS-380 oscilloscope. This fixture also allows the DUT to be driven directly at the gate by having a built-in driver in the fixture.

The next section is the programmable drain DC power supply. This section is implemented with an industry standard Agilent N5768A programmable power supply which can be controlled via MATLAB. The final section is the control system. This section involves the use of Microchip demo board which controls various Digital-to-Analogue Converters (DACs) and digital control signals which in turn control the gate pulser hardware. This section also uses MATLAB to control the Microchip demo board as well as the power supplies directly.

## 2.3 Gate Pulser

The gate pulser is the main hardware section of the entire measurement system. In the design of this section the following specifications were kept in mind:

The frequency within the pulse needs to be controllable. Ideally the frequency range must be between 1MHz and 20MHz

There needs to be 40dB range of variable gain in the voltage amplitude of the applied signal. This gain must be from -10dB to +30dB.

The voltage amplitude must have up to 10V of swing. This is required in order to fully test the range of the DUTs.

The pulse width as well as the delay period needs to be variable, as can be seen in Figure 3.

The pulse DC offset must be selectable between three positions:

- 1. Zero Offset The signal swings around 0V without any DC offset

- 2. Positive Offset The signal must swing from a minimum of 0V to the maximum voltage.

- 3. Negative Offset The signal must swing from a maximum of 0V to the minimum voltage.

Provision is made for an external signal for signal generation if necessary.

Keeping these specifications in mind, the pulsar hardware was split into the following sections:

- 1. Sinusoidal Signal Generation

- 2. External Signal Relay

- 3. Amplitude Variation

- 4. Level Detection

- 5. DC and Level Addition

- 6. Signal Modulation

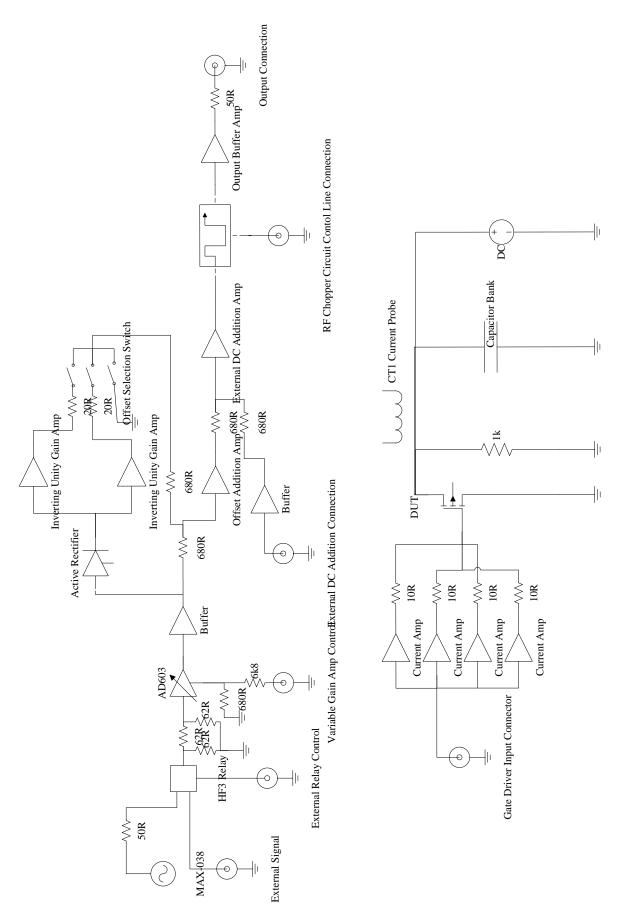

The full system schematic can be seen in Figure 5

#### 2.3.1 Sinusoidal Signal Generation

In order to generate the sinusoidal signal, a Maxim MAX038 high-frequency waveform generator was used. This chip was chosen due to its following properties:

- 1. 0.1Hz 20MHz operating frequency range

- 2. Various waveform types can be created including: triangle, sawtooth, sine, square and pulse. Only the sinusoidal was implemented in this design

- 3. Independent frequency and duty cycle adjustments.

Figure 5 – Figure full schematic of gate pulser system

The first task with the MAX038 is to select the type of wave form. This is done by setting the TTL/CMOS-logic address pins (A0 and A1). Since this hardware will not be switching between different waveforms, it was decided to connect A1 directly to the 5V, and although A0 can be view as 'Don't care' it was decided to connect it to ground for the sake of thoroughness.

The second task is to select the operating frequency of the MAX038. This frequency is determined by the current into  $I_{in}$ , the capacitance  $C_{osc}$  and the voltage on the  $F_{adj}$  pin. Although the original specification of the hardware was to have a variable frequency, it was found that the maximum frequency possible was 6MHz. This was not due to the limitations of the MAX038 but rather due to limitations in the rise times of other components. This issue will be discussed in later in the chapter.

In order to set the centre frequency the following equation is used [11]:

$$Fo(MHz) = Iin(\mu A) \div Cf$$

1

Where:

$F_o$  = Centre Frequency

$I_{in} = Current$  into the  $I_{in}$  pin

$C_{\rm f}$  = Capacitance between the  $C_{\rm osc}$  pin and ground

By examining the data page it was decided that the value of  $C_f = 33$  pF should be used. This would allow the current into the  $I_{in}$  pin when operating at  $F_o = 6$ MHz to be approximately 200uA. The reason for this is that, for optimal performance,  $I_{in}$  should be kept between 10uA and 400uA.

Thus for a centre frequency, Fo, of 6MHz

$$Iin = Fo \times Cf = 198\mu A$$

2

The value of R3 was chosen to be  $6.8K\Omega$ . This allowed the value of  $V_{in}$  to be in the region between 1 and 2V depending on the frequency required.

It can also be seen, from the data page, that the  $I_{\text{in}}$  pin is internally forced to a virtual ground, and thus:

$$V_{in} = I_{in} \times R_3 = 1.334V$$

3

The final task in setting the operating frequency  $F_o$  is to set the voltage on the  $F_{ADJ}$  pin. This pin has a constant 250 $\mu$ A constant current sink that must be furnished by the voltage source. The MAX038 also provides a reference pin (REF) that has a constant, internally supplied voltage of 2.5V.

Thus:

$$R_f = \frac{\left(V_{ref} - V_{fadj}\right)}{250\mu A}$$

4

This resistance  $R_f$  was implemented using a surface-mount multi-turn variable  $20K\Omega$  resistor. Thus the centre frequency  $F_o$  can be fine tuned by tuning the resistor R3.

The duty cycle adjustment pin,  $D_{ADJ}$ , was connected to ground. This is the suggested connection, shown in the data page, when using the MAX038 as a sinusoidal waveform generator. All other pins are connected as suggested in the data page [11]. This includes various DC de-coupling capacitors.

The output impedance is low, thus in order to ensure a 50  $\Omega$  output impedance from the MAX038, two 100  $\Omega$  resistors were placed in parallel at the OUT pin.

#### 2.3.2 External Signal Relay

In order to implement signal selection between the MAX038 and an external signal, an AXICOM HF3 surface-mount relay was used [12].

A voltage control voltage applied across pins 1 and 11 selects the external input. The default state connects the internal input from the MAX38, at pin 20, to output pin 6.

This relay was chosen for two reasons. Firstly the fact that it is surface-mount, and secondly because it has an internal impedance of 50  $\Omega$ .

In order to select the external signal, a TTL/CMOS 5V voltage is applied to pin 1, and to switch back to the MAX038 signal a 0V voltage is applied to the same pin. This signal is supplied by the Microchip control board, and will be discussed later in the chapter.

# 2.3.3 Amplitude Variation

In order to implement the variable gain amplification, an Analogue Devices AD603 [13] variable gain amplifier was chosen. The reasons for this were firstly that it provides a wide (40dB) gain range, and secondly because of its simplicity. It is controlled with a simple voltage difference between two pins.

In order to control the variable gain, a voltage range of -0.5V and +0.5V varies the gain between the minimum and maximum respectively. In order to achieve this, a voltage divider network, from a 5V supply to the GNEG control pin, was implemented. The ratio of R1:R2 was chosen to be 10:1. Thus ensuring that the voltage at the GNEG control pin is a constant 0.5V.

A voltage applied to the GPOS pin that varied between 0V and 1 V would therefore result in the voltage Vg to swing between the desired -0.5V and +0.5V.

It was also found that output from the MAX038 causes the AD603 to saturate too quickly. Thus a 50  $\Omega$  18 dB resistive attenuation Pi-network was placed at the VIN pin to ensure the maximum voltage gain control.

The final stage of the amplitude variation is to amplify the output voltage of the AD603, which is  $\pm 3V$ , to the required  $\pm 10V$ .

In order to implement this gain, a National Semiconductor LM6181 current feedback op amp [14] was chosen. This operational amplifier can provide a high output drive of up to  $\pm 10V$ , and has a high slew rate of  $2000V/\mu s$ .

The LM6181 is a current feed-back op-amp used in a non-inverting set-up. The value of the feedback resistor was chosen to be 820  $\Omega$ . This was at the suggestion of the data page in order to ensure the best performance over all possible applications [14].

Since, the output of the AD603 is  $\pm 3V$  and the required voltage is  $\pm 10V$ , a gain 3.33 is required.

#### 2.3.4 Level Detection

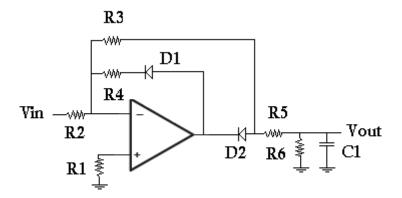

In order to measure the amplitude of the signal, an active full-wave rectification circuit, Figure 6, is used [15]. This circuit is implemented using a Texas Instruments THS4031 voltage feed-back op-amp [16]. This operational amplifier has an output voltage swing of up to  $\pm 13$ V and can drive up to 90mA. Secondly, it has a high slew rate of 100V/ $\mu$ s. The principle of this circuit is that the operational amplifier maintains the bias on the diodes so that they remain on the verge of being on. This increases the accuracy of the circuit over traditional rectification circuits, which do not take the voltage required to switch the diodes 'on' into account.

Figure 6 - Figure showing the schematic of active diode full-wave rectifier

The gain of the active rectifier is set at unity by selecting R3 equal to R2. These two resistors were set at 820  $\Omega$ . R1 is set at R2//R3 thus R1 equals 410  $\Omega$ . R5 is placed in series with the operational amplifier as the output drives a capacitor directly. It is set as 20  $\Omega$  as per suggestion in the data page. The R6 and C1 combination is chosen to set the time constant  $\tau$ .

$$\tau = RC$$

5

With R6 equal to 2K $\Omega$ , and C1 equal to 100nF,  $\tau$  has a value of 0.2ms

This ensures that the ripple voltage on the level detector is small enough to not affect the DC offset of the pulse.

# 2.3.5 DC and Level Addition

This section involves four parts. Firstly, the output of the level detector is buffered with both an inverting and a non-inverting unity amplifier. This provides a both a positive and negative DC voltage that is proportional to the amplitude of the pulse. Next the voltage to be added to the signal in order to provide the desired offset is selected. It can be a positive, negative or zero offset. The next step is to use an addition circuit to add the DC offset. The final stage is to add a precision external DC voltage to the signal in order to compensate for the amplitude and frequency dependant errors in the level detection and amplitude control.

A 20  $\Omega$  resistor is placed at the output of both unity amplifiers. This is in order to ensure that in the possible event that the outputs of the amplifiers are shorted, the circuits are protected.

A LM6181 [14] is selected as the operational amplifiers for the addition amplifiers due to their high speed capabilities.

The feedback resistor in both the additions circuits is again chosen to be 820  $\Omega$ . Gain is provided by both amplifiers to compensate for the voltage division that occurs as a result of the addition circuit.

#### 2.3.6 Pulse Modulation

The modulation circuit was implemented using a Maxim DG413F fault protected, analogue switch. When first implemented, it was found that a single switch did not provide enough isolation between the input and output. Thus it was decided to use a cascade design in order to increase the isolation.

A single control line is used to operate all the switches simultaneously. A problem could occur if the series switches switch on before the parallel switches switch off, thus effectively shorting the circuit down to ground. This is prevented by the break before make feature of the DG413F. The output of the switch circuit is then buffered using a LM6181 operational amplifier.

The 50  $\Omega$  series resistor is used to ensure a match to the 50  $\Omega$  cable used to connect the pulse generation hardware to the test fixture.

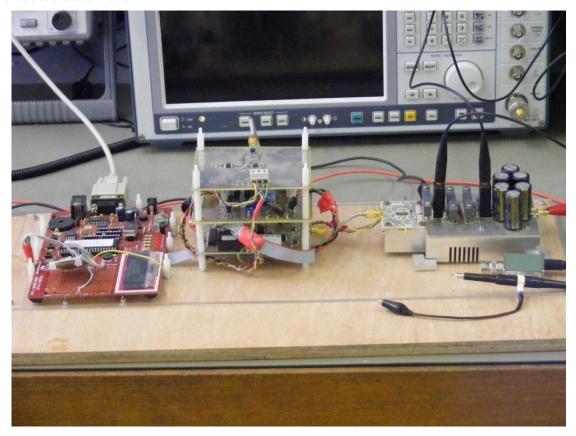

Figure 7 - Figure showing final Pulsed I-V measurement setup

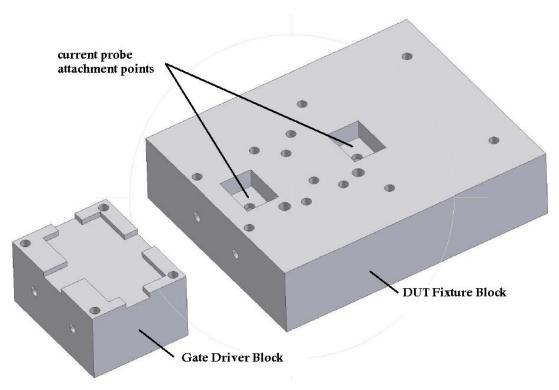

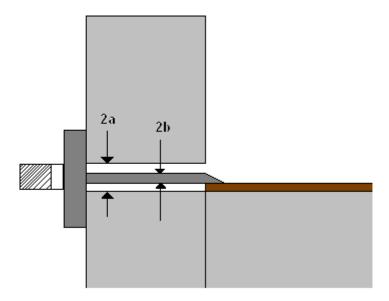

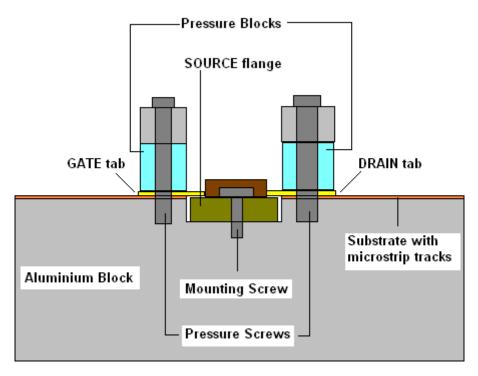

#### 2.4 Test Fixture for Power FETS

When designing the test fixture, various ideas had to be kept in mind. Firstly the gate driver must provide a gate stimulus voltage, irrespective of the required gate current, directly to the gate of the DUT. Secondly the fixture must provide for a voltage and current probe at both the gate and drain of the DUT. Finally the fixture must provide a large, low effective series resistance (ESR) capacitor bank at the drain. This is to ensure that the measurements are not influenced by a voltage drop at the drain.

The gate driver was implemented using an Analog Devices AD8392 quad pack current feed-back op-amp [17]. The AD8392 has a high current output (400mA), large output voltage swing ( $\pm 12V$ ) and high slew rate (900V/ $\mu$ s). The quad pack allows for a compact design. The design put the four op-amps in parallel with each other and places a series resistor at the output of each op-amp in order to isolate them from each other.

The choice of feedback and gain resistors was according to the suggestions in the data page [17].

The gate driver circuit board is mounted on an aluminium block. This block is then attached to the main DUT fixture block. This allows for a strong mechanical attachment, as well as allowing a modular implementation of the gate driver which would allow for future improvements. This would be useful if there is a need to change the driver amplifier.

The voltage sensing is implemented by mounting high impedance probe attachments directly on to the PCB. A thin high impedance transmission line connects the mounting point to the gate and drain.

Current sensing is achieved by the use of two Tektronix current probes, a CT-1 and CT-2 probe. These probes are mounted directly to the fixture block.

Figure 8 - Figure of gate driver block and DUT fixture block

When performing initial tests on various devices, an unwanted resonance was observed in the measurements. This was found to be due to the series inductance of the current probe. In the practical implementation, shown in Figure 7, Figure 8 and Figure 9, the current probe requires a short length of copper wire to pass through the probe, which has an inductance. A common estimate for the inductance of a thin wire is 1nH per millimetre. The length of wire used is roughly 10mm, thus a series inductance of 10nH is added. This inductance, along with the

small capacitance formed at the drain caused a resonant effect. In order to solve the problem, a shunt resistor was placed directly at the drain. The value of this resistor was chosen to be  $1k\Omega$ . This allowed for the stabilization of the drain while not drawing more than 26mA of DC current from the power supply.

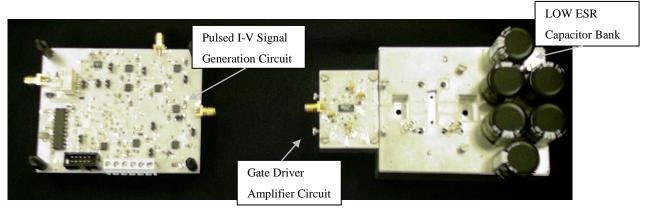

Figure 9 - Photo of fixture assembly shown in two separate sections. The section on the left shows the pulsed I-V signal generation circuit. The section on the right shows the gate driver amplifiers attached to the power FET test fixture

# 2.5 Control System

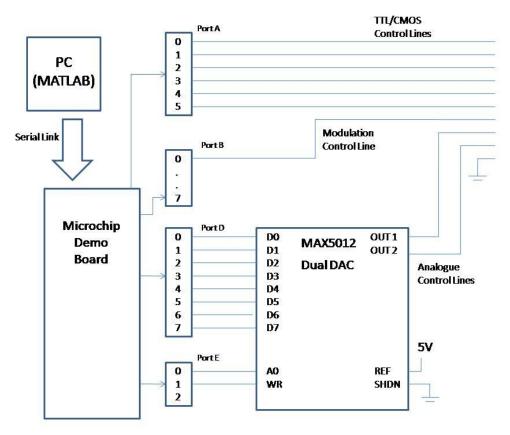

The control of the entire system, as shown in Figure 10, is done by means of MATLAB executable code. This code allows the user to send instructions via a serial cable to the Microchip demonstration board. The demonstration board controls an 8-bit Maxim MAX5102 dual digital to analogue converter (DAC) [18], as well as seven TTL/CMOS logic control lines. The DACs are used to control the amplitude variation and the frequency variation as described earlier in the chapter. The logic control lines are used to control the relay position, the various offset and addition switches and the modulation cascade switch.

The DC voltage output of each of the DACs is controlled by the following:

$$Vout = (Nb \times Vref) \div 256$$

6

Figure 10 - Figure showing schematic of the control system.

The MAX5102 DAC is controlled by firstly setting the 8-bit parallel control line (D0...D7). The PIC then selects the DAC to be set by setting the address line (A0) on the MAX5102 to either high (sets DAC 1) or low (sets DAC 2). The write line is then toggled on and off to latch the 8-bit level of the selected DAC.

# 2.6 Measurement System

Data retrieval was performed by firstly setting the gate voltage and then sweeping the drain voltage. The resulting currents were measured on a Tectonics TDS-380 oscilloscope. These measurements were performed by hand as the computer interface of the oscilloscope was not implemented at the time. This allowed for possibility of inaccuracies, although this was minimised by measuring each point several times and averaging the results.

## 2.7 Calibration

In order to ensure that the measurements taken were accurate enough to correctly characterize the device, two calibration techniques were used. Firstly, a known power was applied to a known 50  $\Omega$  load. This was implemented using a Rohde & Schwartz SMIQ signal generator. The frequency was set at 6MHz to ensure that

there could be no distortion of the results due to a frequency dependent response. By measuring the resulting currents flowing through the 50  $\Omega$  load and the voltage over the load, an exact calibration of the voltage and current sensors could be made. Through this technique, it was found that both resulted in negligible measurement errors.

#### 2.8 Results

As discussed previously, a pulsed RF test of transistors allows for various advantages over traditional DC measurements. The main advantage is that in RF testing, the SOA (safe operating area) is much greater. This allows for a better understanding of the devices high power response. A second advantage is that it allows the effect of dispersion and temperature to be taken into account. This would allow for better design parameters, such as load-line placement, and would thus lead to a more efficient and effective design.

Testing of the system was performed in two ways. Firstly the system was transported to IMEC in Belgium. These tests involved DC as well as RF pulse testing. Slight modifications were made to allow for on-wafer testing but functionally the system remained identical.

The second set of tests was perfumed at the University of Stellenbosch on LDMOS devices. This involved only pulsed RF testing.

The first set of results shown are those from the tests performed on on-wafer silicon carbide transistors at IMEC in Belgium. These test highlighted the first main difference between DC and RF pulse testing.

IMEC uses a hybrid between DC testing and RF pulse testing whereby the gate of the transistor is stimulated with a DC (square wave) pulse. By comparing the results of these tests to those of a similar RF pulse test, the direct effect of RF pulse testing can be seen.

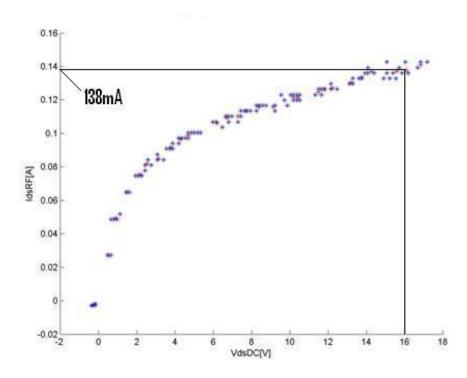

Figure 11 - Figure showing pulsed RF I-V curve of Silicon Carbide transistor P259\_4\_T03F3

Figure 12 - Figure showing pulsed DC I-V curve of Silicon Carbide transistor P259\_4\_T03F3

The graph showing the pulsed RF I-V curve, Figure 11, when compared to the pulsed DC I-V curve, Figure 12, shows a  $\pm$  30% drop in drain current Ids. This can be directly correlated to the fact that the gate is receiving a RF pulse instead of a DC pulse. Thus the effect of dispersion can be observed. In order to show a repeatable result and thus rule out the possibility of single transistor malfunctioning, the test was repeated on several transistors. The results shown in Figure 13 indicate a constant drop in drain current of approximately 20 - 30%.

Figure 13 - Diagram comparing the measured Ids of RF vs. DC pulsed measurements

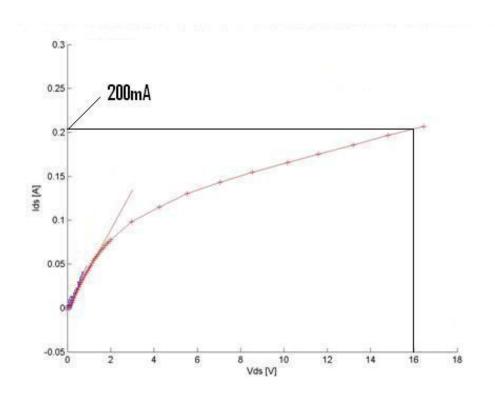

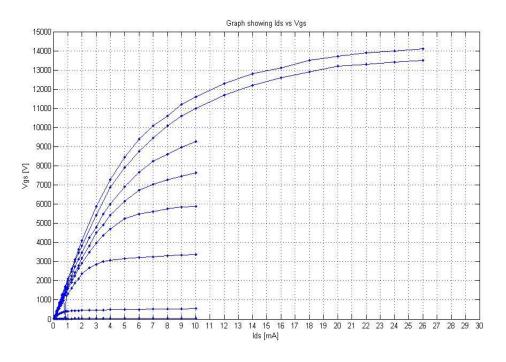

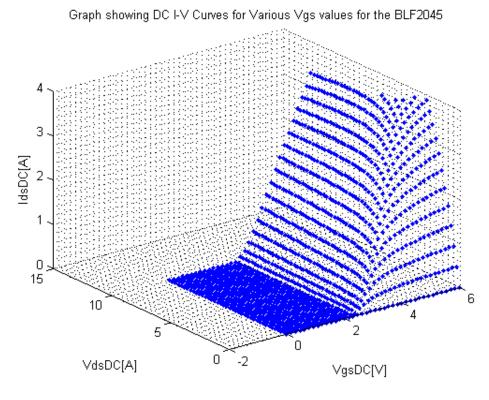

The second set of results are those of the RF pulse tests that were performed on the silicon based BLF2045 LDMOS transistor. The following graphs show the trend of the I-V curves to varying gate and drain voltages. This allows a direct comparison between pulsed RF measurements, shown in Figure 14, to a pure DC measurement, shown in Figure 15. The measurement was limited to operation within the safe operating area.

Figure 14 - Graph showing pulsed RF I-V curves for BLF2045 LDMOS device

Figure 15 - Graph showing DC I-V curves for various  $V_{\text{GS}}$  of the BLF2045 LDMOS device.

This test highlighted a much greater range of Ids swing in the pulsed RF I-V curves of Figure 14, and secondly, a more subtle difference in the shape of the pulsed RF and DC I-V curves. In the testing of the DC I-V curve, the knee area, which is the area in which the device begins to saturate, is distinct. This is very different when performing the pulsed RF testing which shows a more gradual transition into saturation. The significance of this fact is that load-line placement, for which I-V curves are the most important measurement, becomes a more difficult task. This will be discussed more detail in chapter 6.

A final result observed is that the device was not full driven into saturation. This would be due to a lack of voltage range of the gate driver.

# 2.9 Recommended System Improvements

Although the system showed very promising results, various flaws are apparent in the design. These hamper the effectiveness of the system. In order to improve the design, the following issues should be addressed:

The signal generator should be replaced with a high speed (>100MHz) digitally controlled IC.

The amplitude control should be replaced with a set pre-amplifier which amplifies the signal to a set maximum level and this should then be followed by a variable attenuator. This is suggested because of the fact that a major limiting factor in the design was that of the limited slew rate of the AD603 variable gain op-amp. The faster LM6181 op-amps compensated for this to some degree but do not counteract the limitations completely.

The level detection should be replaced with a digitally controlled power meter. This would allow a much greater accuracy as it would not be frequency or amplitude dependant as is the case with the active peak detector.

The DC level addition should be replaced with a DAC which would be set depending on the feedback from the power meter. This would also then facilitate a calibration procedure.

Finally, the gate driver amplifier should be replaced with a high speed, high voltage transistor amplifier. This would allow for a much greater range of gate voltages, thus enabling a view of the entire range of the devices operation.

#### 2.10 Conclusions

By using a pulsed RF measurement system instead of a DC measurement system it was found that new modes of system operation can be observed, although the accuracy and usefulness of this is still unproven. It showed that a device can be tested well beyond the DC SOA without fear of damage, which facilitates the creation of more accurate designs and estimations. It showed differences between the nature of DC and RF responses, as well as variations in the curve shapes.

It should be mentioned, though, that this system is not without its shortcomings. These faults are mainly due to the fact that the system is in a prototype stage of development.

These changes aside, the design of the pulsed RF measurement system was a success and proved the concept. This system can only lead to a greater understanding, and improved design of power amplifiers. The results obtained in this section will form the basis of design process of the 30W BLF2045 amplifier in chapter 6.

# Chapter 3 - Advanced Low Impedance TRL Fixture

#### 3.1 Introduction

The goal of this chapter is to document the design and implementation of a high-accuracy RF test fixture that allows for very accurate low impedance measurements of high power devices [19] [20]. This test fixture is implemented using a THRU-REFLECT-LINE (TRL) calibration method and pre-matching networks in order to create a smooth, frequency independent, and low reflection transition from a 50 Ohm coaxial environment to a low impedance microstrip measurement environment [21] [22].

The first section of this chapter will discuss the design and implementation of the Klopfenstein pre-matching networks [23]. The second section of the chapter will discuss the design of the mechanical fixture, and the third section will discuss the testing and validation procedure.

# 3.2 Low Impedance TRL design

#### 3.2.1 Klopfenstein Taper Design

As mentioned before, one of the challenges of a low impedance measurement test fixture is to create a smooth transition between the 50 Ohm coaxial environment and the low impedance device environment. This was implemented by using a Klopfenstein taper [23]. The reason for this choice is twofold. Firstly, a Klopfenstein taper allows for a very low reflection transition, and secondly, the taper provides a frequency independent response over a very wide band [24]. A further advantage of the Klopfenstein taper over other taper designs (such as triangular and exponential tapers) is that, for a given reflection coefficient within the pass band, the Klopfenstein taper gives the shortest taper length [24].

In all the taper designs, MATLAB code written by Pieter Jacob De Villiers Malan was used to generate the actual taper models. This code was written as part of his MSc.Eng thesis [24].

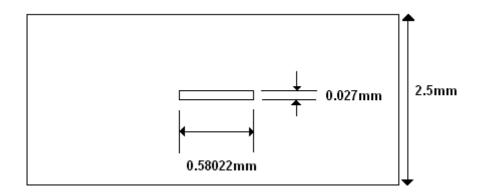

In order to design the tapers the following information was necessary: the input impedance, the output impedance, the maximum ripple within the pass band as well as the minimum operating frequency. The substrate dielectric constant must also be known. This is a value that is dependent on the substrate chosen. In this project Rodgers 6010 was used. This substrate has a typical  $\epsilon_r$  of  $10.2 \pm 0.25$ . This allows low impedances to be realised with moderate track widths. Specifically it allows the design of the 50  $\Omega$  input track width to be 0.58mm which is roughly the same width as the inner pin of the SMA connectors used in the fixture design.

The input impedance is naturally 50  $\Omega$  as this is the impedance of the coaxial measurement environment of the network analyser. The output tab widths were chosen to be the same as the transistor tab widths. The tab widths were between 5mm and 13mm. These widths along with the chosen substrates high  $\epsilon_r$  results in a low characteristic impedance which is closer to the transistor port impedance, thus resulting in less of a mismatch between the DUT and the measurement system.

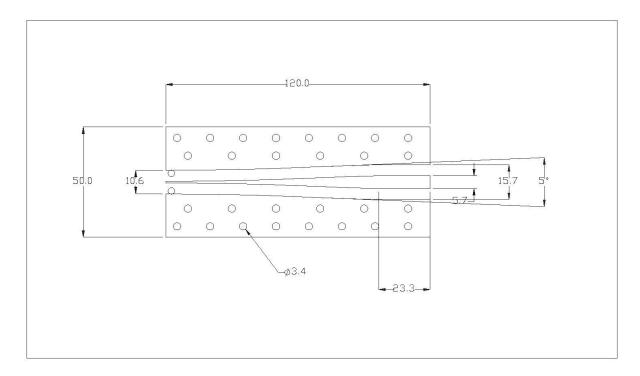

In terms of this project, two different tapers were required. The first taper, shown in Figure 16, was used to measure the low power BLF2045 and BLL1214-35 transistors. The second taper was used to measure the high power BLL1214-20 transistor, this taper has the same profile as the taper shown in Figure 16 but has a wider tab width.

Figure 16 - Figure Showing Klopfenstein Taper Profile of BLF2045 and BLL1214-35 measurement fixtures including mounting holes for screws.

As both the BLF2045 and BLL1214-35 transistors use the same package, the same taper design could be used. The port tab widths on the two transistors are between 5.53mm and 5.7 mm. Thus, the final output impedance of the low power taper is  $10.7551\Omega$

The BLL1214-250 is packaged in a larger die. This accommodates a higher power capability. The tab widths on this package are between 12.57mm and 12.83mm. Thus, the final output impedance for the high power taper is  $5.33811\Omega$

The MATAB Klopfenstein design program [24] calculated the tapers to be 96.7283mm long. As this is an awkward number, a short transmission line was added to the output port in order to lengthen the taper to a more

useable length of 110mm. This line had the same width as the low impedance output (DUT) port, as to not affect the output impedance.

#### 3.2.2 Mechanical Fixture Design

There are two considerations when designing a mechanically sound test fixture. The first and most important is to ensure that the in-fixture measurements are accurate. The second is to maintain an easily repeatable measurement. One should keep in mind that although measurement and fixture errors can be compensated for in the calibration process, this proves to be detrimental to the overall measurement accuracy of the system. It should also be noted that as the measurement fixture requires manufacturing, the design must be of reasonably low complexity so that designs can be created without the large cost of outsourced machining.

As mentioned previously in the chapter, two fixtures were designed. A complete fixture for the low power devices and a second fixture for the high power device. Fortunately the size of each fixture allowed for the reuse of the design, with only the actual DUT (Device Under Test) fixture block being different.

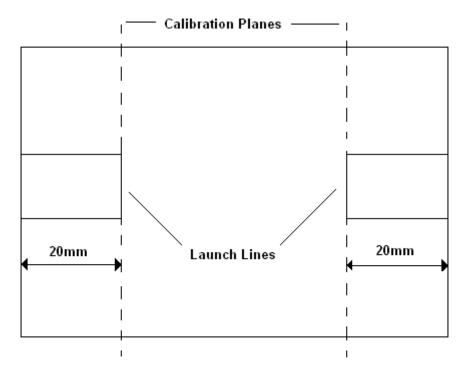

Each fixture set comprised of six sections: the tapered launch sections with their coaxial to microstrip conversions, the DUT fixture blocks and the three TRL (Through-Line-Reflect) calibration standards, these being a zero length through standard, two non-zero line standards, and a short standard [24] [22] [25] [26] [27]. The DUT fixture block could also double as an open standard.

The first step in the mechanical design is the coaxial to microstrip conversion. A flange mount female SMA connector was used to provide the coaxial launch due to their relatively low cost and availability. The SMA connector chosen provided an inner pin diameter that was near to the 0.58mm of the  $50~\Omega$  initial taper width.

Figure 17 - Figure showing the coaxial to microstrip conversion including the dimensioning of the coaxial to microstrip transition implemented in order to maintain a 50  $\Omega$  impedance.

The dimensions of the inner pin and the hole diameter were designed firstly so that the 50  $\Omega$  impedance was maintained but also to ensure that the ground discontinuity at the transition is minimised by placing the edge of the hole at the same point as the underside of the 0.635mm substrate.

Next, the inner pin diameter and hole diameter, as shown in Figure 17, needed to be chosen. Two equations dictate these values. Firstly, the equation for the characteristic impedance of a coaxial line  $(Z_0)$  [28] [29].

$$Z_0 = \sqrt{\frac{\mu}{\epsilon}} \times \frac{\ln\left(\frac{a}{b}\right)}{2\pi}$$

7

where

$$\mu = 4~\text{x}~\Pi~\text{x}~10^{\text{-}7}$$

$\varepsilon = 8.854 \text{ x } 10^{-12}$

Secondly the physical restrictions of the fixture result in the equation

$$2a = 2 \times 0.635 + 2b$$

8

Solving these equations for a  $Z_0$  of  $50\Omega$  results unusable values as the accuracies required would not be possible with available machining techniques. Thus an approximation was made:

Inner Pin

$$\emptyset = 0.6mm$$

Outer Hole  $\emptyset = 1.4mm$

This resulted in characteristic impedance  $Z_0$  of  $50.799\Omega$ .

The next step was a precautionary step. It was decided that, as a coaxial-microstrip transition can cause higher-order modes to propagate, a short channel would be placed at the transition. This would help to suppress any possible higher-order modes.

Figure 18 - Figure showing approximation of the cross section of a waveguide channel at coaxial-microstrip transition

Several approximations were made when choosing the dimensions of the channel shown in cross section in Figure 18. Firstly, the effect of the substrate was ignored, and secondly the width was chosen wide enough to not effect design significantly.

The width of the track as well as the thickness of the track was also fixed at 0.58022mm and 0.027mm respectively. The centre frequency ( $f_c$ ) was chosen to be 1.3GHz.

The next step was to design the calibration standards.

Figure 19 - Figure showing the design plan of the calibration standards as well as their launch lines and calibration planes.

The use of launching lines, shown in Figure 19, allowed a repeatable transition between the taper blocks and each of the calibration and DUT blocks. In a TRL standard calibration, a non-zero length line is required. The choice of line length determines the frequency band over which the calibration remains valid.

For any given length, the minimum and maximum operating frequencies are those at which the line is  $20^{\circ}$  and  $160^{\circ}$  respectively [27] [26].

It was decided that two calibration lines would be used, the first to cover the 500MHz-4 GHz band, and the second to cover the 1 GHz -8 GHz band.

The calculations resulted in the two lines being  $\pm 12$ mm and  $\pm 6$ mm for the low and high band respectively.

Table 1 - Table showing the relative electrical lengths of LINE 1 calibration Standard (12mm)

|                       | Frequency | Angle (degrees) |

|-----------------------|-----------|-----------------|

| Centre Frequency      | 2.25 GHz  | 96.1674         |

| Upper Frequency Limit | 4 GHz     | 172.433         |