# The Design and Characterization of Diode Detectors

WJC Koen

Supervisor: Prof JB de Swardt

Thesis presented in partial fulfilment for the requirements of the degree of Master of Engineering at the University of Stellenbosch.

## Declaration

I, the undersigned, hereby declare that the work contained in this thesis is my own work and has not previously in its entirety or in part been submitted at any university for a degree.

WJC Koen Date

#### Abstract

The use of diode detectors for power measurement and AM demodulation is not a new subject. The design and characterization of optimum diode detectors can, however, always be improved. In this thesis a step-by-step design procedure is presented for the design of various diode detectors. The design itself is not a complex task, but the success of the results depends on the characterization of both the detector and the diode. A method to extract optimized diode models from DC and small signal measurements are presented. Analyzing the detector circuit with the harmonic balance technique does the characterization of the detector. These results can be used to create an error-correcting algorithm to compensate for the non-linear behavior of diode detectors and to improve the dynamic range and sensitivity of the design.

## **Opsomming**

Die gebruik van diode detektors vir drywingmetings en AM demodulasie is nie 'n nuwe begrip nie. Die ontwerp en karakterisering van optimum diode detektors kan egter altyd verbeter word. 'n Stap-vir-stap prosedure word in hierdie tesis beskryf waarvolgens verskeie detektors ontwerp kan word. Die ontwerp, op sig self, is nie 'n ingewikkelde proses nie, maar die sukses van die detektor hang af van die karakterisering van beide die detektor en die diode. 'n Metode om diode modelle vanuit GS- en kleinseinmetings te onttrek word bespreek. Die karakterisering van die detektor word gedoen deur die baan met die harmonieke balans metode op te los. Hierdie resultate kan gebruik word om 'n algoritme te skep wat kompenseer vir die nie-lineêre gedrag van die detektor. Die dinamiese bereik en sensitiwiteit van die ontwerp kan sodoende verbeter word.

## Acknowledgements

I would like to thank the following persons for their contributions to this work:

- Firstly my supervisor, Prof Johann de Swardt, for his guidance and interest in the progress of my work.

- Wessel Croukamp and Ashley Cupido for their precision work.

- My friends and family, for all their love and support throughout my engineering studies, especially towards the end of this thesis.

- Lastly my Creator, Jesus Christ, who gave me the ability and strength to study and whose guiding hand is following me wherever I go.

# Contents

| 1 | INTRODUCTION                                                    |    |

|---|-----------------------------------------------------------------|----|

|   | 1.1 MICROWAVE DIODES                                            |    |

|   | 1.2 SCHOTTKY BARRIER DIODE DETECTORS                            | 2  |

|   | 1.3 THE CHARACTERIZATION OF DIODES                              | 2  |

|   | 1.4 THE DESIGN OF MATCHING CIRCUITS                             | 2  |

|   | 1.5 THE DESIGN OF DIODE DETECTORS                               | 3  |

|   | 1.6 ANALYSIS ALGORITHMS                                         |    |

|   | 1.7 SIMULATED RESULTS AND MEASUREMENTS                          |    |

|   |                                                                 |    |

| 2 | MICROWAVE DIODES.                                               | 4  |

|   | 2.1 SCHOTTKY DIODES.                                            |    |

|   | 2.2 PIN DIODES                                                  |    |

|   | 2.3 TUNNEL DIODES                                               |    |

|   | 2.4 VARACTOR DIODES                                             |    |

|   | 2.5 GUNN DIODES.                                                |    |

|   | 2.6 IMPATT DIODES.                                              |    |

|   | 2.7 CONCLUSION.                                                 |    |

|   | 2.7 CONODOSION                                                  | 13 |

| 3 | SCHOTTKY BARRIER DIODE DETECTORS                                | 14 |

| - | 3.1 INTRODUCTION                                                |    |

|   | 3.2 DIODE PERFORMANCE CHARACTERISTICS.                          |    |

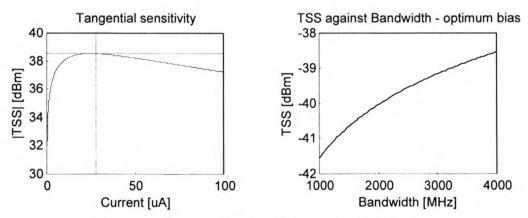

|   | 3.2.1 Tangential Sensitivity (TSS)                              |    |

|   | 3.2.2 Video Resistance (Rv)                                     |    |

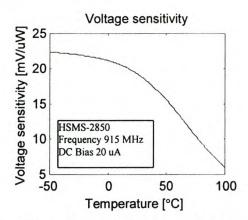

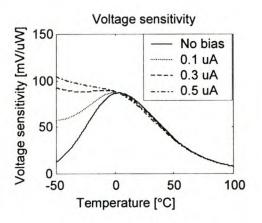

|   | 3.2.3 Voltage Sensitivity.                                      |    |

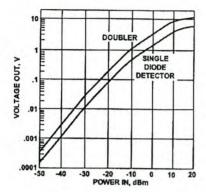

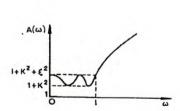

|   | 3.3 SQUARE-LAW AND LINEAR DETECTION.                            | 20 |

|   | 3.3.1 Diode Basics.                                             |    |

|   | 3.3.2 Detection Law.                                            |    |

|   | 3.4 THE NECESSITY OF BIAS CURRENT.                              | 22 |

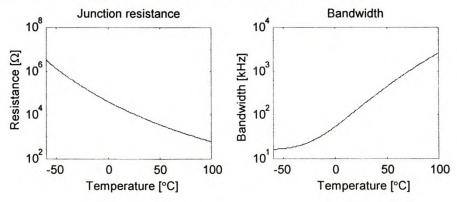

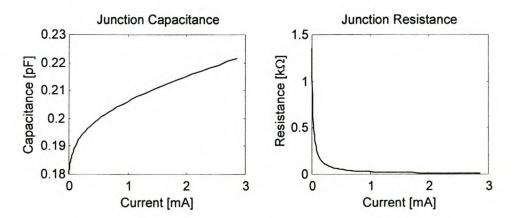

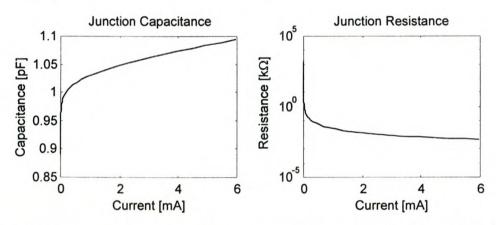

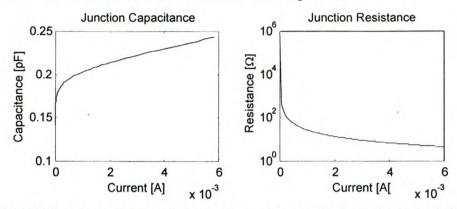

|   | 3.4.1 Junction Resistance                                       |    |

|   | 3.4.2 Measured Detected Voltage.                                |    |

|   | 3.5 THE VOLTAGE DOUBLER.                                        |    |

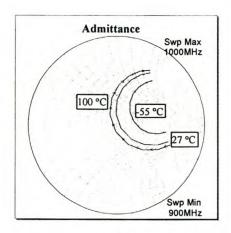

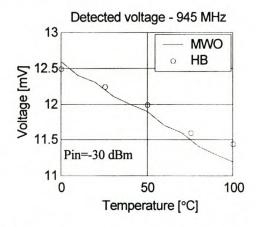

|   | 3.6 THE DIODE DETECTOR AT TEMPERATURE EXTREMES                  |    |

|   | 3.6.1 Junction Resistance.                                      |    |

|   | 3.6.2 Performance of Detector over Temperature.                 | 25 |

|   | 3.6.3 Compensation Methods.                                     |    |

|   | 3.7 CONCLUSION                                                  |    |

|   | 3.7 CONCLUSION                                                  | 21 |

| 4 | THE CHARACTERIZATION OF DIODES.                                 | 20 |

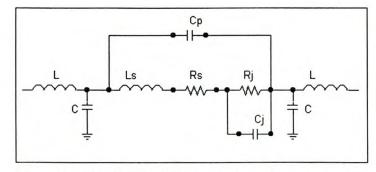

| • | 4.1 THE SPICE MODEL                                             |    |

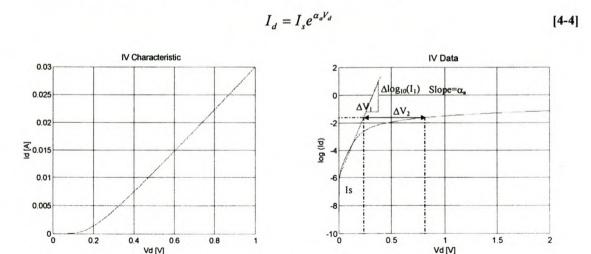

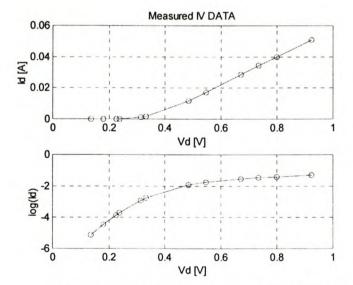

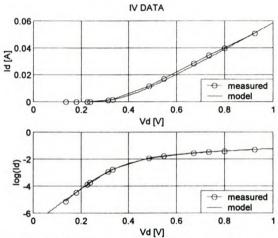

|   | 4.2 PARAMETER EXTRACTION FROM THE IV-CURVE                      |    |

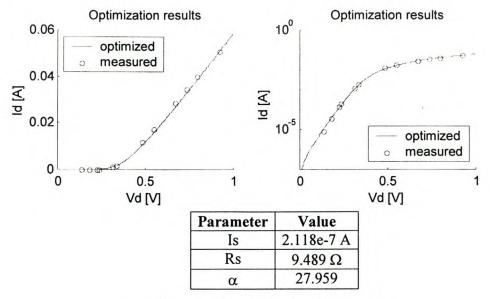

|   | 4.2.1 Optimizing the results obtained by the IV Characteristics |    |

|   | 4.3 PARAMETER EXTRACTION FROM CV-CURVE                          |    |

|   | 4.4 SMALL SIGNAL PARAMETER EXTRACTION                           |    |

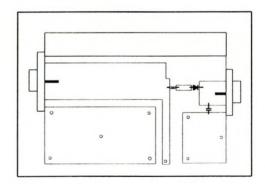

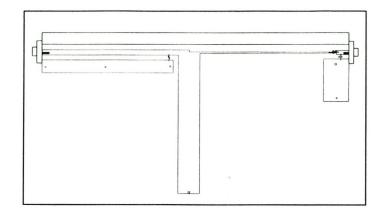

|   | 4.4.1 The use of TRL calibration.                               |    |

|   | 4.4.2 Designing TRL standards                                   |    |

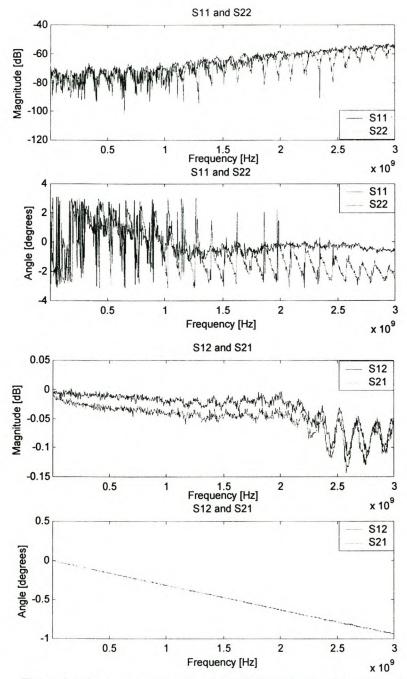

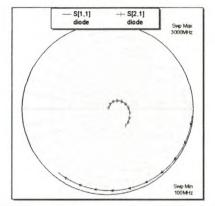

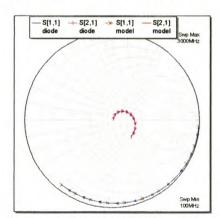

|   | 4.4.3 Measuring the s-parameters                                |    |

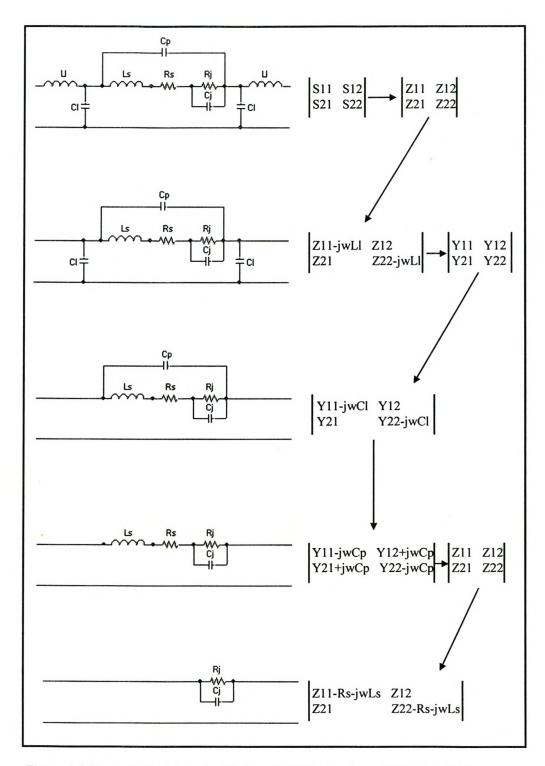

|   | 4.5 DE-EMBEDDING THE DIODE MODEL                                |    |

|   | 4.5.1 Calculation of Junction Parameters.                       |    |

|   |                                                                 |    |

|   | 4.5.2 Application to Simulated Data                             |    |

|   | 4.5.3 Application to Measured Data                              |    |

|   | 4.6 OPTIMIZATION OF THE DIODE MODEL.                            |    |

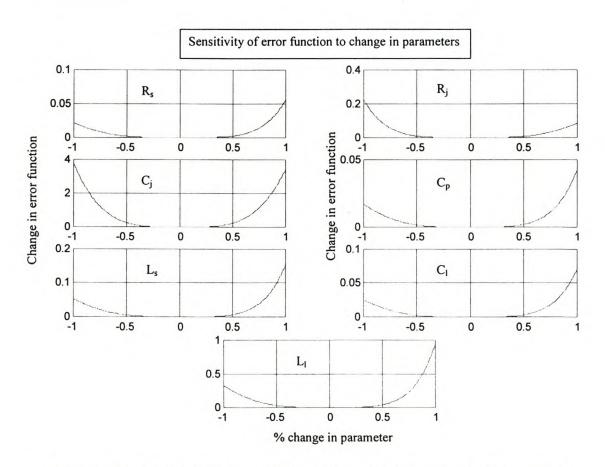

|   | 4.6.1 Determination of Sensitivity of Parameters                |    |

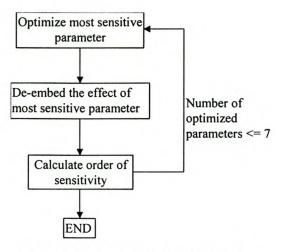

|   | 4.6.2 The Optimization Algorithm                                |    |

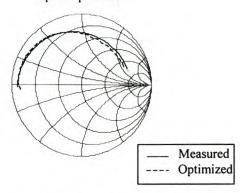

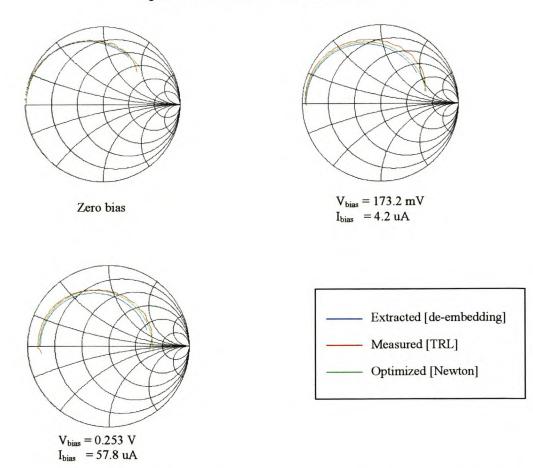

|   | 4.6.3 Results                                                   |    |

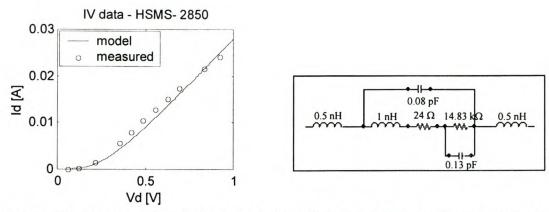

|   | 4.7 EXAMPLES OF PARAMETER EXTRACTION                            | 45 |

|   | 7.7.1 113(1)3*2010                                              | 47 |

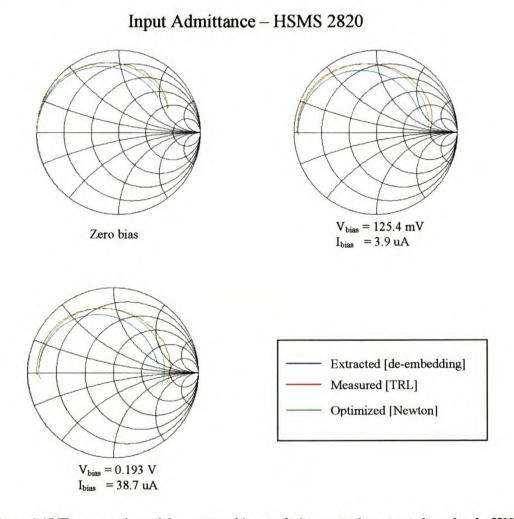

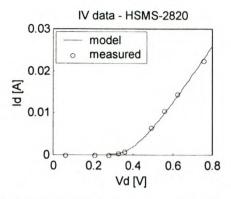

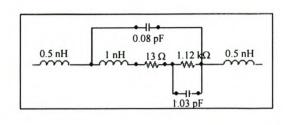

|   | 4.7.2 HSMS-2820                                      | 47 |

|---|------------------------------------------------------|----|

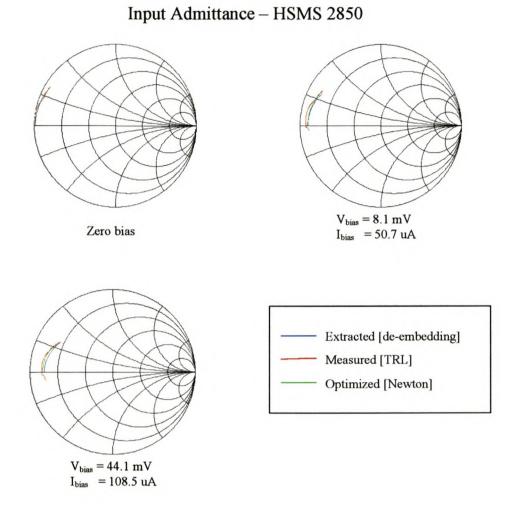

|   | 4.7.3 HSMS-2850                                      | 49 |

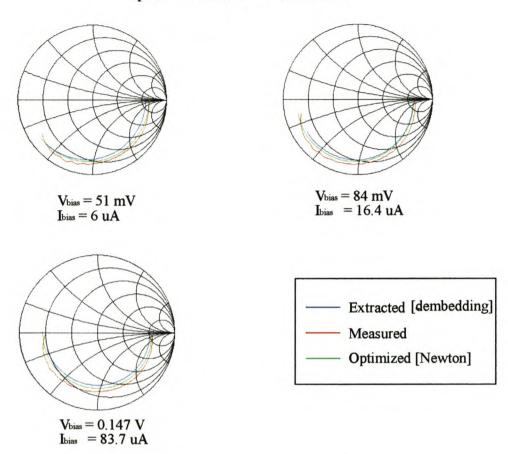

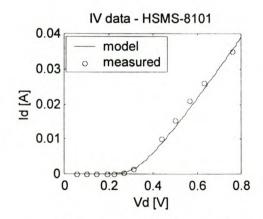

|   | 4.7.4 HSMS-8101                                      | 51 |

|   | 4.8 CONCLUSION                                       | 53 |

|   |                                                      |    |

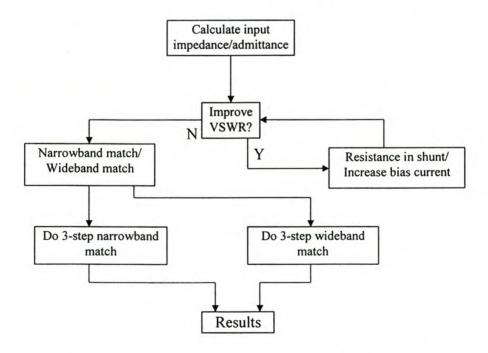

| 5 | THE DESIGN OF MATCHING CIRCUITS                      |    |

|   | 5.1 BACKGROUND                                       | 54 |

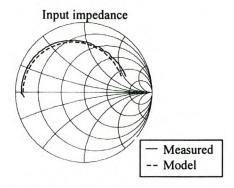

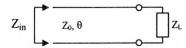

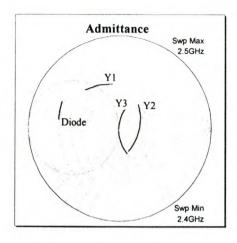

|   | 5.2 CALCULATION OF THE INPUT IMPEDANCE OF A DIODE    | 54 |

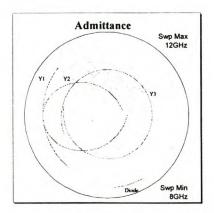

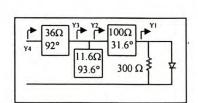

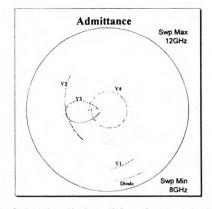

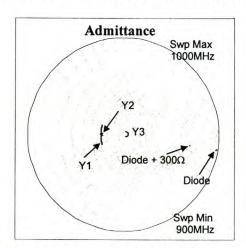

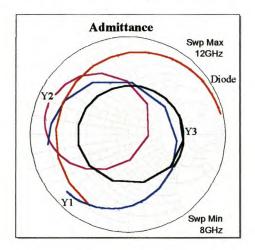

|   | 5.3 NARROWBAND MATCHING                              | 57 |

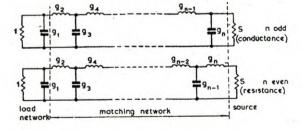

|   | 5.4 BROADBAND MATCHING                               | 58 |

|   | 5.5 IMPLEMENTATION IN MATLAB                         |    |

|   | 5.6 RESISTIVE MATCHING FOR LARGE SIGNAL DETECTORS    |    |

|   | 5.7 CONCLUSION                                       | 61 |

|   |                                                      |    |

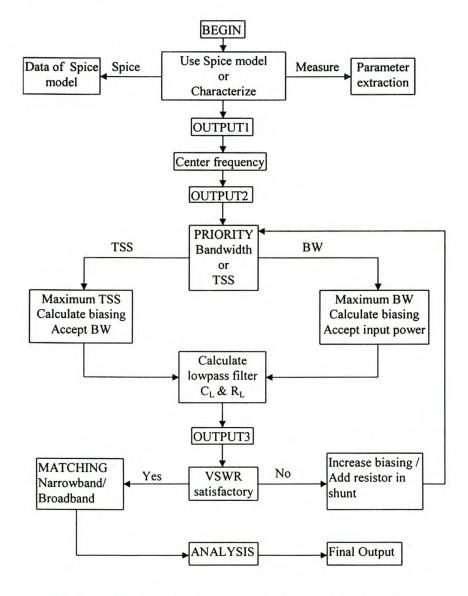

| 6 | THE DESIGN OF DIODE DETECTORS                        | 62 |

|   | 6.1 INTRODUCTION                                     |    |

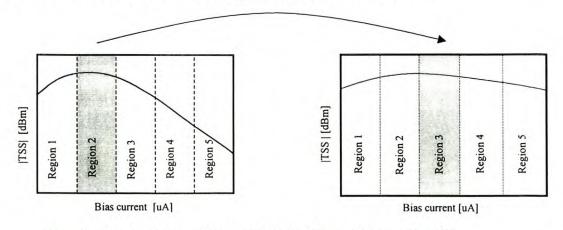

|   | 6.2 BIAS CURRENT                                     |    |

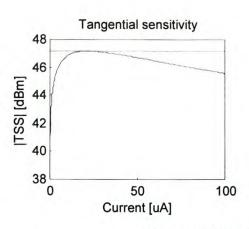

|   | 6.2.1 Design for Maximum TSS                         |    |

|   | 6.2.2 Design for Maximum Bandwidth                   |    |

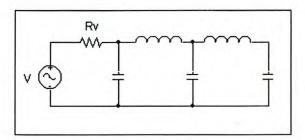

|   | 6.3 OUTPUT CIRCUIT                                   |    |

|   | 6.4 REMOVING THE DC OFFSET                           |    |

|   | 6.5 DESIGN EXAMPLE 1 – 950 MHZ.                      |    |

|   | 6.5.1 Background.                                    | 66 |

|   | 6.5.2 Schottky Diode and Models.                     |    |

|   | 6.5.3 Bias Current                                   |    |

|   | 6.5.4 Output Circuit                                 |    |

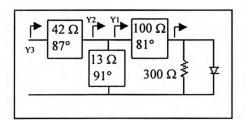

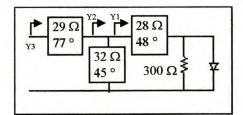

|   | 6.5.5 Matching Circuit                               |    |

|   | 6.5.6 The Final Design.                              |    |

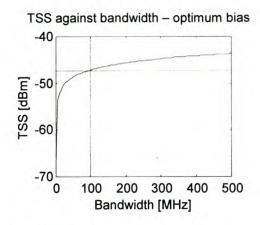

|   | 6.6 DESIGN EXAMPLE 2 – 2.45 GHZ.                     |    |

|   | 6.6.1 Background                                     |    |

|   | 6.6.2 Schottky Diode and Models                      |    |

|   | 6.6.3 Bias Current                                   |    |

|   | 6.6.4 Output Circuit.                                |    |

|   | 6.6.5 Matching Circuit                               |    |

|   | 6.7 DESIGN EXAMPLE 3 – 10 GHZ.                       |    |

|   | 6.7.1 Background                                     |    |

|   | 6.7.2 Schottky Diode and Models.                     |    |

|   | 6.7.3 Bias Current.                                  |    |

|   | 6.7.4 Output Circuit.                                |    |

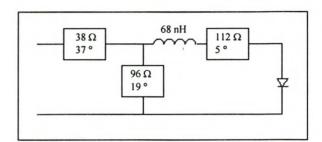

|   | 6.7.5 Matching Circuit.                              |    |

|   | 6.7.6 The Final Design.                              |    |

|   | 6.8 CONCLUSION.                                      |    |

|   |                                                      |    |

| 7 | ANALYSIS ALGORITHMS                                  | 79 |

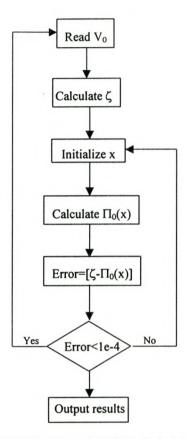

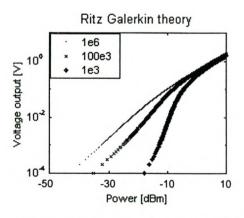

|   | 7.1 RITZ-GALERKIN METHOD.                            |    |

|   | 7.1.1 Background                                     | 79 |

|   | 7.1.2 Application of Theory                          |    |

|   | 7.1.3 Conclusion                                     |    |

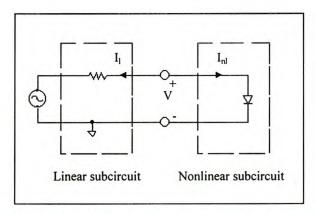

|   | 7.2 HARMONIC BALANCE METHOD                          | 83 |

|   | 7.2.1 Background                                     |    |

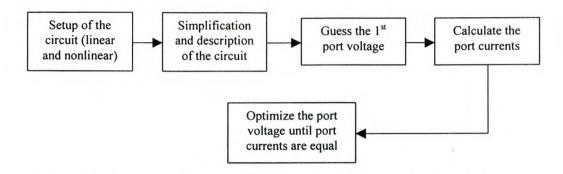

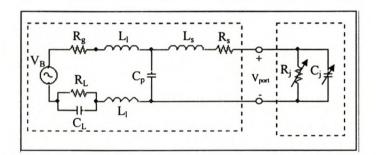

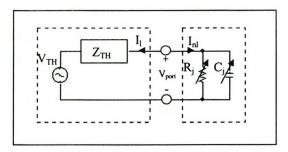

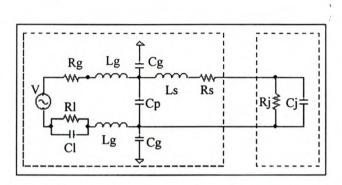

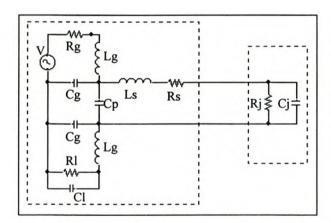

|   | 7.2.2 The Simplification of the Circuit              | 84 |

|   | 7.2.3 The Calculations of Port Voltages and Currents |    |

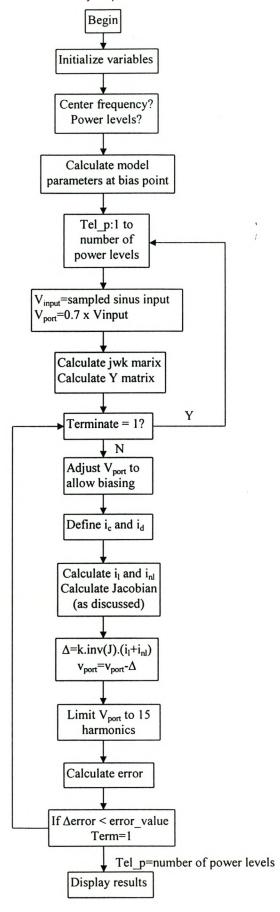

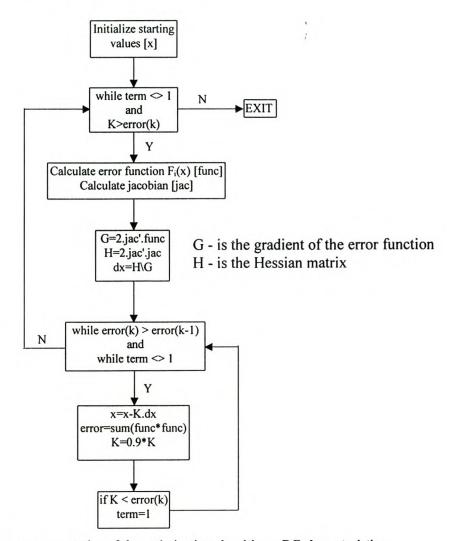

|   | 7.2.4 The Optimization Algorithm                     | 87 |

|   | 7.2.5 Implementation of HB algorithm in MATLAB       |    |

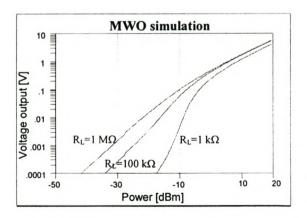

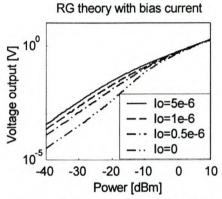

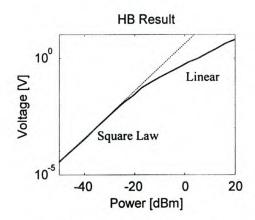

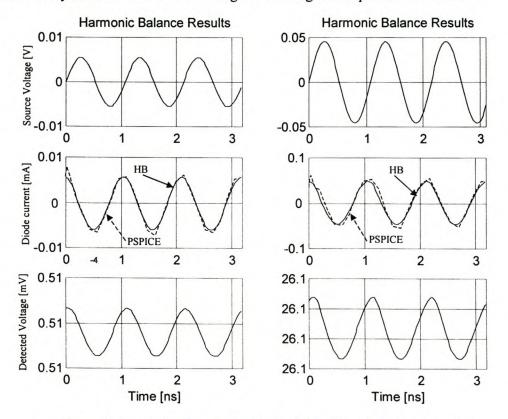

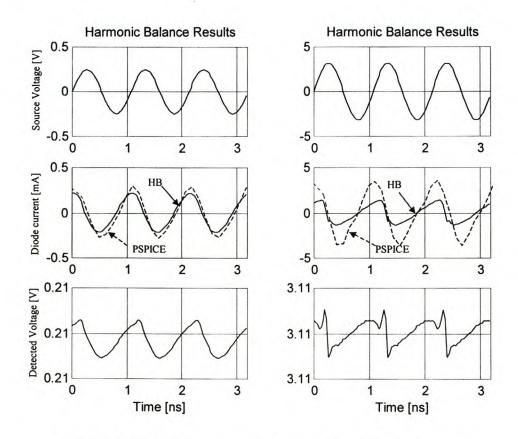

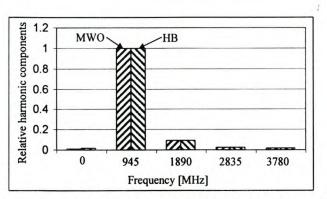

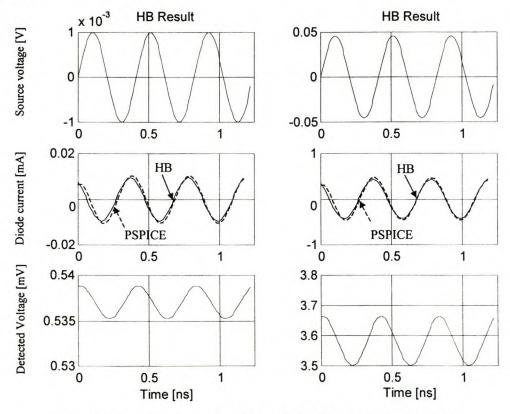

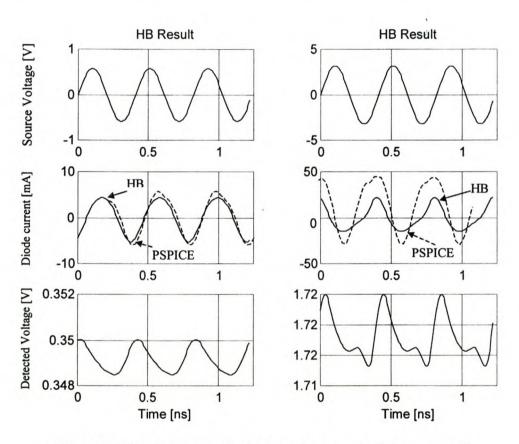

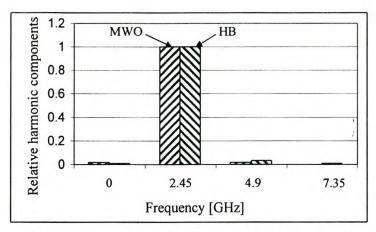

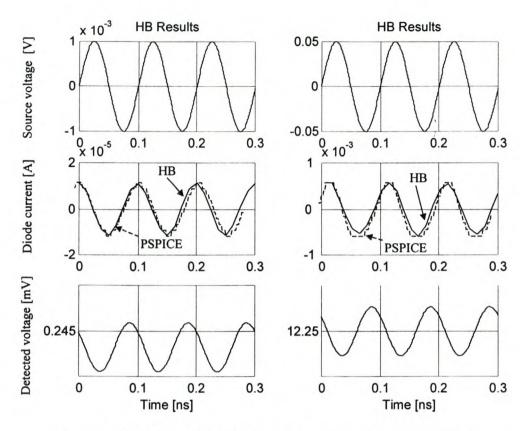

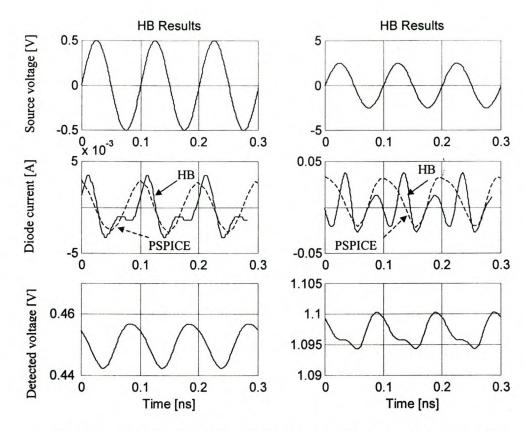

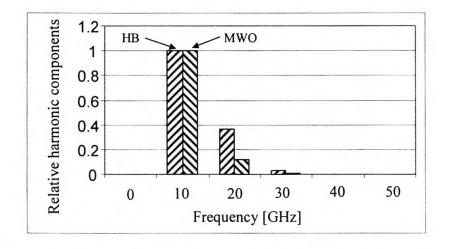

|   | 7.2.6 Simulated Results of HB algorithm              | 93 |

## Stellenbosch University http://scholar.sun.ac.za

|      | 7.2.7 General discussion on some aspects of the HB algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 93  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.3  | 3 CONCLUSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 94  |

| 8    | SIMULATED RESULTS AND MEASUREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 05  |

| 8.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

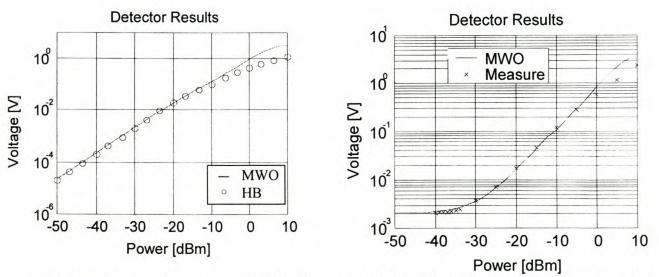

| 8.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

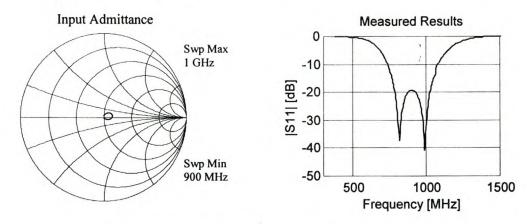

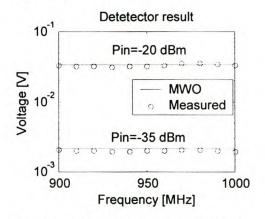

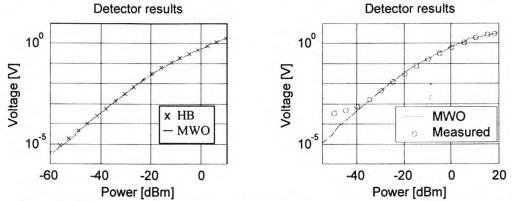

| 0.2  | 8.2.1 Verification of Matching Circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

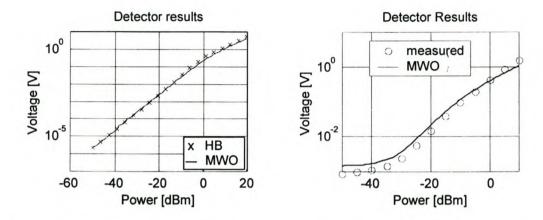

|      | 8.2.2 Simulations and Measurements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

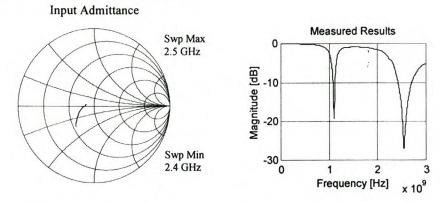

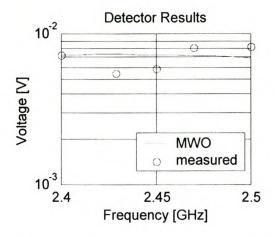

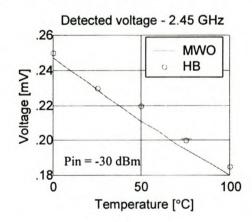

| 8.3  | DESIGN EXAMPLE 2 – 2.45 GHZ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

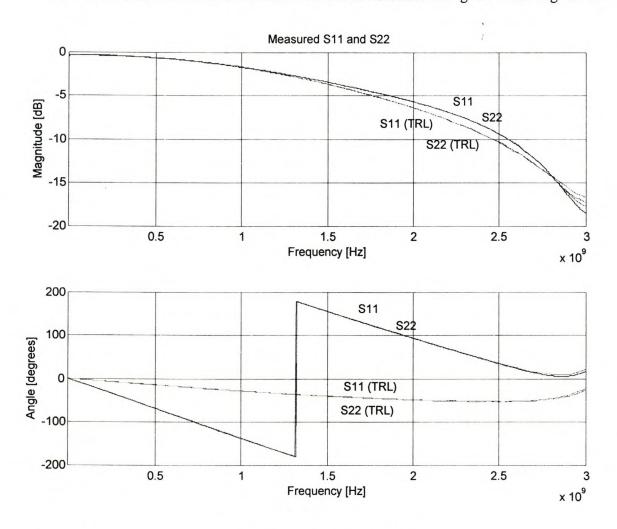

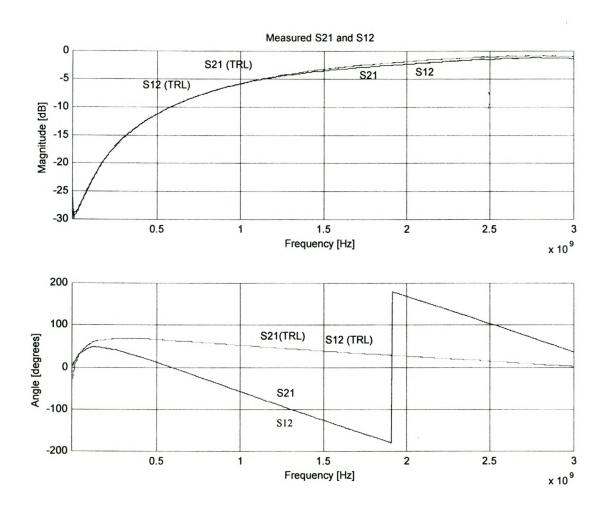

|      | 8.3.1 Verification of Matching Circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|      | 8.3.2 Simulations and Results.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

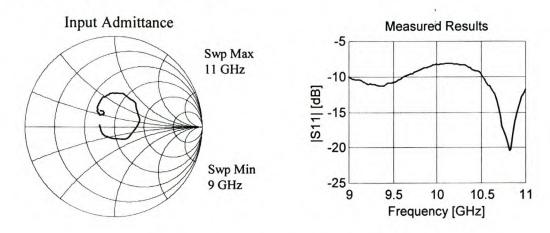

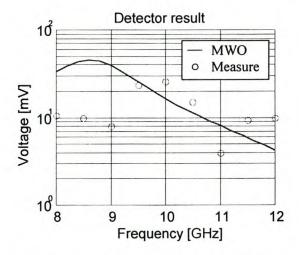

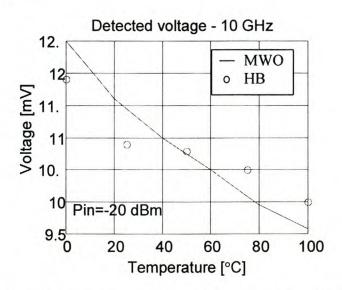

| 8.4  | DESIGN EXAMPLE 3 – 10 GHZ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|      | 8.4.1 Verification of Matching Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|      | 8.4.2 Simulations and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|      | CONCLUSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 9    | CONCLUSIONS AND RECOMMENDATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 110 |

|      | CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|      | 9.1.1 The Diode Model.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|      | 9.1.2 The Design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|      | 9.1.3 The Analysis and Error-correcting Methods.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 9.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|      | REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 113 |

| APPE | NDICES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

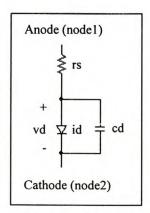

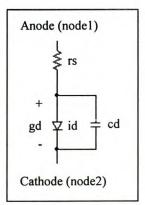

| A1   | The Spice Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

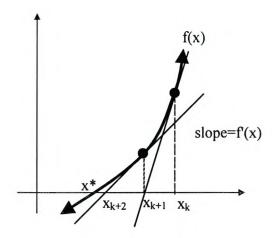

| B1   | Newton's Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| B2   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| B3   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| C1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| D1   | The state of the s |     |

| E1   | Calculation of Microstrip Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| F1   | Ritz-Galerkin Equations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| F2   | Harmonic Balance - Simplification of the detector circuit - X-band                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| G1   | Detector Design with Diode Pairs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

# List of Figures

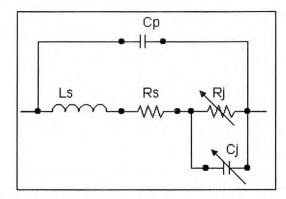

| Figure 2-1: The Schottky diode model                                                                         |

|--------------------------------------------------------------------------------------------------------------|

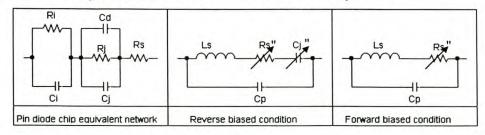

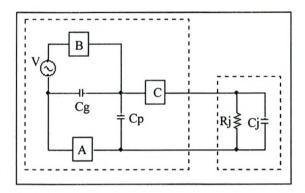

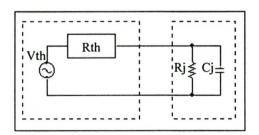

| Figure 2-2: The PIN Diode Equivalent Circuits                                                                |

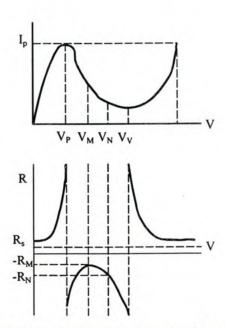

| Figure 2-3: Two characterization curves of tunnel diodes                                                     |

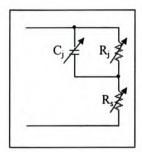

| Figure 2-4: The Varactor diode model9                                                                        |

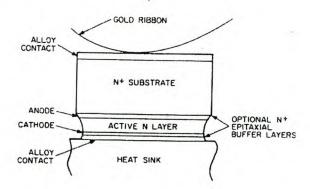

| Figure 2-5: The cross section of a Gunn diode                                                                |

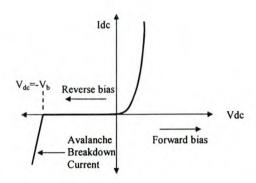

| Figure 2-6: The characteristic of a pn Junction Diode                                                        |

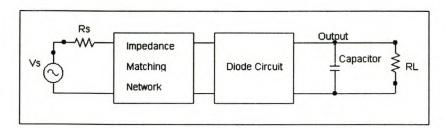

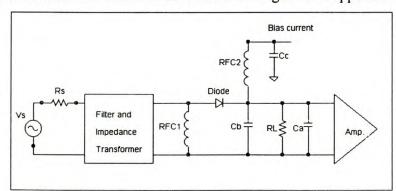

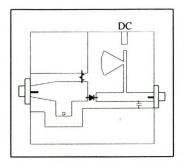

| Figure 3-1: Block diagram of a detector circuit                                                              |

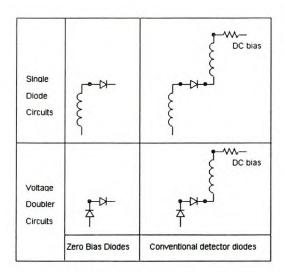

| Figure 3-2: Common types of diode circuits                                                                   |

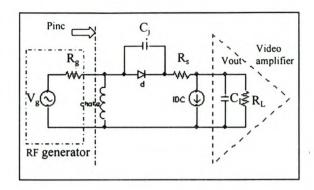

| Figure 3-3: Detector circuit                                                                                 |

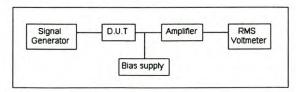

| Figure 3-4: TSS Test System                                                                                  |

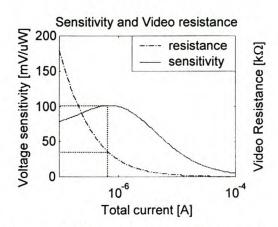

| Figure 3-5: Voltage sensitivity and Video resistance as a function of total current                          |

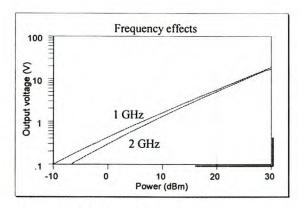

| Figure 3-6: Effect of higher frequency on detection slope                                                    |

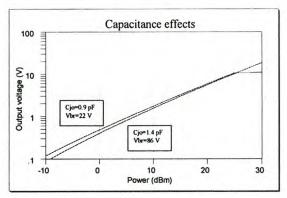

| Figure 3-7: Effect of higher capacitance on detection slope                                                  |

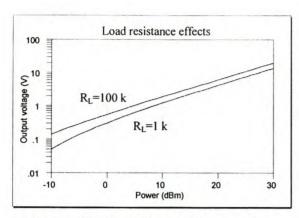

| Figure 3-8: The effect of load resistance on the detection slope                                             |

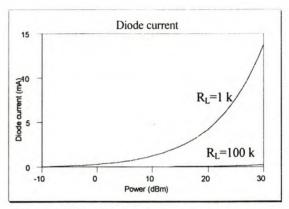

| Figure 3-9: The effect of load resistance on the diode current                                               |

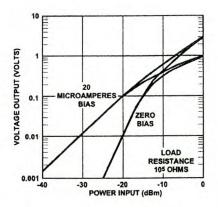

| Figure 3-10: Detection characteristics of Schottky diode                                                     |